Изобретение относится к области контрольно-измерительной техники и может быть использовано для контроля монтажных соединений при производстве электронной и электротехнической аппаратуры.

Известны устройства для контроля электрических соединений, содержащие два коммутатора, два счетчика, источник тестового напряжения, анализатор, память, элемент ИЛИ, регистр.

Общими признаками известных и предлагаемого устройства являются:

активизирующий коммутатор;

опрашивающий коммутатор;

активизирующий счетчик;

опрашивающий счетчик;

источник тестирующего напряженияJ

анализатор,

память1,

элемент ИЛИ.1

регистр.

Недостатком известных устройств является низкое быстродействие, обусловленное избыточностью выполняемых операций, так как происходит контроль связей точек объекта контроля

-s|

ел

00

§

о

по принципу каждая с каждой независимо от ранее выявленной принадлежности точки к какой-либо цепи. К недостаткам известных устройств следует отнести и сложность обработки информации при работе устройства в режиме автопрограммирования.

Наиболее близким к заявляемому объекту является устройство для контроля соединений в электрическом монтаже, содержащее п клемм для подключения объекта контроля, где п - число элементов объекта контроля, активизирующий и опрашивающий коммутаторы, активизирующий и опрашивающий счетчики, источник тестирующего напряжения, резистор, анализатор, блок памяти, клемму Общий вывод, блок управления, при этом каждая из п клемм для подключения объекта контроля соединена с соответствующими выходами активизирующего и опрашивающего коммутаторов, информационный вход опрашивающего коммутатора подключен к клемме Общий вывод и второму выводу источника тестирующего напряжения, первый вывод которого, через резистор подключен к информационным входам анализатора и активизирующего коммутатора, управляющий вход которого соединен с выходом активизирующего счетчика и информационным входом блока памяти, первый управляющий вход опрашивающего коммутатора соединен с выходом опрашивающего счетчика, выход анализатора соединен с первым управляющим входом блока памяти.

Общими признаками прототипа и заявляемого объекта являются:

п клемм для подключения объекта контроля,

активизирующий коммутатор;

опрашивающий коммутатор;

клемма Общий вывод,1

активизирующий счетчик ,

опрашивающий счетчик;

блок памяти;

анализатор;

источник тестирующего напряжения,

резистор,

блок управления.

Недостатком прототипа является ограниченное быстродействие, обусловленное тем, что после выявления связи не производится анализ на окончание цепи, вследствие чего выполняются лишние опросы точек, в ча10

15

20

25

58606

стности, большие излишние временные затраты формируются при исследовании обособленных точек объекта контроля.

Так как время контроля монтажа при производстве электронной и электротехнической аппаратуры является одним из основных технологических параметров, то создание быстродействующих устройств для контроля соединений в электрическом монтаже является на сегодняшний день актуальной задачей.

Целью изобретения является сокращение времени контроля,

Поставленная цель достигается тем, что в устройство для контроля соединений в электрическом монтаже, содержащее п клемм для подключения объекта контроля, где п - число элементов объекта контроля, активизирующий и опрашивающий коммутаторы, активизирующий и опрашивающий счетчики, источник тестирующего напряжения, резистор анализатор, блок памяти, . клемму Общий вывод, блок управления, при этом каждая из п клемм для подключения объекта контроля соединена с соответствующими выходаг ми активизирующего и опрашивающего коммутаторов, информационный вход опрашивающего коммутатора подключен к клемме Общий вывод и второму выводу источника тестирующего напряжения, первый вывод которого через резистор подключен к информационным входам анализатора и активизирующего коммутатора, управляющий вход которого соединен с выходом активизирующего счетчика и информационным входом блока памяти, первый управляющий вход опрашивающего коммутатора соединен с выходом опрашивающего счетчика, выход анализатора.соединен с первым управляющим входом блока памяти, введены первый, второй и третий элементы ИЛИ, дешифратор команд, регистр адреса, при этом вы- ход опрашивающего счетчика соединен с адресным входом блока памяти, второй управляющий вход которого подключен к выходу первого элемента ИЛИ, а выход к информационному входу блока управления, информационный выход которого соединен с информационными входами регистра адреса, активизирующего и опрашивающего счетчиков, выход анализатора подключен к управляющему входу блока управле30

35

40

45

50

55

5

ния, управляющий выход которого подключен к управляющему входу регистр адреса, выход которого подключен к входу дешифратора команд, первый выход которого соединен с первым входом второго элемента ИЛИ, второй выход с вторым входом второго элемента ИЛИ и управляющим входом активизирующего счетчика., третий выход с первым входом первого элемента ИЛ и первым входом третьего элемента ИЛИ, четвертый выход со вторыми входами первого и третьего элементов ИЛИ, пятый выход с третьим входом первого элемента ИЛИ, щестой выход с вторым управляющим вхолом опрашивающего коммутатора, седьмой выход с третьим управляющим входом опрашивающего коммутатора и сбрасывающими входами активизирующего и опрашивающего счетчиков, выход второго элемента ИЛИ соединен с управляющим входом опрашивающего счетчика, выход третьего элемента ИЛИ соединен со счетным входом опрашивающего счетчика, при этом опрашивающий коммутатор содержит дешифратор с п выходами, п триггеров, п диодов, п ключей, при этом первым управляющим входом опрашивающего коммутатора является первый вход дешифратора, выходы которого соединены с первыми входами соответствующих триггеров и анодами соответствующих диодов, третьим управляющим входом опрашивающего коммутатора являются соединенные между собой вторые входы триггеров, вторым управляющим входом опрашивающего коммутатора являются соединенные между собой управляющие входы триггеров и дешифратора, выходы триггеров соединены с катодами соответствующих диодов и управляющими входами соответствующих ключей, информационные входы ключей соединены с информационным входом опрашивающего коммутатора, а выходы ключей являются соответствующими выходами опрашивающего коммутатора,

Введение регистра адреса, дешифратора команд, первого, второго и третьего элементов ИЛИ в вышеуказанных связях с остальными элементами устройства обеспечивает смену активизируемых точек немедленно после обнаружения обособленных точек, либо конца цепи, что ведет к сокращению времени контроля. Использова586066

ние в составе опрашивающего коммутатора дешифратора, п триггеров, п диодов, п ключей в предложенных свя- 5 зях обеспечивает оперативное обнаружение обособленных точек и окончаний цепей, что ведет к значительному сокращению времени контроля.

Сопоставительный анализ с прото- Ю типом показывал, что заявляемое техническое решение отличается от известного наличием регистра адреса, дешифратора, элементов ИЛИ и их связями с остальными элементами уст- 15 роиства.

Таким образом, заявляемое устройство соответствует критерию изобретения Новизна.

Для доказательства соответствия 20 заявляемого объекта критерию существенные отличия был проанализирован ряд технических решений. Анализ показал, что регистры, дешифраторы, элементы ИЛИ, триггера, ключи, диоды, 25 и их свойства широко известны,

однако их введение в заявляемый объект в указанных связях между собой и с остальными элементами предлагаемого устройства в аналогичных тех- 30 нических решениях отсутствует, Это позволяет сделать вывод о соответствии заявляемого объекта критерию Существенные отличия.

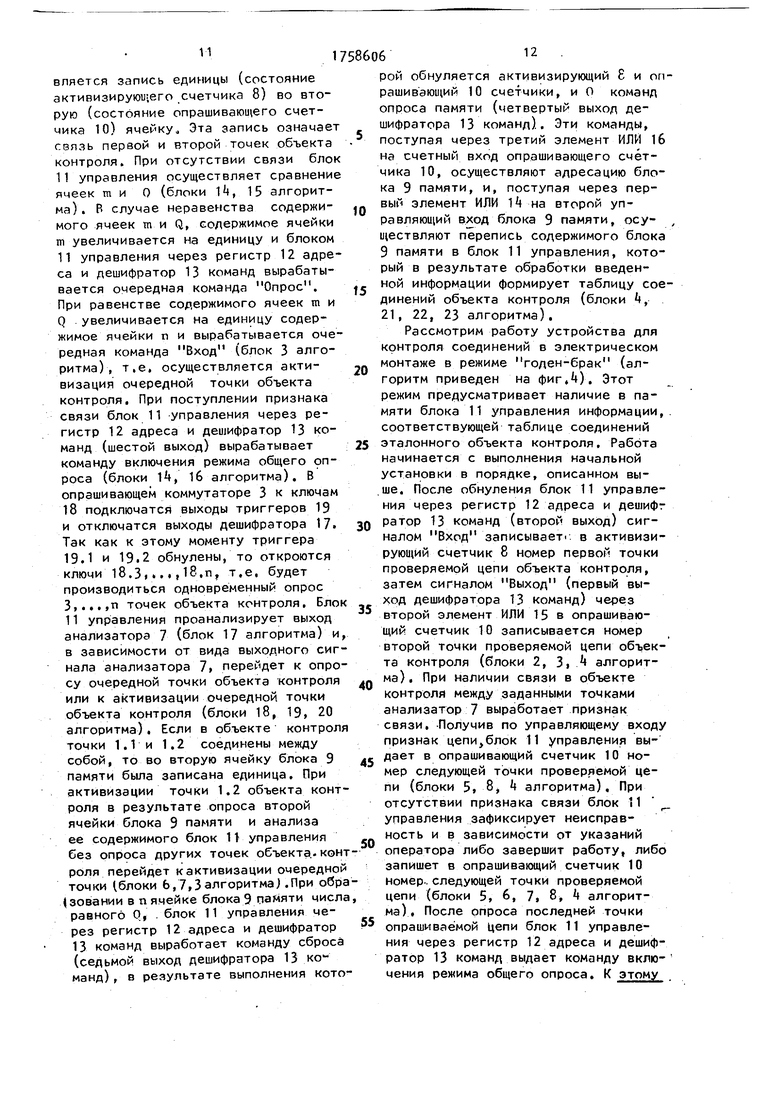

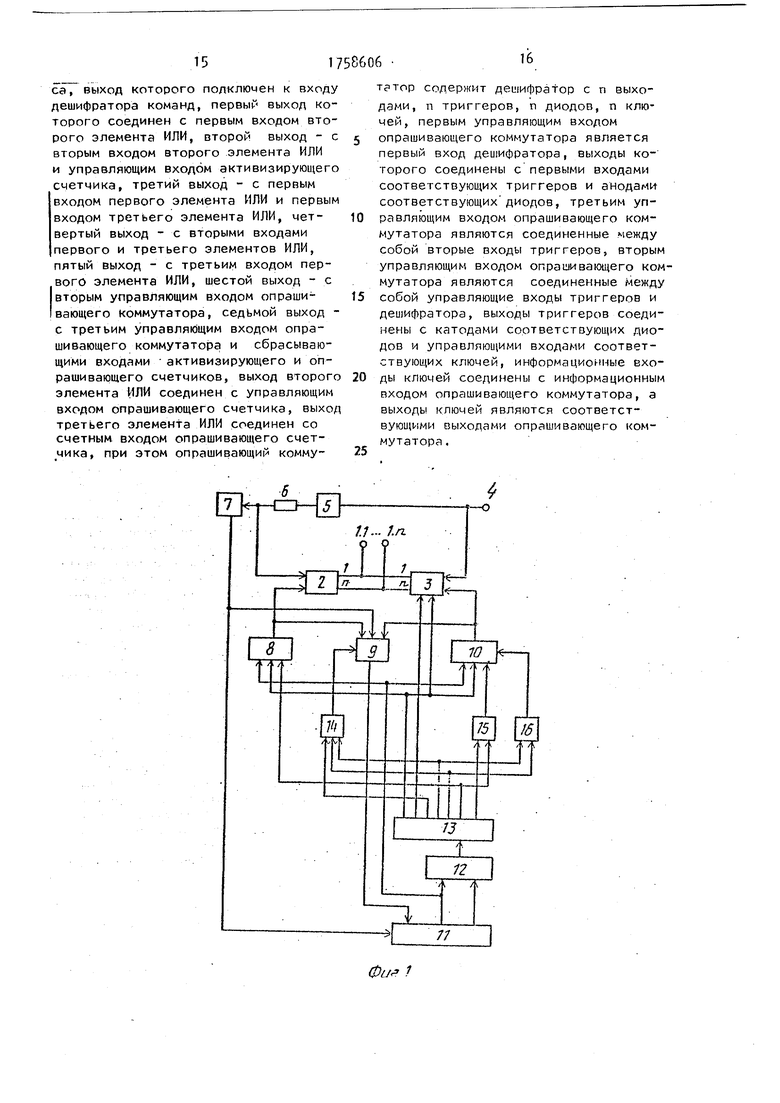

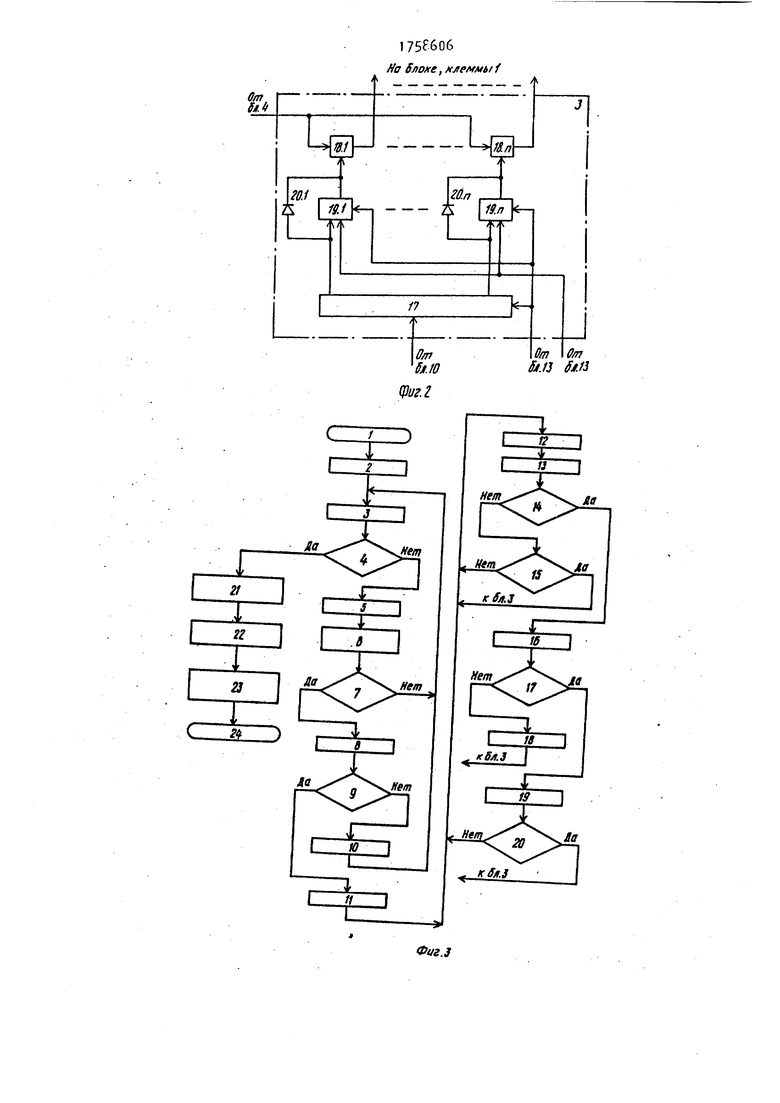

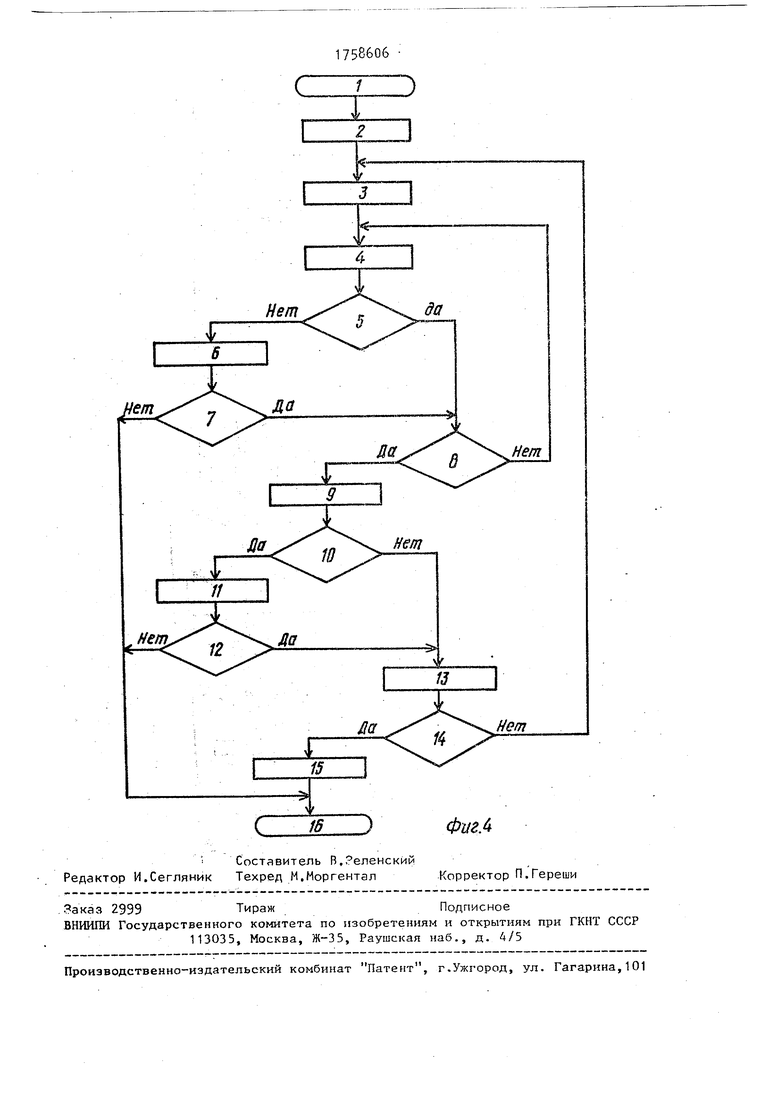

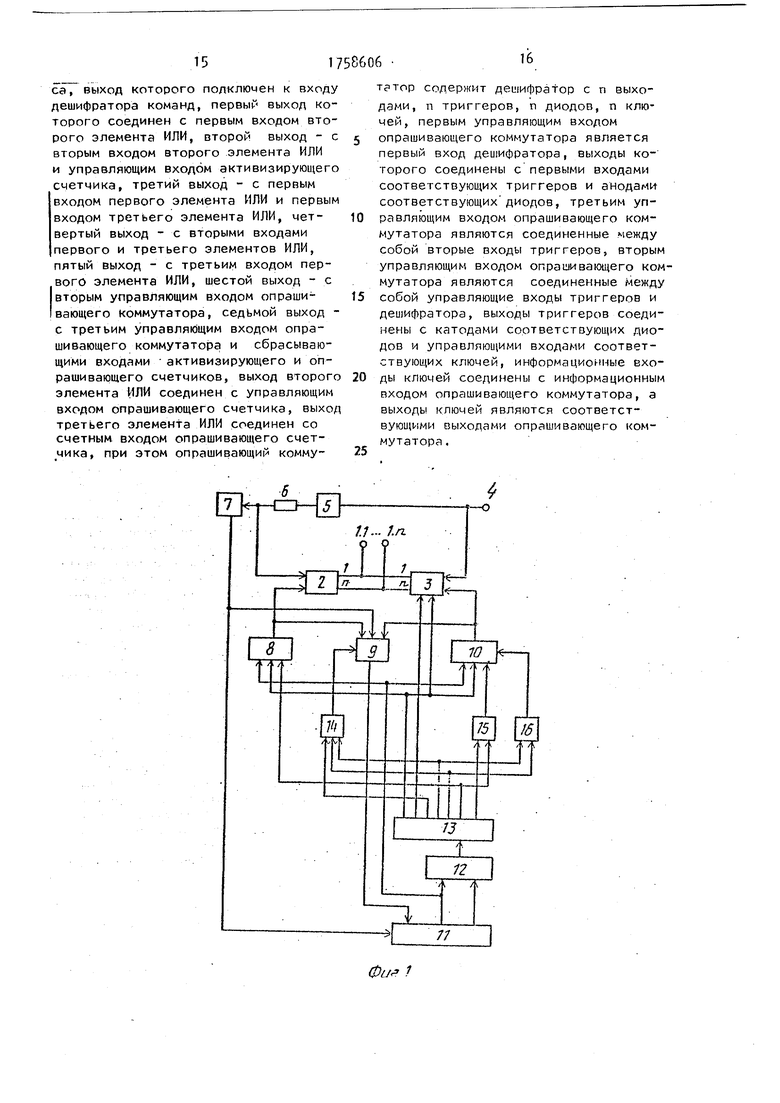

Сущность заявляемого технического j5 решения поясняется чертежами, где на фиг.1 приведена функциональная схема устройства для контроля соединений в электрическом монтаже, на фиг.2 - функциональная схема опрашивающего 40 коммутатора, на фиг.З - алгоритм

работы устройства для контроля соединений в электрическом монтаже в режиме автопрограммирования, на.фиг.4 - алгоритм работы устройства для конт- 5 роля соединений в электрическом монтаже в режиме годен-брак.

Устройство для контроля соединений в электрическом монтаже (фиг,1) содержит п клемм 1.1, .,,,1.п для 0 подключения объекта контроля, соединенных с соответствующими выходами активизирующего 2 и опрашивающего 3 коммутаторов. Информационный вход опрашивающего 3 коммутатора 5 соединен с клеммой k Общий вывод и вторым выводом источника 5 тестирующего напряжения, первый вывод которого через резистор 6 подключен к информационным входам анализатора

7 и активизирующего коммутатора 2. Управляющий вход активизирующего коммутатора 2 соединен с выходом активизирующего счетчика 8 и информационным входом блока 9 памяти. Первый управляющий вход опрашивающего коммутатора 3 соединен с выходом опрашивающего счетчика 10 и адресным входом блока 9 памяти. Выход анализатора 7 подключен к первому управляющему входу блока 9 памяти и управляющему входу блока 11 управления. Информационный вход блока 11 управления подключен к выходу блока

9памяти. Информационный выход блока 11 управления соединен с информационными входами регистра 12 адреса активизирующего 8 и опрашивающего

10счетчиков. Управляющий выход блока 11 управления подключен к управлющему входу регистра 12 адреса, выход которого соединен с входом дешифратора 13 команд. Второй управляющий вход блока 9 памяти соединен

с выходом первого элемента ИЛИ 1. Выход второго элемента ИЛИ 15 соединен с управляющим входом опрашивающего счетчика 10, выход третьего элемента ИЛИ 16 - со счетным входом опрашивающего счетчика 10. Первый выход дешифратора 13 команд соединен с первым входом второго элемент ИЛИ 15, второй выход - с управляющи входом активизирующего 8 счетчика и вторым входом второго элемента ИЛИ 15 третий выход - с первым входом первого элемента ИЛИ 1 и первым входом третьего элемента ИЛИ 16, четвертый выход - с вторыми входами первого Т и третьего 16 элементов ИЛИ, пятый выход - с третьим входом первого элемента ИЛИ 1, шестой выход - с оторым управляющим входом опрашивающего коммутатора 3, седьмой выход - с третьим управляющим входом опрашивающего коммутатора 3 и сбрасывающими входами активизирующего 8 и опрашивающего 10 счетчиков,

Опрашивающий коммутатор 3 (фиг.2) содержит дешифратор 17 с п выходами, первый вход которого является первым управляющим входом опрашивающего коммутатора 3. В состав опрашивающего коммутатора 3 входят также ключи 18.1,,..,18.п, триггера 19.1,...,19.п. диоды 20.1,...,20.п, при этом выходы дешифратора 17 соединены с первыми входами соответствующих триггеров 19 и анодами соответствующих диодов 20. Вторые входы триггеров 19 соединены с третьим управляющим входом опрашивающего коммутатора 3- Второй управляющий вход опрашивающего коммутатора 3 соединен с управляющими входами

триггеров 19 и дешифратора 17. Выходы триггеров 19 соединены с катодами соответствующих диодов 20 и управляющими входами соответствующих ключей 18, информационные входы

которых соединены с информационным входом опрашивающего коммутатора 3. Выходы ключей 18 подключены к соответствующим выходам опрашивающего коммутатора 3.

0 Активизирующий коммутатор 2 может быть реализован, например, на мультиплексорах 561КП1} активизирующий 8 и опрашивающий 10 счетчики могут быть реализованы на счетчиках 155ИЕ7,

5 блок 9 памяти может быть реализован на микросхемах серии 537, в качестве элементов ИЛИ И, 15, 16 могут использоваться микросхемы 155ЛЛ1, дешифратор 13 команд и дешифратор 17

0 могут реализоваться на микросхемах 561КП1 или 561ИД1, в качестве регистра 12-адреса может использоваться регистр 155ИР1 , в качестве блока. 11 управления может использоваться

5 любая персональная ЭВМ, например ДВК-ЗН.. В качестве триггеров 19 могут использоваться триггера 561ТР2, в качестве ключей 18 могут использоваться ключи 561КТЗ. Анализа0 тор 7 может быть реализован, например, на микросхеме 1 40УД7, источник 5 тестирующего напряжения - на микросхеме .

Рассмотрим работу устройства для

5 контроля соединений в электрическом монтаже в режиме автопрограммирования (алгоритм приведен на фиг. 3). В исходном состоянии блок 9 памяти обнулен. Блок 11 управления вы0 Дает по информационному выходу код начальной установки, который импульсом с управляющего выхода блока 11 управления записывается в регистр 12 адреса. По этому коду дешифратор 13

5 команд формирует команду сброса, которая с седьмого выхода дешифратора 13 команд поступает на сбрасывающие входы активизирующего 8 и опрашивающего 10 счетчиков, устанавливая их в

нулевое состояние, и на третиг управляющий вход опрашивающего коммутатора 3, устанавливая триггера 19 в единичное состояние. Так как на втором управляющем входе опрашивающего коммутатора 3 сигнал разрешения отсутствует, то выходы триггеров 19 находятся в высокоимпеданс- ном состоянии и не влияют на сигналы, проходящие с дешифратора 17 через диоды 20 на ключи 18. Во внут ренней памяти блока 11 управления выделены ячейки п - номер активизируемого контакта объекта контроля m - номер опрашиваемого контакта объекта контроля, 0 - количество контактов в объекте контроля. При выполнении начальной установки ячейки п и m обнуляются. После сброса содержимое ячеек пит увеличивается на единицу (блок 3 алгоритма) и происходит сравнение содержимого

.ячеек п и Q. (блок k алгоритма). При их неравенстве блок 11 управления через регистр 12 адреса и дешифратор 13 команд формирует команду Вход (второй выход дешифратора 13 команд), по которой в активизирующий 8 и опрашивающий 10 счетчики переписывается содержимое ячейки п (единица) блока 11 управления (блок

5алгоритма), На адресном входе блока 9 памяти устанавливается код первой ячейки памяти. Блок 11 управления через регистр 12 адреса и дешифратор 13 команд (пятый выход) формирует команду анализа активизируемой точки, по которой в блок 11 управления переписывается содержимое n-ой ячейки блока 9 памяти (блок

6алгоритма). Так как в исходном состоянии первая ячейка блока 9 памяти была нулевой, блок 11 управления через регистр 12 адреса и дешифратор 13 команд (шестой выход) формирует команду включения режима общего опроса (блоки 7, 8 алгоритма). Так как в опрашивающем счетчике 10 записана единица, то сигнал с первого выхода дешифратора 17 установил триггер 19.1 в нулевое состояние. Команд включения режима общего опроса, поступив на второй управляющий вход опрашивающего Коммутатора 3, переведет выходы дешифратора 17 в высокоимпе- дансное состояние и снимет запрет с выходов триггеров 19, Так как к этому моменту триггер 19.1 находится в

10

15

0

5

0

5

0

5

0

5

нулевом, а триггера 19.2,...,19.п единичном состоянии, то откроются ключи 18.2,.,.,18.п, Таким образом, все точки объекта контроля, кроме первой, окажутся подключенными к клемме Общий вывод и второму выводу источника 5 тестирующего напряжения. Так как в активизирующем счетчике 8 записана единица, то первая точка объекта контроля, соединенная с первым выходом активизирующего коммутатора 2, через его информационный вход подключится к информационному входу анализатора 7 и через резистор 6 к первому выводу источника 5 тестирующего напряжения. Если в объекте контроля первая точка 1.1 связана с какой-либо другом, то она также окажется подключенной к клемме.Общий вывод ), а, следовательно, и на информационном входе анализатора 7 установится низкий уровень сигнала, что вызовет появление сигнала на выходе анализатора 7, свидетельствующего о наличии связи в объекте контроля. Признак связи с выхода анализатора 7, поступив на управляющий вход блока 11 управления, вызовет выключение режима общего опроса, содержимое ячейки m блока 11 управления увеличится на единицу и через регистр 12 адреса и дешифратор 13 команд (третий выход) вырабатывается сигнал Опрос (блоки 9, 11, 12, 13 алго- ритма), которым содержимое опрашивающего счетчика 10 через третий элемент ИЛИ 16 увеличивается на единицу, Вследствие этого появляется сигнал на втором выходе дешифратора 17. Этот сигнал переведет триггер 192 в нулевое состояние и через диод 20.2 откроет ключ 18.2, подключив к клемме Общим вывод вторую точку объекта контроля 1.2. Сигнал Опрос через первый элемент ИЛИ 1 поступит на второй управляющий вход блока 9 памяти, разрешив его работу в режиме обмена информацией. Если в объекте контроля точки 1.1 и 1.2 связаны между собой, то на входе анализатора 7 установится низкий уровень сигнала, а на выходе анализатора 7 вырабатывается признак связи, который поступает на управляющий вход блока 11 управления и на первый управляющий вход блока 9 памяти, где осущест11

вляется запись единицы (состояние активизирующего счетчика 8) во вторую (состояние опрашивающего счетчика 10) ячейкуt Эта запись означает связь первой и второй точек объекта контроля. При отсутствии связи блок 11 управления осуществляет сравнение ячеек m и 0 (блоки 1, 15 алгоритма) . В случае неравенства содержимого ячеек m и Q, содержимое ячейки т увеличивается на единицу и блоком 11 управления через регистр 12 адреса и дешифратор 13 команд вырабатывается очередная команда Опрос. При равенстве содержимого ячеек m и Q увеличивается на единицу содержимое ячейки п и вырабатывается очередная команда Вход (блок 3 алгоритма) , т.е. осуществляется активизация очередной точки объекта контроля. При поступлении признака связи блок 11 управления через регистр 12 адреса и дешифратор 13 команд (шестой выход) вырабатывает команду включения режима общего опроса (блоки , 16 алгоритма). В опрашивающем коммутаторе 3 к ключам 18 подключатся выходы триггеров 19 и отключатся выходы дешифратора 17. Так как к этому моменту триггера 19.1 и 19.2 обнулены, то откроются ключи 18.3,...i18,п, т.е. будет производиться одновременный опрос 3,...,п точек объекта контроля. Блок 11 управления проанализирует выход анализатора 7 (блок 17 алгоритма) и, в зависимости от вида выходного сигнала анализатора 7, перейдет к опросу очередной точки объекта контроля или к активизации очередной точки объекта контроля (блоки 18, 19, 20 алгоритма). Если в объекте контроля точки 1.1 и 1.2 соединены между собой, то во вторую ячейку блока 9 памяти была записана единица. При активизации точки 1.2 объекта контроля в результате опроса второй ячейки блока 9 памяти и анализа ее содержимого блок 11 управления без опроса других точек объекта.контроля перейдет к активизации очередной точки (блоки 6,7,3алгоритма) .При обра- (зовании в п ячейке блока 9 памяти числа, равного О, блок 11 управления через регистр 12 адреса и дешифратор 13 команд выработает команду сброса (седьмой выход дешифратора 13 команд) , в результате выполнения кото10

15

20

25

175860612

рой обнуляется активизирующий Ј и опрашивающий 10 счетчики, и О команд опроса памяти (четвертый выход дешифратора 13 команд). Эти команды, поступая через третий элемент ИЛИ 16 на счетный вход опрашивающего счётчика 10, осуществляют адресацию блока 9 памяти, и, поступая через первый элемент ИЛИ 14 на второй управляющий вход блока 9 памяти, осуществляют перепись содержимого блока 9 памяти в блок 11 управления, который в результате обработки введенной информации формирует таблицу соединений объекта контроля (блоки Ц, 21, 22, 23 алгоритма).

Рассмотрим работу устройства для контроля соединений в электрическом монтаже в режиме годен-брак (алгоритм приведен на фиг,4). Этот режим предусматривает наличие в памяти блока 11 управления информации, соответствующей таблице соединений эталонного объекта контроля, Работа начинается с выполнения начальной установки в порядке, описанном выше. После обнуления блок 11 управления через регистр 12 адреса и дешифг ратор 13 команд (второй выход) сигналом Вход записывает в активизирующий счетчик 8 номер первой точки проверяемой цепи объекта контроля, затем сигналом Выход (первый выход дешифратора 13 команд) через второй элемент ИЛИ 15 в опрашивающий счетчик 10 записывается номер второй точки проверяемой цепи объекта контроля (блоки 2, 3, 4 алгоритма). При наличии связи в объекте контроля между заданными точками анализатор 7 выработает признак связи. Получив по управляющему входу признак 11 управления выдает в опрашивающий счетчик 10 номер следующей точки проверяемой цепи (блоки 5, 8, k алгоритма). При отсутствии признака связи блок 11 управления зафиксирует неисправность и в зависимости от указаний оператора либо завершит работу, либо запишет в опрашивающий счетчик 10 номер следующей точки проверяемой цепи (блоки 5, 6, 7, 8, 4 алгоритма) , После опроса последней точки опрашиваемой Цепи блок 11 управления через регистр 12 адреса и дешифратор 13 команд выдает команду включения режима общего опроса. К этом

30

35

40

45

50

55

моменту в опрашивающем коммутаторе 3 обнулены триггера 19, соответствующие точкам, опрос которых уже произведен. Таким образом, при поступлении команды общего опроса произойдет одновременный опрос всех неопрошенных точек относительно первой точки проверяемой цепи (блоки 8, 9 алгоритма). Если анализатор 7 в этом случае не выработает признака связи, то блок 11 управления выдаст команду активизации первой точки следующей цепи объекта контроля (блоки 10, 13, 1, 3 алгоритма). Если анализатор 7 выдаст признак связи, что означает связь первой цепи с какой-либ из точек, не принадлежащих этой цепи, блок 11 управления зафиксирует факт брака контролируемого объекта и в зависимости от указаний оператора, либо завершит работу, либо перейдет к контролю следующей цепи (блоки 10, 11, 12, 13, 1, 3 алгоритма). Работ заканчивается после проверки последней цепи объекта контроля (блоки 1, 15 алгоритма). Локализация неисправностей производится выполнением режима автопрограммирования.

Таким образом, реализация опрашивающего коммутатора 3 в предложенном виде обеспечивает возможность оперативного обнаружения обособленных точек и концов цепей в объекте контроля, что позволяет минимизировать количество измерений, сокращая тем самым время контроля. Введение регистра 12 адреса, дешифратора .13 команд, элементов ИЛИ И, 15, 16 в вышеуказанных связях с остальными элементами обеспечивает возможность немедленного переключения активизируемых и опрашиваемых точек объекта контроля при обнаружении обособленных точек или концов цепей в режиме автопрограммирования. В режиме годен-брак реализация опрашивающего коммутатора 3 в предложенном виде обеспечивает возможность выполнения контроля за минимально возможное время,

По сравнению с прототипом преимуществом заявляемого устройства для контроля соединений в электрическом монтаже является сокращение времени контроля, обусловленное ускоренным выявлением обособленных точек объекта контроля с последующим исключением их из дальнейшего процесса контроля

10

15

20

25

30

5

0

5

0

5

и локализацией концов цепей в объекте контроля методом параллельного опроса неопрошенных точек. Использование этого метода позволяет реализовать кроме режима автопрограммирования и ускоренный режим годен-брак, что также обеспечивает сокращение времени контроля.

Формула изобретения

Устройство для контроля соединений в электрическом монтаже, содер- жащее п клемм для подключения объекта контроля, где п - число элементов объекта контроля, активизирующий и опрашивающий коммутаторы, активизирующий и опрашивающий счетчики, источник тестирующего напряжения, резистор, анализатор, блок памяти,клемму Общий вывод, блок управления, при этом каждая из п клемм для подключения объекта контроля соединена с соответствующими выходами активизирующего и опрашивающего коммутаторов, информационный вход опрашивающего коммутатора подключен к клемме Общий вывод и второму выводу источника тестирующего напряжения, первый вывод которого через резистор подключен к информационным входам анализатора и активизирующего коммутатора, управляющий вход которого соединен с выходом активизирующего счетчика и информационным входом блока памяти, первый управляющий вход опрашивающего коммутатора соединен с выходом опрашивающего счетчика, выход анализатора соединен с первым управляющим входом блока памяти, о т- личающееся тем, что, с целью сокращения времени контроля, в устройство введены первый, второй и третий элементы ИЛИ, дешифратор команд, регистр адреса, при этом выход опрашивающего счетчика соединен с адресным входом блока памяти, второй управляющий вход которого подключен к выходу первого элемента ИЛИ, а выход - к информационному входу блока управления, информационный выход которого соединен с информационными входами регистра адреса, активизирующего и опрашивающего счетчиков, выход анализатора подключен к управляющему входу блока управления, управляющий выход которого подключен к управляющему входу регистра адреса, выход которого подключен к входу дешифратора команд, первый выход которого соединен с первым входом второго элемента ИЛИ, второй выход - с вторым входом второго элемента ИЛИ и управляющим входом активизирующего счетчика, третий выход - с первым входом первого элемента ИЛИ и первым входом третьего элемента ИЛИ, четвертый выход - с вторыми входами первого и третьего элементов ИЛИ, пятый выход - с третьим входом первого элемента ИЛИ, шестой выход - с вторым управляющим входом опрашивающего коммутатора, седьмой выход - с третьим управляющим входом опрашивающего коммутатора и сбрасывающими входами активизирующего и опрашивающего счетчиков, выход второго элемента ИЛИ соединен с управляющим входом опрашивающего счетчика, выход третьего элемента ИЛИ соединен со счетным входом опрашивающего счетчика, при этом опрашивающий комму

5

0

25

та тор содержит дешифратор с п выходами, п триггеров, п диодов, п ключей, первым управляющим входом опрашивающего коммутатора является первый вход дешифратора, выходы которого соединены с первыми входами соответствующих триггеров и анодами соответствующих диодов, третьим управляющим входом опрашивающего коммутатора являются соединенные между собой вторые входы триггеров, вторым управляющим входом опрашивающего коммутатора являются соединенные между собой управляющие входы триггеров и дешифратора, выходы триггеров соединены с катодами соответствующих диодов и управляющими входами соответствующих ключей, информационные входы ключей соединены с информационным входом опрашивающего коммутатора, а выходы ключей являются соответствующими выходами опрашивающего коммутатора .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля соединений в электрическом монтаже | 1989 |

|

SU1698842A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| Устройство для управления распределенным объектом | 1986 |

|

SU1363144A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1564693A1 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

| Многоканальное устройство для автоматического контроля микропроцессоров | 1982 |

|

SU1104519A1 |

| Устройство для тестового контроля цифровых узлов | 1980 |

|

SU918949A1 |

Использование: изобретение относится к контрольно-измерительной технике и может быть использовано для контроля монтажных соединений при производстве электронной и электротехнической аппаратуры. Сущность изобретения: устройство содержит п клемм для подключения объекта контроля (1,1-1.п), активизирующий и опрашивающий коммутаторы (2, 3), клемму (4) Общий вывод, источник тестирующего напряжения (5), резистор (6) , анализатор 7, активизирующий счетчик (8), блок памяти (9), опрашивающий счетчик (10), блок управления (11), 1 регистр адреса

Фи J

От fob

F

ш/ . ..п

А ff.f -iА

На блоке, кяеммы{

ЈfH

От От fy.f3 fort

Редактор И.Сегляник

Составитель В,,°еленский Техред М.Моргентал

ФигА

Корректор П.Гереши

| Способ обнаружения обрывов и коротких замыканий в электрическом монтаже | 1984 |

|

SU1273848A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-08-30—Публикация

1990-08-23—Подача