Изобретение относится к вычислительной технике и предназначено для контроля и регулирования параметров,

Целью изобретения является расширение области применения путем обеспечения возможности оперативного введения корекций уставок непосредственно в процессе эксплуатации устройства ,

В устройстве имеются дополнительные блоки оперативной памяти, предназначенные для хранения и введения поправок к основным уставкам. Реальные уставки параметров получаются в результате суммирования (вычитания) основных уставок и поправок к ним (коррекций), причем введение коррекций осуществляется непосредственно в процессе контроля и регулирования в тех тактах, когда оперативная память не работает на выдачу информации. Возможность оперативного и не- .однократного введения коррекций к уставкам, которое может выполняться оператором-технологом сразу после из менения условий производства, позволяет расширить область применения устр ойства.

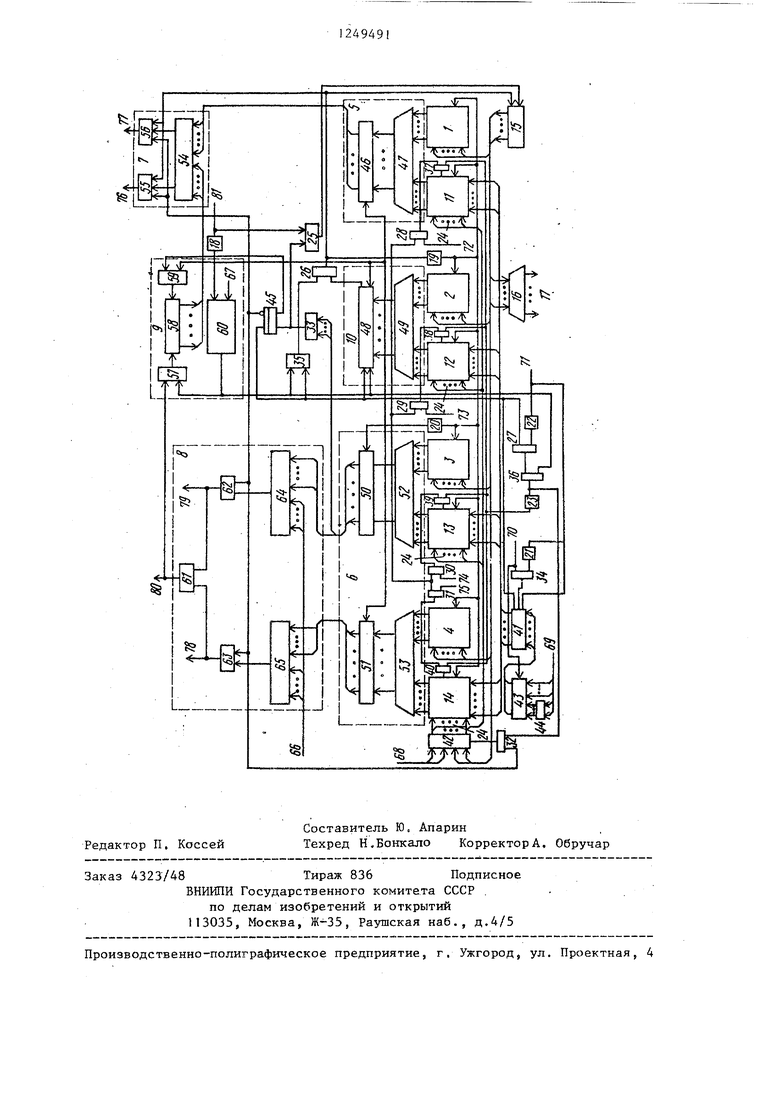

На чертеже предста1влена структурная схема устройства для контроля и регулирования параметров.

В состав устройства входят четыре блока.1-4 постоянной памяти, два формирователя 5 и 6 допуска, два блока 7 и 8 сравнения, блок 9 измерения времени и блок 1.0 формирования интервала измерения. Устройство содержит также четыре блока 11-14 оперативной памяти, счетчик 15 адреса, дешифратор 16, подключенный своими выходами к адресным выходам 17 устройства, шесть элементов 18-23 задержки адре сные входы 24 блока 11-14, семь элементов 25-31 ИЛИ, девять элементов 32-40 И, регистр 41 коррекции, два . коммутатора 42 и 43, группу 44 элементов НЕ и триггер 45,

Первый формирователь 5 допуска выполнен в виде первого регистра 46 и первого сумматора 47, Блок 10 формирования интервала измерения вьшолнен в виде второго регистра 48 и второго сумматора 49. Второй формирователь допуска вьшолнен в виде третьего 50 и четвертого 51 регистров и третьего 52 и четвертого 53 сумматоров. Первый блок 7 сравнения вьтолнен в виде первой схемы 54

сравнения и двух элементов 55 и 56 И. Блок 9 измерения времени выполнен в виде элемента 57 И, счетчика 58 времени, элемента 59 ИЛИ и генератора 60 импульсов. Второй блок 8 сравнения вьтолнен в виде элемента 61 ИЛИ, двух элементов 62 и 63 И и второй 64 и третьей 65 схем сравне- нения. Регистр 50 и триггер 45 выполнены со сбросом по включе 1ию питания .

Устройство имеет также входы 66 кода параметра, вход 67 останова устройства, входы 68 адреса коррекций, входы 69 кода коррекции, вход 70 знака коррекции, вход 71 ввода коррекции, входы 72-75 типа уставки, управляющие выходы 76 - 80, и вход 81 запуска устройства.

Входы 66 кода параметра подключаются к соответствующим различным параметрам цифровым датчикам либо к общему для всех параметров аналого- цифровому преобразователю, вход которого соединяется с аналоговыми датчиками. Выбор параметра осуществляется с помощью дешифратора 16, унитарный выходной код которого, посту- пающий на адресные выходы 17, определяет подключающийся ко входам 66 датчик. Управляющие выходы 76 и 77 служат для управления объектом и ин- рассогласования и соединяются с сигнальными лампочками или

другими индикаторами (если используется режим контроля). Тогда срабатывание индикатора на выходе 77 означает, что контролируемый .объект годен по выбранному параметру (параметр в пределах нормы). Срабатьшание индикатора на выходе 76 говорит, что параметр за пределами нормы (негоден) , В режиме регулирования значе.- ния параметра управляющие выходы 76

и 77 соединяются с исполнительными механизмами инверсного действия по каждому параметру (например, с уп- равляющими обмотками реверсивного

шагового двигателя). Выбор исполни- тельного механизма осуществляется также с помощью адресных выходов 17. Если объект контроля и регулирования таков, что для оценки значения параметра достаточно его проверки, в произвольный единичный момент времени ()Допуск по времени на параметр не требуется), то вместо выходов 76 и 77 в режиме регулирования использу3

ются управляющие выходы 78 и 79.

В режиме контроля индикатор подключается к выходу 80 и еро включенное состояние информирует о том, что параметр находится за пределами допу ска по значению. Входы 68 адреса кор рекции, вход 69 кода коррекции и вход 70 знака коррекции подключаются к тумблерам (или к кнопкам с фиксацией) на пульте управления и индикации. Вход 71 ввода коррекции, входы 81 запуска и вход 67 останова устрой ства также соединяются с кнопками на пульте устройства.

Устройство работает следующим образом.

В блоках 1-4 постоянной памяти хранится информация, соответствующая номинальным значениям .уставок: в бло ке 1 - допуски по времени (максималь но допустимое время нахождения параметра за пределами допуска по величи не), в блоке 2 - величины интервалов времени, необходимого для получения. достоверных значений параметров, в блоке 3 - нижние допустимые значения параметро.в, в блоке А - верхние. В последнюю используемую ячейку блока 3 памяти заносится код 1 ,...., I - признак, конца цикла.

После включения устройства производится обнуление всех ячеек блоков 11-14 оперативной памяти, т.е. все коррекции устанавливаются равными нулю. Это выполняется следующим образом.

В первом такте на вход 81- запуска устройства поступает сигнал, который пройдя через третий элемент 25 ИЛИ, устанавливает в О счетчик 15 адреса. Этот же сигнал, пройдя через пер вьш элемент 18 задержки, поступает на установку в 1 триггера 45, устанавливая его в единичн.ое состояние запускает генератор 60 импульсов и, пройдя через второй элемент 59 ИЛИ, устанавливает в О счетчик 58 времени .

с

Во втором такте импульс с выхода генератора 60, пройдя через восьмой элемент 35 И, на втором входе которого присутствует высокий уровень напряжения с единичного выхода.триггера 45, и через девятый элемент 26 ИЛИ, поступает на счетный вход счетчика 15 адреса и увеличивает его значение на единицу. Сигнал с еди

494914

минного выхода триггера 45 также поступает на вход обнуления регистра 41 коррекции. Нулевой код, записанный в счетчике 15 адреса в предьщу- 5 -щем такте, проходит на выход второго коммутатора 42, так как на его управляющем входе присутствует низкий уровень напряжения, поскольку на одном . из входов седьмого элемента 32 И - логический О с нулевого выхода триггера 45. До поступления сигнала записи на блоки 11-14 оперативной памяти на их адресные входы подается код сформировавшегося в рассматри- 5 ваемом такте значения на регистре 15 адреса. В этом же такте второй регистр 48 устанавливается в нулевое состояние сигналом с единичного выхода триггера 45.

20 в третьем такте на входы записи

блоков 11-14 оперативной памяти подается сигнал, прошедший с выхода генератора 60 импульсов через один из входов четырнадцатого элемента 36 И, на Другом входе которого присутствует логическая 1 с выхода вось- мого элемента 27 ИЛИ, подключенного одним из входов к единичному выходу триггера 45, через шестой элемент 30 23 задержки и через один, из входов с десятого по тринадцатый элементов И, на других входах которых, присутствуют логические 1 q выходов с четвертого по седьмой элемен- 35 тов 28-31 ИЛИ, подключенных одним

из входов- к единичному выходу триггера 45, В этом же такте выполняется запись нулевого кода с выхода регистра 41 коррекции в блоки 11-14 опера- 40 тивной памяти по адресу, установленному на выходах второго коммутатора 42.

В четвертом такте импульс, сформированный во втором такте на выхо45 де девятого элемен-Ра 26 ИЛИ, появляется на выходе четвертого элемента 19 задержки и на входах считывания блоков I-4 и 11-14. Выполняется счи- тьшание информации из всех блоков

50 памяти. Выходные коды уставок блоков 1-4 постоянной памяти суммируются с кодами коррекции блоков.11-14 оперативной памяти I в частном случае - с нулевыми) в сумматорах 47, 49, 52

55 и 53.

В пятом такте сигнал, поступивший в предыдущем такте на входы считывания блоков памяти, пройдя через пяый элемент 20 .задержки, поступает на управляющие входы регистров 46, 48, 50 и 51. После этого результат , суммирования с выходов сумматоров 47 з 52 и 53 записьшается в регистры 46, 50. и 51 соответственно.- Регистр 48 оста ется в нулевом состоянии, так как он заблокирован сигналом на входе обнуления, поступающем с единичного 10 выхода триггера 45.

Такты со второго по пятый повторяются до тех пор, пока на выходах регистра 50 появится код I,...,I, Тогда устройство переходит ко второ- 15 му такту работы, В рассмотренных тактах управляющие выходы 76-80 заблокированы НИЗКИМ уровнем напряжения с нулевого вьЕхода триггера 45.

В шестом такте сигнал с шестого 20 элемента 33 И, на вход которого поступил код Г1 , устанавливает триггер 45 в нулевое состояние и, пройдя через третий элемент 25 ИЛИ, устанавливает счетчик 5 адреса также в 35 нулевое состояние.

.В седьмом такте передний фронт импульса с генератора 60 поступает на вход вычитания регистра 48, в котором хранится нулевой код, изменяет 30 его значение на ,...,I и приводит к появлению сигнала на выходе перемножения, регистра. Данный, сигнал, пройдя через девятый элемент 26 ИЛИ, .поступает на счетный вход счетчика 1.5 35 адреса и увеличивает его содержимое на единицу. Таким образом, на адресных входах блоков 1 - 4 постоянной памяти адрес уставок сформирован.

В восьмом такте на адресных выхо- 40 дах I7 устройства появляется унитарный код, определяющийся подключающийся к входам 66 кода параметра датчик. В этом же такте код адреса контролируемого параметра (адрес коррекции) 45 с выхода счетчика 5 адреса появляется на выходах второго коммутатора 42, так как на одном из входов седьмого элемента 32 И присутствует логическая 1 с единичного выхода триггера 50 45, а на другом - логический О с выхода четырнадцатого элемента 36 И.

В девятом такте устройство функционирует точно так же, как и в четвертом.55

В десятом такте устройство работает аналогично пятому такту, но с выхода второго сумматора 49 информация

принимается во второй регистр 48, вход обнуления которого теперь не заблокирован сигналом с единичного выхода триггера 45.

В одиннадцатом такте одновременно с появлением уставок на нижнее и- верхнее допустимые значения параметр на выходах регистров 50 и 51 соот- ве.тственно,на входы 66 кода параметра поступает р еальное значение параметр Одновременно устанавливается в О счетчик 58 времени сигналом с выхода второго элемента 59 ИЛИ и на управля ющие выходы 78-80 поступает результат сравнения со второй и третьей схем 64 и 65 сравнения. На выходе второй схемы 64 сравнения появляется сигнал, если код параметра меньше, кода нижней границы допуска по з.на- чению. На выходе третьей схемы 65 сравнения сигнал появляется в том случае, если значение параметра больше верхней траницы допуска по значению.

В следующем двенадцатом такте значение интервала изменения параметра, хранящееся во втором регистре 48, уменьшается на единицу очередным сигналом на входе вычитания регистра 48. Этим же сигналом, проходящим через ПЯТЫЙ элемент 57 И, увеличивается значение кода в счетчике 58 времени (время нахождения параметра за пределами допускаj, если на выходе первого элемента 61 ИЛИ - логическая 1. В противном случае содержимое счетчика 58 времени не изменяется.

Двенадцатый такт повторяется до тех пор, пока н.а выходе переполнения второго регистра 48 не появится сигнал. Тогда устройство переходит к

тринадцатому такту. I

В тринадцатом такте работа уст ройства аналогична седьмому такту с тем отличием, что сигнал переполнения, пройдя через девятый элемент 26 ИЛИ, открывает-первый и второй элементы 55 и 56 И. Если значение реального времени нахождения параметра за пределами допуска, определяемого кодом счетчика 58 времени, больще допустимого времени, определяемого кодом первого, регистра 46, то сигналпоявляется на выходе 76, в противном случае - на выходе 77.

На этом обработка очередного параметра заканчивается и устройство

приступает к обработке следующего, начиная с восьмого такта.

Такты с восьмого по тринадцатый повторяются до тех пор, пока в оче- . редном десятом такте не появится код

I,. , , ,-1 в третьем регистре 50 и О,,.,,О во. втором регистре 48, Это соответствует адресу, для которого содержимое ячеек блоков памяти явля- tO ется вспомогательным, ему, так же

как и адресу О,.,.,О, не соответствует ни .один из параметров. Затем устройство переходит к шестому- такту работы и цикл обработки параметров 15 овторяется, процесс, контроля и регулирования параметров прекращается при появлении сигна ла на входе 67 останова устройства.

о-« 20

Запись значении коррекции в блоки

II- 14 оперативной памяти произво- дится непосредственно в процессе работы устройства следующим образом.

Eia входах 68 адреса коррекции ус 5 танавливается адрес корректируемого параметра, на входах 69 - код коррекции, на входе 70 - знак коррекции (единица соответствует отрицательному

знаку). На один из входов 72-75 типа .

/30

уставки (В частном случае - на несколько подается высокий уровень напряжения для выбора типа корректируемой уставки. После этого подается сигнал на управляющий вход 7I ввода коррекции. По этому сигналу в регистр 41 коррекции принимается прямое или инвертированное на группе элементов 44 НЕ значение коррекции со входов

69. В случае отрицательного знака

40

коррекции на управляющем входе первого коммутатора 43 - логическая 1, и на его выходе присутствует инвертированное значение кода коррекции. После приема информации в регистр 41

45

коррекции на его счетном входе (ее

ли знак коррекции отрицательный) появляется сигнал с выхода девятого элемента 34 И, один вход которого открыт логической единицей со входа 70 знака коррекции, а другой - высо- КИМ уровнем напряжения с выхода третьего элемента 21 задержки. К моменту появления сигнала на счетном входе регистра коррекции на его управляющем входе уже присутствует ло

гический О, что определяется длительностью сигнала на входе 71 ввода коррекции. При увеличении обратного

tO

15 20

5

.

30

40

45

55

кода в регистре 41 коррекции на единицу в нем формируется дополнительный код коррекции, сложение которого с уставкой эквивалентно вычитанию прямого кода коррекции из уставки.

Запись коррекций в блоки 11-14 оперативной памяти выполняется в промежутках между считыванием ее из блоков 1 -4 и 1 1 -14 ,

Восьмой элемент 27 ИЛИ, выход которого соединен с одним из входов четырнадцатого элемента 36 И, открывается сигналом, прошедшим через второй элемент 22 задержки со входа 71 ввода коррекции. При поступлении на другой вход элемента 36 И переднего фронта сигнала с выхода генератора 60 импульсов на его выходе появляется логическая 1, открывающая седьмой элемент 32 И, на другом входе которого - высокий уровень напряжения с нулевого вьгхода - триггера 45. В результате этого на адресные входы ,блоков 11-Г4 оперативной памяти через второй коммутатор 42 проходит код со входов 68 адреса коррекции. В этот момент на входах записи тех блоков 11-14 оперативной памяти, на соответствующих которым входах 72-76 типа уставки присутствует единица, появляется сигнал записи, по которому код коррекции с выходов регистра 41 коррекции принимается в соот- ветс твующие ячейки блоков 11-14 оперативной памяти. Сигнал записи проходит через элементы 37-40 И с выхода четырнадцатого элемента 36 И через шестой элемент 23 задержки. При завершении записи коррекции на выходе второго коммутатора 42 появляется код из счетчика 15 адреса в результате закрытия седьмого элемента 32 И задним фронтом импульса с генератора 60 импульсов. запаздьшания сигнала на четвертом элементе 19 задержки таково, что до появления сигнала считывания на входах блоков i-4, 11-14 все действия, связанные с записью коррекции в блоки 11-14 оперативной памяти,успевают закончиться.

Аппаратурная реализации коррекции уставок в процессе контроля и регулирования параметров в данном устройстве позволяет уменьшить стоимость устройства и увеличить его быстродействие. Такое устройство является более простым в обслуживаНИИ и потому может эксплуатироваться менее квалифицированными специалис- Tai iHi

Формула изобретения

Устройство для контроля и регулирования параметров, содержащее последовательно соединенные с первого по четвертый блоки постоянной памяти, с первого по четвертый сумматоры и с первого по четвертый регистры, выходы первого регистра соединены с первыми входами дервой схемы, срав- нения, вторые входы которой соединены с выходами счетчика времени, а выходы-- с первыми входами первого и второго элементов И, выходы третьего и четвертого регистров подключе- ны к первым входам второй и третьей схем сравнения соответственно, вторые входы которых объединены между собой и являются входами кода параметра устройства, а выходы соедине- ны с первьп- 1и входами третьего и четвертого элементов И соответственно первый элемент ИЛИ, входы которого соединены с выходами третьего и четт- вертого элементов И, а вькрд - через пятый элемент И со счетным йтсодом . счетчика времени, вход обнуления которого подключен к выходу второго элемента ИЛИ, генератор импульсов.; вход запуска, которого через первый элемент задержки соединен с входом пуска устройства, а вход останова является входом останова устройства, счетчик адреса, соединенный выходами с адресными входами блоков постоян- ной памяти и входами дешифратора, выходы которого являются адресными вы; одами устройства, отличающееся тем,, что, с целью расширения области применения путем обеспе- чения возможности оперативного введения коррекций уставок в процессе эксплуатации, в него введены с первого по четвертый блоки оперативной памя- ти, регистр коррекции, первый и вто- рой коммутаторы, со второго по шестой элементы задержки, с третьего по девятый элементы ИЛИ и с шестого по четырнадцатый элементы И, группа элементов НЕ и триггер, вход установки единицу которого соединен с выходом первого элемента задержки и с первым входом второго элемента ИЛИ, а вход

установки в нуль - с выходом шестого элемента И и первым входом третьего элемента ИЛИ, нулевой выход триггера подключен к вторым входам первого, второго, третьего, четвертого и седьмого элементов И, единичный-выход триггера соединен с первыми входами восьмого элемента И, с четвертого по восьмой элементов Р ЛИ и с входами обнуления второго регистра и регистра коррекции, счетный . вход которого соединен с выходом девятого элемента И, управляющий вход - с входами второго и третьего элементов задержки и с входом ввода коррекции устройства, информационные входы регистра коррекции соединены с выходами первого коммутатора, а выходы - с информационными входами блоков оперативной памяти, адресные входы которых подключены к выходам второго коммутатора, а входы считьшания объединены с входами считьшания блоков постоянной памяти и подключены к выходу-четвертог и входу пятого элементов задержки, входы записи первого, второго, третьего и че твертого блоков оперативной памяти соединены с выходами десятого одиннадцатого 5 двенадцатого и тринадцатого элементов И соответственно, выходы.с первого по четвертый блоков оперативной памяти подключены к вторым входам с первого по четвертый сумматоров J первые входы второго коммутатора соединены с выходами счетчика адреса, вторые входы являются входами адреса коррекции устройства, а управляющий вход второго коммутатора соединен с выходом седьмого элемента И, второй вход которого соединен с вьпсодом четырнадцатого элемента И и с входом шестого элемента задержки, выход шестого элемента задержки подключен к первым входам с десятого по четырнадцатый элементов И, вторые входы которых соединены с выходами седьмого, шестого, пятого и четвертого элементов ИЛИ соответственно, вторые входы с четвертого по седьмой элементов-ИЛИ являются входами типа уставки устройства, первый вход четырнадцатого элемента И объединен с вторыми входами пятого и восьмого элемента И, с вычитающим входом второго регистра и подключен к выходу генератора импульсов, второй вход четырнадца-

того элемента И подключен к выходу восьмого элемента ИЛИ, второй вход которого соединен с выходом второго элемента задержки, первый вход девятого элемента ИЛИ подключен к выходу восьмого элемента И, второй вход - к выходу переполнения второго регистра, а выход - к третьему входам первого и второго элементов И, к входу четвертого элемента задержки и к счетному входу счетчика адреса, вход обнуления которого подклю чей к выходу третьего элемента ИЛИ, соединенного вторым входом с входом пуска устройства, управляющие входы с первого по четвертый регистров объединены с вторым входом второго элемента ИЛИ иподключены к выходу пятого элемента задержки, выходы третьего регистра соединены с входами шестого -элемента И, входы к ода коррекции устройства соединены с., первыми входами первого коммутатора и через группу элементов НЕ - с вторыми входами первого коммутатора,

управляющий вход которого соединен с первым входом девятого элемента И и с входом знака коррекции устройства, второй вход девятого элемента И соединен с выходом третьего элемента задержки, выходы первого и второго элементов И и первого элемента ИЛИ являются управляющими выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ | 1984 |

|

SU1840542A2 |

| Устройство для контроля параметров | 1989 |

|

SU1667009A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1423982A1 |

| Устройство допускового контроля параметров | 1991 |

|

SU1800380A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

| ЦИФРОВОЕ ЧЕТЫРЕХКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2017 |

|

RU2659990C1 |

| Устройство для формирования признаков распознаваемых образов | 1986 |

|

SU1328830A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

Изобретение относится к вычислительной технике и предназначено для контроля и регулирования параметров. Решается задача расширения области применения устройства путем обеспечения возможности коррекции уставок непосредственно в процессе эксплуатации. В четырех блоках постоянной памяти хранится информация, соответствующая номинальным значениям уставок. Устройство имеет входы кода параметров, вход останова, вход адреса коррекций, вход кода коррекции, вход знака коррекции, вход ввода коррекции, вход типа уставки, управляющие входы и вход запуска. Выбор параметра производится с помощью дешифратора. После включения устройств.а производится обнуление всех ячеек четырех блоков оперативной памяти с помощью счетчика адреса, первого элемента задержки, триггера и блока измерения времени. Работа устройства разбивается на тринадцать тактов. В первом такте запускается генератор, импульсов и устанавливается счетчик времени. Во втором такте на адресные входы блоков оперативной памяти подается код из регистра адреса, а второй регистр устанавливается в нулевое состояние. В третьем такте вьтолняется запись нулевого кода с выхода регистра коррекции в блоки оперативной памяти по адресу с выходов второго коммутатора. В четвертом такте выходные коды уставок блоков постоянной памяти суммируются с кодами коррекции блоков оперативной памяти. В пятом такте результат суммирования с вьгходов сумматоров записываются в регистры формирователей допуска. В шестом такте счетчик адреса устанавливается в нулевое состояние. В седьмом такте на адресных входах блоков постоянной памяти формируется адрес уставок. В восьмом такте код адреса контролируемого параметра появляется: на выходах второго коммутатора. Девятый такт аналогичен четвертому. Десятый такт аналогичен пятому. В одиннадцатом такте на выходах третьего и четвертого регистров второго формирователя появляются уставки нижнего и верхнего допустимых значений параметра. В двенадцатом такте уменьшается на единицу значение интервала изменения параметра, хранящееся во. втором регистре блока формирования интервала времени-. Тринадцатый такт аналогичен седьмому. Запись коррекций в блоки оперативной памяти выполняется в промежутках между считыванием информации из блоков постоянной памяти . 1 ил. (О (Л to 4

Редактор П. Коссей

Составитель Ю. Апарин

Техред Н.Бонкало Корректор А, Обручар

Заказ 4323/48Тираж 836 Подписное

ВНИИПИ Государственного комитета СССР .

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Устройство для допускового контроляОб'ЕКТА | 1979 |

|

SU834678A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля параметров | 1976 |

|

SU605470A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-08-07—Публикация

1984-09-24—Подача