(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МОНТАЖНЫХ СХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля монтажных схем | 1980 |

|

SU920747A1 |

| Устройство для контроля монтажных схем | 1981 |

|

SU1018062A1 |

| Устройство для контроля электрического монтажа | 1980 |

|

SU938212A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для проверки монтажа релейных схем | 1978 |

|

SU744615A1 |

Изобретение относится к области автоматического контроля и может быть использовано для проверки монтажных схем радиоэлектронной аппаратуры. Известны устройства для проверки монтажа, содержащие комл утатор, соединенный с входами контролируемого элекгромонтажа входами блока программы, с блоком измв рений и одним полюсом источника питания Недостатками таких устройств являются большое время контроля, невозможность самопроверки, что снижает достоверность результатов контроля, невозможность автоматической регистрации адресов неисправносте монтажной схемы, сложность подготовки и смены программы проверки. Известно также устройство для проверки монтажа, содержащее блок ввода информации соединрплый с входами блока перфорации и блока предварительной обработки, два коммутатора, управляющие входы которых соединены с выходами соответствующих блоков управления, выходы коммутаторов соединены с входами блока анализа, выход которого соединен с первым входом блока печати 2. Недостатками этого устройства являются большое время проверки монтажных схем и низкая достоверность результатов контроля. Целью изобретения является повышение быстродействия и достоверности контроля. Это яостигаегся тем, что в устройство введены два блока оперативной памяти, блок распределения информации и узел фо{ мироваиия управляющего сигнала, выход которого соединен с входом второго коммутатора, а вход - с первым выходом блока предварительной обработки и входом блока распределения информации, выход которого соединен с первыми входами блоков управления коммутаторами и блоком оперативной памяти, вторые входы блоков оперативной памяти соединены со вторым выходом блока предварительной обработки, выходы блоков оперативной памяти соединены со вторыми входами соответствующих блоков управления коммутаторами и с информационными входами блока печрти, который соединен двусторонней связью с блоком ввода информа-

ПИИ, одноименные информационные входы коммутаторов объединены и соединены с. входами устройства.

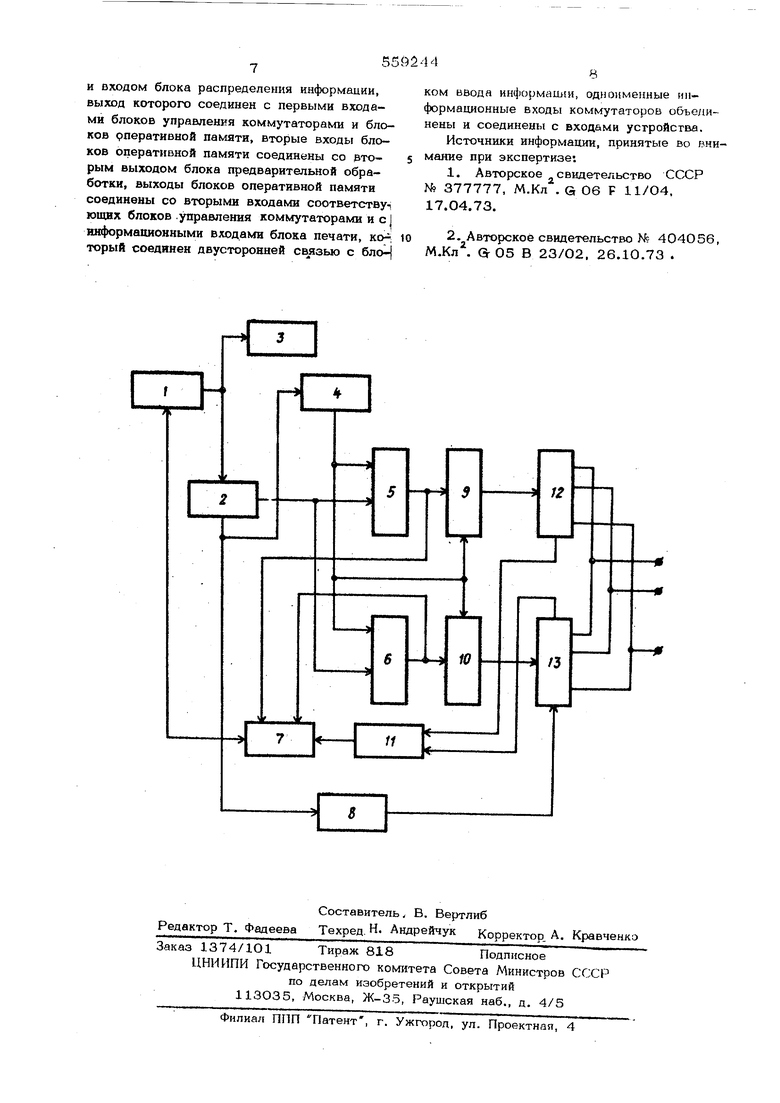

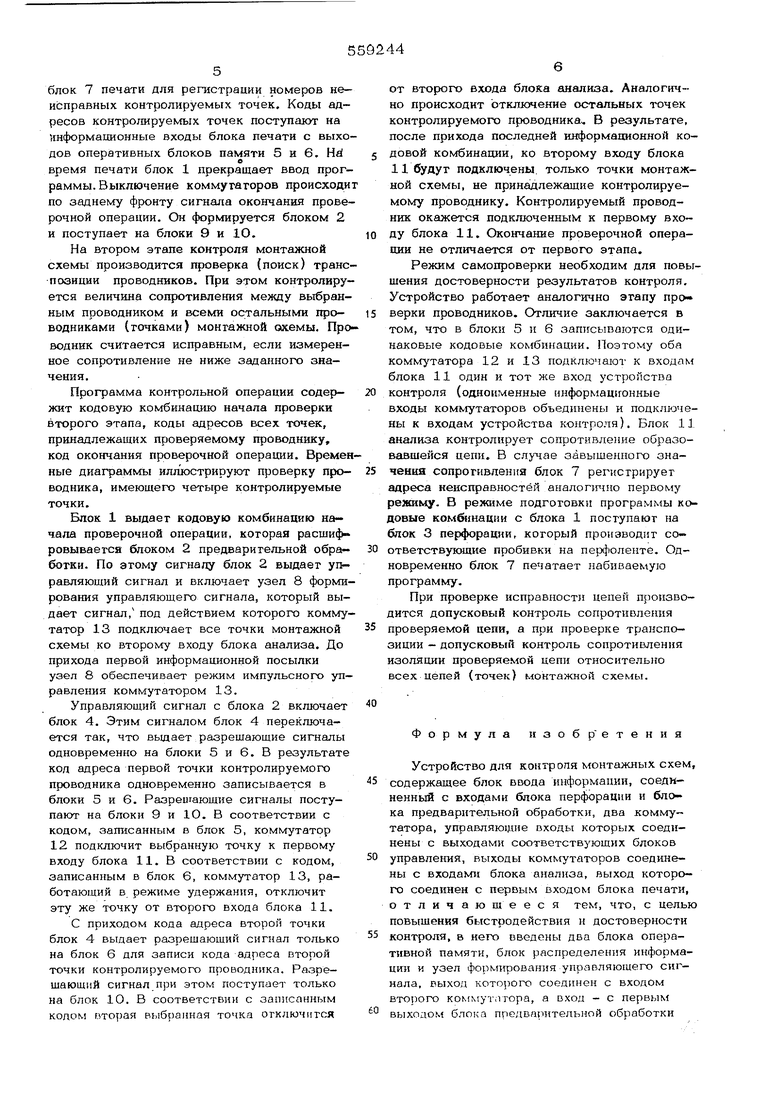

На чертеже приведена функциональная схема устройства.

В устройство входит блок 1 ввода информации, блок 2. предварительной обработки, блок 3 перфорации, блок 4 распределения информации, блок 5 оперативной памяти канала управления первым коммутатором, блок в оперативной памяти канала управления вторым коммутатором, блок 7 печати, узел

8формирования управляющего сигнала, блок

9управления первым коммутатором, блок

10управления вторым коммутатором, блок

11анализа, первый коммутатор 12 и второй коммутатор 13.

Устройство работает следующим образом. .Блок 1 ввода информации подключен к блоку 2 предварительной обработки, блоку 3 перфорации и блоку 7 печати. На эти блоки поступают кодовые комбинации, соответствующие программе контроля, блок 2 связан с блоками 6 i оперативной памяти, на которые поступают кодовые комбинации адресов кбнтрьлируемых точек, ис блоком 4 распределения информации. Кроме того, блок 2 управляет работой узла 8 формирования управляющего сигнала. Вход блока 4 распределения информации подключен к первым (управляющим) входам блоков 5 и 6. Сигналы, поступающие на эти входы, разрещают за пись информации в блоки оперативной памяти. Блок 4 подключен к блокам 9 и 1О. Этим обеспечивается включение коммутаторов после полного обновления информации в блоках оперативной памяти. Выходы блоков 5 и 6 соединены через блоки 9 и 10 с ул равляющими входами коммутаторов 12 и 13. Дополнительно с выходов блоков оперативной памяти кодовые комбинации поступают на информационные входы блока 7 печати. По управляющим входам блок 7 подключен к блоку 11, который вьщает команду на печать, и блоку 1. Эта связь обеспечивает прекращение ввода программы на время регистрации неисправности. Выходы коммутаторов 12 и 13 подключены к блоку 11 анализа, а выход узла 8 - к управляющему входу коммутатора 13. Эта связь обеспечивает подключение выбранных кодов коммутатора 13 к входу блока 11 анализа.

В исходном состоянии сигналы с блока 4 распределения информации на блоки 5, 6, 9 и Ю не поступают. Блоки 9 и 10 выключены. Узел 8 формирования управляющего сигнала выдает нулевой уровень напряжения. В результате в исходном состоянии бло. ки коммутации выключены и все входы устройства контроля монтажных схем отключ(ны от блока 11 анализа.

Устройство может работать в режиме конроля монтажных схем, режиме самоконтроля и режиме подготовки программы контроля. Контроль монтажной схемы осуществляется в два этапа. На первом эТапе производится проверка исправности цепей, предусмотренных монтажной схемой. Для этого контролируется величина сопротивления между двумя точками, принадлежащими проверяемому проводнику. Проводник считается исправным, если его сопротивление не превыщает заданного значения. Программа каждой контрольной операции вьщается блоком 1 и поступает на блок 2 предварительной обработки. На первом этапе проверки монтажной схемы она содержит кодовую комбинат ПИЮ начЕша проверочной операции, которая дополнительно несет информацию об этапе проверки, код адреса первЪй контролируемой точки, код адресавторой контролируемой точки, код окончания проверочной операции.

После расщифровки кодовой комбинации начала проверочной операции блок 2 управляющим сигналом включает блок 4 распределения инф(5рмации. Узел 8 формирования управляющего сигнала на этом этапе не работает.

Первый информационный сигнал - код адреса первой контролируемой точки через блок 2 предварительной обработки поступает на информационные входы блоков 5 и 6. Он подается на управляющий вход оперативного блока памяти 5, обеспечивая запись Кода первого адреса.

В момент прихода второго информационного сигнала - кода адреса второй контролируемой точки блок 4 вьщает разрешающий сигнал на управляющий вход блока 6 и код второго адреса записывается во второй оперативный блок памяти 6.

Сигнал разрещения записи поступает также на блоки 9 и 10 управления коммутаторами. Под действием этого сигнала в соответствии с кодом, записанным в блок 5, блок 9 включает коммутатор 12 и первая контролируемая точка, принадлежащая проверяемому проводнику, подключается к первому входу блока анализа. В соответствии с кодом, записанным в блок 6, блок 0 включает коммутатор 13, в результате вторая точка контролируемого проводника будет подключена ко второму входу блока 11.

С приходом кодовой комбинации окончания проверочной операции блок 1 анализа производит измерение сопротивления проводника ив случае отклонения его значения от заданного предела вьщает команду на блок 7 печати для регастрации номеров неисправных контролируемых точек. Коды адресов контролируемых точек поступают на Информационные входы блока печати с выхо дов оперативных блоков памяти 5 и 6. Hd время печати блок 1 прекращает ввод программы. Выключение коммугагоров происходи по заднему фронту сигнала окончания прове рочной операции. Он формируется блоком 2 и поступает на блоки 9 и 1О. На втором этапе контроля монтажной схемы производится проверка (поиск) транс позиции проводников. При этом контролируется величина сопротивления между выбранным проводником и всеми остальными про- водниками (точками) монтажной охемы. Про водник считается исправным, если измеренное сопротивление не ниже заданного значения. Программа контрольной операции содержит кодовую комбинацию начала проверки второго этапа, коды адресов всех точек, принадлежащих проверяемому проводнику, код окончания проверочной операции. Времен ные диаграммы иллюстрируют проверку проводника, имеющего четыре контролируемые точки. Блок 1 выдает кодовую комбинацию начала проверочной операции, которая расши4ьровываегса блоком 2 предварительной обрабогки. По этому сигналу блок 2 выдает управляющий сигнал и включает узел 8 форми рования управляющего сигнала, который выдает сигнал, под действием которого комму татор 13 подключает все точки монтажной схемы ко второму входу блока анализа. До прихода первой информационной посылки узел 8 обеспечивает режим импульсного управления коммутатором 13. Управляющий сигнал с блока 2 включает блок 4. Этим сигналом блок 4 переключается так, что выдает разрещающие сигналы одновременно на блоки 5 и 6. В результате код адреса первой точки контролируемого проводника одновременно записывается в блоки 5 и 6. Разреигающие сигналы поступают на блоки 9 и Ю. В соответствии с кодом, записанным в блок 5, коммутатор 12 подключит выбранную точку к первому входу блока 11. В соответствии с кодом, записанным в блок 6, коммутатор 13, работающий в режиме удержания, отключит эту же точку от второго входа блока 11. С приходом кода адреса второй точки блок 4 выдает разрещающий сигнал только на блок 6 для записи кода адреса второй точки контролируемого проводника. Разрешающий сигнал при этом поступает только на блок 10. В соответствии с записанным кодом гзторая выбранная точка отключится от второго входа блока анализа. Аналогично происходит отключение остальных точек контролируемого проводника,. В результате, после прихода последней информапионной кодовой комбинации, ко второму входу блока 11 будут подключены, только точки монтажной схемы, не принадлежащие контролируемому проводнику. Контролируемый проводник окажется подключенныК к первому входу блока 11. Окончание проверочной операции не отличается от первого этапа. Режим самопроверки необходим для повышения достоверности результатов контроля. Устройство работает аналогично этапу про верки проводников. Отличие заключается в том, что в блоки 5 и 6 записываются одинаковые кодовые комбинации. Поэтому оба коммутатора 12 и 13 подключают к входам блока 11 один и тот же вход устройства контроля (одноименные информационные входы кoм гyтaтopoв объединены и подключены к входам устройства контроля). Блок 11 анализа контролирует сопротивление образовавшейся цепи. В случае завышенного значения сопрогивлення блок 7 регистрирует адреса неисправностей аналогично первому рехшму. В режиме подготовки программы кодовые комбинации с блока 1 поступают на блок 3 перфорации, который производит соответствующие пробивки на перфоленте. Одновременно блок 7 печатает набиваемую программу. При проверке исправности цепей производится допусковый контроль сопротивления проверяемой цепи, а при проверке транспозиции - допусковый контроль сопротивления изоляции проверяемой цепи относительно всех цепей (точек) монтажной схемы. Формула изобретения Устройство для контр опя монтажных схем, содержащее блок ввода информации, соединенный с входами блока перфорации и блока предварительной обработки, два коммутатора, управляющие входы которых соединены с выходами соответствующих блоков управления, выходы коммутаторов соединены с входами блока анализа, выход которого соединен с первым входом блока печати, отличающееся тем, что, с целью повышения быстродействия и достоверности контроля, в него введены два блока оперативной памяти, блок распределения информации и узел формирования управляющего сигнала, выход которого соединен с входом второго коммутатора, а вход - с первым выходом блока предварительной обработки

и входом блока распределения информации, выход которого соединен с первыми входами блоков управления коммутаторами и блоков рперативной памяти, вторые входы блоков оперативной памяти соединены со это- s рым выходом блока предварительной обработки, выходы блоков оперативной памяти соединены со вторыми входами соответству-i ющих блоков управления коммутаторами и с | Ш1формаю{онными входами блока печати, ю торый соедннен двусторонней связью с блоС -С1

ком ввода информации, одноименные информационные входы коммутаторов объединены и соединены с входами устройства.

Источники информации, принятые во внимание при экспертизе:

Ю

4-J

/3

Авторы

Даты

1977-05-25—Публикация

1975-07-17—Подача