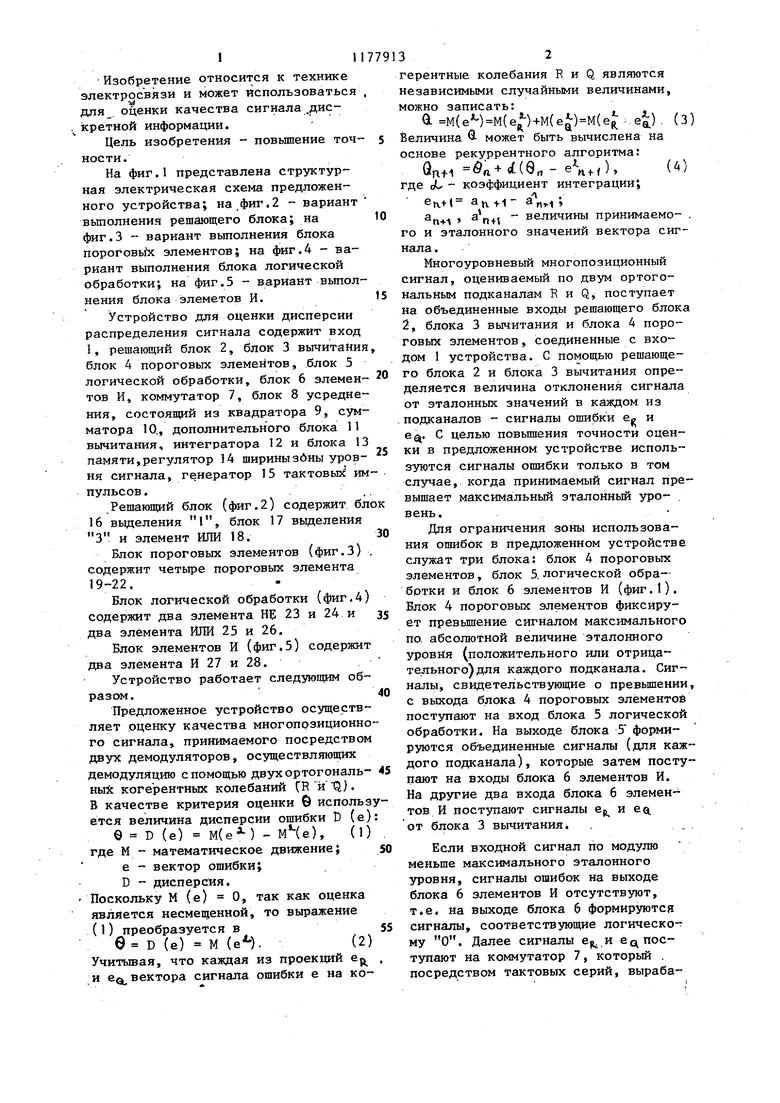

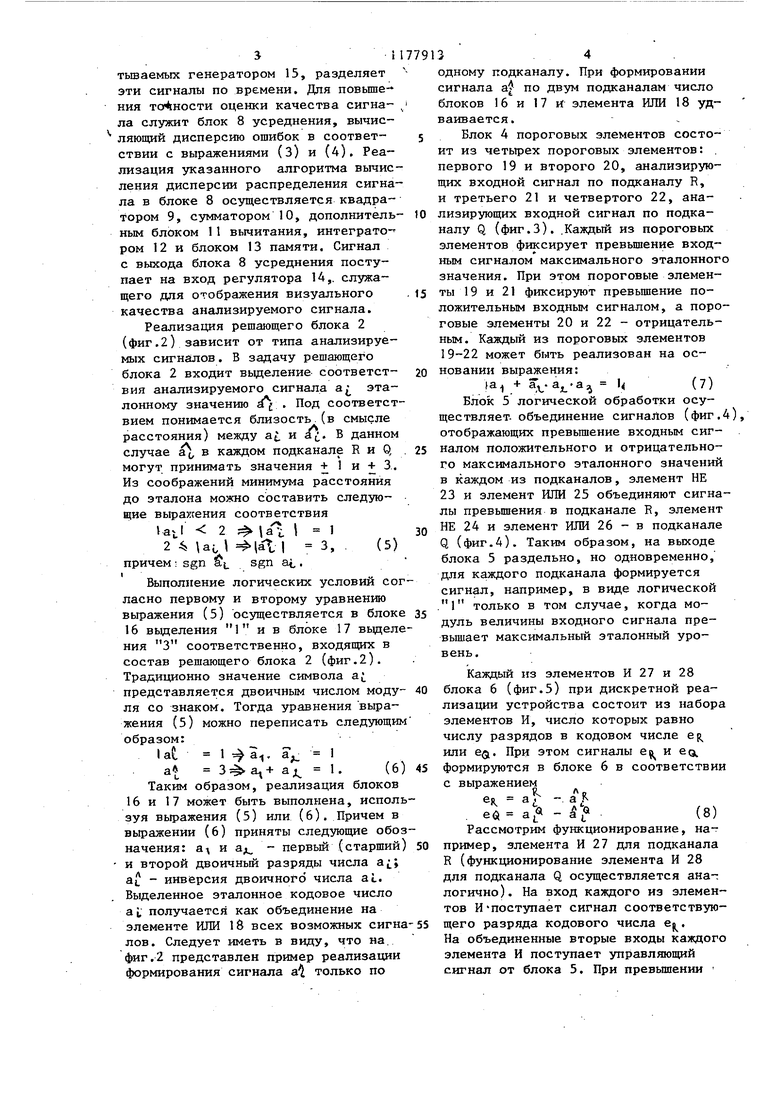

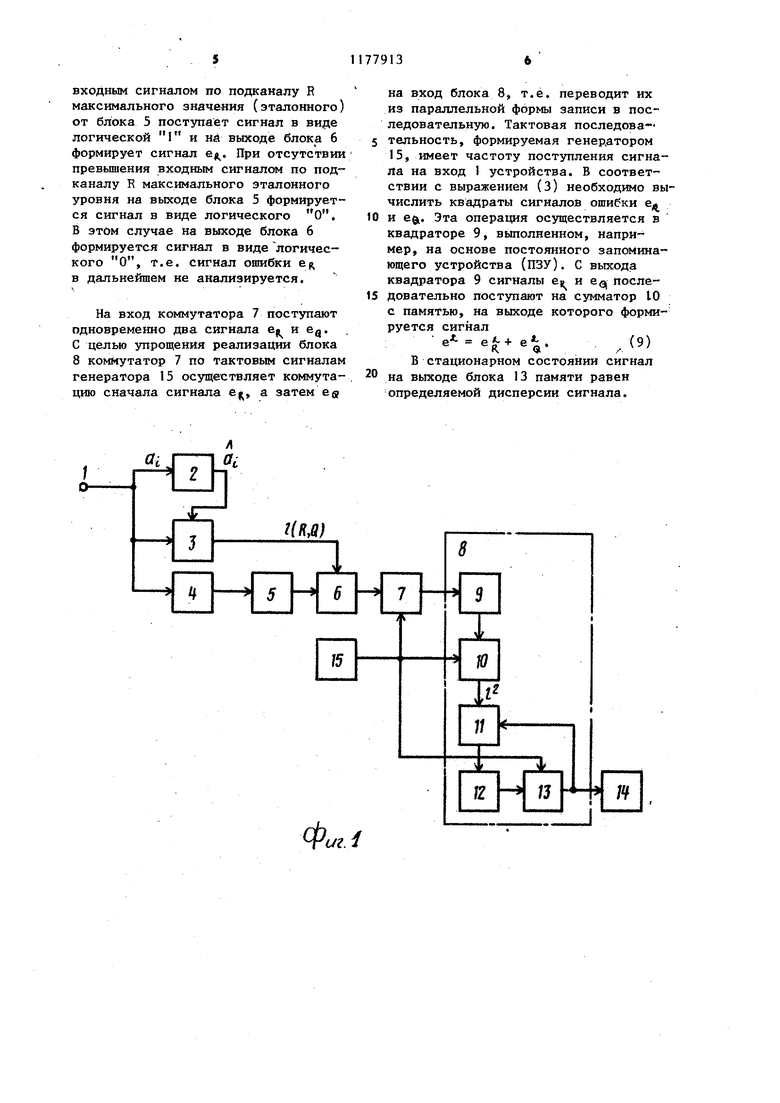

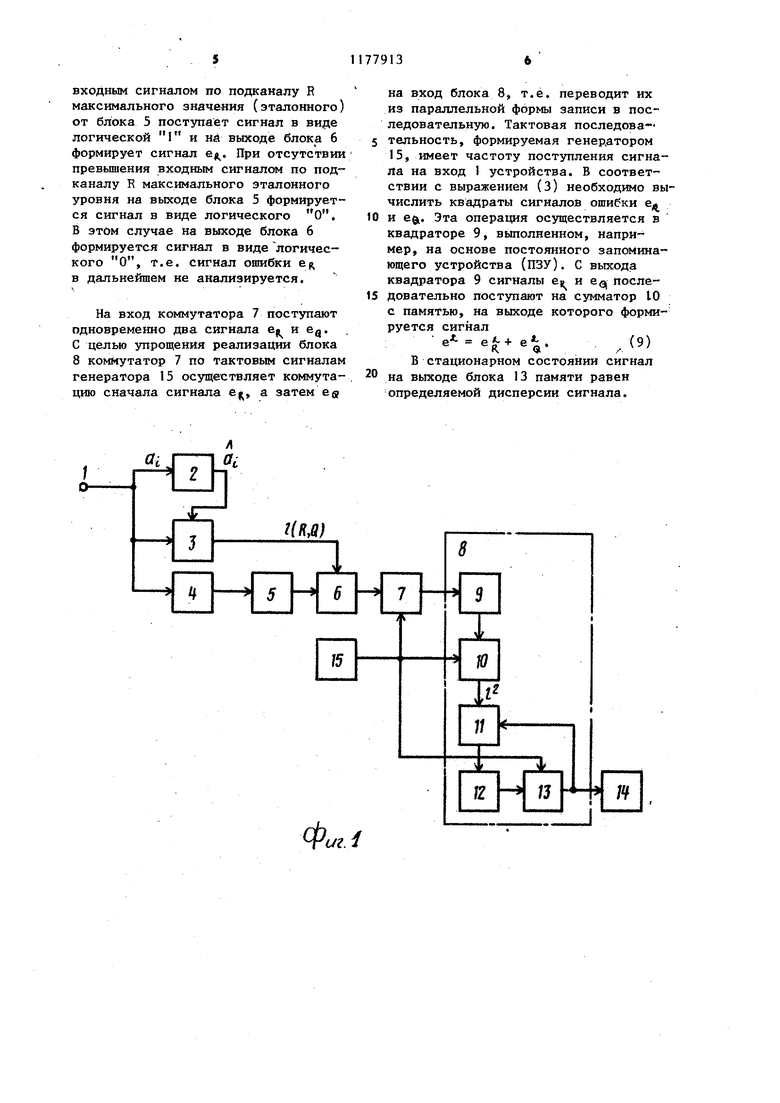

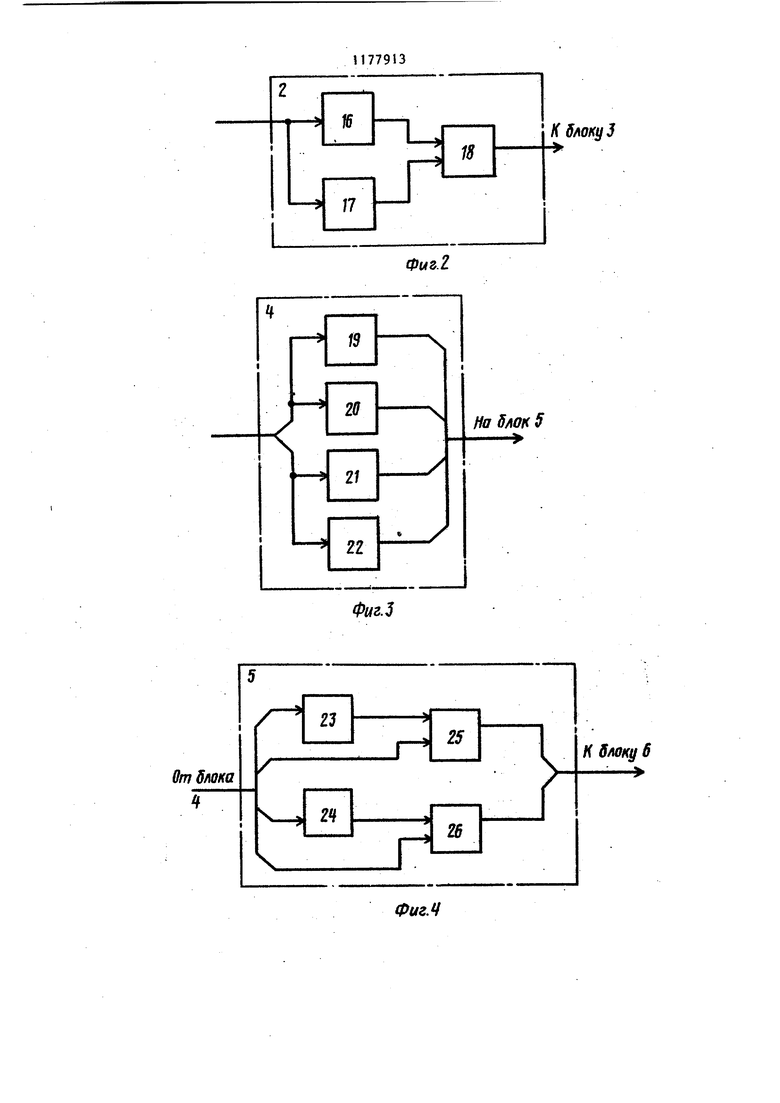

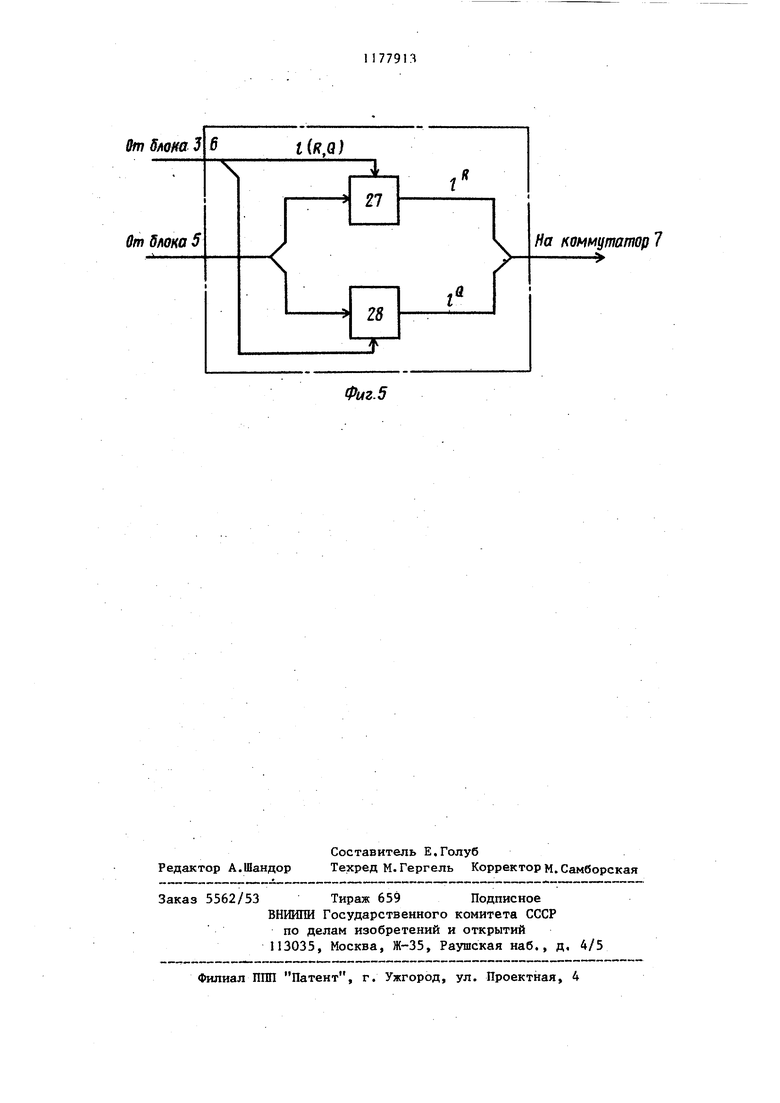

Изобретение относится к технике электросвязи и может использоваться для оценки качества сигнала .дис. кретной информации. Цель изобретения - повьшение точности. На фиг.1 представлена структурная электрическая схема предложенного устройства; на.фиг.2 - вариант вьтолнения решающего блока; на фиг.3 - вариант вьтолнения блока пороговыЬс элементов; на фиг.4 - вариант выполнения блока логической обработки; на фиг.5 - вариант вьтолнения блока элеметов И. Устройство для оценки дисперсии распределения сигнала содержит вход 1, решающий блок 2, блок 3 вычитания блок 4 пороговых элемейтов, блок 5 логической обработки, блок 6 злементов И, коммутатор 7, блок 8 усреднения, состоящий из квадратора 9, сумматора 10., дополнительного блока П вычитания, интегратора 12 и блока 13 памяти,регулятор 14 ширинызбны уровня сигнала, генератор 15 тактовых им пульсов . Решающий блок (фиг.2) содержит бл 16 вьщеления 1, блок 17 вьщеления 3 и элемент ИЛИ 18. Блок пороговых элементов (фиг.З) содержит четыре пороговых элемента 19-22. Блок логической обработки (фиг,4) содержит два элемента Щ 23 и 24 и два элемента ИЛИ 25 и 26. Блок элементов И (фиг.5) содержит два элемента И 27 и 28. Устройство работает следующим образом. Предложенное устройство осуществляет оценку качества многопозиционно го сигнала, принимаемого посредством двух демодуляторов, осуществляющих демодуляцию с помощью двухортогональньйс когерентных колебаний CR HQ} В качестве критерия оценки О использ ется величина дисперсии ошибки D (е) © D (е) М(е - (е), (l) где М - математическое движение; е - вектор ошибки; D - дисперсия. Поскольку М (е) О, так как оценка явлйется несмещенной, то выражение (О преобразуется в 0 D (е) М (е). (2) Учитьгоая, что каждая из проекций е и вектора сигнала ошибки е на ко1132 герентные колебания R и Q являются независимыми случайными величинами, можно записать: а M()M(e)-bM(e)M(eJ;..e) . (З) Величина О- может быть вычислена на основе рекуррентного алгоритма: ОпИ а+(0. - е,,), (4) где dL - коэффициент интеграции; ( 1-1- aVi а, , - величины принимаемо- . го и эталонного значений вектора сигнала . Многоуровневый многопозиционный сигнал, оцениваемый по двум ортогональным подканалам R и Q, поступает на объединенные входы решающего блока 2, блока 3 вычитания и блока 4 пороговых элементов, соединенные с входом 1 устройства. С помощью решающего блока 2 и блока 3 вычитания определяется величина отклонения сигнала от эталонных значений в каждом из подканалов - сигналы ошибки е и eQ, С целью повьш1ения точности оценки в предложенном устройстве используются сигналы ошибки только в том случае, когда принимаемый сигнал превышает максимальный эталонный уровень. Для ограничения зоны использования ошибок в предложенном устройстве служат три блока: блок 4 пороговых элементов, блок 5, логической обра- ботки и блок 6 элементов И (фиг.1). Блок 4 пороговых элементов фиксирует превьппение сигналом максимального по. абсолютной величине эталонного уровня (положительного или отрицательного) для каждого подканала. Сигналы, свидетельствующие о превышении, с выхода блока 4 пороговых элементоб поступают на вход блока 5 логической обработки. На выходе блока 5 формируются объединенные сигналы (для каждого подканала), которые затем поступают на входы блока 6 элементов И. На другие два входа блока 6 элементов И поступают сигналы е и eg от блока 3 вычитания. Если входиой сигнал по модулю меньше максимального эталонного уровня, сигналы ошибок на выходе блока 6 элементов И отсутствуют, т.е. на вьпсоде блока 6 формируются сигналы, соответствующие логическое му О. Далее сигналы е. и е ( поступают на коммутатор 7, который . посредством тактовых серий, вырабаS1тьшаемых генератором 15, разделяет эти сигналы по времени. Для повьшения точности оценки качества сигнала служит блок 8 усреднения, вычисляющий дисперсию ошибок в соответствии с выражениями (З) и (4). Реализация з азанного алгоритма вычисления дисперсии распределения сигнала в блоке 8 осуществляется квадратором 9, сумматором 10, дополнительным блоком 1 I вычитания, интегратором 12 и блоком 13 памяти. Сигнал с выхода блока 8 усреднения поступает на вход регулятора 1А,. служащего для отображения визуального качества анализируемого сигнала. Реализация решающего блока 2 (фиг.2) зависит от типа анализируемых сигналов. В задачу решающего блока 2 входит вьщеление соответстВИЯ анализируемого сигнала а эталонному значению aj . Под соответст вием понимается близость.(в смысле расстояния) между а и а. В данном случае а, в каждом подканале R и Q могут принимать значения + 1 и + 3.. Из соображений минимума расстояния до эталона можно составить следзтощие выражения соответствия latl 2 I 1 2 4 at I Ф(а1 I 3, (5) причем; sgn lii. sgn ai,. Выполнение логических условий сог ласно первому и второму уравнению выражения (5) осуществляется в блоке 16 выделения 1 и в блоке 17 вьщеле ния 3 соответственно, входящих в состав решающего блока 2 (фиг,2). Традиционно значение символа а представляется двоичным числом модуля со знаком. Тогда уравнения выражения (5) можно переписать следующим образом: lat 1 - а. ар - 1 а« 3 ад 1. (б Таким образом, реализация блоков 16 и 17 может быть выполнена, исполь зуя выражения (5) или (6). Причем в вьфажении (6) приняты следующие обоз начения: а и ад - первый (старший - и второй двоичный разряды числа а а - инверсия двоичного числа aL. Выделенное эталонное кодовое число а i, получается как объединение на элементе ИЛИ 18 всех возможных сигна лов. Следует иметь в виду, что на. фиг.2 представлен пример реализации формирования сигнала а только по Э4 одному подканалу. При формировании сигнала а по двум подканалам число блоков 16 и 17 и элемента ИПИ 18 удваивается. Блок 4 пороговых элементов состоит из четьфех пороговых элементов: первого 19 и второго 20, анализирующих входной сигнал по подканалу R, и третьего 21 и четвертого 22, анализирующих входной сигнал по подканалу Q (фиг.З). .Калодый из пороговых элементов фиксирует превьш1ение входным сигналом максимального эталонного значения. При этом пороговые элементы 19 и 21 фиксируют превьш1ение положительным входным сигналом, а пороговые элементы 20 и 22 - отрицательным. Каждый из пороговых элементов 19-22 может быть реализован на основании выражения: х, L Блок 5 логической обработки осуществляет, объединение сигналов (фиг.4), отображающих превьш1ение входным сигналом положительного и отрицательного максимального эталонного значений в каждом из подканалов, элемент НЕ 23 и элемент ИЛИ 25 объединяют сигналы превышения в подканале В, элемент НЕ 24 и элемент ИЛИ 26 - в подканале Q (фиг.4). Таким образом, на выходе блока 5 раздельно, но одновременно, для каждого подканала формируется сигнал, например, в виде логической 1 только в том случае, когда модуль величины входного сигнала превышает максимальный эталонный уровень. Каждый из элементов И 27 и 28 блока 6 (фиг.5) при дискретной реализации устройства состоит из набора элементов И, число которых равно числу разрядов в кодовом числе ер или egi. При этом сигналы ев и eQ, формируются в блоке 6 в соответствии с выражением е, af - af . еС(- а (8) Рассмотрим функционирование, например, элемента И 27 для подканала R (функционирование элемента И 28 для подканала Q осуществляется аналогично). На вход каждого из элементов Ипоступает сигнал соответствующего разряда кодового числа е. На объединенные вторые входы каждого элемента И поступает управляющий сигнал от блока 5. При превьш1ении

входным сигналом по подканалу R максимального значения (эталонного) от блока 5 поступает сигнал в виде логической I и на выходе блока 6 формирует сигнал е. При отсутствии превышения входным сигналом по подканалу R максимального эталонного уровня на выходе блока 5 формируется сигнал в виде логического О. В этом случае на выходе блока 6 формируется сигнал в виде логического О, т.е. сигнал ошибки ер. в дальнейшем не анализируется.

На вход коммутатора 7 поступают одновременно два сигнала ец и е. С целью упрощения реализации блока 8 коммутатор 7 по тактовым сигналам генератора 15 осзгществляет коммутацию сначала сигнала ej, а затем eg

на вход блока 8, т.е. переводит их из параллельной формы записи в последовательнзпо. Тактовая последова-

тельность, формируемая генер,атором 15, имеет частоту поступления сигнала на вход 1 устройства. В соответствии с выражением (З) необходимо вычислить квадраты сигналов ошибки е.

и е. Эта операция осуществляется в квадраторе 9, выполненном, например, на основе постоянного запоминающего устройства (ПЗУ). С выхода квадратора 9 сигналы е и eg, последовательно поступают на сумматор 10 с памятью, на выходе которого формируется сигнал

е е. (9)

. стационарном состоянии сигнал на выходе блока 13 памяти равен определяемой дисперсии сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации несущей частоты | 1985 |

|

SU1356249A1 |

| Устройство оценки качества дискретного канала связи | 1988 |

|

SU1540012A1 |

| Устройство для приема сигналов с парциальным откликом | 1983 |

|

SU1117855A1 |

| Устройство для преобразования сигналов | 1984 |

|

SU1234991A1 |

| Адаптивный корректор межсимвольных искажений | 1982 |

|

SU1067605A1 |

| Адаптивный корректор | 1979 |

|

SU866756A2 |

| Устройство для классификации дискретных случайных сигналов | 1983 |

|

SU1160435A1 |

| Адаптивный корректор канала связи | 1983 |

|

SU1166318A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

УСТРОЙСТВО ДЛЯ ОЦЕНКИ ДИСПЕРСИИ РАСПРЕДЕЛЕНИЯ СИГНАЛА, содержащее генератор тактовых импульсов, последовательно соединенные блок .пороговых элементов, вход которого является входе устройства, блок логической обработки и блок элементов И, регулятор ширины зоны уровня сигнала, выход которого является выходом устройства, отличающееся тем, что, с целью повышения точности, в него введены последовательно соединенные решакщий блок и блок вычитания, объединенные входы которых соединены с входом блока пороговых элементов, коммутатор и блок усреднения, выполненный в виде последовательно соединенных квадратора,вход которого соединенс выходом коммутатора, сумматора, второй вход которого соединен с выходом генератора тактовых импульсов, дополнительного блока вычитания, интегратора и блока памяти, второй вход и выход которого соединены соответственно с выходом генератора тактовых импульсов и вторым входом дополнительного блока вычитания, выход блока памяти подключен к входу регу(Л лятора ширины зоны уровня сигнала, выход генератора тактовых импульсовк управлякщему входу коммутатора, информационный вход которого соединен с выходом блока элементов И, второй вход которого соединен с выходом блока вычитания. ч со

Фс,1. /

23

От блока

24

К блоку 3

18

Фиг.2

На блок 5

Фиг.З

25

Н блоку 6

26

Фиг,Ц

Вт блока 5

l(K,Qj

От блока 5

Фиг. 5

| Патент США 3633108, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для оценки распределения дисперсии сигнала | 1974 |

|

SU543159A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-09-07—Публикация

1984-05-28—Подача