С71

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования сигналов | 1984 |

|

SU1234991A1 |

| Двухканальное устройство приема сигналов данных | 1986 |

|

SU1415451A1 |

| Устройство для оценки дисперсии распределения сигнала | 1984 |

|

SU1177913A1 |

| ЦИФРОВОЙ ТЕЛЕФОННЫЙ АППАРАТ | 1992 |

|

RU2012151C1 |

| Система передачи и приема дискретной информации | 1980 |

|

SU944146A1 |

| Система передачи и приема сигналов с дифференциальной импульсно-кодовой модуляцией | 1978 |

|

SU758513A1 |

| Устройство для приема сигналов с парциальным откликом | 1983 |

|

SU1117855A1 |

| Радиолиния, защищенная от несанкционированного доступа | 2023 |

|

RU2820855C1 |

| Устройство преобразования сигналов для каналов тональной частоты | 1989 |

|

SU1709551A1 |

| Устройство преобразования сигналов | 1982 |

|

SU1053311A1 |

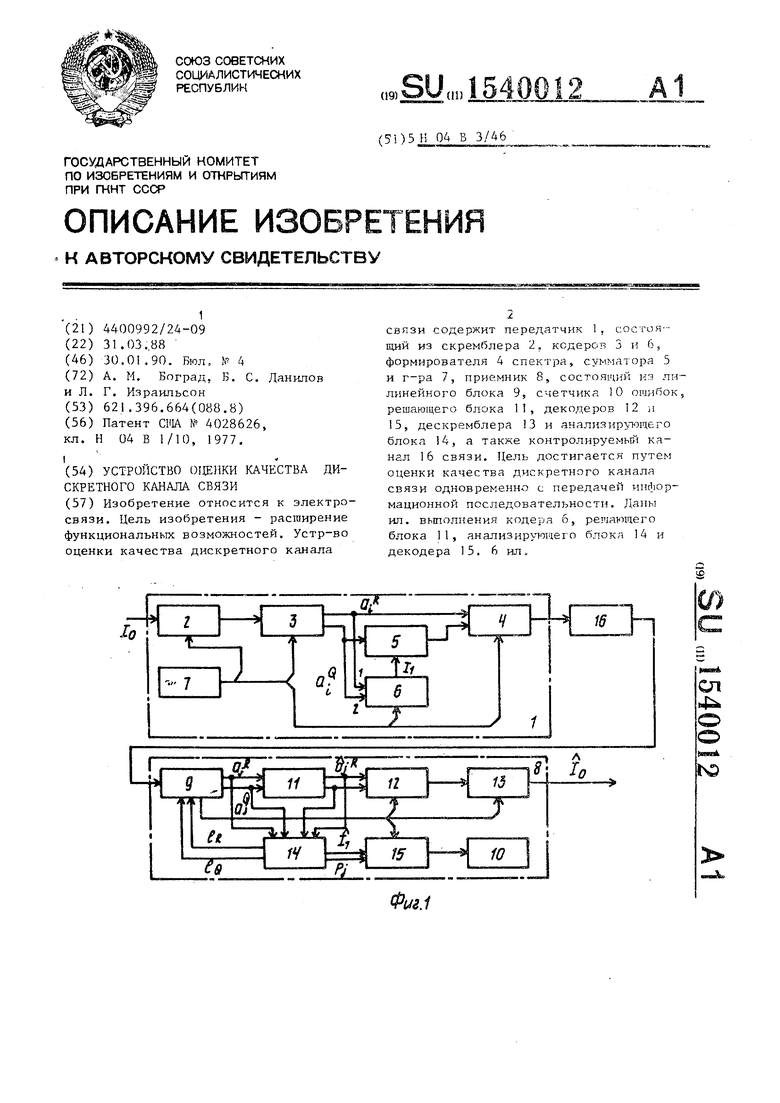

Изобретение относится к электросвязи. Цель изобретения - расширение функциональных возможностей. Устройство оценки качества дискретного канала связи содержит передатчик 1, состоящий из скремблера 2, кодеров 3 и 6, формирователя 4 спектра, сумматора 5 и г-ра 7, приемник 8, состоящий из линейного блока 9, счетчика 10 ошибок, решающего блока 11, декодеров 12 и 15, дескремблера 13 и анализирующего блока 14, а также контролируемый канал 16 связи. Цель достигается путем оценки качества дискретного канала связи одновременно с передачей информационной последовательности. Даны ил.выполнения кодера 6, решающего блока 11, анализирующего блока 14 и декодера 15.6 ил.

Изобретение относится к электросвязи, в частности к устройствам оценки качества дискретных каналов связи при передаче амплитудно-фазоманипулирован них сигналов.

Цель изобретения - расширение функциональных возможностей путем оценки качества дискретного канала связи одновременно с передачей инфор- мационной последовательности.

Па фиг. 1 приведена электрическая структурная схема устройства оценки качества дискретного канала связи; на фиг. 2 - пространство передаваемых сигналов; на фиг. 3 - электрическая структурная схема второго кодера; на фиг. 4 - электрическая структурная схема решающего блока; на фиг. 5 - электрическая структурная схема лизирующего блока; на фиг. 6 - электрическая структурная схема второго декодера,

Устройство оценки качества дискретного канала связи содержит передатчик 1, состоящий из скремблера 2, первого кодера 3, формирователя 4 спектра, сумматора 5, второго кодера 6 и генератора 75 а также приемник 8, образованный линейным блоком 9, счетчик 10 ошибок, решающим блоком 11, первым декодером i2, дескремблером 13, анализирующим блоком 14 и вторым декодером 15. На фиг. 1 также показан контролируемый канал 16 связи.

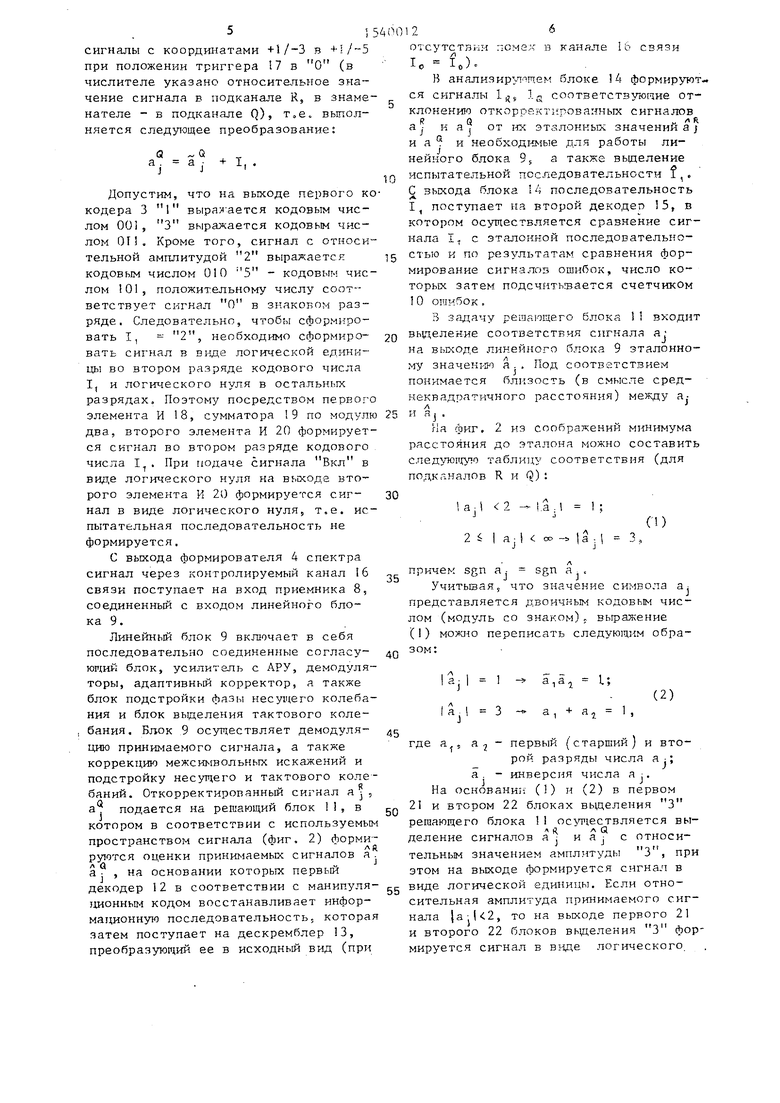

Второй кодер 6 образуют триггер 17 первый элемент И 18, сумматор 19 по модулю два и второй элемент И 20.

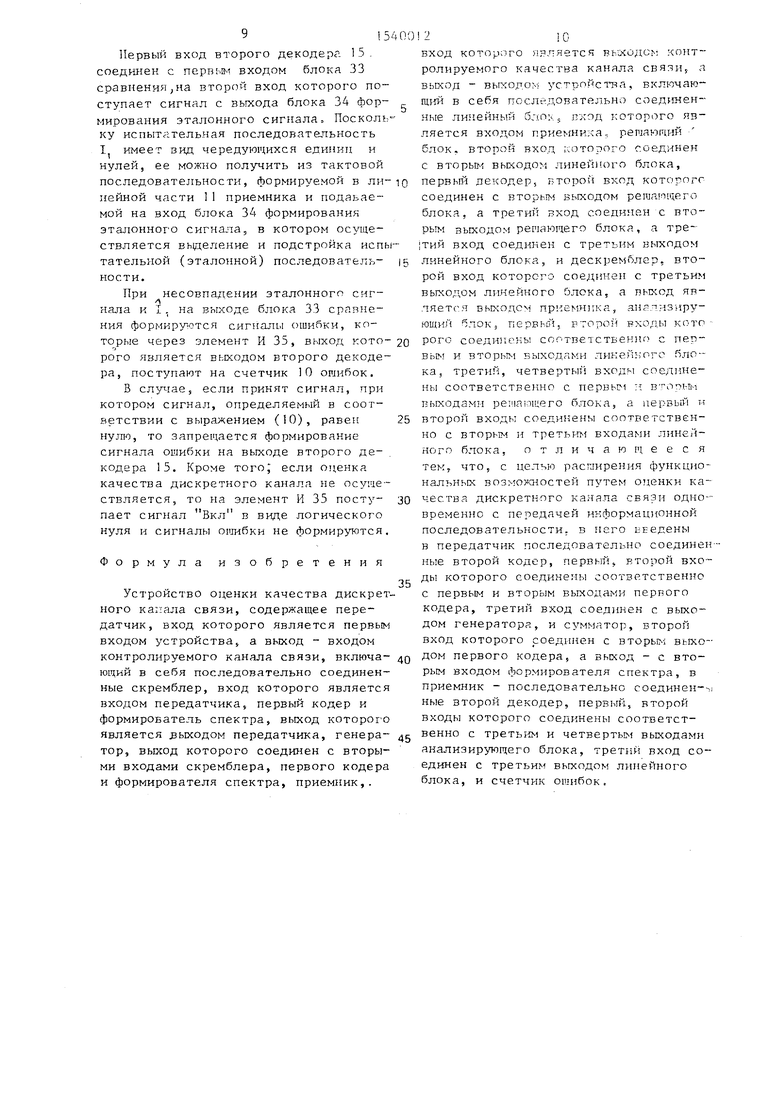

Решающий блок 11 состоит из первого 21 и второго 22 блоков выделения

ll-jll

Анализирующий блок 14 содержит первый 23 и второй 24 блоки вычитания, блок 25 выделения 5, первый элемент И 26, элемент 27 ИЛИ, форми- рователь 28, третий блок 29 вычитания, второй 30 и третий 31 элементы И. и коммутатор 32.

Второй декодер 15 выполнен на блоке 33 сравнения, блоке 34 формиро- вания эталонного сигнала и элементе

И 35.

Устройство работает следующим образом.

Передаваемая информационная по- следовательность 10 от -источника информации поступает на вход передать чика 1, соединенный с входом скрембг- лера 2, который преобразует структу

Q

5 0 с

5 о

5

ру передаваемой информации к виду псевдослучайной последовательности.

Вид псевдослучайной последовательности на выходе скремблера 2 определяется его образующим полиномом. Такое преобразование необходимо для работы систем синхронизации и адаптивной коррекции приемника 8.

С выхода скремблера 2 преобразованная последовательность поступает на первый кодер 3, где осуществляется кодирование сигнала в соответствии с манипуляционным кодом.

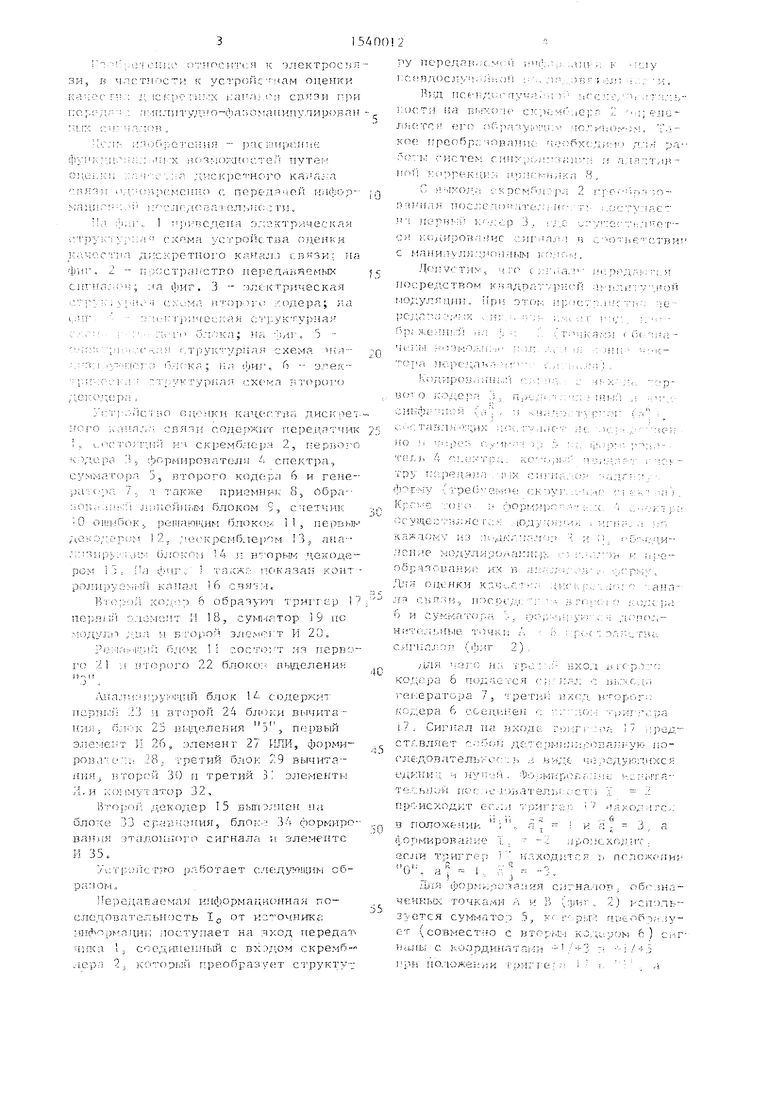

Допустим, что сигналы передаются посредством квадратурной амплитудной модуляции. При этом пространство передаваемых сигналов имеет вид, изображенный на фиг. 2 (точками обозначены возможные положения конца вектора передаваемого сигнала).

Кодированный сигнал с выхода первого кодера 3, представленный в виде синфазной (а) и квадратурной (а)„ составляющих поступает непосредственно и через сумматор 5 на формирова-. тель 4 спектра, который придает спектру передаваемых сигналов заданную форму (требуемое скругление спектра). Кроме того, в формирователе 4 спектра осуществляется . (Одуляция сигнала по каждому из подканалов R и О, объединение модулированные сигналов и преобразование их в аналоговую форму. Для оценки качества дискретного канала связи, посредством второго кодера 6 и сумматора 5, формируются дополнительные точки А и В пространства сигналов (фиг. 2).

Для чего на третий вход второго Кодера 6 подается сигнал с выхода генератора 7, третий вход второго кодера 6 соединен с входом триггера 17. Сигнал на входе триггера 17 представляет собой детерминированную последовательность в виде чередующихся единиц и нулей. Формирование испытательной последовательности I 2 происходит если триггер 17 находится

в положении 1, а 1 и a z 3, а формирование I, -2 происходит, если триггер 17 находится в положении О, а} 1, а -3.

Для формирования сигналов, обозначенных точками А и В (фиг. 2) используется сумматор 5, который преобразует (совместно с вторым кодером 6) сигналы с координатами +1/+3 в +1/+5 при положении триггера 17 в 1, а

сигналы с координатами +1/-3 в +1/-5 при положении триггера 17 в О (в числителе указано относительное значение сигнала в подканале R, в знаменателе - в подканале Q), т.е. выполняется следующее преобразование:

а. а

Q

I,

Допустим, что на выходе первого ко- кодера 3 1 выражается кодовым числом 001, 3 выражается кодовым числом Oil. Кроме того, сигнал с относительной амплитудой 2 выражается

кодовым числом 010

IICII

кодовым чис20

35

40

50

30

лом 101, положительному числу соответствует сигнал 0м в знаковом разряде. Следовательно, чтобы сформировать I, - 2, необходимо сформировать сигнал в виде логической единицы во втором разряде кодового числа I, и логического нуля в остальных разрядах. Поэтому посредством первого элемента И 18, сумматора 19 по модулю 25 и а два, второго элемента И 20 формируется сигнал во втором разряде кодового . числа It. При подаче сигнала Вкл в виде логического нуля на выходе второго элемента И 20 формируется сигнал в виде логического нуля, т.е. испытательная последовательность не формируется.

С выхода формирователя 4 спектра сигнал через контролируемый канал 16 связи поступает на вход приемника 8, соединенный с входом линейного блока 9.

Линейный блок 9 включает в себя последовательно соединенные согласующий блок, усилитель с АРУ, демодуляторы, адаптивный корректор, а также блок подстройки фазы несущего колебания и блок выделения тактового колебания. Блок ,9 осуществляет демодуляцию принимаемого сигнала, а также коррекцию межсимвольных искажений и подстройку несущего и тактового колебаний. Откорректированный сигнал а, а подается на решающий блок 1 1, в

В анализирующем блоке 14 формируют ся сигналы 1Л, 1а соответствующие отклонению откорректированных сигналов а и aj от их эталонных значений aj и а и необходимые для работы линейного блока 9, а также выделение испытательной последовательности ,. С выхода блока 14 последовательность I, поступает на второй декодер 15, в котором осуществляется сравнение сигнала I, с эталонной последовательностью и по результатам сравнения формирование сигналов ошибок, число которых затем подсчитывается счетчиком 10 ошибок.

В задачу решающего блока 11 входит выделение соответствия сигнала а: на выходе линейного блока 9 эталонному значению а.. Под соответствием

lj

понимается близость (в смысле среднеквадратичного расстояния) между а,л

j

На фиг. 2 из соображений минимума

расстояния до эталона можно составить следующую таблицу соответствия (для подканалов R и Q):

1:1 2

.а,,

2 I

а-

i л а

О)

причем sgn aj sgn a,.

Учитывая, что значение символа а, представляется двоичным кодовым числом (модуль со знаком), выражение (1) можно переписать следующим образом:

1а:|

1

Я5 Ч

а-,5,, L;

+ а,

(2)

1,

45

где а

2 - первый (старший) и второй разряды числа а:; а. - инверсия числа а:. На основании (1) и (2) в первом 21 и втором 22 блоках выделения 3

решающего блока 11 осуществляется вы- л я л а

деление сигналов а

и

aJ

котором в соответствии с используемым пространством сигнала (фиг. 2) формируются оценки принимаемых сигналов а. а , на основании которых первый декодер 12 в соответствии с манипуля- ее виде логической единицы. Если отно- ционным кодом восстанавливает инфор- сительная амплитуда принимаемого сиг21

относительным значением амплитуды 3, при этом на выходе формируется сигнал в

мационную последовательность, которая затем поступает на дескремблер 13, преобразующий ее в исходный вид (при

нала }а , то на выходе первого и второго 22 блоков выделения 3 формируется сигнал в виде логического

5

0

5 и а

отсутствии помех в канале 16 связи

1о - 1о).

В анализирующем блоке 14 формируются сигналы 1Л, 1а соответствующие отклонению откорректированных сигналов а и aj от их эталонных значений aj и а и необходимые для работы линейного блока 9, а также выделение испытательной последовательности ,. С выхода блока 14 последовательность I, поступает на второй декодер 15, в котором осуществляется сравнение сигнала I, с эталонной последовательностью и по результатам сравнения формирование сигналов ошибок, число которых затем подсчитывается счетчиком 10 ошибок.

В задачу решающего блока 11 входит выделение соответствия сигнала а: на выходе линейного блока 9 эталонному значению а.. Под соответствием

lj

понимается близость (в смысле среднеквадратичного расстояния) между а,л

j

На фиг. 2 из соображений минимума

расстояния до эталона можно составить следующую таблицу соответствия (для подканалов R и Q):

и а

1:1 2

.а,,

2 I

а-

i л а

О)

причем sgn aj sgn a,.

Учитывая, что значение символа а, представляется двоичным кодовым числом (модуль со знаком), выражение (1) можно переписать следующим обра40

зом:

|

1

Я5 Ч

а-,5,, L;

+ а,

(2)

1,

где а

2 - первый (старший) и второй разряды числа а:; а. - инверсия числа а:. На основании (1) и (2) в первом 21 и втором 22 блоках выделения 3

решающего блока 11 осуществляется вы- л я л а

деление сигналов а

и

aJ

виде логической единицы. Если отно- сительная амплитуда принимаемого сиготносительным значением амплитуды 3, при этом на выходе формируется сигнал в

21

нала }а , то на выходе первого и второго 22 блоков выделения 3 формируется сигнал в виде логического

нуля. Исходя из описанного представления сигналов в виде многоразрядных чисел необходимо формировать только второй разряд эталонного сигнала. При этом третий разряд имеет вид логической единицы, второй разряд представляет собой сигнал с выхода первого 21 и второго 22 блоков выделения 3. Остальные разряды имеют вид логичес- кого нуля.

С первого и второго выходов рейа- ющего блока 11 сигналы а и а подаются на третий и четвертый входы анализирующего блока 14, на первый и второй входы которого подается сйгнаR и а« ка 9.

В первом блоке 23 вычитания анализирующего блока 14 формируется сигнал 1, во втором блоке 24 вычитания - сигнал lg, сигналы формируются по еле следующему правилу:

лы а и а Т с выхода линейного блоп

aj

л R

-ai 5

ла

-а. .

(3)

Выход первого блока вычитания 23 соединен с вторым выходом анализирую- щего блока 14. Выход второго блока 24 вычитания соединен с первым входом коммутатора 32, выход которого соединен с первым выходом анализирующего блока 14. На второй вход коммутатора 32 подается сигнал 1д с выхода третьего блока 29 вычитания; сигнал 1Q формируется по следующему правилу:

а

а , a. -bj .

() 40

На управляющий вход коммутатора 32 подается сигнал V- с второго выхода формирователя 28, сигнал V.- определяется согласно следующему правилу: Д5

(5)

V. {а}К iHleJI «JПод действием управляющего сигнала V. коммутатор 32 формирует сигнал -Q

1Q по следующему правилу:

1 VT

1Q при Vj

о;

1 Q при V j. 1.

(6)

Эталонный сигнал Ъ формируется в формирователе 28 по правилу:

sgn bj (Ц 1)(а« 4). (7)

При этом остальные разряды кодового числа b.- соответствуют 5.

На первый и второй входы формирователя 28 подаются сигналы соответственно с первого и второго вы-- ходов блока 25 выделения 5. Сигналы в блоке выделения 5 25 формируются по правилу:

4

-4

sgn af a ;

sgn a aa

(Я)

На третий вход формирователя 28 ( подается сигнал с выхода первого элемента И 26, где формируется сигнал с уровнем логической единицы при услол R ,

вии a j 1 .

На третьем выходе формирователя

/

28 формируется последовательность I , по правилу:

I, P. aj 4) + (а® -4)J. (9)

Третий выход формирователя 28 соединен с первым входом второго элемента И 30, выход которого соединен с третьим выходом анализирующего блока 14.

При отсутствии передачи испытательной последовательности на второй вход второго элемента И 30 подается сигнал Вкл в виде логического нуля, а при передаче испытательной последовательности сигнал Вкл имеет вид логической единицы.

Сигнал Р-, соответствующий признаку наличия испытательной информации, формируется на выходе третьего элемента И 31 по следующему правилу:

5

Q

5

(Ю)

PJ (а 1)(|а}а| 2).

Первый вход третьего элемента И 31 соединен с выходом первого элемента И 26, второй вход соединен с выходом элемента ИЛИ 27, в котором формируется сигнал с уровнем логической единицы при условии .

Выход третьего элемента И 31 соединен, с четвертым вьрсодом анализирующего блока 14 и четвертым входом формирователя 28.

С третьего и четвертого выходов анализирующего блока 14 сигналы I, и Р. подаются соответственно на первый и второй входы второго декодера 15, третий вход которого соединен с третьим выходом линейного блока.

91

Первый вход второго декодера 15. соединен с первым входом блока 33 сравнения,на второй вход которого поступает сигнал с выхода блока 34 фор- мирования эталонного сигнала. Поскольку испытательная последовательность 11 имеет вид чередующихся единиц и нулей, ее можно получить из тактовой последовательности, формируемой в ли нейной части 11 приемника и подаваемой на вход блока 34 формирования эталонного сигнала, в котором осуществляется выделение и подстройка исптательной (эталонной) последователь- ности.

При несовпадении эталонного сиг

нала и I, на выходе блока 33 сравнения формируются сигналы ошибки, ко

торые через элемент И 35, выход кото-20 Р°го соединены соответственно с пер- рого является выходом второго декодера, поступают на счетчик 10 ошибок.

В случае, если принят сигнал, при котором сигнал, определяемый в соответствии с выражением (10), равен 25 нулю, то запрещается формирование сигнала ошибки на выходе второго декодера 15. Кроме того если оценка качества дискретного канала не осуществляется, то на элемент И 35 посту- 30 пает сигнал Вкл в виде логического нуля и сигналы ошибки не формируются.

вым и вторым выходами линейного блока, третий, четвертый входы соединены соответственно с первым и вторым выходами решающего блока, а первьй и второй входы соединены соответственно с вторым и третьим входами линейного блока, отличающееся тем, что, с целью расширения функциональных возможностей путем оценки качества дискретного канала связи одновременно с передачей информационной последовательности, в него введены в передатчик последовательно соединен ные второй кодер, первый, второй входы которого соединены соответственно с первым и вторым выходами первого кодера, третий вход соединен с выходом генератора, и сумматор, второй вход которого соединен с вторым выхо35

Формула изобретения

Устройство оценки качества дискретного канала связи, содержащее передатчик, вход которого является первым входом устройства, а выход - входом контролируемого канала связи, вклгоча- 40 дом первого кодера, а выход - с втовым и вторым выходами линейного блока, третий, четвертый входы соединены соответственно с первым и вторым выходами решающего блока, а первьй и второй входы соединены соответственно с вторым и третьим входами линейного блока, отличающееся тем, что, с целью расширения функциональных возможностей путем оценки качества дискретного канала связи одновременно с передачей информационной последовательности, в него введены в передатчик последовательно соединен ные второй кодер, первый, второй входы которого соединены соответственно с первым и вторым выходами первого кодера, третий вход соединен с выходом генератора, и сумматор, второй вход которого соединен с вторым выхоющий в себя последовательно соединенные скремблер, вход которого является входом передатчика, первый кодер и формирователь спектра, выход которого является .выходом передатчика, генера- 45 тор, выход которого соединен с вторыми входами скремблера, первого кодера и формирователя спектра, приемник,.

рым входом формирователя спектра, в приемник - последовательно соединен--, ные второй декодер, первый, второй входы которого соединены соответственно с третьим и четвертым выходами анализирующего блока, третий вход соединен с третьим выходом линейного блока, и счетчик ошибок.

2

10

вход которого является выходом контролируемого качества канала связи, а выход - выходом устройства, включающий в себя последовательно соединенные линейный блок, вход которого является входом приемника, решающий блок, второй вход которого соединен с вторым выходом линейного блока, первый декодер, второй вход которого соединен с вторым выходом решающего блока, а третий вход соединен с вторым выходом решающего блока, а тре- |тий вход соединен с третьим выходом линейного блока, и дескремблер, второй вход которого соединен с третьим выходом линейного блока, а выход является выходом приемника, анализирующий блок, первьй, второй входы котоР°го соединены соответственно с пер-

дом первого кодера, а выход - с втовым и вторым выходами линейного блока, третий, четвертый входы соединены соответственно с первым и вторым выходами решающего блока, а первьй и второй входы соединены соответственно с вторым и третьим входами линейного блока, отличающееся тем, что, с целью расширения функциональных возможностей путем оценки качества дискретного канала связи одновременно с передачей информационной последовательности, в него введены в передатчик последовательно соединенные второй кодер, первый, второй входы которого соединены соответственно с первым и вторым выходами первого кодера, третий вход соединен с выходом генератора, и сумматор, второй вход которого соединен с вторым выхорым входом формирователя спектра, в приемник - последовательно соединен--, ные второй декодер, первый, второй входы которого соединены соответственно с третьим и четвертым выходами анализирующего блока, третий вход соединен с третьим выходом линейного блока, и счетчик ошибок.

J

В Фиг.2

Фиг. 4

-

Фиг.Э

фиг.5

фиг. В

Составитель В, Курков Редактор Л. Пчолинская Техред Л. Сердюкова Корректор М. Шароши

Заказ 231

Тираж 520

ВНИШ1И Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Патент США № 4028626, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| I | |||

Авторы

Даты

1990-01-30—Публикация

1988-03-31—Подача