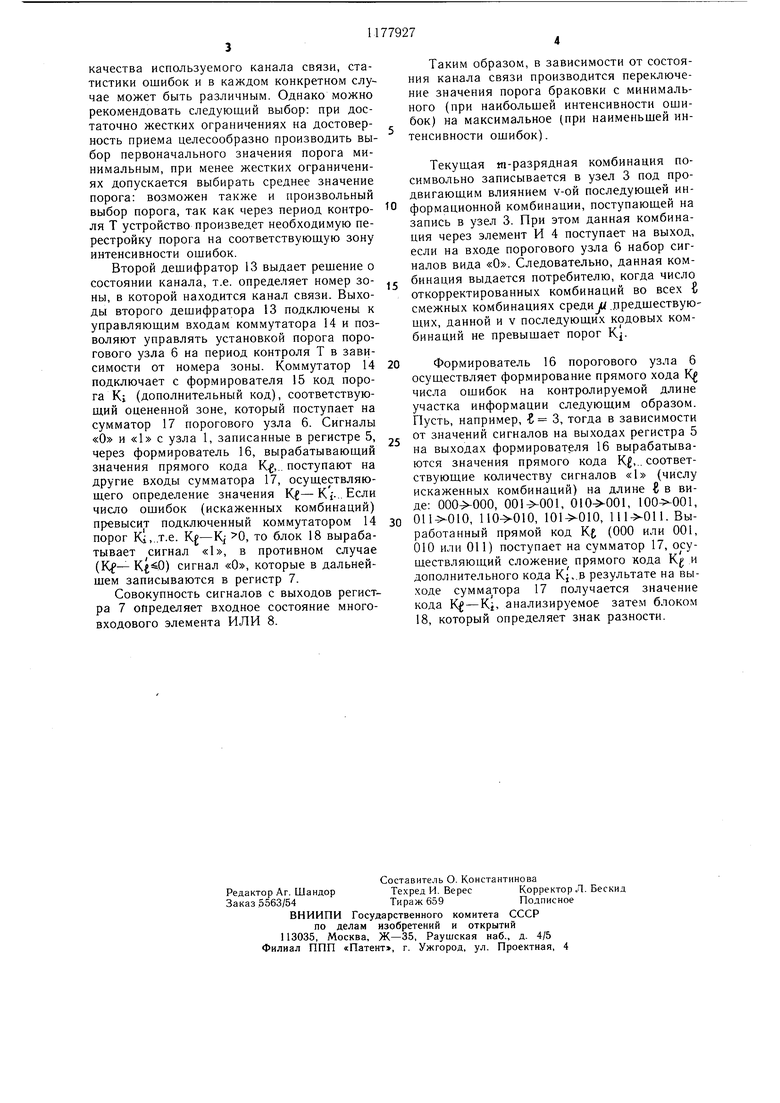

со to Изобретение относится к технике обработки сообщений, может быть использовано в вычислительной технике и системах передачи дискретной информации с -решающей обратной связью и односторонних системах передачи со стиранием сообщений и является усовершенствованием изобретения по авт. св. № 598258. Цель изобретения - увеличение пропускной способности при обеспечении заданной достоверности. На чертеже представлена структурная электрическая схема устройства для исправления ощибок в системе передачи дискретной информации. Устройство содержит узел 1 анализа, узел 2 коррекции, узел 3 буферной памяти, элемент И 4, регистр 5 сдвига, пороговый узел 6, регистр 7 сдвига, элемент ИЛИ 8, синхронный распределитель 9, первый счетчик 10, первый дешифратор 11, второй счетчик 12, второй дешифратор 13, коммутатор 14, формирователь 15 сигнала, при этом пороговый узел 6 содержит формирователь 16, сумматор 17, блок 18 сравнения. Устройство для исправления ошибок в системе передачи дискретной информации работает следуюш,им образом. Принимаемая п-разрядная кодовая комбинация поступает в узел 1, где анализируется на соответствие проверочным условиям. Одновременно синхронный распределитель 9 по последовательности принимаемых кодовых комбинаций производит определение начала комбинации для формирования импульсов длительности t.. равной длительности передачи п-разрядной комбинации, которые в дальнейшем будут использованы для задания периода контроля Т, выбираемого из условия оперативности и достоверности контроля состояния канала связи. Кодовые комбинации посимвольно с узла 1 записываются в узел 2, при этом информация о результате анализа комбинации в виде сигнала «1 (в случае не соответствия кодовой комбинации проверочным условиям) или «О (в случае удовлетворения проверочным условиям) за время не более полтакта сдвиговой частоты вводится с управляющего выхода узла 1 в узел 2, регистр 5 и второй счетчик 12. Информационная часть в узле 2 исправляется при поступлении сигнала «1 от узла 1. После коррекции оши бок информационная часть с выхода узла 2 в виде т-разрядной последовательности (комбинации) посимвольно записывается в узел 3. Перед приемом первой кодовой комбинации предварительно устанавливается началь ное состояние порогового узла 6: коммутатор 14 на период контроля Т подключает начальное значение дополнительного кода порога Ki с формирователя 15 к сумматоСовокупность сигналов с выходов регистра 5 (набор «О и «1 с узла 1), преобразованных формирователем 16 в прямой код Kfi числа ошибок на длине -Е, поступает на другие входы сумматора 17, с выходов которого вырабатывается код разности Kg-Ki, поступающий на блок 18. Если значение кода разности ..Q, то блок 18 вырабатывает сигнал «1, в противном случае (К{-Ki ..Q) - сигнал «О, которые подаются на вход регистра 7. Сигналы «1 или «О с управляющего выхода узла 1 поступают на выход второго счетчика 12, который осуществляет подсчет числа ошибок, фиксируемых узлом 1 (число кодовых комбинаций с обнаруженными ошибками), за период контроля Т состояния канала связи. Синхронный распределитель 9 формирует импульсы длительности, равной длительности tj .кодовой комбинации, которые подсчитываются первым счетчиком 10, ориентированным на объем контрольной выборки в N кодовых комбинаций. Сброс значений первого счетчика 10 производит первый дешифратор 11, который после дешифрации кода N осуществляет, кроме того, управление вторым счетчиком 12 и вторым дешифратором 13. За период контроля Т N-ti .во втором счетчике 12 формируются значения кода К, соответствующее числу искаженных кодовых комбинаций (интенсивности появления ошибок в канале), которые по сигналу с первого дешифратора 11 переписываются из второго счетчика 12 во второй дешифратор 13. Второй дешифратор 13 представляет собой дешифратор зон отсчета, имеющий дискретную установку величин зон отсчета. Состояние канала связи (значения разрядов второго счетчика 12) предварительно разбивается на несколько зон. Например: зона 1 - наименьшая интенсивность ошибок, зона 2- средняя интенсивность ошибок, зона 3 - наибольшая интенсивность ошибок. Для каждой зоны устанавливается соответствующий порог браковки контролируемого участка информации KI, к, tfj, определяемый в процессе проектирования устройства исходя из заданной достоверности приема информации качества используемого канала связи. Из предложенного деления на зоны соотношение между значениями порогов браковки следующие: . Значения кодов порогов браковки переводятся в дополнительные коды (путем добавления «1 к старшим разрядам) и хранятся в формирователе 15. Дополнительный код необходим для реализации операции вычитания Kg-К,- на сумматоре 17. Выбор начального значения порога браковки Ki осуществляется в зависимости от

качества используемого канала связи, статистики ошибок и в каждом конкретном случае может быть различным. Однако можно рекомендовать следующий выбор: при достаточно жестких ограничениях на достоверность приема целесообразно производить выбор первоначального значения порога минимальным, при менее жестких ограничениях допускается выбирать среднее значение порога: возможен также и произвольный выбор порога, так как через период контроля Т устройство произведет необходимую перестройку порога на соответствующую зону интенсивности ошибок.

Второй дешифратор 13 выдает решение о состоянии канала, т.е. определяет номер зоны, в которой находится канал связи. Выходы второго дещифратора 13 подключены к управляющим входам коммутатора 14 и позволяют управлять установкой порога порогового узла б на период контроля Т в зависимости от номера зоны. Коммутатор 14 подключает с формирователя 15 код порога Ki (дополнительный код), соответствующий оцененной зоне, который поступает на сумматор 17 порогового узла 6. Сигналы «О и «1 с узла 1, записанные в регистре 5, через формирователь 16, вырабатывающий значения прямого кода К,.. поступают на другие входы сумматора 17, осуш,ествляющего определение значения K -Ki-..Если число ошибок (искаженных комбинаций) превысит подключенный коммутатором 14 порог Ki,..T.e. Kg-Kj 0, то блок 18 вырабатывает сигнал «1, в противном случае (Kf- ) сигнал «О, которые в дальнейшем записываются в регистр 7.

Совокупность сигналов с выходов регистра 7 определяет входное состояние многовходового элемента ИЛИ 8.

Таким образом, в зависимости от состояния канала связи производится переключение значения порога браковки с минимального (при наибольшей интенсивности ошибок) на максимальное (при наименьшей интенсивности ошибок).

Текущая tn-разрядная комбинация посимвольно записывается в узел 3 под продвигающим влиянием v-ой последующей информационной комбинации, поступающей на запись в узел 3. При этом данная комбинация через элемент И 4 поступает на выход, если на входе порогового узла б набор сигналов вида «О. Следовательно, данная комс бинация выдается потребителю, когда число откорректированных комбинаций во всех смежных комбинациях среди jU .предшествующих, данной и V последующих кодовых комбинаций не превышает порог К|.

0 Формирователь 16 порогового узла б осуществляет формирование прямого хода Kg числа ошибок на контролируемой длине участка информации следующим образом. Пусть, например, С 3, тогда в зависимости от значений сигналов на выходах регистра 5 на выходах формирователя 16 вырабатываются значения прямого кода К,.. соответствующие количеству сигналов «1 (числу искаженных комбинаций) на длине в виде: , , , ,

0 , , , 111-5-011. Выработанный прямой код Kt (000 или 001, 010 или 011) поступает на сумматор 17, осуществляющий сложение прямого кода KJ; и дополнительного кода Ki-.B результате на выходе сумматора 17 получается значение кода К - Ki, анализируемое затем блоком 18, который определяет знак разности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации | 1978 |

|

SU849521A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302701C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ БЛОКОВ ИНФОРМАЦИИ | 2003 |

|

RU2249920C2 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| Устройство для управления каналами связи | 1977 |

|

SU732843A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ по авт. св. № 598258, отличающееся тем, что, с целью увеличения пропускной способности при обеспечении заданной достоверности, в него введены формирователь сигналов, входы которого соединены с управляющими входами коммутатора, и последовательно соединенные синхронный распределитель, первый счетчик, первый дешифратор, второй счетчик, второй дешифратор и коммутатор, выходы которого соединены с дополнительными входами порогового узла, причем синхронный распределитель подключен входом к входу узла анализа, к управляющему выходу которого подключен управляющий вход второго счетчика, причем управляющий выход первого дешифратора соединен с управляющими входами первого счетчика и второго дешифратора.

| Устройство для исправления ошибок в системах передачи дискретной информации | 1975 |

|

SU598258A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-09-07—Публикация

1984-04-17—Подача