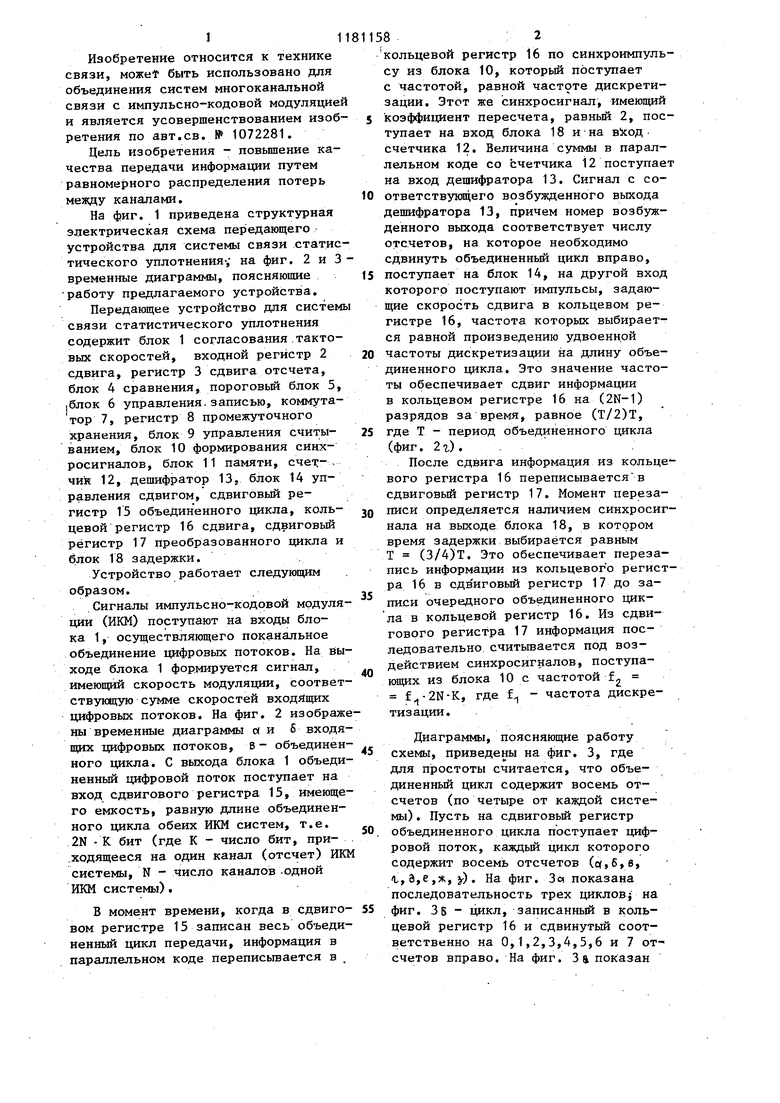

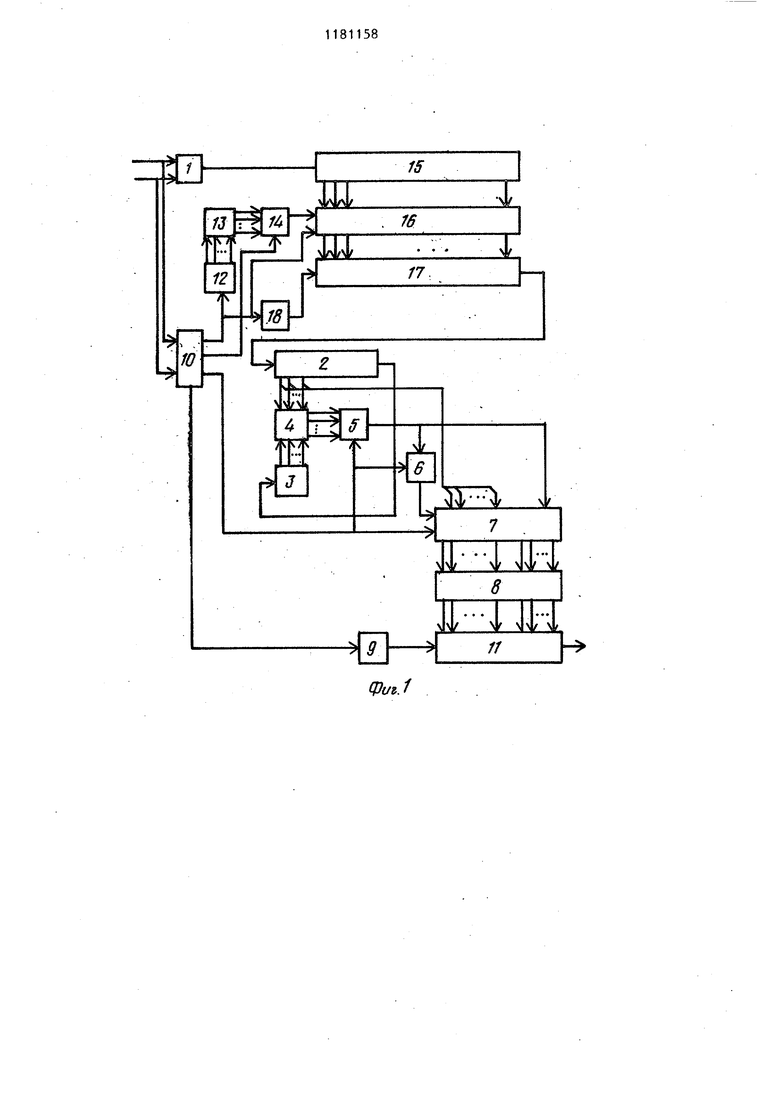

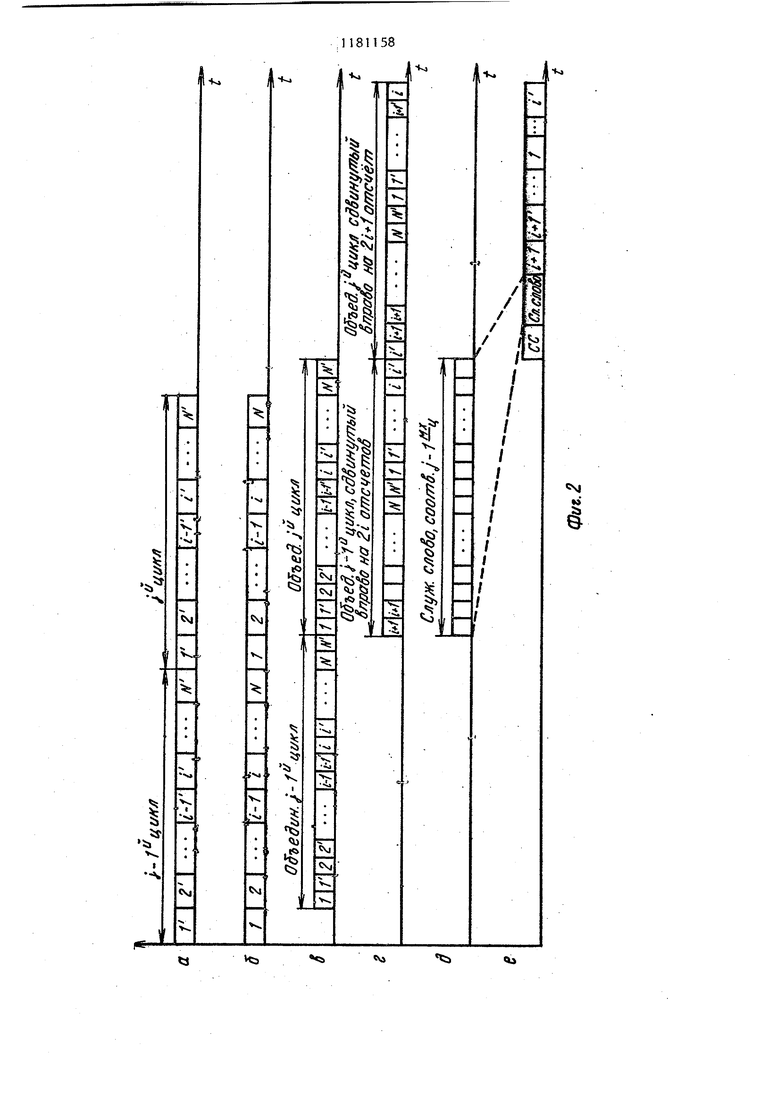

Изобретение относится к технике связи, может быть использовано для объединения систем многоканальной связи с импульсно-кодовой модуляцие и является усовершенствованием изоб ретения по авт.св. № 1072281. Цель изобретения - повьшение качества передачи информации путем равномерного распределения потерь между каналами. На фиг. 1 приведена структурная электрическая схема передающего устройства для системы связи статис тического уплотнения-, на фиг. 2 и 3 временные диаграммы, поясняющие -работу предлагаемого устройства. Передающее устройство для систем связи статистического уплотнения содержит блок 1 согласования.тактовых скоростей, входной регистр 2 сдвига, регистр 3 сдвига отсчета, блок А сравнения, пороговый блок 5, |блок 6 управления.записью, коммутатор 7, регистр 8 промежуточного хранения, блок 9 управления считыванием, блок 10 формирования синхросигналов, блок 11 памяти, счет-. чин 12, дешифратор 13. блок 14 управления сдвигом, сдвиговый регистр 15 объединенного цикла, кольцевой регистр 16 сдвига, сдвиговьй регистр 17 преобразованного цикла и блок 18 задержки.. Устройство работает следующим образом. Сигналы импульсно-кодовой модуля ции (ИКМ) поступают на входы блока 1, осуществляющего поканальное объединение цифровых потоков. На вы ходе блока 1 формируется сигнал, имеющий скорость модуляции, соответ ствующую сумме скоростей входящих цифровых потоков. На фиг. 2 изображ ны временные диаграммы и и б входя щих цифровых потоков, в- объединен ного цикла. С выхода блока 1 объеди ненный цифровой поток поступает на вход сдвигового регистра 15, имеюще го емкость, равнуто длине объединенного цикла обеих ИКМ систем, т.е. 2N - К бит (где К - число бит, при.ходящееся на один канал (отсчет) ИК системы, N - число каналов -одной ИКМ системы). В момент времени, когда в сдвиго вом регистре 15 записан весь объеди ненный цикл передачи, информация в параллельном коде переписьшается в . кольцевой регистр 16 по синхроимпульсу из блока 10, который поступает с частотой, равной частоте дискретизации. Этот же синхросигнал, имеющий коэффициент пересчета, равньш 2, поступает на вход блока 18 и на счетчика 12. Величина суммы в параллельном коде со счетчика 12 поступает на вход дешифратора 13. Сигнал с соответствующего возбужденного выхода дешифратора 13, причем номер возбужденного выхода соответствует числу отсчетов, на которое необходимо сдвинуть объединенньй цикл вправо, поступает на блок 14, на другой вход которого поступают импульсы, задающие скорость сдвига в кольцевом регистре 16, частота которых выбирается равной произведению удвоенной частоты дискретизации на длину объединенного цикла. Это значение частоты обеспечивает сдвиг информации в кольцевом регистре 16 на (2N-1) разрядов за время, равное (Т/2)Т, где Т - период объединенного цикла (фиг. 2г). После сдвига информация из кольцевого регистра 16 переписывается в сдвиговый регистр 17. Момент перезаписи определяется наличием синхросигнала на выходе блока 18, в котором время задержки выбирается равным Т (3/4)Т. Это обеспечивает перезапись информации из кольцевого регистра 16 в сдвиговый регистр 17 до записи очередного объединенного цикла в кольцевой регистр 16. Из сдвигового регистра 17 информация последовательно, считьшается под воздействием синхросигналов, поступающих из блока 10 с частотой f2 f -2N-K, где f - частота дискретизации. Диаграммы, поясняющие работу схемы, приведены на фиг. 3, где для простоты считается, что объе- диненньй цикл содержит восемь отсчетов (по четыре от каждой системы) . Пусть на сдвиговьй регистр объединенного цикла поступает цифровой поток, каждьй цикл которого содержит восемь отсчетов (сг,6,б, г,а,е,ж, j). На фиг. Зя показана последовательность трех циклов; на фиг. Зб - цикл, записанньй в кольцевой регистр 16 и сдвинутьй соответственно на 0,1,2,3,4,5,6 и 7 отсчетов вправо. На фиг. За показан 3 цифровой поток на выходе сдвигового регистра 17, где j-й цикл сдвинут вправо на О отсчетов, j+1-й - на один отсчет, j+2-й цикл - на два отсчета вправо и т.д. Таким образом, оказывается, что отсчеты различных каналов от цикла к циклу сдвигаются на один канальный интервал, что приводит в условиях ста.тис тической перегрузки к равномерному распределению потерь информации между каналами. Далее цифровой поток поступает на входной регистр 2 с емкостью 2N-«K бит. Сигналы с выхода последнего разряда входного регистра 2 поступают на вход регистра сдвига 3 емкостью К бит. Сигналы с выходов регистра сдвига 3 и выходов разрядов входного регистра 2, имеющих номера от (К+1) до 2К, подаются на блок 4, на выходе которого в параллельном коде формируется сигнал равньш абсолютной величине разности предыдущего и текущего отсчетов i-ro канала. На фиг. 32 условно изображен вхо ной регистр 2, блок 4 и регистр сдвига 3. На входной регистр 2 поступает цифровой поток. Пусть, напри мер, в нем записаны отсчеты двух соседних циклов j и (j+1)-ro. С выхода разрядов входного регистра 2 с номерами от (К+1)-го до 2К (К число разрядов, занимаемое одним отсчетом) на вход блока сравнения поступает отсчет c((j + 1)-ro цикла, которьй занимает вторую позицию в цикле. На регистр 3 сдвига в этот момент поступает отсчет g j-го ;цикла, который занимал третью .позицию в J-M цикле. Таким образом происходит сравнение одноименных отсчетов соседних циклов. На фиг.3 происходит сравнение следующих отсчетов и т.д. С выхода блока сигнал поступает на вход порогового блока 5, который в моменты времени, определяемые бло 84 ком 10, формирует на своем выходе сигналы 1, при превышении установленного порога, или О - в противном случае. Сигналы с выхода порогового блока 5 поступают на вход блока 6 и соответствующий вход коммутатора 7, к другим К входам которого подаются в параллельном коде сигналы от разрядов входного регистра 2 с номерами от (К+1) до 2К. Блок 6 в моменты времени, определяемые блоком 10, формирует управляющие сигналы, по которым коммутатор 7 записывает текущее значение канальных отсчетов (разность которых с предыдущими значениями превысила величину, определяемую пороговым блоком 5) и сигналы О и 1, сформированные на выходе порогового блока 5, в отведенные для этих целей информационные и служебное поля регистра 8. Регистр 8 имеет емкость (KN - М )бит, где Mj.j,- число бит, отводимых под синхросигнал циклового фазирования устройства. Для передачи обновляющей информации отводится (KN -2N - ,) бит в каждом выходном цикле. Причем кроме синхросигнала в каждом выходном цикле передается служебное слово емкостью 2N бит, которое показывает, в каких канальных интервалах объединенного цифрового потока абсолютная величина разности значений отсчетов текущего и предыдущего циклов соответствующих канальных интервалов превысила пороговое значение. В момент окончания сравнения величин отсчетов всех канальных интервалов предыдущего и текущего объединенных циклов передачи информация из регистра 8 переписывается в блок 11. Осуществляя последовательное считывание информации из ячеек блока 11, блок 9 формирует цикл передачи, представленный на фиг. , е . Емкость блока 11 равна KN бит.

И5.

«S.

(b

| название | год | авторы | номер документа |

|---|---|---|---|

| Передающее устройство для системы связи статистического уплотнения | 1982 |

|

SU1072281A1 |

| ПЕРЕДАЮЩЕЕ УСТРОЙСТВО ДЛЯ СИСТЕМЫ СВЯЗИ СТАТИСТИЧЕСКОГО УПЛОТНЕНИЯ | 2003 |

|

RU2251217C1 |

| СПОСОБ ОБРАБОТКИ СИГНАЛОВ СВЯЗИ В АБОНЕНТСКОМ ПУНКТЕ БЕСПРОВОДНОЙ СИСТЕМЫ ЭЛЕКТРОСВЯЗИ | 1990 |

|

RU2159007C2 |

| АБОНЕНТСКИЙ ПУНКТ В СИСТЕМЕ БЕСПРОВОДНОЙ ЦИФРОВОЙ ТЕЛЕФОННОЙ СВЯЗИ | 1990 |

|

RU2154360C2 |

| АБОНЕНТСКИЙ ПУНКТ В АБОНЕНТСКОЙ СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ | 1990 |

|

RU2138122C1 |

| Система передачи и приема цифровой информации | 1985 |

|

SU1288923A1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| ПРИЕМНИК СИНХРОСИГНАЛА | 2002 |

|

RU2242093C2 |

| ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ С УСТРОЙСТВОМ БЫСТРОГО ПОИСКА НАВИГАЦИОННЫХ СИГНАЛОВ В УСЛОВИЯХ ВЫСОКОЙ ДИНАМИКИ ОБЪЕКТА | 2006 |

|

RU2341898C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

ПЕРЕДАКЩЕЕ УСТРОЙСТВО ДЛЯ СИСТЕМЫ СВЯЗИ СТАТИСТИЧЕСКОГО УПЛОТНЕНИЯ по авт.св. № 1072281, отличающееся тем, что, с целью повьшения качества передачи информации путем равномерного распределения потерь между каналами, блок согласования скоростей соединен с входным регистром сдвига через введенные в последовательно соединенные сдвиговьш регистр объединенного цикла кольцевой регистр сдвига и сдвиговый регистр преобразованного цикла, а также введены блок задержки и последовательно соединенные счетчик, дешифратор и блок управления сдвигом, выход которого соединен с управляющим входом кольцевого регистра сдвига, синхронизирующий вход сдвигового регистра преобразованного цикла соединен с выходом блока задержки, вход которого объединен с синхронизирующими входами кольцевого регистра сдвига и счетчиi ка и соединен с первым дополнительным выходом блока формирования синх(Л росигналов, второй управляющий вход которого соединен с вторым дополнительным выходом блока формирования синхросигналов.

| Передающее устройство для системы связи статистического уплотнения | 1982 |

|

SU1072281A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-09-23—Публикация

1984-04-10—Подача