Изобретение относится к цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением.

Известные устройства для цикловой синхронизации осуществляют синхронизацию по комбинациям синхросигнала, передаваемым на определенных позициях цикла цифровой передачи.

Однако существуют цифровые передачи, в которых для обеспечения динамического временного уплотнения организуется цикл, который содержит n символов канала управления и символы, отведенные для объединяемых цифровых передач. Канал управления включает комбинацию синхросигнала, состоящую из m (m≤2) последовательных символов, служебные символы и (n-k) проверочных символов (n, k) линейного блокового кода.

Известны устройства для цикловой синхронизации [патент РФ №2019046 С1, патент РФ №2136111 C1], содержащие регистр сдвига, опознаватель циклового синхросигнала, анализатор совпадения синхросигнала, генераторное оборудование, элементы И, ИЛИ, входы и выходы устройства, соединенные определенным образом.

Недостатком данных устройств является высокая вероятность ложной цикловой синхронизации цифровых передач с синхросигналом, состоящим из одного-двух последовательных символов.

Наиболее близким по технической сущности к заявленному изобретению является выбранное в качестве прототипа устройство для цикловой синхронизации [Левин Л.С. Цифровые системы передачи информации / Л.С.Левин, М.А.Плоткин. - М.: Радио и связь, 1982. - С.102-103, рис.4.4], содержащее опознаватель синхросигнала, состоящий из регистра сдвига и дешифратора, цепи удержания и поиска синхронизма, генераторное оборудование, выделитель тактовой частоты, канальный распределитель, входы и выходы устройства.

Недостатком данного устройства является высокая вероятность ложной цикловой синхронизации цифровых передач с синхросигналом, состоящим из одного-двух последовательных символов.

Технической задачей изобретения является снижение вероятности ложной цикловой синхронизации цифровых передач, в которых цикл содержит символы объединяемых цифровых передач и n символов канала управления, включающего комбинацию синхросигнала, состоящую из m (m≤2) последовательных символов, служебные символы и (n-k) проверочных символов (n, k) линейного блокового кода.

Указанный технический результат достигается тем, что устройство для цикловой синхронизации, как и прототип, содержит регистр сдвига, выделитель тактовой частоты и канальный распределитель, сигнальные входы которых объединены и являются входом устройства, дешифратор, входы которого соединены с m выходами регистра сдвига, первый, второй и третий элементы И, первые входы которых объединены с первыми входами первого и второго элементов НЕТ, при этом вторые входы первого элемента И и первого элемента НЕТ объединены и соединены с синхронизирующим выходом генераторного оборудования, выход первого элемента И соединен со вторым входом первого элемента ИЛИ, выход которого подключен к обнуляющему входу накопителя по выходу из синхронизма, накапливающий вход которого соединен с выходом первого элемента НЕТ, а выход подключен к входу первого умножителя, выход которого соединен с первым входом первого сумматора, выход которого подключен к входу первого порогового устройства, выход которого соединен с первым входом четвертого элемента И, выход которого подключен к сбрасывающему входу генераторного оборудования и первому входу первого элемента ИЛИ, объединенные вторые входы второго и четвертого элементов И и второго элемента НЕТ соединены с выходом делителя частоты, выход второго элемента НЕТ соединен с первым входом триггера, выход которого подключен к второму входу третьего элемента И, выход которого соединен со вторым входом триггера, сбрасывающим входом делителя частоты и вторым входом второго элемента ИЛИ, первый вход которого соединен с выходом второго элемента И, а выход подключен к входу накопителя по входу в синхронизм, выход которого соединен с входом второго умножителя, выход которого подключен к второму входу первого сумматора, выход выделителя тактовой частоты соединен с объединенными тактовыми входами делителя частоты и генераторного оборудования, адресные выходы которого подключены к входам канального распределителя.

Особенность заключается в том, что количество ячеек регистра сдвига равно числу символов кодового слова (n, k) линейного блокового кода, применяемого в канале управления цифровой передачи, а также дополнительно введены второе пороговое устройство, пятый элемент И и второй сумматор, входы которого соединены с n выходами регистра сдвига, а (n-k) выходов подключены к входам второго порогового устройства, выход которого, соединен со вторым входом пятого элемента И, первый вход которого соединен с выходом дешифратора, а выход подключен к объединенным первым входам первого, второго, третьего элементов И и первого, второго элементов НЕТ.

Система синхронизации, использующая цикловой синхросигнал, описывается двумя вероятностями - вероятностью пропуска циклового синхросигнала и вероятностью ложной цикловой синхронизации [Былянски П. Цифровые системы передачи / П.Былянски, Д.Ингрем; Пер. с англ. / Под ред. А.А.Визеля. - М.: Связь, 1980. - С.99-101; Скляр Б. Цифровая связь. Теоретические основы и практическое применение / Б.Скляр. - Изд. 2-е, испр.: Пер. с англ. - М.: Издательский дом «Вильямс», 2003. - С.659-663; Крухмалев В.В. Цифровые системы передачи / В.В.Крухмалев, В.Н.Гордиенко, А.Д.Моченов. - М.: Горячая линия - Телеком, 2007. - С.251-253].

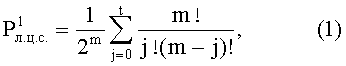

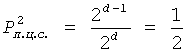

При условии, что вероятности появления «0» и «1» на любой позиции одинаковы и равны 0,5, вероятность ложной цикловой синхронизации, вызванная m битами случайной последовательности данных, при анализе одного цикла описывается выражением (1).

где t - количество ошибок, допускаемых в цикловом синхросигнале схемой синхронизации.

Уменьшение вероятности ложной цикловой синхронизации цифровых передач с цикловым синхросигналом, состоящим из одного-двух символов, возможно за счет использования свойств канала управления, в котором применяется (n, k) линейный блоковый код.

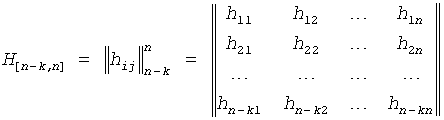

Проверочная матрица (n, k) линейного блокового кода имеет вид:

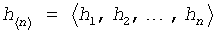

Каждая строка проверочной матрицы H[n-k,n] представляет собой проверочный вектор  , состоящий из n элементов. Так как каждый проверочный вектор

, состоящий из n элементов. Так как каждый проверочный вектор  отражает проверку на четность, введенную для любой кодовой комбинации, то при отсутствии ошибок скалярное произведение любой кодовой комбинации

отражает проверку на четность, введенную для любой кодовой комбинации, то при отсутствии ошибок скалярное произведение любой кодовой комбинации  на этот вектор, определяемое выражением (2), равно нулю

на этот вектор, определяемое выражением (2), равно нулю

Для кодовой комбинации длиной n символов возможно 2n событий. Из них 2k событий соответствуют разрешенным. Тогда при условии, что ошибки в кодовых комбинациях линейного блокового кода схемой цикловой синхронизации не допускаются, вероятность ложной цикловой синхронизации при анализе одного цикла описывается выражением (3)

При проверке d символов на четность в кодовой комбинации длиной n (d≤n) символов число всех возможных событий равно 2d; число событий, удовлетворяющих условию четности, равно 2d-1. Вероятность имитации четности проверяемых символов случайной последовательностью данных равна

Если используется несколько проверочных векторов, вероятность ложной цикловой синхронизации описывается выражением (4)

где i=1, 2, …, n-k - число проверочных векторов, используемых для обнаружения кодовых слов линейного блокового кода.

Минимальное значение вероятности ложной цикловой синхронизации достигается при i=n-k.

При цикловой синхронизации как по комбинациям синхросигнала, так и по комбинациям кодовых слов линейного блокового кода, применяемого в канале управления цифровой передачи, вероятность ложной цикловой синхронизации равна произведению вероятностей  и

и  , т.е.

, т.е.

, при этом

, при этом  ,

,

Предлагаемое устройство иллюстрируется чертежами, на которых изображены:

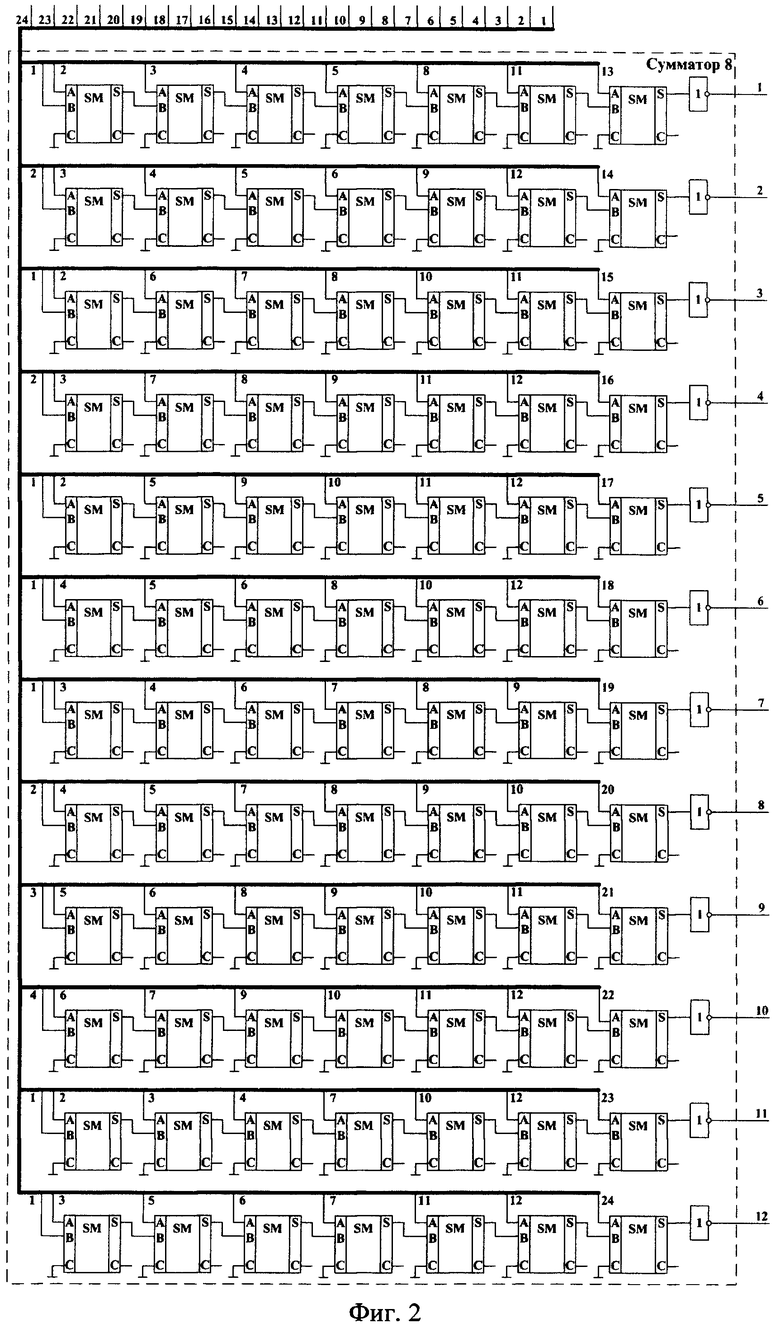

фиг.1 - структурная схема устройства для цикловой синхронизации;

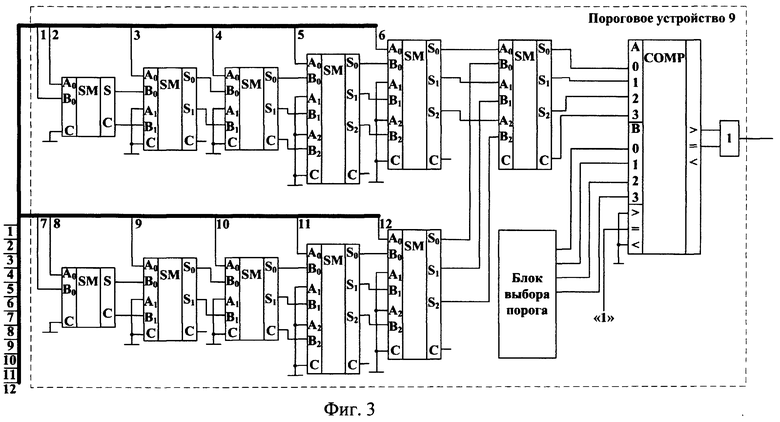

фиг.2 - функциональная схема сумматора 8;

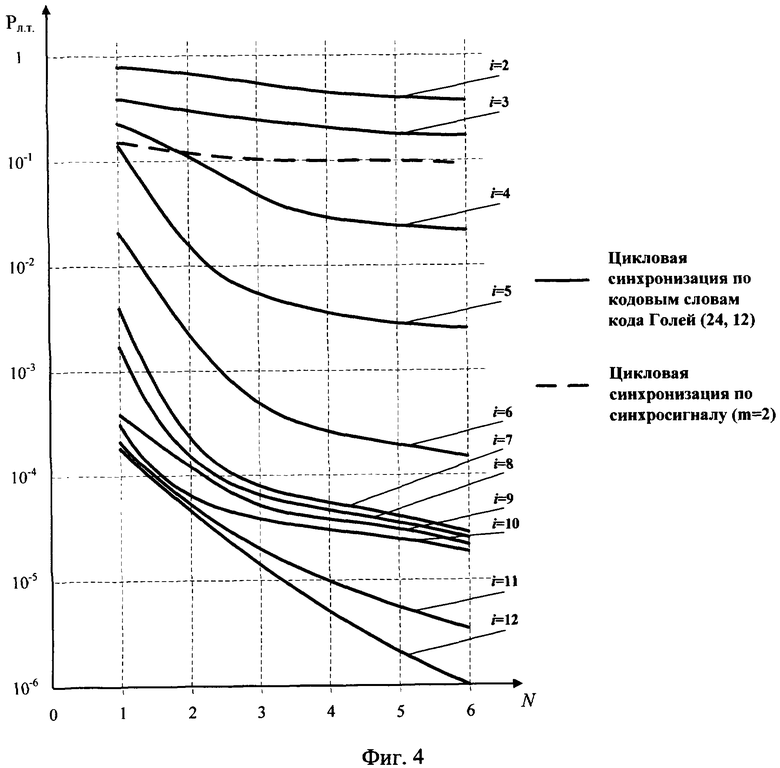

фиг.3 - функциональная схема порогового устройства 9;

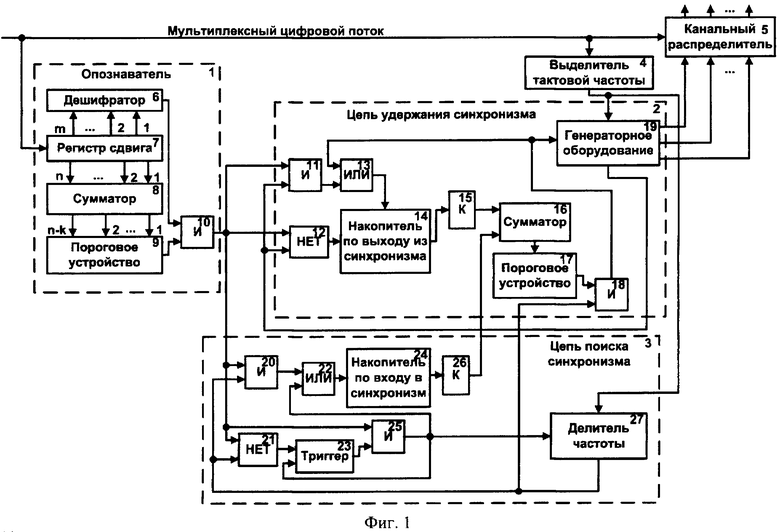

фиг.4 - зависимость вероятности ложной цикловой синхронизации от количества анализируемых циклов, полученная при имитационном моделировании.

Устройство для цикловой синхронизации (фиг.1) содержит опознаватель 1 синхросигнала, цепь 2 удержания синхронизма, цепь 3 поиска синхронизма, выделитель 4 тактовой частоты, канальный распределитель 5. При этом опознаватель 1 синхросигнала содержит регистр 7 сдвига с числом ячеек, равным количеству символов кодовой комбинации (n, k) линейного блокового кода, применяемого в канале управления, дешифратор 6, второй сумматор 8, второе пороговое устройство 9, пятый элемент И 10. Цепь 2 удержания синхронизма содержит первый элемент И 11, первый элемент НЕТ 12, первый элемент ИЛИ 13, накопитель 14 по выходу из синхронизма, первый умножитель К 15, первый сумматор 16, первое пороговое устройство 17, четвертый элемент И 18, генераторное оборудование 19. Цепь 3 поиска синхронизма содержит второй элемент И 20, второй элемент НЕТ 21, второй элемент ИЛИ 22, триггер 23, накопитель 24 по входу в синхронизм, третий элемент И 25, второй умножитель К 26, делитель 27 частоты. При этом вход регистра 7 сдвига является сигнальным входом устройства для цикловой синхронизации. Отводы с первого по m-й регистра 7 сдвига подключены к входным отводам дешифратора 6, отводы с первого по n-й регистра 7 сдвига подключены к входным отводам второго сумматора 8, выходные отводы которого с первого по (n-k)-й подключены к входным отводам второго порогового устройства 9. Выходы второго порогового устройства 9 и дешифратора 6 подключены к второму и первому входам соответственно пятого элемента И 10, выход которого подключен к объединенным первым входам первого элемента И 11, первого элемента НЕТ 12, второго элемента И 20, второго элемента НЕТ 21, третьего элемента И 25. К вторым входам первого элемента И 11, первого элемента НЕТ 12 подключен синхронизирующий выход генераторного оборудования 19. Выход первого элемента И 11 соединен со вторым входом первого элемента ИЛИ 13, выход которого соединен с обнуляющим входом накопителя 14 по выходу из синхронизма, накапливающий вход которого соединен с выходом первого элемента НЕТ 12. Выход накопителя 14 по выходу из синхронизма подключен к входу первого умножителя К 15, выход которого подключен к первому входу первого сумматора 16. Выход первого сумматора 16 подключен к входу первого порогового устройства 17, выход которого подключен к первому входу четвертого элемента И 18. Выход четвертого элемента И 18 подключен к сбрасывающему входу генераторного оборудования 19 и первому входу первого элемента ИЛИ 13. К вторым входам четвертого элемента И 18, второго элемента И 20, второго элемента НЕТ 21 подключен выход делителя 27 частоты. Выход второго элемента НЕТ 21 соединен с первым входом триггера 23, выход которого подключен к второму входу третьего элемента И 25. Выход третьего элемента И 25 подключен к сбрасывающему входу делителя 27 частоты и вторым входам триггера 23 и второго элемента ИЛИ 22, к первому входу которого подключен выход второго элемента И 20. Выход второго элемента ИЛИ 22 подключен к входу накопителя 24 по входу в синхронизм, выход которого подключен к входу второго умножителя К 26. Выход второго умножителя К 26 подключен к второму входу первого сумматора 16. Выход выделителя 4 тактовой частоты подключен к тактовому входу делителя 27 частоты и тактовому входу генераторного оборудования 19, адресные выходы которого подключены к адресным входам канального распределителя 5.

Устройство для цикловой синхронизации (фиг.1) работает следующим образом. Мультиплексный цифровой поток поступает на вход опознавателя 1 синхросигнала, состоящего из регистра 7 сдвига с числом ячеек, равным количеству символов кодовой комбинации (n, k) линейного блокового кода, применяемого в канале управления, дешифратора 6, второго сумматора 8, второго порогового устройства 9, пятого элемента И 10. В течение каждого тактового интервала в регистр 7 сдвига записывается один символ принимаемого сигнала, причем с приходом очередного символа предыдущий продвигается в следующую ячейку. Если в регистре 7 сдвига содержится кодовая комбинация (n, k) линейного блокового кода, включающая комбинацию синхросигнала (первые m последовательных символов), то в случае приема без ошибок первая вызывает формирование сигналов на всех (n-k) выходах второго сумматора 8, а последняя - формирование сигнала не выходе дешифратора 6. Сигнал на выходе дешифратора 6 отражает совпадение первых m символов кодовой комбинации, записанной в регистре 7 сдвига, с комбинацией синхросигнала, а каждый сигнал на выходе второго сумматора 8 - результат скалярного произведения кодовой комбинации из n символов и одного из (n-k) проверочных векторов (2).

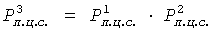

Второй сумматор 8 в совокупности с регистром 7 сдвига представляют собой типовую схему вычисления синдрома при декодировании линейных блоковых кодов [Кларк Дж. Кодирование с исправлением ошибок / Дж.Кларк, Дж.Кейн; Пер. с англ. - М.: Радио и Связь, 1987. - С.53-96; Скляр Б. Цифровая связь. Теоретические основы и практическое применение / Б.Скляр. - Изд. 2-е, испр.: Пер. с англ. - М.: Издательский дом «Вильямс», 2003. - С.354-367]. Например, на фиг.2 представлена функциональная схеме второго сумматора 8 для частного случая, когда в канале управления цифровой передачи применяется код Голея (24, 12) с проверочной матрицей вида:

.

.

В данном случае второй сумматор 8, на входе и выходе которого 24 и 12 выводов соответственно, состоит из совокупности одноразрядных двоичных сумматоров, подключенных к его входам в соответствии с представленной проверочной матрицей.

В случае приема с ошибками, в зависимости от их количества и местоположения в кодовой комбинации (n, k) линейного блокового кода, последняя не вызовет формирования сигналов на определенных выходах второго сумматора 8. Количество сформированных на выходах второго сумматора 8 сигналов, равное или превышающее установленный порог, вызывает формирование сигнала на выходе второго порогового устройства 9. При нулевом пороге, установленном на втором пороговом устройстве 9, на выходе опознавателя 1 синхросигнала формируется сигнал только при обнаружении комбинации синхросигнала.

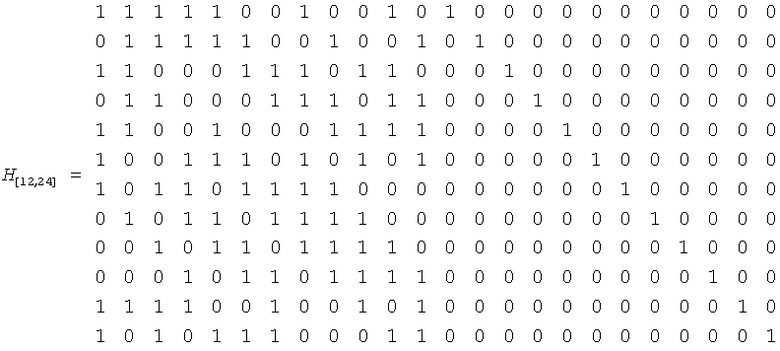

Второе пороговое устройство 9 представляет собой комбинационную схему, имеющую k входов и один выход и реализующую функцию [Пухальский Г.И. Цифровые устройства: Учебное пособие для втузов / Г.И.Пухальский, Т.Я.Новосельцева. - СПб.: Политехника, 1996. - С.553-556]

,

,

где ν=(xk, …, xi, …, x1), xi - сигнал на i-м входе порогового устройства 9; l - установленный порог, 1≤l≤k.

На фиг.3 представлена функциональная схема второго порогового устройства 9 для частного случая, когда в канале управления цифровой передачи применяется код Голея (24, 12). Второе пороговое устройство 9 состоит из совокупности двоичных сумматоров, позволяющих подсчитать количество поступивших сигналов, блока выбора порога, с помощью которого задается порог l, цифрового компаратора, осуществляющего сравнение числа поступивших сигналов с порогом l, и элемента логического ИЛИ. Если количество поступивших сигналов больше или равно порогу l, то на выходе элемента логического ИЛИ, являющегося выходом второго порогового устройства 9, формируется единичный сигнал.

Сигнал обнаружения комбинации синхросигнала с дешифратора 6 и сигнал обнаружения кодовой комбинации линейного блокового кода, применяемого в канале управления, со второго порогового устройства 9 поступают на пятый элемент И 10. При одновременности данных событий на выходе пятого элемента И 10 формируется сигнал, поступающий на первый элемент И 11, первый элемент НЕТ 12, второй элемент И 20, второй элемент НЕТ 21 и третий элемент И 25. Если устройство цикловой синхронизации находится в состоянии синхронизма, то сигнал с выхода опознавателя 1 синхросигнала совпадает по времени с сигналом с выхода генераторного оборудования 19, поступающего на первый элемент И 11, первый элемент НЕТ 12. При этом на выходе первого элемента НЕТ 12, соединенного с накопительным входом накопителя 14 по выходу из синхронизма, сигнал отсутствует, а на выходе первого элемента И 11, соединенного через первый элемент ИЛИ 13 с обнуляющим входом накопителя 14 по выходу из синхронизма, формируется сигнал, обнуляющий накопитель 14 по выходу из синхронизма (рассчитанный, обычно, на четыре-шесть следующих подряд импульсов). Ложные комбинации синхросигнала и линейного блокового кода, формируемые в мультиплексном цифровом потоке вследствие случайного сочетания единиц и нулей, не совпадают по времени с сигналом на выходе генераторного оборудования 19, а следовательно, и не участвуют в процессе накопления. Благодаря совпадению временных положений импульсных последовательностей с выходов опознавателя 1 синхросигнала и делителя 27 частоты (коэффициент деления которого равен коэффициенту деления генераторного оборудования 19) накопитель 24 по входу в синхронизм оказывается заполненным, а триггер 23 удерживает третий элемент И 25 в закрытом состоянии, при котором ложные комбинации синхросигнала, формирующиеся в мультиплексном цифровом потоке, не вызывают сброса делителя 27 частоты. Разрешающий сигнал с выхода накопителя 24 по входу в синхронизм (рассчитанного, обычно, на два-три следующих подряд импульса) поступает на второй вход первого сумматора 16 через второй умножитель К 26, где он умножается на коэффициент, соответствующий весу сигнала. В первом сумматоре 16 производится суммирование сигналов с выходов накопителя 14 по выходу из синхронизма и накопителя 24 по входу в синхронизм с учетом коэффициентов первого умножителя К 15 и второго умножителя К 26. Сброс генераторного оборудования 19 производится только в случае достижения суммарной емкостью накопителей уровня, установленного первым пороговым устройством 17. При сбое синхронизма накопитель 14 по выходу из синхронизма заполняется и вырабатывает разрешающий сигнал. Однако четвертый элемент И 18 остается закрытым до тех пор, пока на вход первого сумматора 16 не будет подан разрешающий сигнал с выхода накопителя 24 по входу в синхронизм, и суммарная емкость накопителей не превысит уровень, установленный первым пороговым устройством 17. В цепи 3 поиска синхронизма третий элемент И 25 открывается сигналом с выхода триггера 23, и первый же ложный синхросигнал, сформировавшийся в мультиплексном цифровом потоке, установит делитель 27 частоты и триггер 23 в нулевое состояние. В результате третий элемент И 25 оказывается закрытым до тех пор, пока на анализируемых позициях не сформируется комбинация символов, отличающаяся от синхронизирующей, после чего следующий ложный синхросигнал вновь установит делитель 27 частоты и триггер 23 в нулевое состояние. При обнаружении истинного синхросигнала накопитель 24 по входу в синхронизм заполняется и вырабатывает разрешающий сигнал, который поступает через второй умножитель К 26 на первый сумматор 16. Если к этому моменту накопитель 14 по выходу из синхронизма уже заполнен и сумма сигналов на входе первого порогового устройства 17 превышает заданный порог, сигнал с выхода делителя 27 частоты устанавливает генераторное оборудование 19 в нулевое состояние. При длительном искажении синхросигнала состояние циклового синхронизма удерживается сколь угодно долго благодаря отсутствию разрешающего сигнала из цепи 3 поиска синхронизма.

Предлагаемое изобретение по сравнению с прототипом имеет более низкую вероятность ложной цикловой синхронизации цифровых передач, в которых цикл содержит символы объединяемых цифровых передач и n символов канала управления, включающего комбинацию синхросигнала, состоящую из m (m≤2) последовательных символов, служебные символы, и (n-k) проверочных символов (n, k) линейного блокового кода, так как цикловая синхронизация осуществляется как по комбинациям синхросигнала, так и по кодовым словам (n, k) линейного блокового кода, применяемого в канале управления.

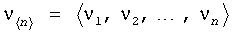

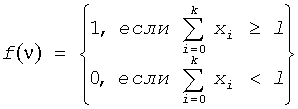

Для определения качественных показателей устройства для цикловой синхронизации была построена его имитационная модель.

Моделирование производилось при следующих исходных данных:

- ошибки в канале связи отсутствуют (t=0);

- вероятности появления «0» и «1» на любых позициях не одинаковы;

- длина цикла передачи L=2048 бит;

- длина синхрокомбинации m=2 (01);

- применяемый в канале управления цифровой передачи линейный блоковый код: код Голея (24, 12);

- число используемых проверочных векторов: i=2÷12;

- число анализируемых циклов N=1÷6;

- порог на пороговом устройстве в опознавателе синхросигнала: 0.

В результате моделирования устройство показало характеристики, которые представлены на фиг.4 (пунктиром указаны характеристики прототипа).

Моделирование подтвердило достижение технического результата - снижение вероятности ложной цикловой синхронизации - при осуществлении изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Устройство для синхронизации по циклам | 1988 |

|

SU1690209A1 |

Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением. Технический результат - снижение вероятности ложной цикловой синхронизации цифровых передач, в которых цикл содержит символы объединяемых цифровых передач и n символов канала управления, включающего комбинацию синхросигнала, состоящую из m (m≤2) последовательных символов, служебные символы, и (n-k) проверочных символов (n, k) линейного блокового кода. Для этого в устройство для цикловой синхронизации, содержащее регистр сдвига, дешифратор, генераторное оборудование, выделитель тактовой частоты, канальный распределитель, четыре элемента И, два элемента НЕТ, два элемента ИЛИ, накопители по входу и выходу из синхронизма, первый сумматор, первое пороговое устройство, два умножителя, триггер и делитель частоты введены второй сумматор, второе пороговое устройство, пятый элемент И и количество ячеек регистра сдвига равно числу символов кодового слова (n, k) линейного блокового кода, применяемого в канале управления цифровой передачи. 4 ил.

Устройство для цикловой синхронизации, содержащее регистр сдвига, выделитель тактовой частоты и канальный распределитель, сигнальные входы которых объединены и являются входом устройства, дешифратор, входы которого соединены с m выходами регистра сдвига, первый, второй и третий элементы И, первые входы которых объединены с первыми входами первого и второго элементов НЕТ, при этом вторые входы первого элемента И и первого элемента НЕТ объединены и соединены с синхронизирующим выходом генераторного оборудования, выход первого элемента И соединен со вторым входом первого элемента ИЛИ, выход которого подключен к обнуляющему входу накопителя по выходу из синхронизма, накапливающий вход которого соединен с выходом первого элемента НЕТ, а выход подключен к входу первого умножителя, выход которого соединен с первым входом первого сумматора, выход которого подключен к входу первого порогового устройства, выход которого соединен с первым входом четвертого элемента И, выход которого подключен к сбрасывающему входу генераторного оборудования и первому входу первого элемента ИЛИ, объединенные вторые входы второго и четвертого элементов И и второго элемента НЕТ соединены с выходом делителя частоты, выход второго элемента НЕТ соединен с первым входом триггера, выход которого подключен к второму входу третьего элемента И, выход которого соединен со вторым входом триггера, сбрасывающим входом делителя частоты и вторым входом второго элемента ИЛИ, первый вход которого соединен с выходом второго элемента И, а выход подключен к входу накопителя по входу в синхронизм, выход которого соединен с входом второго умножителя, выход которого подключен к второму входу первого сумматора, выход выделителя тактовой частоты соединен с объединенными тактовыми входами делителя частоты и генераторного оборудования, адресные выходы которого подключены к входам канального распределителя, отличающееся тем, что количество ячеек регистра сдвига равно числу символов кодового слова (n, k) линейного блокового кода, применяемого в канале управления цифровой передачи, а также дополнительно введены второе пороговое устройство, пятый элемент И и второй сумматор, входы которого соединены с n выходами регистра сдвига, a (n-k) выходов подключены к входам второго порогового устройства, выход которого соединен со вторым входом пятого элемента И, первый вход которого соединен с выходом дешифратора, а выход подключен к объединенным первым входам первого, второго, третьего элементов И и первого, второго элементов НЕТ.

| ЛЕВИН Л.С., ПЛОТКИН М.А | |||

| Цифровые системы передачи информации | |||

| - М.: Радио и связь, с.102, 103, рис.4.4 | |||

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2342796C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1998 |

|

RU2136111C1 |

| US 5969631 А, 19.10.1999 | |||

| US 5778010 А, 07.07.1998 | |||

| DE 10046920 А1, 25.04.2002. | |||

Авторы

Даты

2012-05-10—Публикация

2009-07-01—Подача