и выходы 10 канала. Каждый канал содержит регистр адреса канала, два коммутатора, сумматор по модулю два, триггер. Блок управления содержит m узлов, по одному на каждую шину информационной магистрали, узел содержит четыре двухвходовых элемента И, два двухвходовых элемента ИЛИ,

асинхронньй RS-триггер типа MS, асин- хронньй RS-триггер. В устройстве с целью сокращения времени опроса применен блок управления, который путем предварительного анализа информации на магистрали позволяет сравнивать приоритеты отдельных источников по значимым разрядам. 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072047A1 |

| Резервированная измерительная система | 1990 |

|

SU1781682A1 |

| Многоканальное устройство приоритетного обслуживания | 1989 |

|

SU1675886A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ АБОНЕНТОВ К ОБЩЕЙ МАГИСТРАЛИ | 2011 |

|

RU2444780C1 |

| Многорежимное устройство приоритета | 1990 |

|

SU1805469A1 |

| Многоканальное устройство для сопряжения вычислительных машин | 1986 |

|

SU1322302A1 |

| Устройство связи для вычислительной системы | 1984 |

|

SU1164722A1 |

| Устройство для сопряжения группы из М вычислительных машин с группой из К абонентов | 1986 |

|

SU1310830A1 |

| Устройство для сопряжения группы каналов ЭВМ с группой периферийных устройств | 1987 |

|

SU1520529A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия устройства. Многоканальное устройство для подключения абонентов к общей магистрали содержит общую информационную магистраль 7, в которую входят m шин, шину подачи счетных импульсов 2, п каналов 8 устройства, магистраль управления 6, в которую входят m шин, об- ций блок управления 1, шину сброса 3, шину блокировки прохождения сигналов запроса 11, шину окончания анализа устройства 5, шину записи информации в блок управления 4, резисторы 12, источник напряжения 34, входы 9 « (Л 4: сл

1

Изобретение относится к области вычислительной техники и может быть использовано для подключения периферийных устройств к общей магистрали.

Целью изобретения является повы- шение быстродействия за счет предварительного анализа поразрядной логической суммы адресов каналов, в которые поступают запросы, и последуинце™ го сравнения только тех разрядов, поразрядная логическая сумма которьк равна единице и по которым адреса каналов отлнгчаются друг от друга.

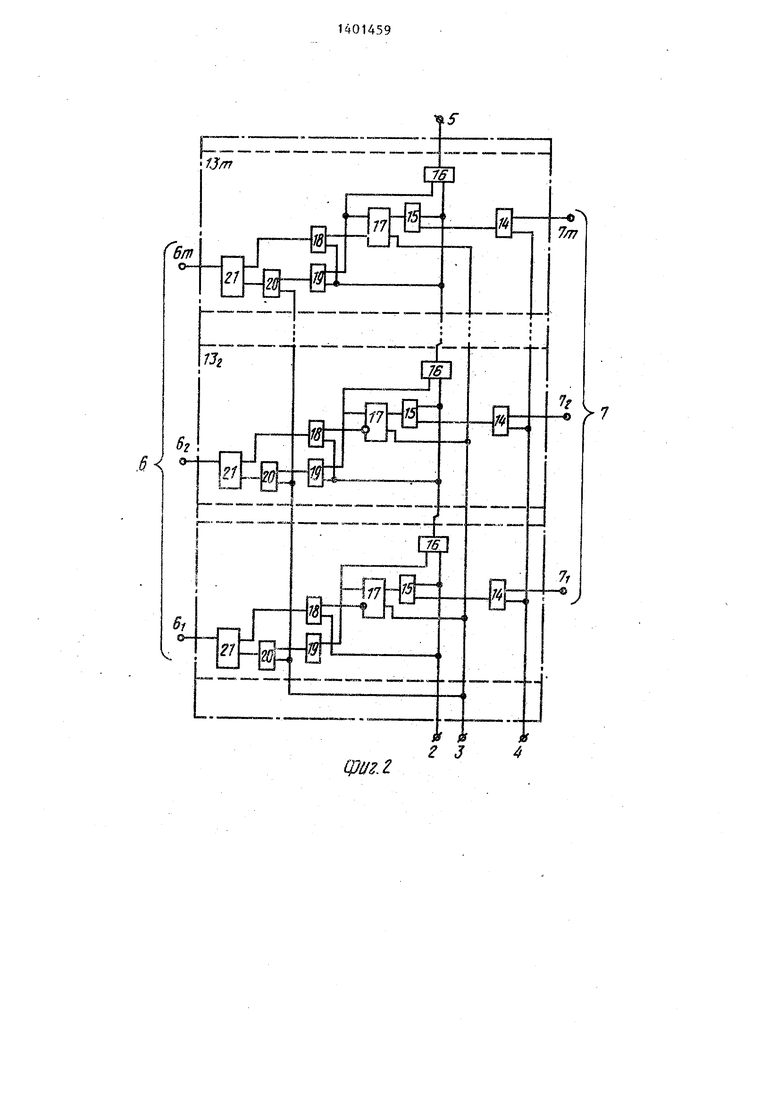

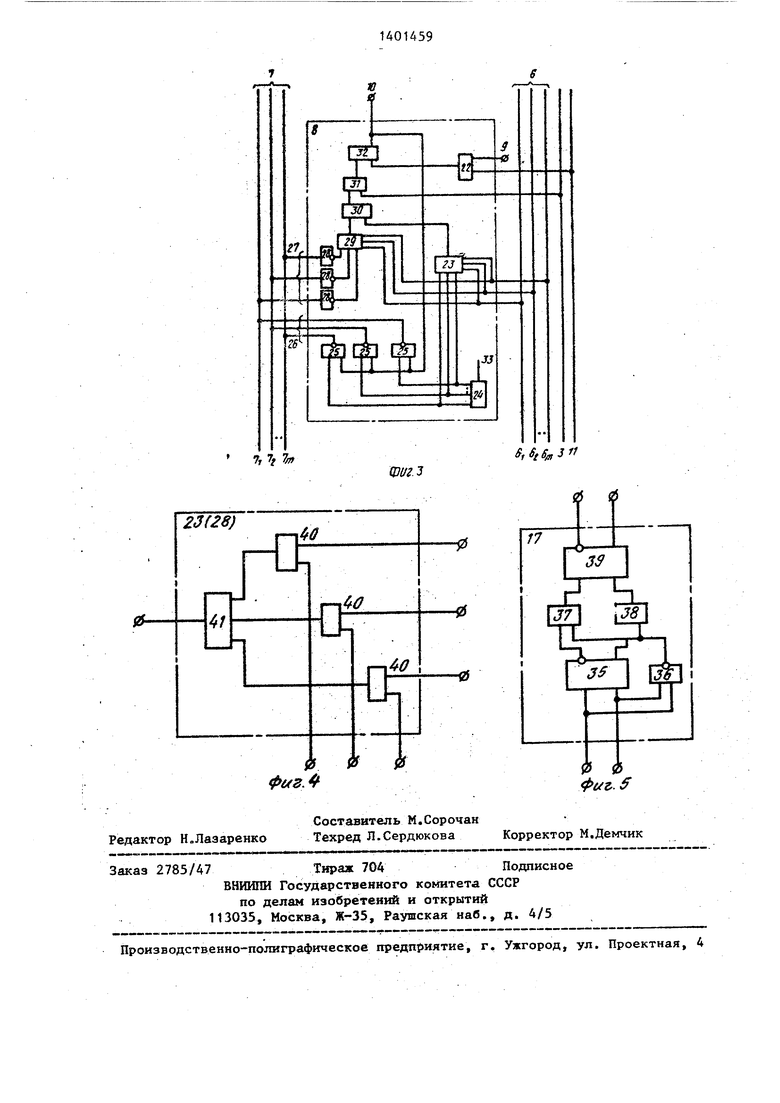

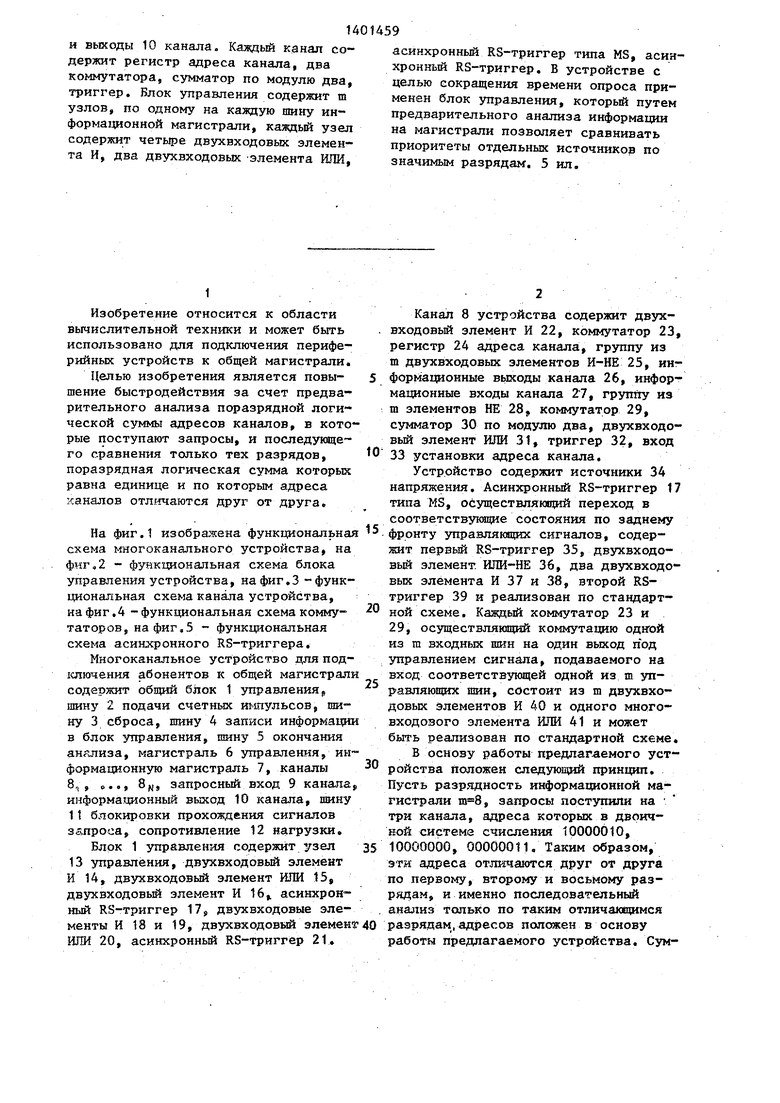

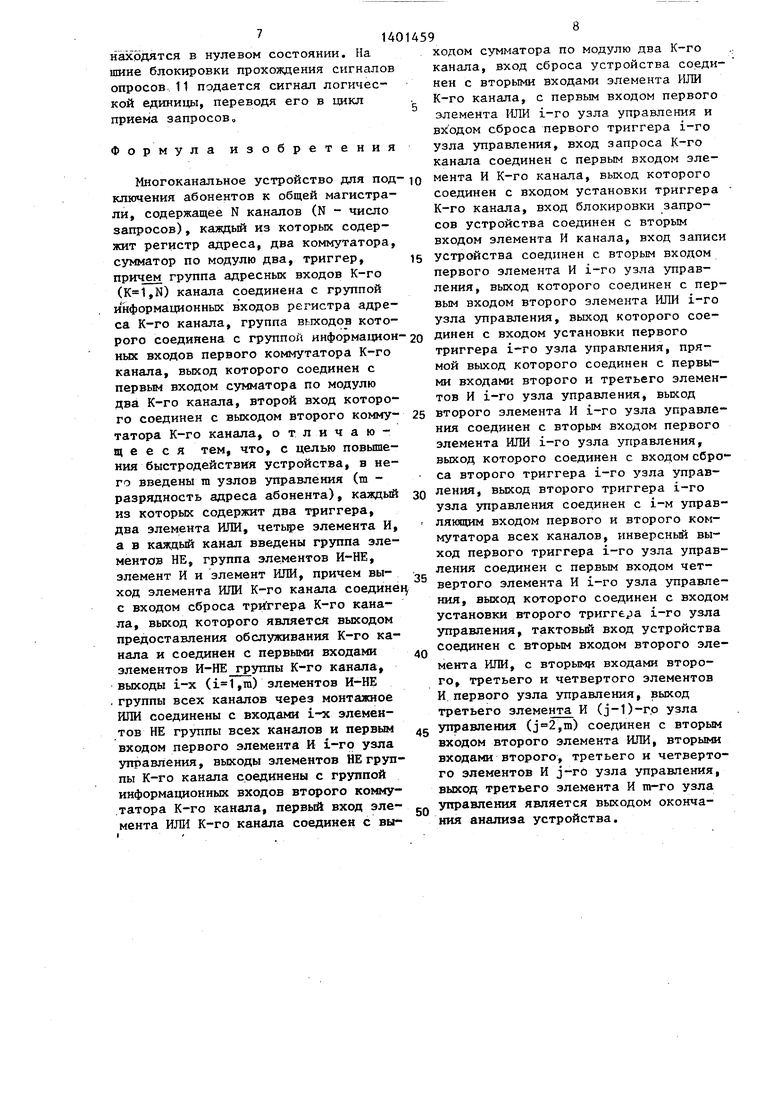

На фиг.1 изображена функциональная схема многоканального устройства, на фиг,2 - функциональная схема блока управления устройства, на фиг.З -функциональная схема канала устройства, на фиг, 4-функциональная схема комму- таторов, на фиг,5 - функциональная схема асинхронного RS-триггера,

Многоканальное устройство для под- ютючения абонентов к общей магистрали содержит общий блок 1 управления,, шину 2 подачи счетных шшульсов, шину 3 сброса, шину 4 записи информации в блок управления, шину 5 окончания анйлиза, магистраль 6 управления, ин формационную магистраль 7, каналы 8,, е,,, 8, запросный вход 9 канала, информационный выход 10 канала, шину 11 блокировки прохождения сигналов запроса, сопротивление 12 нагрузки.

Блок 1 управления содержит узел 13 управления, двухвходовый элемент И 14, двухвходовый элемент ИЛИ 15, двухвходовьй элемент И 16 асинхронный RS-триггер 17, двухвкодовые элементы И 18 и 19, двухвходовый элемен-г ИЛИ 20, асинхронньй RS-триггер 21.

Канал 8 устройства содержит двзгх- входовьй элемент И 22, коммутатор 23, регистр 24 адреса канала, группу из m двухвходовых элементов И-НЕ 25, информационные вьссоды канала 26, информационные входы канала 27, группу из га элементов НЕ 28, коммутатор 29, сумматор 30 по модулю два, двухвходовьй элемент ИЛИ 31, триггер 32, вход 33 установки адреса канала.

Устройство содержит источники 34 напряжения. Асинхронный RS-триггер 17 типа MS, осуществляющий переход в соответствуклцие состояния по заднему фронту управляющих сигналов, содержит первый RS-триггер 35, двухвходовьй элемент, ШШ-НЕ 36, два двухвходовых элемента И 37 и 38, второй RS- триггер 39 и реализован по стандартной схеме. Каждый коммутатор 23 и 29, осуществляющий коммутацию одной из m входных шин на один выход пЪд зшравлением сигнала, подаваемого на вход соответствующей одной из m управляющих шин, состоит из m двухвходовых элементов И 40 и одного много- входового элемента ИЛИ 41 и мак&т быть реализован по стандартной схеме,

В основу работы предлагаемого устройства положен следующий принцип. Пусть разрядность информационной магистрали , запросы поступшш на три канала, адреса которых в двоичной системе счисления 10000010, 10000000, 00000011, Таким образом, эти адреса отличаются друг от друга по первому, второму и восьмому разрядам, и именно последовательный анализ только по таким отличающимся разрядам, адресов положен в основу работы предлагаемого устройства, Сум- 1Д

парный код (поразрядная логическая сумма) для рассматриваемого случая 10000011. Обратное значение этого кода 01111100, Если организовать по- следовательное прибавление единицы к этому значению в коде Джонсона, считая, что левьй разряд самый младший, получим последовательно такие числа:

1+01111100 11111100; 1+11111100 11111110; 1+11111110 11111111; 1+

+ 11111111 11111111+перенос.

Таким образом, переход значения разрядов из нуля в единицу последовательно осуществляется именно в тех разрядах, которые необходимо анализировать для вьщвления самого приоритетного канала. Появление переноса свидетельствует об окончании анализа. Именно по этомз принципу осуще- ствляется работа устройства и вьде- ление сигнала окончания анализа.

Устройство работает следуютдим об- разом.

В регистре 24 канала хранится ад- рее данного канала, устанавливаемый с входа 33 установки адреса, соответствующий критерию его приоритета и представляющий собой двоичное m разрядное число. Работа устройства может проходить в одном из режимов: цикл приема запросов и цикл анализов устройства, Б цикле приема запросов на шине 11 блокировки прохождения сигналов запросов присутствует сигнал логической единицы, который, поступая на первый вход всех элементов И 22 каналов 8, разрешает прохождение сигналов запросов в каналы устройства. Сигнал запроса, поступающий в виде сигнала логической единицы в цикле приема запросов по запросному входу канала 9 в i-й канал через элемент И 22 канала 8, поступает на .вход установки триггера 32 и устанав- ливает его в единичное состояние. Сигнал логической единицы, снимаемьй с единичного выхода этого триггера, поступает на выход канала 10 и на вторые входы элементов 25. Вы- ходы каждого i-ro элемента (,2,„,„ ..,,т) И-НЕ 25 всех-каналов соединены по схеме открытого коллектора, реализуя для каждого разряда функцию И-ИЛИ-НЕ (проводное HJM)„ Таким об- разом, при поступлении нескольких запросов в соответствующие каналы устройства на каждой шине информационной магистрали 7 формируется обрат-

59

ное значение логической суммы значений одноименных разрядов адресов тех каналов, куда поступили запросы,

В цикле анализа устройства, который наступает при постлтлении одного или нескольких сигналов запросов, на шину блокировки запросов подается сигнал логического нуля, которьш сохраняется до окончания цикла анализа и который блокирует устройство от сбоев при поступлении сигналов запросов в цикле анализа. На шину 4 записи инфopмaIJJiи подается сигнал логической единицы, и значение разряда информационной магистрали через элементы И 14, ИЛИ 15 блока управления поступает на установочные коды триггеров 17.

Пусть j - номер первого слева триггера 17 (в j-M узле блока управ- ле;:ия), находящегося в нулевом состоянии, 1 - номер второго слева триггера 17, находящегося в нулевом состоянии, г - третьего и т.д. Общее количество триггеров 17, находящихся в нулевом состоянии К. Триггеры 17 в узлах 1,2,...,j-1,j+1,j+2,...,1-1, l+ljl+2 и т.д. находятся в единичном состоянии. С их единичного выхода С тамаются сигналы логической единицы, которые поступают на первые входы элементов И 16 и на вторые входы элементов И 19 в тех же узлах. С нулевого выхода этих же триггеров снимаются сигналы логического нуля, которые поступают и на вторые входы элемента Р1 18. Триггер 17 в узле j находится в нулевом состоянии. С его единичного выхода снимается сигнал логического нуля, который поступает на первьй вход элемента И 16 и на второй вход элемента И 19, сигнал логической единицы, снимаемый с его нулевого выхода, поступает на второй вход элемента И 18, выход которого заведен на установочный вход триггера 21. Все триггеры 21 блока управления находятся в нулевом состоянии, и на шинах 6 магистрали управления отсутствуют управляющие сигналы. При подаче первого счетного импульса в виде сигнала логической единицы на шину 2 счетных импульсов на выходе элемента И 16 первого узла появляется сигнал логической единицы, который поступает во 2-й узел, на выходе элемента И 16 также появляется сигнал логической единицы, который распро-

страняясь доходит до элемента И 16 j-ro узла и дальше не идет. Одновременно сигнал логической единшды поступает на вторые входы элементов И 18 и 19 и на второй вход элемента ИЛИ 15 в узлах 1,2,.,,,j-1. Триггеры 17 и 21 в узлах i,2,...,j-1 не изменяют своего состояния. Сигнал логической единицы через элемент ИЛИ 15 в J-M узле подается на вход установки триггера 17, который однако не изменяет своего состояния до его сйятия, Сигнал логической единицы через элемент И 18 подается на установочный вход триггера 21 j-ro узла, которьй переходит в единичное состояние, и на j-й шине магистрали управления появляется сигнал логической единицы. При снятии счетного импульса по его заднему фронту триггер 17 в j-M канале устанавливается в единичное состояние, при этом на второй вход элемента И 19 и на первый вход элемента И 16 подается сигнал логической еди- ницы. Сигнал логической единицы, по- даваемьй по j-й шине магистрали управ ления,поступает на j-e управлякяцие входы первого и второго коммутаторов 23 и 29 каналов устройства. Значение j-ro разряда в каждом канале устрой- ства через коммутатор 23 подается на второй вход cyi iaTopa 30 по модулю два, обратное значение логической суммы адресов каналов подается на элементы НЕ 28 и инвертируется, и через коммутатор 29 на первый вход сзлчматора 30 по модулю два подается логическая сумма j-x разрядов адресов каналов, подключенных к информацион ной магистрали . Если в каком-то канале сумма по модулю два j-ro разряда его адреса и поразрядная сумма всех j-x разрядов равна единице, то это означает, что адрес данного канала меньше адресов каких-то других кана лов в устройстве, на которые поступили запросы, В этом случае с выхода сумматора 30 по модулю два сигнал ло- псческой единицы через элемент ИЖ 31 подается на сбросов 1й вход триггера 32, устанавливая его в нулевое состояние. Сигнал логического иуля с его единичного выхода подается на вторые входы элементов И-НЕ 25 кана- ла, отключая канал от дальнейшего анализа, Если же на выходе сумматора 30 по модулю два вырабатывается логический нуль, то данный канал участвует в дальнейшем анализе. При подаче второго счетного импульса, который последовательно проходит через элементы И 16 блока управления до элемента И 16 в 1-м узле, на первьй вход элемента И 19 j-ro узла подается сигнал логической единицы, С выхода этого элемента снимается сигнал логической единицы, который через элемент ИЛИ 20 подается на сбросовый вход Триггера 21, переводя его в нулевое состояние, в результате чего управляющий сигнал снимается с j-й шины магистрали управления. Счетный им- пульс, дойдя до 1-го узла, подается на первые входы элементов И 18 и 19 и на второй элемент ИЛИ 15, По аналогии с j-M узлом на 1-й шине магистрали управления вырабатьгеается управляющий сигнал логической единицы, который сохраняется до прихода следующего счетного импульса и по которому анализируются 1-е разряды в каналах, подклк1ченньк к информационной магистрали, В результате от информационной магистрали отключаются каналы, адреса которых отключаются от максимальных по 1-му. разряду.

После подачи К-го импульса все триггеры 7 переходят в единичное состояние и к информационной магистрали 7 подключается только один канал с максимальным адресом из всех каналов, в которые поступают сигналы запросов. Только в этом канапе на информационном выходе канала 10 присутствует сигнал логической единицы. Во время подачи (К+1)-го счетного импульса все триггеры 21 переходят в нулевое состояние, на шинах управляющей м;агистрали отсутствуют управляющие сигналы, на выходе элемента И 16 в га-м узле блока управления присутствует сигнал логической единицы, который поступает на шину 5 окончания анализа устройства Этот сигнал синхронизирует работу устройства, фиксируя момент окончания анализа и разрешая работу с выбранным перифе- рийным устройством. На шину 3 сброса подается сигнал логической единицы, в результате чего все триггеры 17 блока управления переходят в нулевое состояние (триггеры 21 сбрасываются раньше), Этот сигнал через элементы ИЛИ 31 каналов подается на сбросовые входы триггеров 32 каналов, в результате чего все триггеры 32 устройства

находятся в нулевом состоянии. На шине блокировки прохождения сигналов опросов 11 подается сигнал логической единицы, переводя его в цикл приема запросов,

Формула изобретения

ходом сумматора по модулю два К-го канала, вход сброса устройства соединен с вторыми входами элемента ИЛИ К-го канала, с первым входом первого элемента 1-ШИ i-ro узла управления и входом сброса первого триггера i-ro узла управления, вход запроса К-го канала соединен с первым входом эле- Многоканальное устройство для под- Q мента И К-го канала, выход которого

15

30

ключения абонентов к общей магистрали, содержащее N каналов (N - число запросов), каждый из которых содержит регистр адреса, два коммутатора, сумматор по модулю два, триггер, причем группа адресных входов К-го (,N) канала соединена с группой информационных входов регистра адреса К-го канала, группа выходов которого соединена с группой информацион- 2о динен ных входов первого коммутатора К-го канала, выход которого соединен с первым входом сумматора по модулю два К-го канала, второй вход которого соединен с выходом второго коммутатора К-го канала отличающееся тем, что, с целью повышения быстродействия устройства, в него введены m узлов управления (т - разрядность адреса абонента), каждый из которых содержит два триггера, два элемента ИЛИ, четьфе элемента И, а в каждый канал введены группа элементов НЕ, группа элементов И-НЕ, элемент И и элемент ИЛИ, причем выход элемента ИЛИ К-го канала соецмнщ с входом сброса три ггера К-го канала, выход которого является выходом предоставления обслуживания К-го канала и соединен с первыми входами элементов И-НЕ группы К-го канала, выходы i-x (,m) элементов И-НЕ группы всех каналов через монтажное ИЛИ соединены с входами i-x элементов НЕ группы всех каналов и первым входом первого элемента И i-ro узла управления, выходы элементов НЕ группы К-го канала соединены с группой информационных входов второго комму- татора К-го канала, первь вход элемента ИЛИ К-го канала соединен с высоединК-го сов у входом устрой перво ления вым вх узла у

тригге мой вы ми вхо тов И

25 второг ния со элемен выход са вто ления узла у ляющим мутато ход пе ления вертог ния, в устано управл соедин мента го, тр И перв третье

jg управл входом входам го эле выход

- управл ния ан

35

40

5

0

о динен

соединен с входом установки триггера К-го канала, вход блокировки запросов устройства соединен с вторым входом элемента И канала, вход записи устройства соединен с вторым входом первого элемента И i-ro узла управления, выход которого соединен с первым входом второго элемента ИЛИ i-ro узла управления, выход которого соес входом установки первого триггера i-ro узла управления, прямой выход которого соединен с первыми входами второго и третьего элементов И i-ro узла управления, выход

5 второго элемента И i-го узла управления соединен с вторым входом первого элемента ИЛИ i-ro узла управления, выход которого соединен с входом сброса второго триггера i-го узла управления, выход второго триггера i-ro узла управления соединен с i-м управляющим входом первого и второго коммутатора всех каналов, инверсный выход первого триггера i-ro узла управления соединен с первым входом четвертого элемента И i-ro узла управления, выход которого соединен с входом установки второго триггера i-ro узла управления, тактовый вход устройства соединен с вторым входом второго элемента ИЛИ, с вторыми входами второго, третьего и четвертого элементов И первого узла управления, выход третьего элемента И (j-l)-rp узла

jg управления (,m) соединен с вторым входом второго элемента ИЛИ, вторыми входами второго, третьего и четвертого элементов И j-ro узла управления, выход третьего элемента И га-го узла

- управления является выходом окончания анализа устройства.

5

0

qjuti

2 J

B,StSff3i1

Ш1/г.з

| Устройство для выбора запросов по приоритетам | 1985 |

|

SU1307458A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1977 |

|

SU731438A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-07—Публикация

1985-12-30—Подача