со со э

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

Изобретение относится к автоматике и вычислителной технике и может быть использовано в распределенных отказоустойчивых управляющих системах АСУ ТП, использующих программный принцип управления и допускающих наращивание при расширении числа выполняемых функций. Цель изобретения - расширение функциональных возможностей и области применения устройства. Поставленная цель достигается тем, что в известное устройство, содержащее блок памяти микрокоманд, регистры адреса и микроопераций, мультиплексоры адреса и логических условий, триггеры пуска и ошибки и первый элемент ИЛИ, введены дешифратор, счетчик, триггеры контроля и состояния, сумматор по модулю два, второй - седьмой элементы ИЛИ, первый - пятый элементы И, первый и второй магистральные элементы и шина адресного кода управления. Введение новых элементов позволяет существенно повысить достоверность функционирования устройства, обеспечить возможность построения на основании данного устройства легко наращиваемой гибкой распределенной управляющей системы, перестраиваемой при отказах одного из устройств, входящих в систему, что позволяет существенно расширить функциональные возможности устройства. 4 ил.

Изобретение относится к автоматике и вычислительной технике и может быть использовано в распределенных отказоустойчивых управляющих системах АСУ ТП, использующих программный принцип управления и допускающих наращивание при расширении числа выполняемых (Функций

Цель изобретения - расширение функциональньгх возможностей и области применения устройства

Сущность изобретения состоит в том, что на основе данного устройства обеспечивается возможно,сть построения легко наращиваемой гибкой - распределенной управляющей системы.

,150

перестраиваемой при отказаХоВзаимо- действие устройств осуществляется путем передачи от одного устройства другому кода микропрограммы или мик роподпрограммы, которую должно выполнять устройство, получившее этот адресный код управления

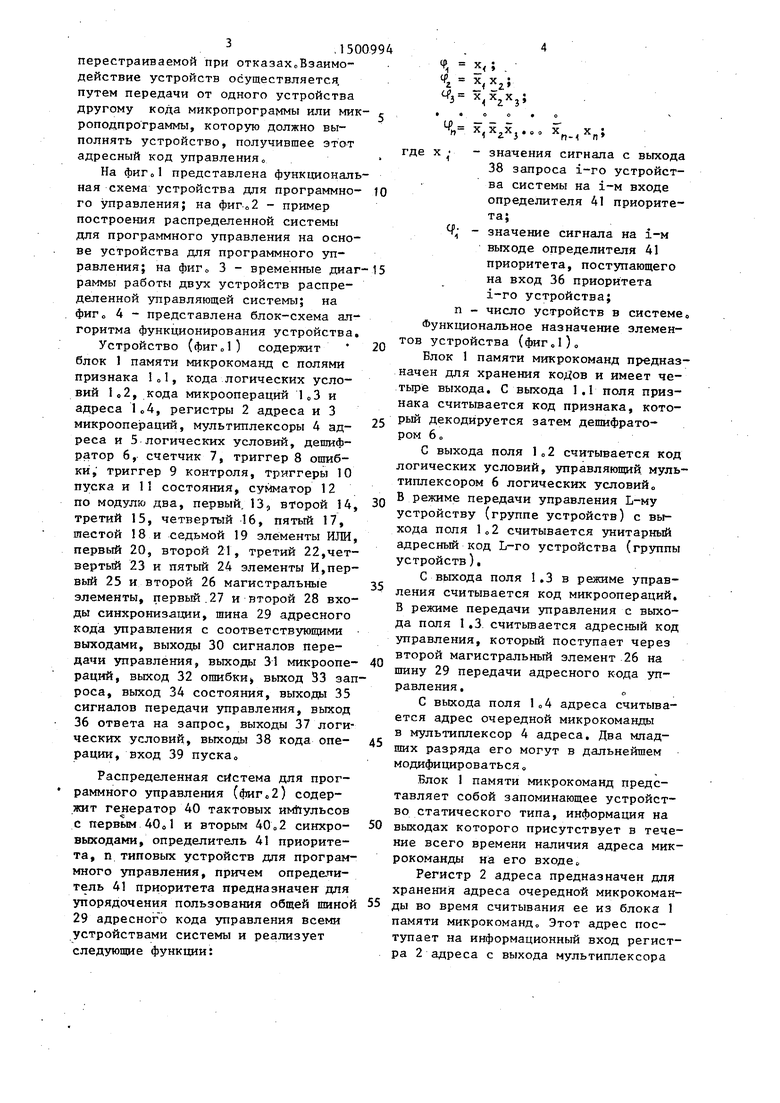

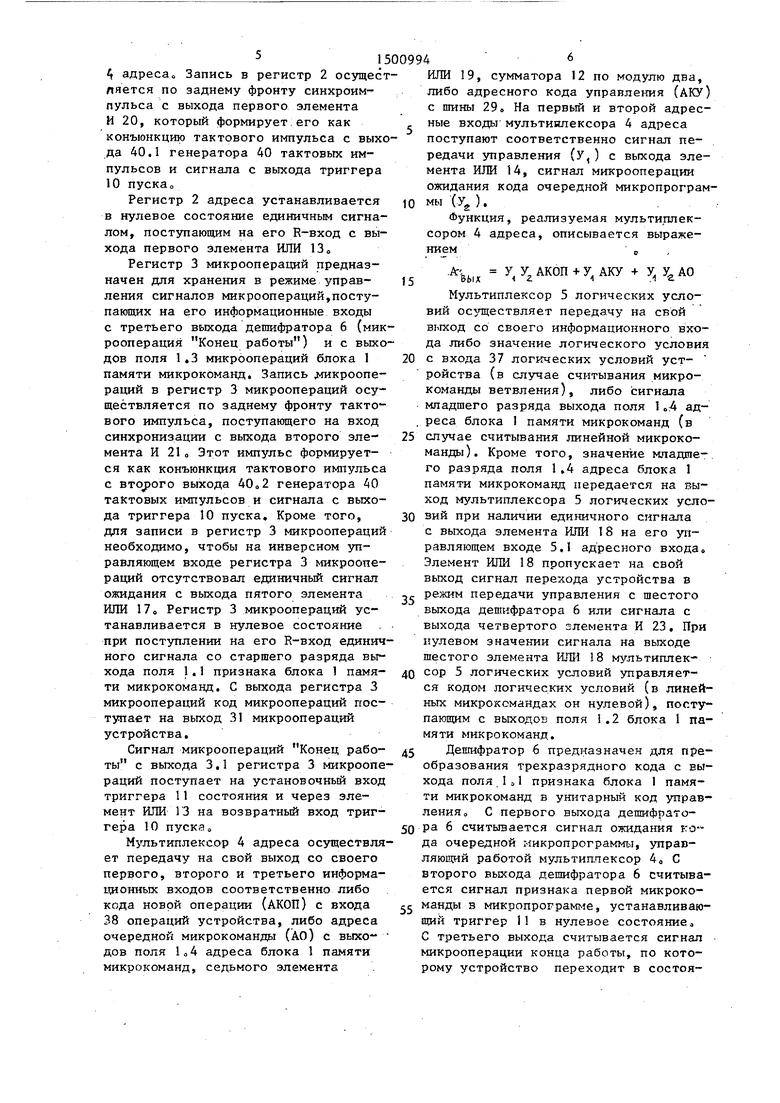

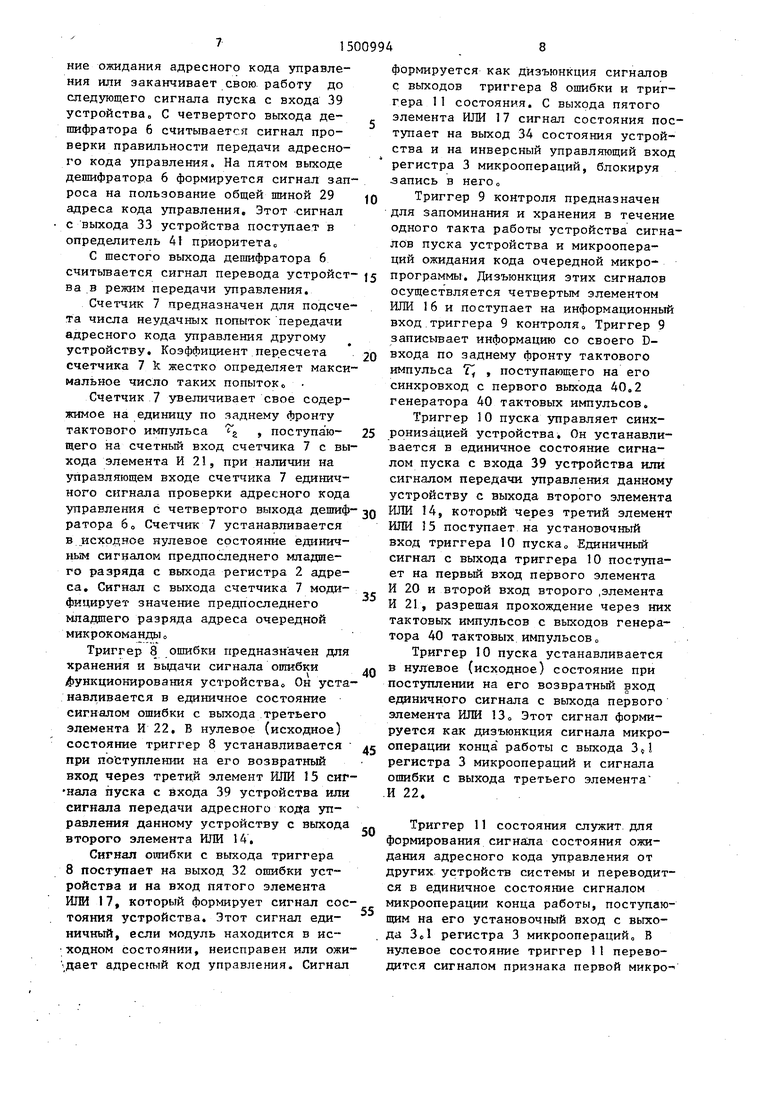

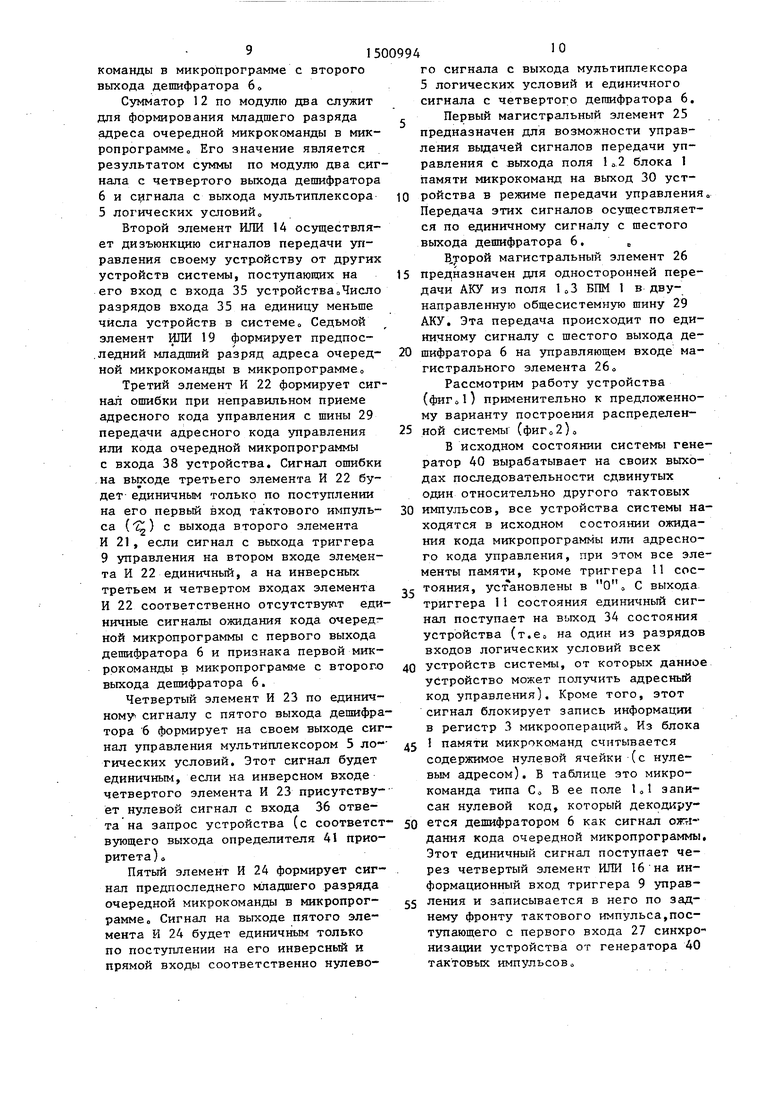

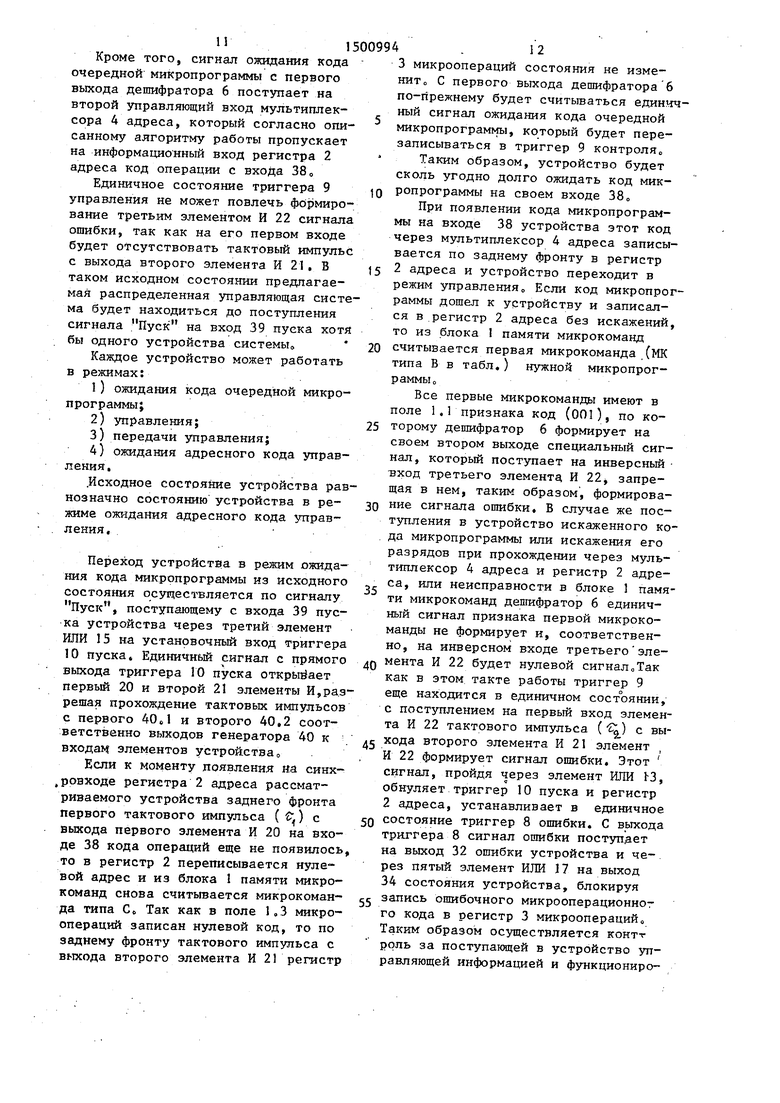

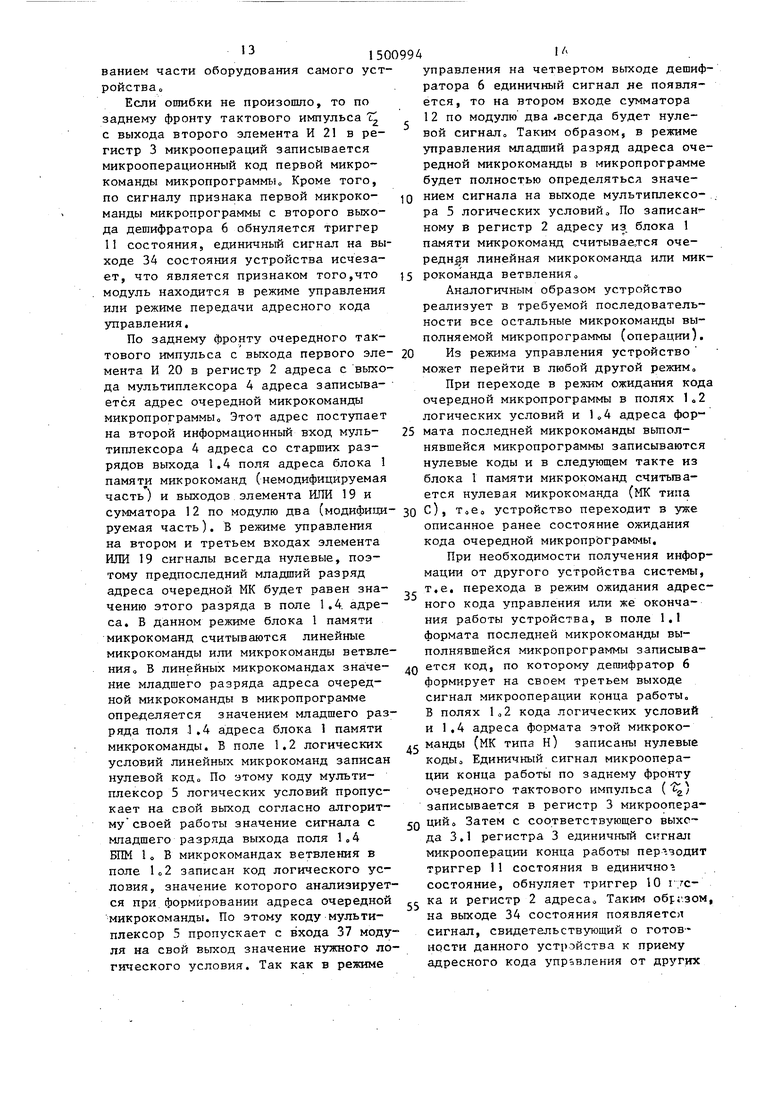

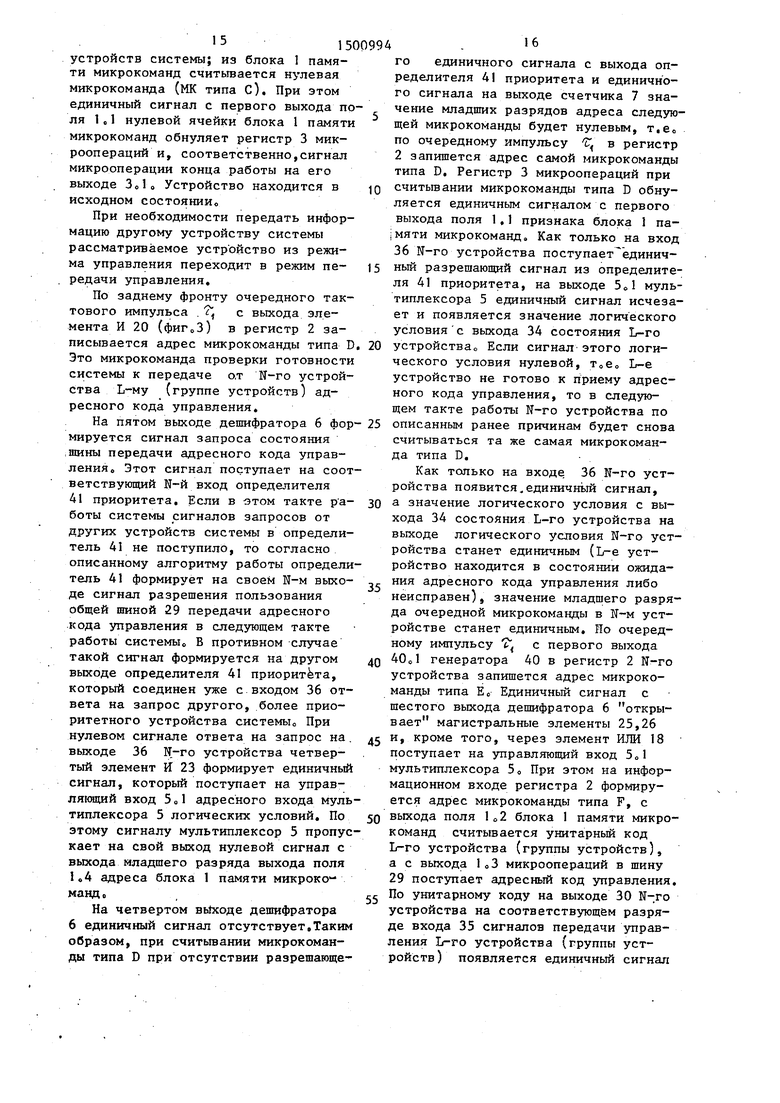

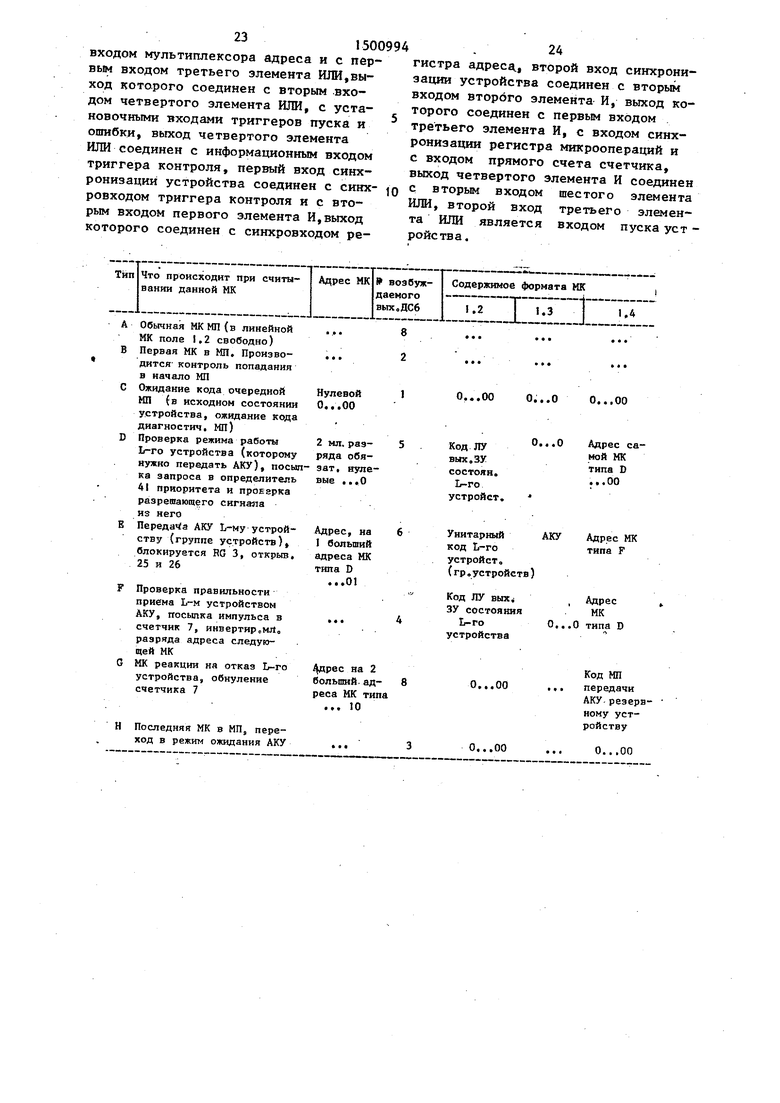

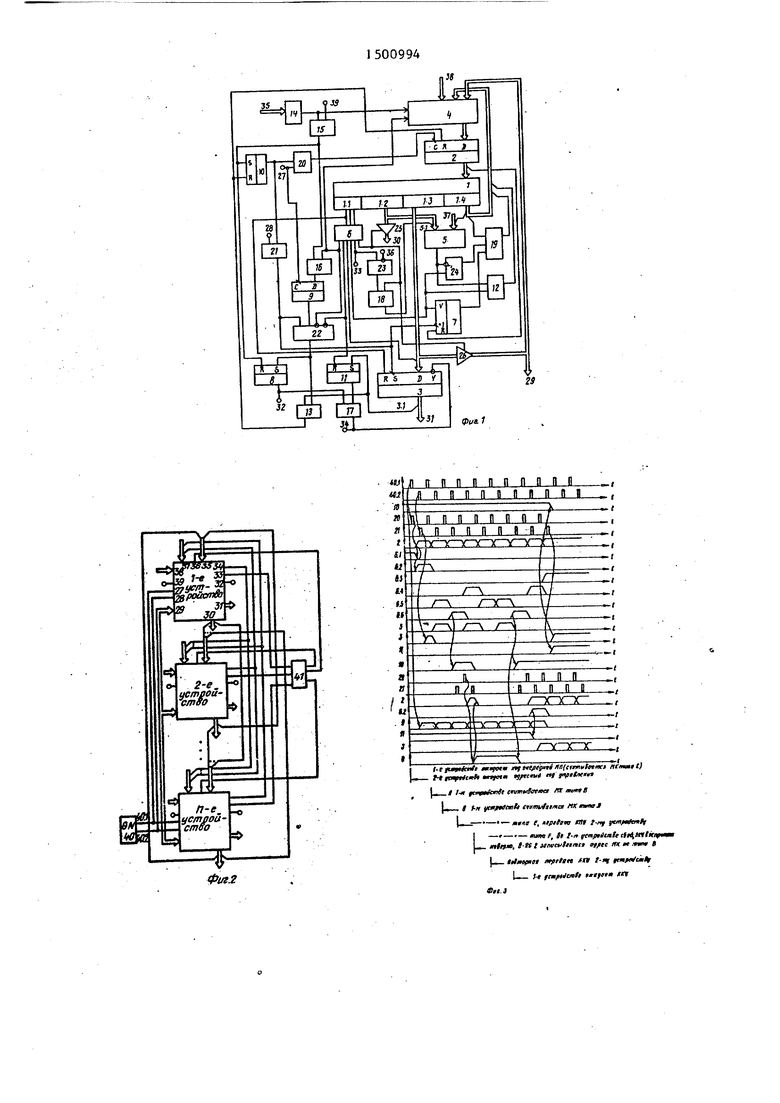

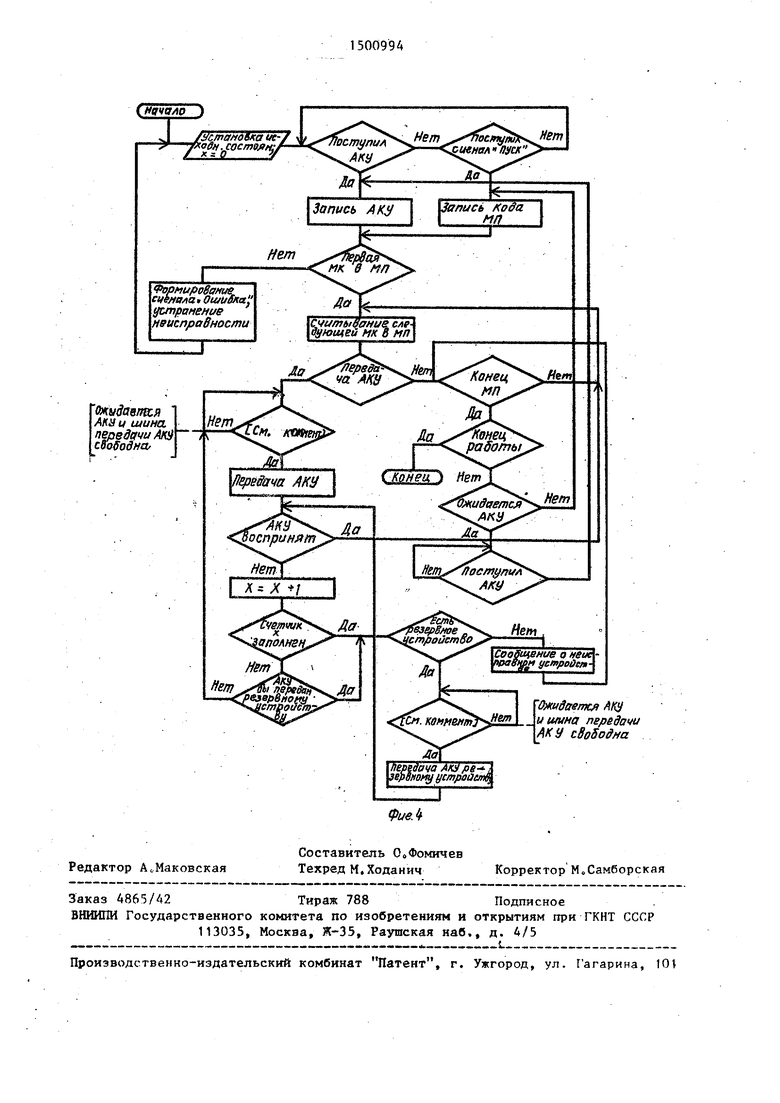

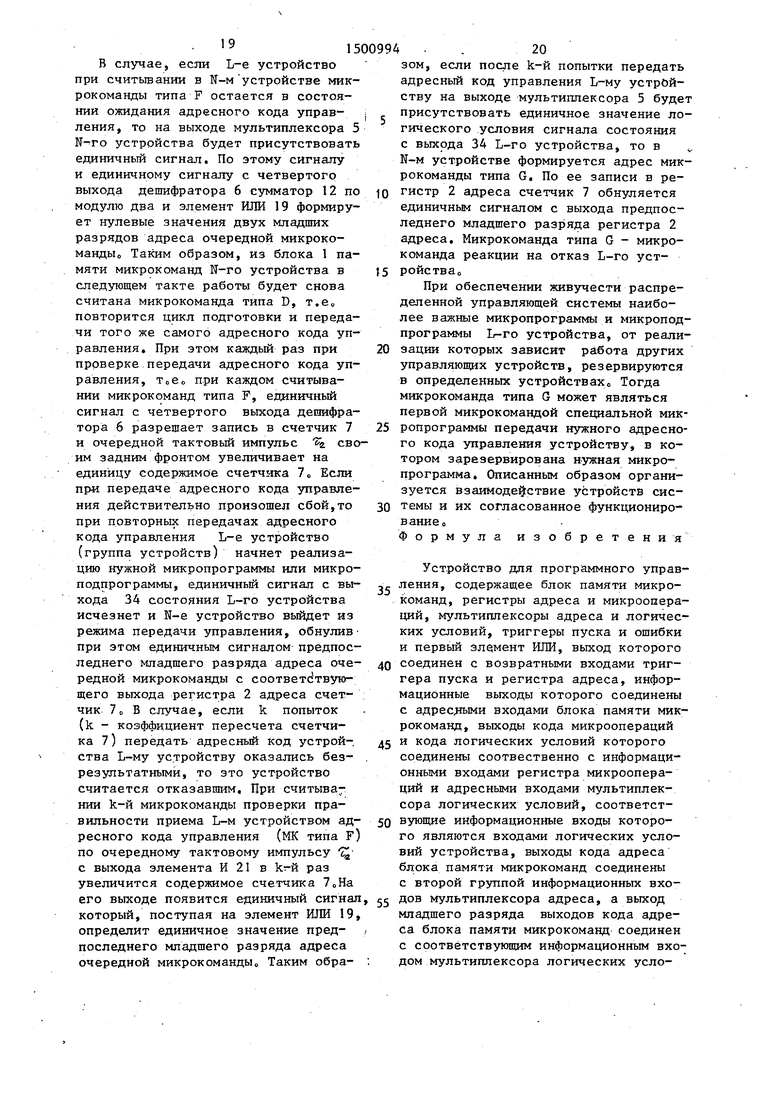

На фиго представлена функциональная схема устройства для программно- го управления; на фиг-о2 - пример построения распределенной системы для программного управления на основе устройства для программного управления; на фиг о 3 - временные дйаг раммы работы двух устройств распределенной управляющей системы; на фиг с 4 - представлена блок-схема алгоритма функционирования устройства.

Устройство (фиГоО содержит блок 1 памяти микрокоманд с полями признака Kl, кода логических условий 1,2, кода микроопераций 1оЗ и адреса К4, регистры 2 адреса и 3 микроопераций, мультиплексоры 4 ад- раса и 5 логических условий, дешифратор 6, счетчик 7, триггер 8 опшб- ки, триггер 9 контроля, триггеры 10 пуска и 11 состояния, сумматор 12 по модулю два, первый, 13, второй 14, третий 15, четвертый 16, пятый 17, шестой 18 и седьмой 19 элементы ИЛИ, первый 20, второй 21, третий 22,четвертый 23 и пятьй 24 элементы И,первый 25 и второй 26 магистральные элементы, первый.27 и второй 28 входы синхронизации, шина 29 адресного кода управления с соответствующими выходами, выходы 30 сигналов передачи управления, выходы 31 микроопе- раций, выход 32 огаибки выход 33 запроса, выход 34 состояния, выходы 35 сигналов передачи управления, выход 36 ответа на запрос, выходы 37 логических условий, выходы 38 кода one- рации, вход 39 пуска

Распределенная система для программного управления () содержит генератор 40 тактовых имйульсов с первым 40о1 и вторым 40о2 синхро- выходами, определитель 41 приоритета, п типовых устройств для программного управления, причем определитель 41 приоритета предназначен для упорядочения пользования общей шиной 29 адресного кода управления всеми устройствами системы и реализует следующие функции:

Ф, X, ;

z Ч з

X XX,.о о X X ;

n- п

где X

- значения сигнала с выхода 38 запроса 1-го устройства системы на 1-м входе определителя 41 приоритета;

- - значение сигнала на i-M выходе определителя 41 приоритета, поступающего на вход 36 приоритета i-ro устройства; п - число устройств в системе Функциональное назначение элементов устройства (фиГоОо

Блок 1 памяти микрокоманд предназначен для хранения коДов и имеет че- тьфе выхода. С выхода I.1 поля признака считывается код признака, который декодируется затем дешифратором 6 о

С выхода поля 1о2 считывается код логических условий, управляющий, мультиплексором 6 логических условий„ В режиме передачи управления L-му устройству (группе устройств) с выхода поля 1о2 считывается унитарный адресный код L-ro устройства (группы устройств).

С вьгхода поля 1.3 в режиме управления считывается код микроопераций. В режиме передачи управления с вьгхода поля 1 .3. считьшается адресный код управления, который поступает через второй магистральный элемент 26 на шину 29 передачи адресного кода равления.„

С выхода поля адреса считывается адрес очередной микрокоманды в мультиплексор 4 адреса. Два младших разряда его могут в дальнейшем модифицироваться„

Блок 1 памяти микрокоманд представляет собой запоминающее устройство статического типа, информация на выходах которого присутствует в течение всего времени наличия адреса микрокоманды на его входе

Регистр 2 адреса предназначен для хранения адреса очередной микрокоманды во время считывания ее из блока 1 памяти микрокоманд Этот адрес поступает на информационный вход регистра 2 адреса с выхода мультиплексора

4 адресао Запись в регистр 2 осущест ляется по заднему фронту синхроимпульса с выхода первого элемента И 20, который формирует:его как конъюнкцию тактового импульса с выхода 40.1 генератора 40 тактовых импульсов и сигнала с выхода триггера 10 пуска

Регистр 2 адреса устанавливается в нулевое состояние единичным сигналом, поступающим на его R-вход с выхода первого элемента ИЛИ 13

Регистр 3 микроопераций предназначен для хранения в режиме З Прав- ления сигналов микроопераций,поступающих на его информационные входы с третьего выхода дешифратора 6 (микрооперация Конец работы) и с выходов поля 1,3 микроопераций блока 1 памяти микрокоманд. Запись гакроопе- раций в регистр 3 микроопераций осуществляется по заднему фронту тактового импульса, поступающего на вход синхронизации с выхода второго элемента И 21 о Этот импульс формируется как конъюнкция тактового импульса с второго выхода 40«2 генератора 40 тактовых импульсов и сигнала с выхода триггера 10 пуска. Кроме того, для записи в регистр 3 микроопераций необходимо, чтобы на инверсном управляющем входе регистра 3 микроопераций отсутствовал единичный сигнал ожидания с выхода пятого элемента ИЛИ 17о Регистр 3 микроопераций устанавливается в нулевое состояние при поступлении на его R-вход единичного сигнала со старшего разряда выхода поля 1.1 признака блока 1 памяти микрокоманд. С выхода регистра 3 микроопераций код микроопераций поступает на выход 31 микроопераций устройства.

Сигнал микроопераций Конец работы с выхода 3.1 регистра 3 микроопераций поступает на установочный вход триггера 11 состояния и через элемент ИЛИ ГЗ на возвратный вход триггера 10 пуска

Мультиплексор 4 адреса осуществляет передачу на свой выход со своего первого, второго и третьего информационных входов соответственно либо кода новой операции (АКОП) с входа 38 операций устройства, либо адреса очередной микрокоманды (Ао) с выхо- дов поля 1,4 адреса блока 1 памяти микрокоманд, седьмого элемента

ИЛИ 19, сумматора 12 по модулю два, либо адресного кода управления (АКУ) с щины 29 На первый и второй адресные входы мультиплексора 4 адреса поступают соответственно сигнал передачи управления (У,) с выхода элемента ИЛИ 14, сигнал микрооперации ожидания кода очередной микропрограммы (У ),. .

Функция, реализуемая мультиплексором 4 адреса, описывается выражениемо ,

5

0

5

0

0

.Аг

У У., АКОП + У, АКУ

У, АО

febix

Мультиплексор 5 логических условий осуществляет передачу на свой выход со своего информационного входа либо значение логического условия с входа 37 логических условий устройства (в случае считывания микрокоманды ветвления), либо сигнала младшего разряда выхода поля 1«4 адреса блока I памяти микрокоманд (в случае считывания линейной микрокоманды). Кроме того, значение младше-, го разряда поля 1.4 адреса блока 1 памяти микрокоманд передается на выход мультиплексора 5 логических условий при наличии единичного сигнала с выхода элемента ИЛИ 18 на его управляющем входе 5,1 адресного входа. Элемент ИЛИ 18 пропускает на свой выход сигнал перехода устройства в режим передачи управления с шестого выхода дешифратора 6 или сигнала с выхода четвертого элемента И 23, При нулевом значении сигнала на выходе шестого элемента ИЛИ 18 мультиплексор 5 логических условий управляется кодом логических условий (в линейных микрокомандах он нулевой), поступающим с ньпсодов поля 1 ,2 блока 1 памяти микрокоманд.

Депгифратор 6 предназначен для преобразования трехразрядного кода с выхода поля. признака блока 1 памяти микрокоманд в унитарный код управления С первого выхода дешифратора 6 считывается сигнал ожидания кода очередной микропрограммы, управляющий работой мультип-пексор 4, С второго выхода дешифратора 6 считывается сигнал признака первой микроко- 5 манды в микропрограмме, устанавливающий триггер 11 в нулевое состояние С третьего выхода считывается сигнал микрооперации конца работы, по которому устройство переходит в состоя5

0

5

кие ожидания адресного кода управления или заканчивает свою работу до следзтощего сигнала пуска с входа 39 устройства, С четвертого выхода дешифратора 6 считывается сигнал проверки правильности передачи адресного кода управления. На пятом выходе дешифратора 6 формируется сигнал запроса на пользование общей шиной 29 адреса кода управления. Этот сигнал с выхода 33 устройства поступает в определитель 41 приоритета

С шестого выхода дешифратора 6 считьгаается сигнал перевода устройст- ва в режим передачи управления.

Счетчик 7 предназначен для подсчета числа неудачных попыток передачи адресного кода управления другому устройству. Коэффициент пересчета счетчика 7 k жестко определяет максимальное число таких попытоко

Счетчик 7 увеличивает свое содержимое на единицу по заднему фронту тактового импульса г , поступаю- щего на счетный вход счетчика 7 с выхода элемента И 21, при наличии на управляющем входе счетчика 7 единичного сигнала проверки адресного кода управления с четвертого выхода дешиф- ратора 6 о Счетчик 7 устанавливается в исходное нулевое состояние единичным сигналом предпоследнего младшего разряда с выхода регистра 2 адреса. Сигнал с выхода счетчика 7 модифицирует значение предпоследнего младшего разряда адреса очередной микрокоманды о

Триггер 8 ошибки предназначен для хранения и вьщачи сигнала ошибки 4 ункционирования устройства Он устанавливается в единичное состояние сигналом ошибки с выхода третьего элемента И 22, В нулевое (исходное) состояние триггер 8 устанавливается при по ступлении на его возвратньй вход через третий элемент ИЛИ 15 сиг нала пуска с входа 39 устройства или сигнала передачи адресного кода управления данному устройству с выхода второго элемента ИЛИ 14,

Сигнал оигабки с выхода триггера 8 поступает на выход 32 ошибки устройства и на вход пятого элемента ШШ 17, который формирует сигнал состояния устройства. Этот сигнал единичный, если модуль находится в ис- ходком состоянии, неисправен или ожи (Дает адресньтй код управления. Сигнал

Q

5

0

5 д

Q g

5

0

формируется как дизъюнкция сигналов с выходов триггера 8 ошибки и триггера 11 состояния. С выхода пятого элемента ШШ 17 сигнал состояния поступает на выход 34 состояния устройства и на инверсный управляющий вход регистра 3 микроопераций, блокируя запись в него

Триггер 9 контроля предназначен для запоминания и хранения в течение одного такта работы устройства сигналов пуска устройства и микроопераций ожидания кода очередной микропрограммы. Дизъюнкция этих сигналов осуществляется четвертым элементом ИЛИ 16 и поступает на информационный вход триггера 9 контроля Триггер 9 записьгеает информацию со своего D- входа по заднему фронту тактового импульса Т, , поступающего на его синхровход с первого выхода 40.2 генератора 40 тактовых импульсов.

Триггер 10 пуска з равляет синхронизацией устройства. Он устанавливается в единичное состояние сигналом пуска с входа 39 устройства или сигналом передачи управления данному устройству с выхода второго элемента ИЛИ 14, который через третий элемент ШШ 15 поступает на установочный вход триггера 10 пуска,, Единичный сигнал с выхода триггера 10 поступает на первый вход первого элемента И 20 и второй вход второго .элемента И 21, разрешая прохождение через них тактовых импульсов с выходов генератора 40 тактовых импульсов

Триггер 10 пуска устанавливается в нулевое (исходное) состояние при поступлении на его возвратньй вход единичного сигнала с выхода первого элемента ИЛИ 13 Этот сигнал формируется как дизъюнкция сигнала микрооперации конца работы с выхода 3« регистра 3 микроопераций и сигнала ошибки с выхода третьего элемента .И 22,

Триггер 11 состояния служит, для формирования сигнала состояния ожидания адресного кода управления от других устройств системы и переводится в единичное состояние сигналом микрооперации конца работы, поступающим на его установоч 1ый вход с выхода 3,1 регистра 3 микроопераций, В нулевое состояние триггер 1 I переводится сигналом признака первой микрокоманды в микропрограмме с второго выхода дешифратора б

Сумматор 12 по модулю два служит для формирования младшего разряда адреса очередной микрокоманды в микропрограмме Его значение является результатом суммы по модулю два сигнала с четвертого выхода дешифратора 6 и с 1гнала с выхода мультиплексора 5 логических условий.

Второй элемент ИЛИ 14 осуществляет дизъюнкцию сигналов передачи управления своему устройству от других устройств системы, поступающих на его вход с входа 35 устройства„Число разрядов входа 35 на единицу меньше числа устройств в системе о Седьмой элемент ИЛИ 19 формирует предпос- .ледний младший разряд адреса очередной микрокоманды в микропрограмме

Третий элемент И 22 формирует сигнал ошибки при неправильном приеме адресного кода управления с шины 29 передачи адресного кода управления или кода очередной микропрограммы с входа 38 устройства. Сигнал ошибки ,на выходе третьего элемента И 22 будет единичным только по поступлении на его первый вход тактового импульса ( 2) с выхода второго элемента И 21, если сигнал с выхода триггера 9 управления на втором входе элемента И 22 единичный, а на инверсных третьем и четвертом входах элемента И 22 соответственно отсутствует единичные сигналы ожидания кода очередной микропрограммы с первого выхода дешифратора 6 и признака первой микрокоманды в микропрограмме с второго выхода дешифратора 6.

Четвертый элемент И 23 по единич- ному сигналу с пятого выхода дешифратора 6 формирует на своем выходе сигнал управления мультиплексором 5 ло гических условий. Этот сигнал будет единичным, если на инверсном входе четвертого элемента И 23 присутствуёт нулевой сигнал с входа 36 ответа на запрос устройства (с соответствующего выхода определителя 41 приоритета)

Пятый элемент И 24 формирует сигнал предпоследнего младшего разряда очередной микрокоманды в микропрограмме о Сигнал на выходе пятого элемента И 24 будет единичным только по поступлении на его инверсный и прямой входы соответственно нулево-

0

5

5

0

го сигнала с выхода мультиплексора 5 логических условий и единичного сигнала с четвертого дешифратора 6.

Первый магистральный элемент 25 предназначен для возможности управления вьщачей сигналов передачи управления с выхода поля 1 о 2 блока 1 Памяти микрокоманд на выход 30 устройства в режиме передачи управления о Передача этих сигналов осуществляется по единичному сигналу с шестого выхода дешифратора 6. „

В,торой магистральный элемент 26 предназначен для односторонней передачи АКУ из поля 1оЗ БПМ 1 в двунаправленную общесистемную шину 29 АКУ, Эта передача происходит по единичному сигналу с шестого выхода де0 шифратора 6 на управляющем входе магистрального элемента 26„

Рассмотрим работу устройства (фиГоО применительно к предложенному варианту построения распределенной системы (фиго2)о

В исходном состоянии системы генератор 40 вырабатывает на своих выходах последовательности сдвинутых один относительно другого тактовых импульсов, все устройства системы находятся в исходном состоянии ожидания кода микропрограммы или адресного кода управления, при этом все элементы памяти, кроме триггера 11 состояния, ус гановлены в О С выхода триггера 1I состояния единичный сигнал поступает на выход 34 состояния устройства (т.ео на один из разрядов входов логических условий всех устройств системы, от которых данное устройство может получить адресный код управления). Кроме того, этот сигнал блокирует запись информации в регистр 3 микроопераций о Из блока 1 памяти микрокоманд считывается содержимое нулевой ячейки (с нулевым адресом), В таблице это микрокоманда типа Со В ее поле записан нулевой код, который декодкру0 ется дешифратором 6 как сигнал Дания кода очередной микропрограммы. Этот единичный сигнал поступает через четвертый элемент ИЛИ 16 на информационный вход триггера 9 управ5 ления и записывается в него по заднему фронту тактового импульса,поступающего с первого входа 27 синхронизации устройства от генератора 40 тактовых импульсов о

5

0

5

Кроме того, сигнал ожидания кода очередной микропрограммы с nepsoro выхода дешифратора 6 поступает на второй управляющий вход мультиплексора 4 адреса, который согласно описанному алгоритму работы пропускает на информационный вход регистра 2 адреса код операции с входа 38 о

Единичное состояние триггера 9 управления не может повлечь формирование третьим элементом И 22 сигнала ошибки, так как на его первом входе будет отсутствовать тактовый импульс с выхода второго элемента И 21, В таком исходном состоянии предлагаемая распределенная управляющая система будет находиться до поступления сигнала .Пуск на вход 39 пуска хотя бы одного устройства системы

Каждое устройство может работать в режимах:

1)ожидания кода очередной микропрограммы;

2)управления;

3)передачи управления;

4)ожидания адресного кода управления,

.Исходное состояние устройства равнозначно состоянию устройства в режиме ожидания адресного кода управления,

Переход устройства в режим ожидания кода микропрограммы из исходного состояния осуществляется по сигналу Пуск, поступающему с входа 39 пуска устройства через третий элемент ИЛИ I5 на установочный вход триггера

10 пуска. Единичный сигнал с прямого др мента И 22 будет нулевой сигнал„Так

выхода триггера 10 пуска открывает первый 20 и второй 21 элементы И,разрешая прохождение тактовых импульсов с первого 40,1 и второго 40,2 соответственно выходов генератора 40 к входан элементов устройства о

Если к моменту появления иа синх- ,ровходе регистра 2 адреса рассматриваемого устройства заднего фронта первого тактового импульса ( ) с выхода первого элемента И 20 на входе 38 кода операций еще не появилось, то в регистр 2 переписывается нулевой адрес и из блока 1 памяти микрокоманд снова считывается микрокоманда типа Со Так как в поле 1.3 микроопераций записан нулевой код, то по заднему фронту тактового импульса с вьжода второго элемента И 21 регистр

45

как в этом такте работы триггер 9 еще находится в единичном состЪянии, с поступлением на первый вход элемен та И 22 тактового импульса () с вы хода второго элемента И 21 элемент И 22 формирует сигнал ошибки. Этот сигнал, пройдя через элемент ИЛИ ЬЗ, обнуляет триггер 10 пуска и регистр 2 адреса, устанавливает в единичное

50 состояние триггер 8 ошибки. С выхода триггера 8 сигнал ошибки поступает на выход 32 ошибки устройства и через пятый элемент ИЛИ 17 на выход 34 состояния устройства, блокируя

55 запись ошибочного микрооперационног го кода в регистр 3 микроопераций Таким образом осуществляется контт роль за поступакицей в устройство управляющей информацией и функциониро3 микроопераций состояния не изменит С первого выхода дешифратора 6 по-прежнему будет считываться ный сигнал ожидания кода очередной микропрограммы, который будет перезаписываться в триггер 9 контроля Таким образом, устройство будет сколь угодно долго ожидать код микропрограммы на своем входе 38„

При появлении кода микропрограммы на входе 38 устройства этот код через мультиплексор 4 адреса записывается по заднему фронту в регистр

2 адреса и устройство переходит в

режим управления„ Если код микропрограммы дошел к устройству и записался в регистр 2 адреса без искажений, то из блока 1 памяти микрокоманд

считывается первая микрокоманда .(МК типа В в табл.) нужной микропрограммы о

Все первые микрокоманды имеют в поле 1.1 признака код (001), по которому дешифратор 6 формирует на своем втором выходе специальный сигнал, который поступает на инверсный вход третьего элемента И 22 запрещая в нем, таким образом, формирование сигнала ошибки, В случае же поступления в устройство искаженного кода микропрограммы или искажения его разрядов при прохождении через мультиплексор 4 адреса и регистр 2 адреса, или неисправности в блоке 1 памяти микрокоманд дешифратор 6 единичный сигнал признака первой микрокоманды не формирует и, соответственно, на инверсном входе третьего эле

др мента И 22 будет нулевой сигнал„Так

45

как в этом такте работы триггер 9 еще находится в единичном состЪянии, с поступлением на первый вход элемента И 22 тактового импульса () с выхода второго элемента И 21 элемент И 22 формирует сигнал ошибки. Этот сигнал, пройдя через элемент ИЛИ ЬЗ, обнуляет триггер 10 пуска и регистр 2 адреса, устанавливает в единичное

50 состояние триггер 8 ошибки. С выхода триггера 8 сигнал ошибки поступает на выход 32 ошибки устройства и через пятый элемент ИЛИ 17 на выход 34 состояния устройства, блокируя

55 запись ошибочного микрооперационног го кода в регистр 3 микроопераций Таким образом осуществляется контт роль за поступакицей в устройство управляющей информацией и функциониро10

ванием части оборудования самого устройства

Если ошибки не произопшо, то по заднему фронту тактового импульса 7 с выхода второго элемента И 2 в регистр 3 микроопераций записывается микрооперационный код первой микрокоманды микропрограммьи Кроме того, по сигналу признака первой микрокоманды микропрограммы с второго выхода дешифратора 6 обнуляется триггер 11 состояния, единичный сигнал на выходе 34 состояния устройства исчезает, что является признаком того,что модуль находится в режиме управления или режиме передачи адресного кода управления.

По заднему фронту очередного тактового импульса с выхода первого эле- 20 мента И 20 в регистр 2 адреса с выхода мультиплексора 4 адреса записывается адрес очередной микрокоманды микропрограммыо Этот адрес поступает на второй информационный вход мультиплексора 4 адреса со старших разрядов выхода 1.4 поля адреса блока 1 памяти микрокоманд (немодифицируемая часть) и выходов элемента ИЛИ 19 и

управления на четвертом выходе дешиф ратора 6 единичный сигнал яе появляется, то на втором входе сумматора 12 по модулю два .всегда будет нулевой сигнал Таким образом, в режиме управления младший разряд адреса оче редной микрокоманды в микропрограмме будет полностью определяться значением сигнала на выходе мультиплексора 5 логических условий По записанному в регистр 2 адресу из. блока 1 памяти микрокоманд считывае,тся очередная линейная микрокоманда или мик

15 рокоманда ветвления.

Аналогичным образом устройство реализует в требуемой последовательности все остальные микрокоманды выполняемой микропрограммы (операции). Из режима управления устройство может перейти в любой другой режим.

При переходе в режим ожидания код очередной микропрограммы в полях 1а2 логических условий и 1о4 адреса фор25 мата последней микрокоманды вьтол- нявшейся микропрограммы записываются нулевые коды и в следующем такте из блока 1 памяти микрокоманд считьша- ется нулевая микрокоманда (МК типа

сумматора 12 по модулю два (модифици- зо С), т,ео устройство переходит в уже

руемая часть). В режиме управления на втором и третьем входах элемента ИЛИ 19 сигналы всегда нулевые, поэтому предпоследний младший разряд адреса очередной МК будет равен значению этого разряда в поле 1.4. адреса. Б данном режиме блока 1 памяти микрокоманд считываются линейные микрокоманды или микрокоманды ветвления В линейных микрокомандах значение младшего разряда адреса очередной микрокоманды в микропрограмме определяется значением младшего разряда ттоля .1 .4 адреса блока 1 памяти

35

описанное ранее состояние ожидания кода очередной микропрограммы.

При необходимости получения инфор мации от другого устройства системы, т.е. перехода в режим ожидания адрес ного кода управления или же окончания работы устройства, в поле 1.1 формата последней микрокоманды выполнявшейся микропрограммы записыва- дд ется код, по которому дешифратор 6 формирует на своем третьем выходе сигнал микрооперации конца работы, В полях К 2 кода логических условий и 1.4 адреса формата этой микрокомикрокоманды. В поле 1.2 логических ,г манды (МК типа Н) записаны нулевые

условий линейных микрокоманд записан нулевой кодо По этому коду мультиплексор 5 логических условий пропускает на свой выход согласно алгоритму своей работы значение сигнала с младшего разряда выхода поля 1.4 БПМ 1 о В микрокомандах ветвления в поле 1о2 записан код логического условия, значение которого анализируется при формировании адреса очередной микрокоманды. По этому коду мультиплексор 5 пропускает с входа 37 модуля на свой выход значение нужного логического условия. Так как в режиме

коды. Единичный сигнал микрооперации конца работы по заднему фронту очередного тактового импульса (t) записывается в регистр 3 микроопера- 5Q цийо Затем с соответствующего выхода 3.1 регистра 3 единичный сигнал микрооперации конца работы переводит триггер 11 состояния в единичное состояние, обнуляет триггер 10 i тс- ка и регистр 2 адреса. Таким обр; .зом на выходе 34 состояния появляется сигнал, свидетельствующий о готовности данного устройства к приему адресного кода управления от других

55

0

0

управления на четвертом выходе дешифратора 6 единичный сигнал яе появляется, то на втором входе сумматора 12 по модулю два .всегда будет нулевой сигнал Таким образом, в режиме управления младший разряд адреса очередной микрокоманды в микропрограмме будет полностью определяться значением сигнала на выходе мультиплексо . ра 5 логических условий По записанному в регистр 2 адресу из. блока 1 памяти микрокоманд считывае,тся очередная линейная микрокоманда или микрокоманда ветвления.

Аналогичным образом устройство реализует в требуемой последовательности все остальные микрокоманды выполняемой микропрограммы (операции). Из режима управления устройство может перейти в любой другой режим.

При переходе в режим ожидания кода очередной микропрограммы в полях 1а2 логических условий и 1о4 адреса фор5 мата последней микрокоманды вьтол- нявшейся микропрограммы записываются нулевые коды и в следующем такте из блока 1 памяти микрокоманд считьша- ется нулевая микрокоманда (МК типа

5

описанное ранее состояние ожидания кода очередной микропрограммы.

При необходимости получения информации от другого устройства системы, т.е. перехода в режим ожидания адресного кода управления или же окончания работы устройства, в поле 1.1 формата последней микрокоманды выполнявшейся микропрограммы записыва- д ется код, по которому дешифратор 6 формирует на своем третьем выходе сигнал микрооперации конца работы, В полях К 2 кода логических условий и 1.4 адреса формата этой микрококоды. Единичный сигнал микрооперации конца работы по заднему фронту очередного тактового импульса (t) записывается в регистр 3 микроопера- Q цийо Затем с соответствующего выхода 3.1 регистра 3 единичный сигнал микрооперации конца работы переводит триггер 11 состояния в единичное состояние, обнуляет триггер 10 i тс- ка и регистр 2 адреса. Таким обр; .зом, на выходе 34 состояния появляется сигнал, свидетельствующий о готовности данного устройства к приему адресного кода управления от других

5

15150

устройств системы; из блока I памяти микрокоманд считьгеается нулевая микрокоманда (МК типа С), При этом единичный сигнал с первого выхода поля 1,1 нулевой ячейки блока I памяти микрокоманд обнуляет регистр 3 микроопераций и, соответственно,сигнал микрооперации конца работы на его выходе Зо1о Устройство находится в исходном состоянии

При необходимости передать информацию другому устройству системы рассматриваемое устройство из режима управления переходит в режим пе- редачи управления.

По заднему фронту очередного тактового импульса . с выхода элемента И 20 (фиГоЗ) в регистр 2 записывается адрес микрокоманды типа D Это микрокоманда проверки готовности системы к передаче о.т N-ro устройства L-му (группе устройств) адресного кода управления.

На пятом выходе дешифратора 6 фор мируется сигнал запроса состояния ,шины передачи адресного кода управления. Этот сигнал поступает на соответствующий N-й вход определителя 41 приоритета. Если в этом такте ра- боты системы сигналов запросов от других устройств системы в определитель 41 не поступило, то согласно описанному алгоритму работы определитель 41 формирует на своем Ы-м выхо- да сигнал разрешения пользования общей шиной 29 передачи адресного кода управления в следующем такте работы системЫс В противном случае такой сигнал формируется на другом выходе определителя 41 приоритета, который соединен уже с входом 36 ответа на запрос другого, более приоритетного устройства системы При нулевом сигнале ответа на запрос на. выходе 36 N-ro устройства четвертый элемент И 23 формирует единичный сигнал, который поступает на управ- лянлций вход 5о1 адресного входа мультиплексора 5 логических условий. По этому сигналу мультиплексор 5 пропускает на свой выход нулевой сигнал с выхода младщего разряда выхода поля 1,4 адреса блока 1 памяти мшсроко манд. ,

На четвертом вь1ходе дешифратора 6 единичный сигнал отсутствует,Таким образом, при считьшании микрокоманды типа D при отсутствии разрешагоще16

го единичного сигнала с выхода определителя 41 приоритета и единичного сигнала на выходе счетчика 7 значение младших разрядов адреса следующей микрокоманды будет нулевым, т.е по очередному импульсу Т в регистр 2 запишется адрес самой микрокоманды типа D, Регистр 3 микроопераций при считьгаании микрокоманды типа D обнуляется единичным сигналом с первого выхода поля 1,1 признака блока 1 памяти микрокоманд. Как только на вход 36 N-ro устройства поступает единич- ный разрешающий сигнал из определителя 41 приоритета, на выходе 5о1 мультиплексора 5 единичный сигнал исчезает и появляется значение логического условия с выхода 34 состояния L-ro устройства Если сигнал-этого логического условия нулевой, тфе L-e устройство не готово к приему адресного кода управления, то в следующем такте работы N-ro устройства по описанным ранее причинам будет снова считываться та же самая микрокоманда типа D, ,

Как только на входе 36 N-ro устройства появится,еднничньгй сигнал, а значение логического условия с выхода 34 состояния L-ro устройства на выходе логического условия N-ro устройства станет единичным (L-e устройство находится в состоянии ожидания адресного кода управления либо неисправен), значение младшего разряда очередной микрокоманды в N-M устройстве станет единичным. Но очередному импульсу t с первого выхода 40о 1 генератора 40 в регистр 2 N-ro устройства запишется адрес микрокоманды типа ЕС Единичный сигнал с шестого выхода дешифратора 6 открывает магистральные элементы 25,26 и, кроме того, через элемент ИЖ 18 поступает на управляющий вход 5 мультиплексора 5 При этом на информационном входе регистра 2 формируется адрес микрокоманды типа F, с выхода поля 1 о2 блока 1 памяти микрокоманд считывается унитарный код L-ro устройства (группы устройств), а с выхода 1оЗ микроопераций в шину 29 постзтает адресный код управления По унитарному коду на выходе 30 N-:ro устройства на соответствующем разряде входа 35 сигналов передачи управления Ь-го устройства (группы устройств ) появляется единичный сигнал

передачи управленияо Этот сигнал через элемент ИЛИ 14 поступает на мультиплексор А адреса, который согласно ,описанному алгоритму своей работы пропускает на вход регистра 2 адреса адресный код управления с шины 29, Кроме того, сигнал передачи управления через элемент ИЛИ 15 устанавливает в единичное состояние триггер 10 пуска L-ro устройства и обнуляет триггер 8 огаибкио Очередной тактовый импульс 2 с второго выхода 40,2 генератора 40 пройдет через элемент И 21 на первый вход элемента И 22 и вход синхронизации регистра 3 микрооперации Однако сигнал ошибки элементом И 21 сформирован не будет из-за присутствия на его третьем инверсном входе единичного сигнала с первого выхода дешифратора 6, а запись в регистр 3 запрещена сигналом с выхода триггера 11 состояния По очередному-тактовому импульсу 7 с выхода генератора 40 единичный сигнал передачи управления с выхода элемента ИЛИ 15 L-ro устройства через элемент ИЛИ 16 запишется в триггер 9 о По заднему фронту этого же тактового импульса Ti в регистр 2 L-ro устройства запишется адресный код управления, а в регистр 2 N-ro устройства адрес микрокоманды типа Р. Если в L-M устройстве не было сбоя, оно исправно и адресный код управления записан без искажений-, то из блока 1 памяти микрокоманд L-ro устройства считьшается первая микрокоманда микропрограммы или микропрограммы, которую потребовало выполнить N-e устройство о В полях I признака таких микрокоманд записан код, по которому формируется сигнал на втором в ыходе дешифратора 6, Этот сигнал запрещает формирование элементом И 22 сигнала ошибки, так как поступает на его четвертый инверсный вход. Кроме того, этот же сигнал обнуляет триггер 11 состояния; таким образом, на выходе 34 cocfoяния L-ro устройства единичный сигнал исчезает и разрешается запись первого микрооперационного кода в регистр 3 L-ro устройства Если же L-e устройство бьшо неисправно или адресный код управления был воспринят им искаженным то на втором выходе дешифратора 6 единичный сигнал не появится,триггер 1 I останется в единичном состоянии.

запись в регистр 3 будет заблокирована, на выходе 34 состояния L-ro устройства останется единичный сигнал. Кроме того, по очередному тактовому импульсу Т с выхода элемента И 21 элемент И 22 L-ro устройства сформирует сигнал ошибки, который устанавливает в единичное состояние триггер

8 ошибки и через элемент ИЛИ 13 об- : нуляет триггер 10 пуска, стирает из регистра 2 адреса искаженный адресный код управления, L-e устройство как бы о ;тается в состоянии ожидания адресного кода управления, но на его выходе формируется единичный сигнал ошибки,

В этом же такте работы системы из блока 1 памяти микрокоманд N-ro

устройства считывается микрокоманда типа FO

На четвертом выходе дешифратора 6 формируется единичный сигнал,разрешающий запись в счетчик 7 Мультиплексор 5 логических условий пропускает на свой выход сигнал логического условия состояния L-ro устройства с его выхода 34 Если L-e устройство после передачи ему адресного кода управления заработало в режиме управления, т.е, на его выходе состояния единичный сигнал отсутствует, то элемент И 24 и сумматор 12 по модулю два по единичному сигналу с четвертоГО выхода дешифратора 6 формируют единичные значения двух младших разрядов адреса очередной микрокоманды. Значения остальных разрядов адреса очередной микрокоманды в поле 1о4

блока 1 памяти микрокоманд совпадают со значениями разрядов адреса соответствующей микрокома1зды типа D, По такому адресу микрокоманды типа D, но с модифицированными единичными младшими разрядами W-e устройство (группа устройств) и переходит в любой другой режимо При этом записанная в счетчик 7 задним фронтом тактового импульса с выхода элемента И 21 1 стирается единичным сигналом с предпоследнего младшего разряда выхода- регистра 2 адреса Если адресный код управления передавался нескольким устройствам сразу,

то далее из блока 1 памяти микрокоманд К-го устройства считывается микрокоманда Т1ша F - проверка приема адресного кода управления устройством системы

10

15

20

25

30

В случае, если L-e устройство при считывании в W-M устройстве микрокоманды типа F остается в состоянии ожидания адресного кода управ- ления, то на выходе мультиплексора 5 N-ro устройства будет присутствовать единичный сигнал. По этому сигналу и единичному сигналу с четвертого выхода дешифратора 6 сумматор 12 по модулю два и элемент РШИ 19 формирует нулевые значения двух младших разрядов адреса очередной микрокоманды Таким образом, из блока 1 памяти микрокоманд N-ro устройства в следующем такте работы будет снова считана микрокоманда типа D, т.е повторится цикл подготовки и передачи того же самого адресного кода управления. При этом каждый раз при проверке передачи адресного кода управления, Тоео при каждом считывании микрокоманд типа Р, единичный сигнал с четвертого выхода дешифратора 6 разрешает запись в счетчик 7 и очередной тактовый импульс % своим задним фронтом увеличивает на единицу содержимое счетчнка 7 Если при передаче адресного кода управления действительно произошел сбой,то при повторных передачах адресного кода управления L-e устройство (группа устройств) начнет реализацию нужной микропрограммы или микроподпрограммы, единичньЙ1 сигнал с выхода 34 состояния L-ro устройства исчезнет и N-e устройство выйдет из режима передачи управления, обнулив- при этом единичным сигналом предпоследнего младшего разряда адреса очередной микрокоманды с соответствующего выхода регистра 2 адреса счет- : чик 7о В случае, если k попыток (k - коэффициент пересчета счетчика 7) передать адресньй код устрой-, ства L-му устройству оказались без- , результатными, то это устройство считается отказавшим. При считывании k-й микрокоманды проверки правильности приема L-M устройством адресного кода управления (МК типа F) по очередному тактовому импульсу с выхода элемента И 21 в kr-й раз увеличится содержимое счетчика 7оНа его выходе появится единичный сигнал, 55 который, поступая на элемент ИЛИ 19, определит единичное значение пред- / последнего младшего разряда адреса очередной микрокоманды Таким обра- :

150099А . . 20

зом, если после k-й попытки передать адресный код управления L-му устройству на выходе мультиплексора 5 будет присутствовать единичное значение логического условия сигнала состояния с выхода 34 L-ro устройства, то в . N-M устройстве формируется адрес микрокоманды типа G, По ее записи в регистр 2 адреса счетчик 7 обнуляется единичным сигналом с выхода предпоследнего младшего разряда регистра 2 адреса. Микрокоманда типа G - микрокоманда реакции на отказ L-ro уст- ройства,

При обеспечении живучести распределенной управляющей системы наиболее важные микропрограммы и микроподпрограммы L-ro устройства, от реализации которых зависит работа других управляющих устройств, резервируются в определенных устройствах Тогда микрокоманда типа G может являться первой микрокомандой специальной микропрограммы передачи нужного адресного кода управления устройству, в котором зарезервирована нужная микропрограмма. Описанным образом организуется вза1шоде ствие устройств системы и их согласованное функционированиеФормула изобретения

35

40

45

Устройство для программного управления, содержащее блок памяти микрокоманд, регистры адреса и микроопераций, мультиплексоры адреса и логических условий, триггеры пуска и ошибки и первый элемент ИЛИ, выход которого соединен с возвратными входами триггера пуска и регистра адреса, информационные выходы которого соединены с aдpec ыми входами блока памяти микрокоманд, выходы кода микроопераций и кода логических условий которого соединены соотвественно с информационными входами регистра микроопераций и адресными входами мультиплексора логических условий, соответст- 50 вующие информационные входы которого являются входами логических условий устройства, выходы кода адреса блока памяти микрокоманд соединены с второй группой информационных входов мультиплексора адреса, а выхо;; младшего разряда выходов кода адреса блока памяти микрокоманд соединен с соответствующим информационным входом мультиплексора логических уело5

5

0

5

Устройство для программного управления, содержащее блок памяти микрокоманд, регистры адреса и микроопераций, мультиплексоры адреса и логических условий, триггеры пуска и ошибки и первый элемент ИЛИ, выход которого соединен с возвратными входами триггера пуска и регистра адреса, информационные выходы которого соединены с aдpec ыми входами блока памяти микрокоманд, выходы кода микроопераций и кода логических условий которого соединены соотвественно с информационными входами регистра микроопераций и адресными входами мультиплексора логических условий, соответст- 0 вующие информационные входы которого являются входами логических условий устройства, выходы кода адреса блока памяти микрокоманд соединены с второй группой информационных входов мультиплексора адреса, а выхо;; младшего разряда выходов кода адреса блока памяти микрокоманд соединен с соответствующим информационным входом мультиплексора логических уелоВИЙ, информационные выходы регистра микроопераций являются выходами микроопераций устройства, соответствующий выход конца работы информационных выходов регистра микроопераций соединен с первым входом первого элемента ИЛИ, информационные выходы мультиплексора адреса соединены с информационными входами регистра адреса, а первая группа информационных входов мультиплексора адреса является группой входов кода операции,о т- личающееся тем, что, с целью расширения функциональных возможностей и области применения устройства, в него введены дешифратор, счетчик, триггеры контроля и состояния, сумматор по модулю два, второй, третий, четвертый, пятый, шестой и седьмой элементы ИЛИ, первый,второй, третий, четвертый, пятый элементы И, первый и второй магистральные элементы и шина адресного кода управления, выходы которой являются выходами адресного кода управления устройства, первый разряд выходов поля признака блока памяти микрокоманд соединен с первьм входом дешифратора и возвратным входом регистра микроопераций, соответствующий выход конца работы информационных выходов которого соединен с установочным входом триггера состояния, выход которого соединен .с первым входом пятого элемента ЦПИ, выход которого соединен с-управляющим входом регистра микроопераций и является выходом состояния устройства, второй и третий разряды выходов поля признака блока памяти микрокоманд соединены соответственно с вторым и третьим входами дешифратора, первый выход которого соединен с-вторым адресным входом мультиплексора адреса, с первым входом четвертого элемента ИЛИ и с третьим инверсным входом третьего элемента И, выход которого соединен с установочным входом триггера ошибки и вторым вхо дом первого элемента ИЛИ,выходы кода логических условий блока памяти микрокоманд соединены с информационными входами первого магистрального элемента, выходы которого являются выходами сигналов передачи управления устройства, выходы кода микроопераций блока памяти микрокоманд соединены с информационными входами второго магистрального элемента,вы

5

0

ходы которого соединены с шиной адресного кода управления, а. через нее с третьей группой информационных входов мультиплексора адреса,выход предпоследнего младшего разряда выходов кода адреса блока памяти микрокоманд соединен с первым входом седьмого элемента ИЛИ, выход которого соединен с предпоследним младшим разрядом второй группы информационных входов мультиплексора адреса, предпоследний младший разряд инфор- мацио нных вькодов регистра адреса соединен с возвратным входом счетчика, выход которого соединен с третьим входом седьмого элемента ИЛИ, выход мультиплексора логических условий соединен с инверсным входом пятого элемента И и с первым входом сумматора по модулю два, выход которого соединен с младшим разрядом второй группы информационных входов мультиплексора адреса, второй выход

5 дешифратора соединен с четвертым инверсным входом третьего элемента И и с возвратным входом триггера состояния, третий выход дешифратора соединен с соответствующим разрядом ин0 формационных входов регистра микроопераций, четвертый выход дешифратора соединен с управляющим входом счетчика, с вторым входом сумматора по модулю два и с вторым входом пятого элемента И, выход которого соединен с вторым входом седьмого элемента ИЛИ, пятый выход дешифратора является выходом запроса устройства и соединен с первым входом четвертого элемента И, второй инверсный вход которого является входом ответа на запрос устройства, шестой выход дешиф-, ратора соединен с управляющими входами первого и второго магистральных элементов и с первым входом шестого элемента ИЛИ, вьгход которого соединен с соответствующим разрядом адресных входов мультиплексора логических условий, выход триггера ошибки соединен с вторым входом пятого элемента ИЛИ и является выходом ошибки устройства, выход триггера контроля соединен с вторым входом j peTbero элемента И, выход триггера пуска соединен с первыми входами первого и второго элементов И, входы сигналов передачи управления устройства соединены с входами второго элемента ИЛИ,выход которого соединен с первым адресным

5

0

5

0

5

231500

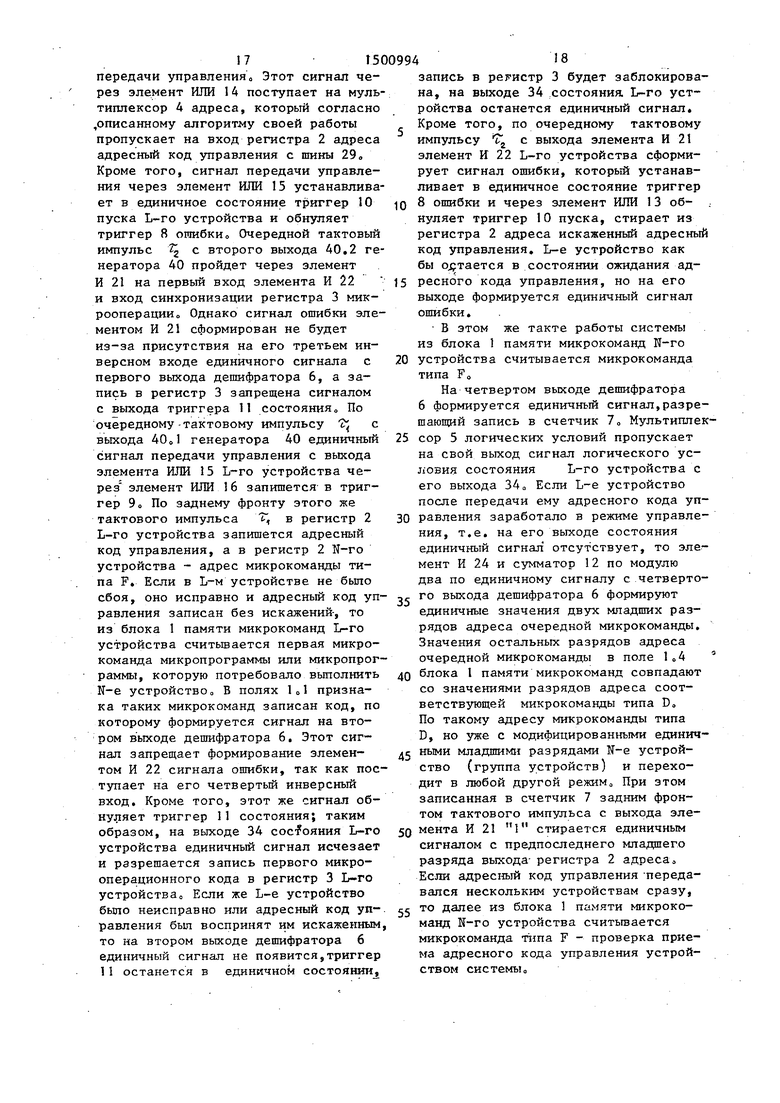

входом мультиплексора адреса и с пер- вьм входом третьего элемента ЮШ,выход кото.рого соединен с вторым входом четвертого элемента ИЖ, с установочными входами триггеров пуска и ошибки, выход четвертого элемента ИЛИ соединен с информационным входом триггера контроля, первый вход синхронизации устройства соединен с сикх- ровходом триггера контроля и с вторым входом первого элемента И,выход которого соединен с синхровходом редится контроль попадания в начало МП

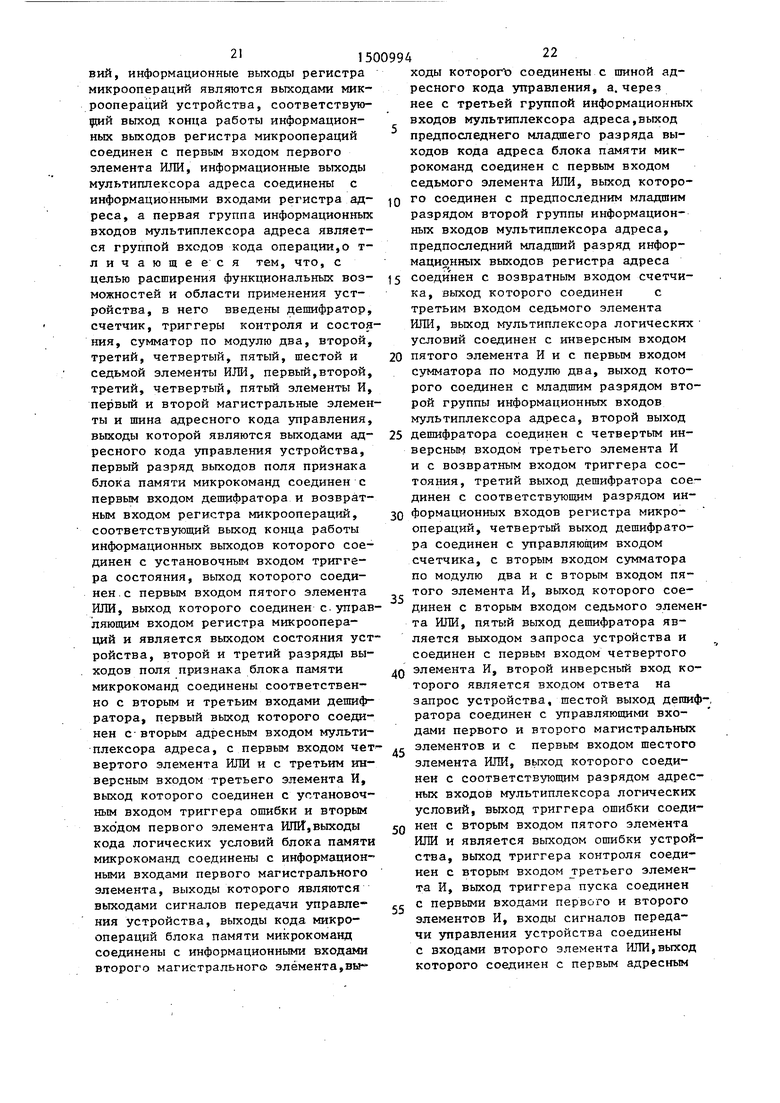

Ожидание кода очередной МП (в исходном состоянии устройства, ожидание кода диагностич, МП) Проверка режима работы L-ro устройства (которому нужно передать АКУ), посыка запроса в определитель 41 приоритета и проварка разрешающего сигнала из него

Переда а АКУ L-му устройству (группе устройств), блокируется RG 3, открыв 25 и 26

Проверка правильности приема L-M устройством АКУ, посыпка импульса в счетчик 7, инвертироМЛ, разряда адреса следующей МК

МК реакции на отказ L-ro устройства, обнуление счетчика 7

Н Последняя МК в МП, переход в режим ожидания АКУ

. 24

гистра адреса., второй вход синхронизации устройства соединен с вторым входом второго элемента И, выход которого соединен с первым входом третьего элемента И, с входом синхронизации регистра микроопераций и с входом прямого счета счетчика, выход четвертого элемента И соединен С вторым входом шестого элемента ИЛИ, второй вход третьего элемента ИЛИ является входом пуска уст- ройства.

0...00 0...0 О..,00

о...о Адрес самой МК типа D ...00

Унитарный АКУ

код Ь-го

устройст.

(гр.устройств)

Адрес

МК О,..О типа D

Код МП передачи АКУ. резервному устройству

0...00

Ф1а2

фиг.1

UJ

n n Л n n fl

t-t guntfciafi ftrefeem Mf fttefleffnti Яй{е1гт $пяк ffftmett} « лпгпт vsftemi of уяраЯмтл

Ц / t-я enrmtiffffMcf ЛГ oMrfg j g yfttffifae/i t am sifMt HKetimeJi

Ц -г-- - e, Mtfltffffvcr ffff f-frf yortftAftf

U

---01Я /, л t-n fcaffitahЛ1 «Я(«щяш i ff f utwevfetnc offgc ЯЛ ff affrrr 8

ttfmfpefft titftfen fn t-mi ftrnfa/eiti U t fCiffHuelt Iffff tn

fft.l

MtfSaeffKa шина пврвЗсгчиАку свободна/

OiKudaemcfl AKi

u ufUMO передачи

AK{/ cBoSodHa

| Авторское свидетельство | |||

| Микропрограммное устройство управления | 1976 |

|

SU596947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для автоматического раз-гОНА и ТОРМОжЕНия дВигАТЕля CTAHKA СпРОгРАММНыМ упРАВлЕНиЕМ | 1975 |

|

SU834669A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для автоматического разгона и торможения двигателя станка с программным управлением | 1983 |

|

SU1149221A1 |

Авторы

Даты

1989-08-15—Публикация

1988-01-26—Подача