Изобретение относится к вычислительной технике, в частности к устройствам управления распределенной вычислительной системой,, включающей узлы обработки информации и линии связи.:

Известно устройство для управления управляющей логической систеш й, содержащее групповые датчики-сигнализаторы, групповые запоминающие триггера, групповые клапаны подачи питания; подачи логических переменных и взаимного соединения логических схем, универсальный логический блок. Для сокращения числа линий связи в него введены групповые клапаны передачи информации, входные и выходные линейные схемы ИЛИ и линейные реле. Устройство обеспечивает управление управляющей логической системой 1.

Недостатком устройства является низкое быстродействие.

Наиболее близким техническим решением к предлагаемому является устройство для распределения заданий процессорам, содержащее блок управления поиском и распределением, регистр готовности процессоров, процессоры, элементы ИЛИ, И, регистр сдвига С 2 .

Недостатком известного устройства является невозможность распределения заданий территориально разнесенным группам процессоров с учетом состояний процессоров и линий связи , а также маршрутов передачи данных .

10

Целью изобретения является расширение функциональных возможностей за счет управления распределением заданий территориально разнесенным группам процессоров с учетом состоя15ний процессоров и линий связи, а также маршрутов передачи данных.

Поставленная цель достигается за счет назначения заданий, в первую очередь, на те узлы обработки,

20 время передачи данных на которые является минимальным. Это обеспечивает повышение пропускной способности распределенной вычи.слйтельной систеMt

25

Поставленная .цель достигается тем, .что в устройство для управления распределенной вычислительной системой,, содержащее блок угравления, регистр сдвига, первую группу элементов ИЛИ, первую и вторую группы бло30 .ков элементов И, регистры готовности , первые входы блоков элементов И Первой группы соединены с выходами соответствующих регистров готовности, нулевые входы которых соединены с входами готовности процессоров устройства, выходы регистров готовЛости соединены с входами кода свободных процессоров блока управления выходы регистра сдвига соединены с вторыми входами блоков элементов И второй группы, выход отказа блока управления является выходом отказа Устройства, выходуправления сдвигом блока управления соединен с вхо дом управления сдвигом регистра сдв га, разрешающие входы которого соединены с выходом приема блока управ ления, информационные входы регистра, сдвига соединены с входами, кода числа необходимых процессоров устройства, которые соединены с входами, кода числа необходимых процессоров блокауправления, введены регис номера задания, регистр номера запрашивающего узла и (где и - число процессорс й регистров числа пр.оцес соров, ц регистров маршрутов, пер-. аый и второй счетчики адресов, 2. счетчиков занятых каналов ( где 2 число каналов), дешифратор узлов блок памяти узлов, блок памяти марш рутов, с третьей по седьмую группы блоков элементов И, вторая группа элементов ИЛИ, первый, второй и тре тий элементы И, первый и второй эле менты ИЛИ, элементы НЕ, три блока элементов И, причем нулевые выходы регистра сдвига соединены с входами первого элемента И, выход которого соединен с первыми входами блоков элейентов И второй группа элементов, с ВХОДОМ:конца распределения блока управления и -с--входом сброса первого счетчика адреса, счетный вход которого соединен с выходом просмотра узлов блока управления, с входом пуска блока памяти узлов, вход обнуления которого сбединен с выходом обнуленця блока управления, выход первого счетчика адреса соединен с входом адреса блока памяти узлов, выход регистра номера аапрашивающего узла соединен с первыми входами соответствующего блока элементов И третьей группы с входом ад реса блока Пс1мяти маршрутов и блока памяти узлов, выход которого соедин с входом адреса блока памяти маршру тов И с входом дешифратора узлов, выходы которого соединены с первыми входами соответствующих блоков элементов И четвертой,пятой и шестой групп и с вторыми входс1ми соответствующих блоков .элементов И первой группы, выкоя разрешения распределе ния блока управления подключен к тр тьим входам блоков элементов И первой .группы, выходы которых соедине-. ны с соответствующими входами элементов ИЛИ первой группы, выходы которых соединены с вторыми входами элементов И второй группы, выходы которых соединены с входами сброса регистра сдвига и с вторыми входами блоков элементов И пятой группы, выходы которых соединены с входами регистров числа процессоров и с единичными входами регистров готовности, выходы которых соединены с втоpfciMH входами блоков элементов и четвертой группы, выходы которых соединены с входами первого элемента ИЛИ, выход которого соединен с входом отсутствия процессоров блока управления, выход просмотра маршрутов которого соединен со счетным входом второго счетчика адреса и с входом пуска блока памяти маршрутов, выход сброса маршрутов блока управления соединен с входом сброса второго счетчика адреса и обнуления с входом блока памяти маршрутсэв, нулевые выходы которого соединены с входами второго элемента И, выход которого соединен с соответствующим входом второго элемента ИЛИ и входом начала маршрутизации блока управления, выход второго счетчика адреса соединен с входом адреса блока памяти маршрутов, единичные выходы которого соединены с первыми входами блоков элементов И седьмой группы, с группой входов первого блока элементов И и с входами третьего элемента И первого, выход которого соединен с входом отсутствия свободного маршрута блока управления и с i соответствующим входом второго элемента ИЛИ, выходы второй группы элементов ИЛИ соединены со счетными входами счетчиков занятых каналов, входы готовности каналов устройства соединены с вычитающими входами счетчиков занятых каналов, выходы которых соединены с вторыми входами блоков , элементов И седьмой группы, выходы которых соединены с входами второго элемента ИЛИ, выход которого соединен с входом первого элемента НЕ, выход которого соединен с входом наличия маршрута блока управления и с входом блока элементов И, выход которого соединен с вторыми входами блоков элементов И шестой группы, выход записи маршрута блока управления соединен с третьими входами блоков элементов И шестой группы, выходы которых соединены (С входами регистров маршрутов, выходы которых соединены с вторыми входами соответствующей блоков элементов третьей группы, выходы регистров числа процессоров соединены с в.торыми входами соответствующих блоков

элементов И третьей группы, выход приема блока управления соединен с первыми входами второго и третьего блоков элементов И, входы кода номера задания устройства соединены с вторым входом второго блока элементов И, выходы которого соединены с входом регистра номера задания, выходы которого соединены с вторым входом соответствующего блока элементов И третьей группы, выходы, которого соединены ;с выходами заголовка задания устройства и с соответствующими входами элементов ИЛИ второй группы, вход .номера запрашивающего узла устройства соединен с вторым входом третьего блока элементОв И, выход которого соединен с вkoдoм регистра номера эмтрашявающего узла, выход которого соединен с вторым входом соответствующего блока элементов И третьей группы, выходы которого соединены с соответствующими входами элементов ИЖ второй группы. .

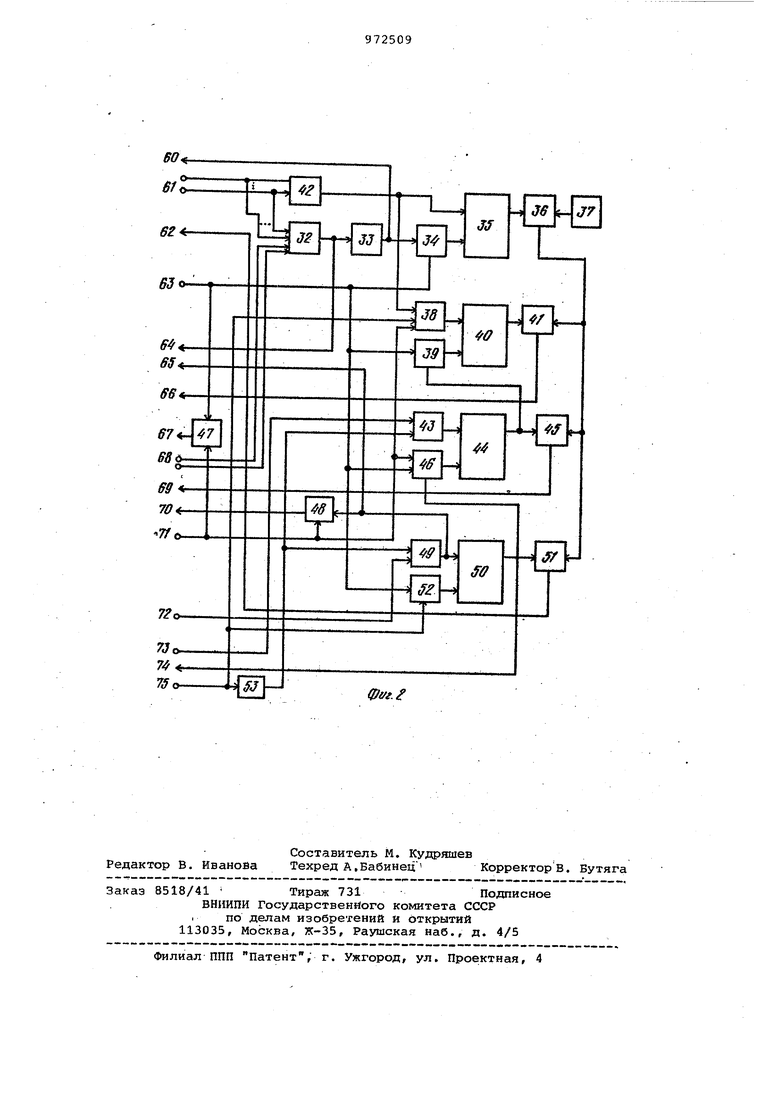

Кроме того, блдк управления содерткит четыре триггера, генератор импульсов, ,схему сравнения, восемь элементов ИЛИ, шесть элементов И, два элемента НЕ, входы Кода числа необходимых процессоров блока соеди,нены с входами первого элемента ИЛ блока и с первой группой входов схемы сравнения, вторая группа входов которой соединена с входом кода свободных процессоров блока, выход схемы сравнения соединен с выходом приема блока и с входом первого элемента НЕ выход которого соединен с выходом отказа блока и с первым входом второго элемента ИЛИ, выход первого элемента ИЛИ соединен

с первым входом третьего элемента ИЛИ и с единичным входом первого триггера, вход конца распределения блока соединен с первыми входами четвертого, пятого, шестого и седьмого элементов ИЛИ и с вторым входом второго элемента ИЛИ, выход которого соединен с нулевым входом первого триггера, единичный выход которого соединен с первым входом первого элемента И, выход генератора импульсов соединен с вторым входом первого элемента И, выход которого соединен с первыми входами в Ророго, третьего и четвертого элементов И, вход отсутствия свободного маршрута блока соединен с вторым входом третьего элемента ИЛИ, с вторыми входами пятого и седьмого элементов ИЛИ, и с первым входом восьмого элемента ИЛИ, выход седьмого элемента ИЛИ являет-, ся выходом обнуления блока, вход отсутствия процессоров соединен с вторым входом шестого элемента ИЛИ с входом второго элемента НЕ и вторым входом третьего элемента ИЛИ,

выход которого соединен с единичным входом второго триггера, единичный / выход которого соединен с вторым входом второго элемента И, выход которого соединен с выходом просмотра 5 узлов блока, вход наличия маршрута блока соединен с первым входом пятого элемента Ц, выход второго элемента НЕ соединен с первь входом шестого элемента И и с вторым входом пятого элемента И, выход которого соединен с выходом записи маршрута блока с вторым входом восьмого элемента ИЛИ и с единичным входом третьего триггера, единичный выход

5 которого соединен с вторым входом

четвертого элемента И, выход которо- го соединен с выходом управления сдвигом блока, выход шестого элемента ИЛИ соединен с кулевым входом

0 третьего триггера, единичный выход которого соединен с выходом разрешения распределения блока и с вторым входом пятого элемента ИЛИ, выход которого соединен с нулевым входом

5 четвертого Триггера, единичный выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с нулевым внодом второго триггера, вход начала маршQ РУтизации блока Ьоединен с вторым

входом шестого элемента И, выход ко- . торого соединен с единичным входом четвертого триггера, единичный выход которого соединен с вторим входом третьего элемента И, выход которого является выходом просмотра маршрутов блока, выход восьмого элемента ИЛИ является выходом сброса маршрутов блока.

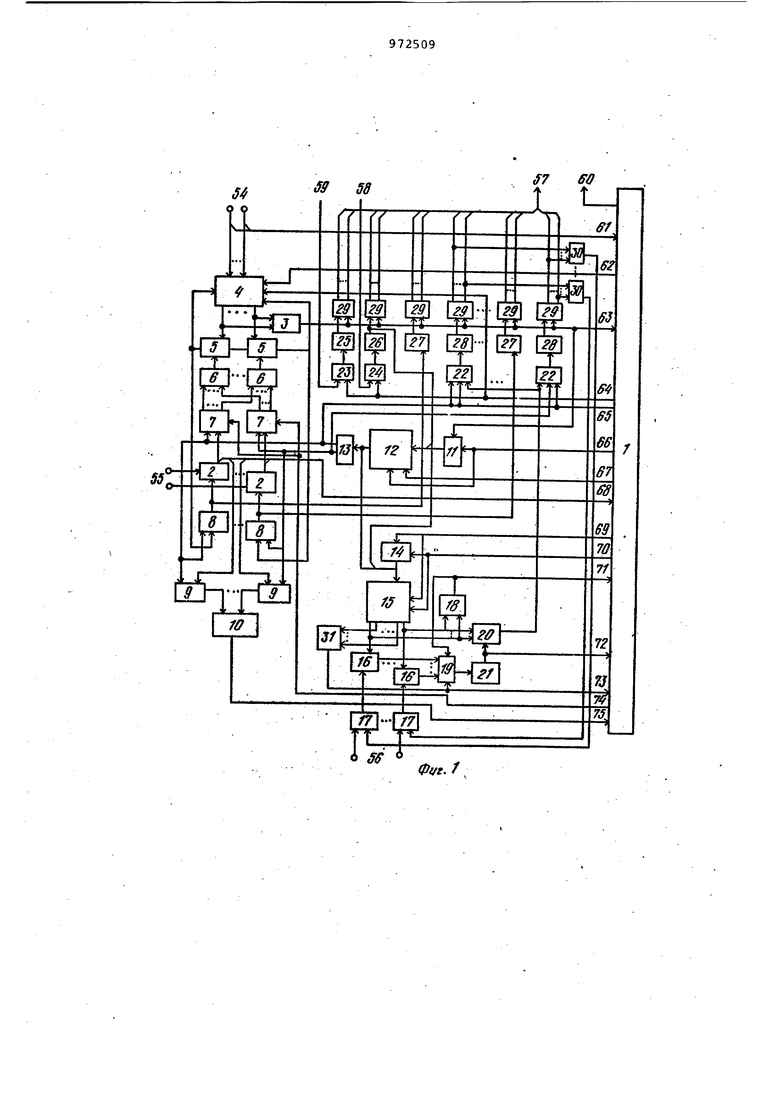

На фиг.1 представлена структурная схема устройства; на фиг,2 структурная схема блока управления.

Устройство содержит блок.1 управления, регистр 2 готовности,первый элемент И 3 окончания распределения,

5 регистр 4 сдвига, первую группу

блоков элементов И 5, первую группу элементов ИЛИ 6, вторую, третью и четвертую группы блоков элементов И 7-9, первый элемент ИЛИ 10, пер-

0 вый счетчик 11 .адреса, блок 12 памяти узлов, дешифратор 13 узлов, второй счетчик 14 адреса, блок 15 памяти маршрутов, пятую группу блоков элементрв И 16, счетчик 17 за- нятых каналов, второй элемент И 18, второй элемент ИЛИ 19, шестую группу блоков элементов И 20, первый элемент НЕ 21, седьмую, восьмую и девятую группу блоков элементов И 22 24, регистр 25 номера задания, ре0 гисТр 26 номера запрашивающего узла, регистр 27 числа процессоров, регистра 28 маршрутов, десятую группу блоков элементов И 29, вторую группу элементов ИЛИ 30, третий элемент И 31, элемент 32 сравнения, второй элемент НЕ 33, третий элемент ИЛИ 34, триггер 35 пуска, четвертый элемент И 36, генератор 37 импульсов, четвертый и пятый элементы ИЛИ 38 и 39, триггер 40 узлов, пятый элемент И 41, шестой элемент ИЛИ 42 шестой элемент И 43, триггер 44 марш рутов, седьмой элемент И 45, седьмой, восьмой и девятый элементы ИЛИ 46 - 48, восьмой элемент И 49, триггер 50 распределения, девятый элемент И 51, десятый элемент ИЛИ 52, трзтий элемент НЕ 53, шины 54 кода числа необходимых процессоров, ши-;. ны 55 готовности процессоров, шины 5 готовности каналов, шины 57 заголовка задания, шины 58 номера запрашивающего узла, шины 59 номера задания, первый выход 60 блока 1 управления, первый вход 61 .блока 1 управления, второй выход 62 блока 1 управления, второй,вход 63 блока 1 управления, третий, четвертый, пятый и шестой 64 - 67 блока 1 управления, третий вход 68 блока 1 упч равления, седьмой и восьмой выхбды 69 и 7Qблока 1 управления, четвертый, пятый и шестой входы 71 г- 7 блока 1 управления, девятый выход 74 блока Ъ управления, седьмой вход 75 блока 1 управления. Устройство работает следующим образом. Известно, что распределенные вычислительные cиcтe vIЫ (РВС) могут содержать пСп 1)-узлов обработки Да ных, соединенных между собой z линиями связи. Каждый j-ый (j 1, п) узел включает в свой состав программно совместимых процессоров, позволяющих независимо друг от выполнять задания по обработке данных, а 1-ая {1 1, z) линия свя зи состоит из РА g каналов связи. В такихРВС задания на обработку данных выдаются пользователями, ра1мещаемыми на узлах обработки. За дания пользователей, располагаемых на i-музле, может быть, выполнено на. J-M узле (j 1), если на j-м узле имеется необходимое количество свободных процессоров, а в противном случае на группе j , jj, , , ., J узлов обработки, если суммгфное количество свободных процессоров на этой группе узлов больше или равно количеству необходимых для выполнения задания процессоров и имеются свободные линии связи, обеспечивающие передачу частей задания на эти узлы. В группу узлов обычно включаются те узлы, передача задания к которым П9требуёт наименьшего количества линий свяйи и промежуточных узлов коммутации . В исходном состоянии в J-м (J в 1, п) регистре 2 готовности хранятся данные о готовности к работе процессоров J-ro узла обработки, ав Ё-м (1 1 - z) счетчике 17 количество Pg занятых каналов в t-й линии связи. Триггеры счетчиков 11 и 14 адресов и триггеры 35, 40, 44 и 50 находятся в нулевом состояний. В блоке 12 номеров узлов хранится п массивов г-разрядных чисел (г ) . Любой массив содержит п ячеек, в каждой из которых записан код номера узла, на котором возможна обработка задания. Коды номеров узлов внутри 1-го массива могут быть упорядочены, например, по удаленности от I-го узла обработки. Для обращения к блоку 15 используется адрес, включающий поле базы, задающей номер 1 массива данных, я поле адреса, задающего номер числа в массиве. В блоке 15 маршрутов хранится п массивов z-разрядных чисел. Каждый ij- массив содержит чисел, равных количеству маршрутов их i-ro в j-ый узел. Маршруты могут быть удорядочены в каждом:ij-м массиве, например, в порядке возрастания их длин, или количества промежуточных центров когФ утации из i -го в j-й узел. Каждый JJ-й массив заканчивается ячейкойf в которой ааписан код, содержащий единицы во всех разрядах, для отделения одного массива от другого. Для обращения к блоку 15 маршрутов используется адрес, включаиощий поле базы и поле смещения, задаю1две номер j-ro массива, а также поле адреса, задающего номер числа в массиве. Устройство обеспечивает формирование заголовка задания, включающего номер задания; номер i запрашивающего узла, от которого поступило задание; количество процессоров, необходимых для обработки задания на каждом узле и маршруты передачи задания к этим узлам. В работе устройства можно выделить три этапа.. На первом этапе осуществляется проверка возможности выполнения задания в РВС и прием задания на обслуживание. По шинам 54 код необходимого для выполнения задания числа процессоров поступает на входы элемента ИЛИ 42 и на первые входы элемента 32 сравнения. Одновременно по шинам 59 и шинам 58 поступают соответственно код номера задания и код номера i запрашивающего, узла. При этом на выходе элемента ИЛИ 42 появляется сигнал, устанавливающий триггер 35 пуска в единичное состояние. На вторые входы элемента 32 сравнения поступает код количества свободных процессоров с регистров 2 готовности. Элемент 32 сравнения сравнивает код необходимого количества процессоров с кодом количест ва свободных процессоров. Если коли чество свободных процессоров меньше количества необходимых,, то на вы ходе элемента НЕ 33 и выходной шине 60 появится сигнал отказа от выполнения задания, который через эле мент ИЛИ 34 сбрасывает триггер 35 пуска в нулевое состояние. Если количество свободных процес соров в РВС больше либо равно количеству необходимых процессоров, то на выводе элемента 32 сравнения появится сигнал, разрешшо1ф й прием в устройство кодов номера задания, номера i запрс1ШИЕ)аю1цего узла и числа меобходи КЁК для выполнения згщания процессоров. Код номера задания через группу элементов И 23 запишется в регистр 25, код J номера залрашивакяаего узла через группу эл ментов И 24 запишется в регистр 26 и поступит на базовые адресные входы блоков 12 и. 15. Код числа необходимых для выполнения задания процессоров примется в.регистр 4 сдвига. На этом первый этап работы устройства закапчивается. На вторе этапе производится определение номеров узлов, на которых возможна обработка, маршрутов передачи данных на эти узлы, а также вы деление процессюров на выбранных узлах для выполнения задания. Второй этап выполняется за несколько шагов. Каждый шаг, в общем случае, включает три типа итераций. В начале каяздого шаса выполняется итерация первого типа, обеспечивающая поиск ближайшего к i.-му запрашивающему узлу j-ro узла обработки, на Котором имеются в рассматриваемый мсялент времени свободные процессоры. Выполнение итерахши начинается с ус тановки в единичное состояние триггера 40 узлов и обращения к-ПЗУ 12 по адресу, образованному кодом I но мера запра11ивающего.;узла и содержимым счетчика 11 ajtipeca. С появлением импульса на выходе элемента И 4 из блока 12 считываешся номер j-ro узла и на j-м выходе дешифратора 12 появится сигнал. Это-г сигнал разрешает выдачу содержимого j-ro регист ра 2 готовности на j-ю группу элементов И 9. Если с нулевых выходов триггеров j-го,регистра 2 готовности поступают одиночные сигналы, сообщающие о том, что в J-M узле все процессоры заняты, то на выходе j-r I элемента И 9 появится единичный сиг нал, поступающий через элементы ИЛИ ,и 38 на единичный вход триггера 40 узлов, разрешая прохождение импульсов на счетный вход счетчика 11 и запускающий вход блока 12. При этом адрес обращения в блоке 12 увеличивается на единицу по сравнению с предыдущим циклом считывания, что обеспечивает выборку очередного-номера узла. Описанная выше итерация первого типа повторяется до тех пор, пока не будет найден узел, на котором имеются свободные процессоры. В этом случае появляется нулевой сигигш на выходе j-й группы элементов И 9, а на выходе элемента НЕ 53 появится единичный сигнал. Этот сигнал через элемент И 43 устанавливается в единичное состояние триггер 44 маршрутов . Сигнал с единичного выхода триггера 44 через элемент ИЛИ 39 устанавливается в нулевое состояние триггер 40 узлов, что запрещает прохождение импульсов на запускающий вход блока 12.Это обеспечивает за:поминание номера j-ro узла, содержа-, щего свободные процессоры. На этом итерация первого типа заканчивается. Итерация второго типа выполняется после итергщии первого типа и осуществляет выбор кратчайшего маршрута из i-ro узла в j-й с учетом свободных линийсвязи. Выполнение итерации начинается с обращения к блоку 15 по адресу, образованному кодом i . запрашивающего узла, кодом j ноъюра узла и содержимым счетчика 14 адреса. С появлением сигнала на выходе элемента И 45 из блока 15 считывается по сформулированному адресу код кратчайшего маршрута из }-го уэла в j-й. Этот код поступает на первые входы группы элементов И 16, на вторые входы .которых поступают сцгиалы готовности линий связи с выходом Kg,4(l l,z) разрядов счетчиков 17. Предполагается, что К -и разряд счетчика 17 находится в единичнс состоянии, если в t-Л линии связи заняты все Р каналов. Если хотя бы одна линия связи в выбранном марнируте занята, то на выходе соответствующего 1-го элемента И 16 появится сиг.нал, запрещающий вьщачу кода маряирута из блока 15 в j-й регистр 28. С приходом очередного импульса с выхода элемента И 45 осуществляется формирование последовательности номеров маршрутов с помощью счетчика 14 адреса, пуск ПЗУ 15 для считывания кода маршрута и проверка наличия с вободных линийг используемых в данном маршруте. Описанный процесс поиска свободных МсфШРУтов повторяется по тех пор, пока не .будет обнарузкен свободный кратчайший маршрут,.из i-ro в j-й либо не будут счи.таны все

марируты из ij-ro массива данных ПЗУ 15. В последнем случае, при очередном запуске ПЗУ 15 будет считан код, содержащий единицы во всех разрявдах. В этом случае прерывается выполнение итерации второго типа и производится переключение на выполнение итерации первого типа. Для этого с выхода элемента И 18 сигнал поступает на единичный вход триггера 40 узлов, нулевой вход триггера 44 маршрутов и на первые входы элементов ИЛИ 47 и 48. На выходе элементов ИЛИ 47 и 48 появляются единичные сигналы,, устанавливающие соответственно в нулевое состояние ПЗУ 12 узлов иПЗУ 15 маршрутов. Пр переключении триггера 44 маршрутов в нулевое состояние снимается разрешающий сигнал с входа элемента И 45, что прекращает Поступление импульсов на запуск ПЗУ 15.

Если при выполнении итерации второго типа ПЗУ 15 считан код маршрута, для которого свободные линии связи, то на выходе элемента НЕ 21 появится сигнал, разрешающий выдачу кода маршрута.через группу элементов И 20 на входы j-й 5группы элементов И 22. Запись кода маршрута в -й регистр 27 маршрута осуществляется при наличии сигналов на j-м выходе дешифратора на выходе элемента И 49, поступающих на входы j-й группы элементов И 22. Сигнал ,с выхода элемента И 49 поступает на единичный вход триггера 50 распределения и через элемент..ИЛИ 48 на . обнуление счетчика 14 адреса. На этом итерация второго типа, заканчивается.

Итерация третьего типа выполня- . ется после итерации второго типа и осуществляет назначение частей задания на свободные процессоры.:.выбранного узла обработки. С этой целью производится выдача содержимого J-r регистра 2 готовности по сигналу с единичного выхода триггера 50 распределения на первые входы группы элементов -И 5. При, этом на выходах некоторых элементов И 5 появится разрешающий сигнал. Очевидно, что номера этих элементов определяются совпадением одноименных единичных разрядов в j-м регистре 2 готовности и регистра 4 сдвига. С выходов элементов И 5 сигналы поступают на сброс соответствукяцих триггеров регистра 4 сдвига и j-ro регистра 2 готовности через соответствующие элементы И 8 J-й гр1уппы. Одновременно с этим сигналы с .соответствующих выходов элементов И 8. j-й группы поступают н установку в еди ничное состояние триггеров j-ro регистра 2 числа процессоров на j -м узле обра,ботки, назначенных на выполнение части задания. Если при этом в регистре 4 сдвига остались триггера в единичном состоянии, о чем сообщает сигнал на выходе элемента И 3

окончания распределения, то с выхода элемента И 51 в регистр 4 сдвига подаются импульсысдвига до., .тех пбр,.пока j-й регистр 2 готовности не будет полностью обнулен. Если все

триггеры j-ro регистра 2 готовности сброшены в нулевое состояние, то на выходе j-ro элемента И 9 появится сигнал, который через элемен-. с ты ИЛИ 10 и 52 установит триггер 50

распределения в нулевое, а через элемент ИЛИ 38 триггер узлов 40 в единичное состояние. На этом итерация третьего типа заканчивается. Если при этом не все разряды регистра 4 сдвига обнулены, то устройство повторяет итерацию первого типа поиска свободных узлов РВС, выдавая разрешающий сигнал через элемент И 41, на.прохождение импульсов

на счетный вход счетчика 11 адреса и залуск ПЗУ 12.

При установке в нулевое состояние всех разрядов регистра 4 сдвига на очередном шаге выполнения итррации третьего типа элемент И 3 окончания распределения выдает сигнал, который через элементы ИЛИ 34, 39, 46 и 52 сбрасывает триггеры 35, 40, 44 и 50 в нулевое состояние.

Это означает, что задание распределено среди процессоров на выбранных узлах йбработки. На этом заканчивается выполнение итерации третьего типа и выполнение второго типа. . На третьем этапе производится выдача сформированного заголовка задания в выходные шины 57 устройства. Сигнал с выхода элемента И 3 поступает на вход группы элементов И 29 и разрешает выдачу заголовка задания из регистров 25 - 28 в выходные даны 57. При вьщаче заголовка задания появляется сигнал, на выходе (t 1, z) элемента ИЛИ 30, если имеется код, равный единице, в К-м.раэряде одного из регистров 28 маршрута. сигнал поступает на счетный вход 2-го счетчика 17 и увели-, чивает его содержимое на единицу, что обеспечивает учёт занятости одного канала- в t-й линии связи.

Таким образом, предлагаемое устройство обеспечивает управление распределением заданий территориально разнесенным группам процессоров, заклю.чающееся в.-.выделении необходимого числа процессоров в узлах, .обработки распределенной вычислительной .системы, которые являются ближайши:ми к запрашивающему узлу, и выделение необходимых линий связи для передачи частей задания по кратчайшему маршруту, за счет чего расишряются функциональные возможности устройства,

Формула изобретения

1. Устройство для управления распределенной вычислительной системой, содержащее блок управления, регистр сдвига, первую группу элементов ИЛИ, первую и вторую группы блоков эле-е. ментов И, регистры готовности, первые входы блоков элементов И первой группы соединены с выходами соответствующих регистров готовности, нулевые входы которых соединены..с входами го овности процессоров устройства, выходы регистров готовности соединены с входами кода свободных процессоров блока управления, выходы регистра сдвига соединены с вторьами входс1ми блоков элементов И второй группы, выход, отказа блока управления является выходом отказа устройства, выход управления сдвигом блока управления соеданен с входом управления сдвигом регистра сдвига, разрешающие входы которого соединены с выходом приема блока управления, информационные входы регистра сдвига соединены с входами кода числа необходимых процессоров устройства, которые соединены с входами кода числа необходимых процессоров блока управления, отличающееся тем, что, с целью расширения области применения устройства, в него введены регистр номера задания, регистр номера запращивающего узла, И ( где и - число процессоров) регистров числа процессоров, л регистров маршрутов, первый и второй счетчики адресов. Т счетчиков занятых каналов (.где т.- число каналов), дешифратор узлов, блок памяти узлов, блок памяти маршрутов, с третьей по седьмую группы блоков элементов И, вторая группа элементов ИЛИ, первый, второй и третий элементы И, первый и второй -элементы ИЛИ, элемент НЕ, три блока элементов И, причём нулевые выходы регистра сдвига соединен:) ны с входами первого элемента И, выход которого соединен с первыми входами блоков элементов И второй группы элементов, с входом конца распределения блока управления и с входом сброса первого счетчика адреса счет, ный вход которого соединен с выходом просмотра узлов блока управления, с входом пуска блока памяти узлов, вход обнуления которого соединен с выходом обнуления блока управления, выход первого счетчика адреса соединен с входом адреса блока памяти узлов, выход регистра номера запрашивающего узла соединен с первыми входами соответствующего блока , элементов И третьей группы, с входом адреса блока маршрутов и блока памяти узлов, выход которого соединен с входом адреса блока памяти маршрутов и с входом дешифратора узлов, выходы которого соединены с первыми входами соответствующих блоков элементов И четвертой, пятой и шестой групп и с вторьохи входами соответствующих блоков элементов И первой группы, выход раэрешег

ния распределения блока управления подключен к третьим входам блоков элементов И первой группы, выходы которых соединены с соответствующими входами элементов ШШ первой

группы, выходы которых соединены с вторыми входами элементов И второй группы, выходы которых соединеШ: с .. входами сброса регистра сдвига и с вторыми входами блоков элементов И

пятой группы, выходы кото{Н с соединены с входами регистров тсла процессоров и с единичЕ1ыми входа14И регистров готовности, выходфя которых соединены .с вторыкш входс1МИ блоков

элементов И четвертой , выэсрдо которых соединены с входгши первого элемента ИЛИ, выход которого соединен с входом отсутствия процессоров блока угфавления, выход щюсмотра маршрутов которого соединен со счетным входом второго счетчика гшреса и с входом пуска блока памяти м яирутов, выход сброса мар1футов блока управления соединен с входом сброса второго счетчика и обнуления, с входом блока памяти маршрутов, нулевые выходы- которого соединены с входами второго элемента И, выход которого соединен с .соответствующим входом второго элемента ИЛИ и входом начала маршрутизации блока управления, выход второго счетчика адреса соединен с входом. )€ca блока памяти марц5 Угов, е ничные выходы которого соединены с первыми

входами блоков элементов И седьмой группы, с группой входов первого блока элементов И и с входами третьего элемента И, выход которого соединен с входом отсутствия свободного маршрута блока управления не соответствующим входом второго элемента ИЛИ, выходы второй группы элементов ИЛИ соединены со счетными входг1Нми счетчиков занятых каналов, входы готовности каналов устройства соединены с вычитающими входгши счетчиков занятых каналов, выходы которых соединены с вторыми входами блоков элементов И седьмой группы, выходы которых соединены с входгили второго элемента ИЛИ, выход которого соединен с входом первого элемента НЕ, выход которого соединен с входом наличия марвирута блока управления и с входом блока элементов И, выход

которого соединен с вторыми входами

блокоб элементов И шестой группы, выход записи маршрута блока управле,ния соединен с третьими входами элементов И шестой группы, вы (СОДЫ которых соединены с входами регистров маршрутов, выходы которых соединены с вторыми входами соответствующих блоков элементов И третьей группы, выходы регистров числа процессоров соединены с вторыми входс1ми соответствующих блоков элементов И третьей группы, выход приема блока управления соединен с первыми входами второго и третьего блоков элементов И, входы кода номера задания устройства соединены с вторым входом вторрго блока элементов И выходы которого соединены с входом регистра номера задания, выходы которого соединены с вторым входом соответствующего блока элементов И третьей группы, выходы которого соеди.нены с выходами заголовка задания устрЬйства и с соответствующими входами элементов ИЛИ второй Г1Е)уппы, вход номера запрашивающего узла устройства соединен с вторым входом третьего блока элементов И, выход которого соединен с входом регистра номера запрашивающего узла, выход которого соединен с вторым входом соответствующего блока элементов И третьей.группы, выходи которого соединены с соответствующими входами элементов ИЛИ второй группы,

2. Устройство по п. 1, отличающееся тем, что блок управления содержит четыре триггера, генератор импульсов, cxei сравнет. ния, восемь элементов ИЛИ-, шесть элементов И, два элемента НЕ, входы кода числа необходимых процессоров . блока,соединены с входами первого элемента ИЛИ блока и с первой группой входов схемы сравнения, вторая группа входов которой соединена с входом кода свободных процессоров блока, выход схемы .сравнения .соединен с выходом приема блока и с входом первого элемента НЕ, выход которого соединен с выходом отказа блока и с первым входом второго элемента ИЛИ, выход первого элемента (ИЛИ соединен с. первым входом треМего элемента ИЛИ и с единичным входом первого триггера, вход конца распределения блока соединен с первыми входами четвертого, пятого, шестого и седьмого элементов ИЛИ и с вторым входом второго элемента ИЛИ выход которого соединен с нулевым входом первого триггера,, единичный выход которого соединен с первым входом.первого элемента И, выход генёратора импульсов соединен с вторым входом первого элемента И, выход которого соединен с первыми входами второго, третьего и четвертого элементов И, вход отсутствия свободного маршрута блока соедийен с вторым входом третьего элемента ИЛИ с вторыми входами пятого и седьмого элементов ИЛИ и с первым входом восьмого элемента ИЛИ, выход седьмого элемента ИЛИ является выходом об нуления блока, вход отсутствия процессоров блока соединен с вторым входом шестого элемента ИЛИ, с входом второго элемента НЕ и вторым входом третьего элемента ИЛИ, выход которого соединен с единичным входо второго триггера, единичный выход которого соединен с вторым входом второго элемента И, выход которого соединен с выходом просмотра узлов блока, вход наличия маршрута блока соединен с первым входом пятого элемента И, выход второго элемента НЕ соединен с первым входом шестого элемента И и с вторым входом пятого элемента И, выход которого соединен с выходом записи маршрута блока, с вторым входом восьмого элемента ИЛИ и с единичным входом третьего триггера, единичный выход которого соединен с вторым входом четвертого элемента И, выход которо го соединен с выходом управления сдвигом блока, выход шестого элемента ИЛИ соединен с нулевым вх.6дом третьего триггера, единичный выход которого соединен с выходом разрешения распределения блока и с-вторым входом пятого элемента иЛИ, выход которого соединен с нулевым входом четвертого .триггера, единичный выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с нулевым входом второго триггера, вход начала маршрутизации блока соединен с вторым входом шестого элемента И, выход которого соединен с единичным входом четвертого триггера, единичный выход которого соединен с вторым входом третьего элемента И, выход которого является выходом просмотра маршрутов блока, выход восьмого элемента ИЛИ является выходом сброса маршрутов блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР и 433489, кл. G Об F 9/00, 1974.

2.Авторское свидетельство СССР № 629538,КЛ. G Об F 9/00,1978 (прототип) ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления распределенной вычислительной системой | 1982 |

|

SU1136159A1 |

| Устройство для распределения заданий в сетях электронных вычислительных машин | 1982 |

|

SU1075261A1 |

| Устройство для управления обменом информацией | 1987 |

|

SU1413637A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1453406A1 |

| Устройство для распределения заданий | 1980 |

|

SU903876A1 |

| Устройство для обработки запросов | 1989 |

|

SU1688248A1 |

| Устройство для формирования очереди | 1986 |

|

SU1446626A1 |

| УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПО ПРОЦЕССОРАМ | 1991 |

|

RU2017206C1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

Авторы

Даты

1982-11-07—Публикация

1981-02-03—Подача