соединены с соответствуюпщми информационными входами первого, второ1-О, третьего и четвертого триггеров регистра аргумента, первые ииформационные входы которых соединены с четвертым входом первого элемента 2И-ШШ, вторые информационные входы второго, третьего, четвертого и пятого элементов 2И-ИЛИ соединены с третьим входом первого элемента 2ИШШ, третьи управлякяцие входы второго, третьего четвертого и пятого элементов 2И-ИЛИ соединены с вторым выходом блока управления, четвертый выкоя которого соединен с четвертыми входами второго, третьего четвертого и пятого элементов 2И-ЙЛИ, единичные выходы TpjirrepoB всех регистров аргумента соединены порязрядно с информационными входами сдвигателя и второй группой информационных входов второго коммутатора.выход триггеров четвертого регистра аргумента соединен с первым входом блока формирования эиака операции, второй вход которого подключен к единичным выходам триггеров регистра аргумента, а третий вход блока формирования знака операции подключен к единичным выходам триггеров знакового разряда регистра аргумента, четвертый, пятый и шестой входы блока формирования знака операции соединены- соответственно с шестым, четвертым и седьмым входами блока управления, выход блока формирования знака операции соединен с операционным входом сдвигателя, причем блок управления содержит блок синхронизирующих импульсов, блок выбора операций, счетчик циклов, триггер двойных итераций, счетчик итераций, трехступенчатый коммутатор, коммутатор сигналов сдвига и блок формирования адреса констант, причем управляющий выход блока синхронизирующих импульсов соединен с входом блока выбора операций, выход которого соединен с управляющим входом счетчика циклов и шестым выходом блока управления, первый выход которого соединен с выходной шиной синхронизирующих импульсов, выходная шина которого соединена с третьим выходом блока управления, с тактовым входом счетчика циклов, установочными входами триггера двойных итераций и счетчика итераций выход которого соединен с входом выбора адреса блока фор4292

мирования адреса констант и информационным входом коммутатора сигна- лов сдвига, выход которого подключен к восьмому выходу блока управления, второй выход которого подключен к первому выходу трехступенчатого коммутатора, второй выход которого подключен к седьмому выходу блока управления, четвертый выход которого подключен к третьему выходу трехступенчатого коммутатора, первый информационный вход которого соединен с выходной шиной блока синхронизирующих импульсов, управляющий вход трехступенчатого коммутатора соединен с выходом блока выбора операций, второй информационный вход трехступенчатого коммутатора соединен с вторым входом счетчика циклов, первый выход которого соединен с единич11ым входом триггера двойных итераций и счетным входом счетчика итераций, первый управляшпщй вход которого соединен с единичным выходом триггера двойных итераций, второй управляющий вход счетчика итера ций соединен с выходом, блока выбора

операций, управлякящй выход которого соединен с входом блока синхронизирующих импульсов, выход блока выбора операций соединен с управляющими входами коммутатора сигналов сдвига н блока формирования адреса констант, выход которого соединен с девятым выходом блока управления, пятый выход которого соединен с четвертым выходом трехступенчатого коммутатора, причем блок формирования знака операции содержит коммутатор знаковых разрядов, первый и второй триггеры знака, схему сравнения, первый, второй, третий, четвертый и пятый элементы И, первый, второй, третий и четвертый элементы ИЛИ, первый и второй элементы НЕ, причем группа информационных входов коммутатора знаковых разрядов сое- динена с третьим входом блока формирования знака операции, первый (вход которого соединен с первым информационшшм входрм схемы сравнения, второй информацноннный вход которой соединен с вторым входом блока формирования знака операции четвертый вход которого соединен с группой управляющих входов коммутатора знаковых разрядов, первыми вхддами второго, третьего, четвертого и пятого элементов И, выход cxeh&i сравнения

соединен единичным входом второго триггера знака, нулевой вход которого соединен с выходом первого элемента И и нулевым входом первого триггера знака, единичный вход которого соединен с выходом коммутатора знаковых разрядов, единичные выходы первого и второго триггеров знака соединены соответственно .с первым и вторым входами первого злемента ИЛИ, выход которого соединен с вторыми входами третьего и пятого злементов И и входом первого злемента НЕ, выход которого соединен с вторыми входами второго и четвертого злементов И, выходы которых соединены соответственно с первым и вторым входами третьего элемента ИЛИ, . третий вход которого соединен с выходом третьего элемента И, третий вход которого соединен с шестым вхо-1 дом блока формирования знака операций и с первым и вторым входами второго элемента ИЛИ, третьему входу пятого элемента И, первому и второму входам четвертого элемента ИЛИ и первому входу первого элемента И, второй вход которого подключен к пятому входу блока, илходы второго и четвертого элементов ИЛИ подсоединены к третьим входам соответственно второго и четвертого злементов И, выход пятого элемента И соединен с четвертым входом третьего элемента ИЛИ, выход, которого соединен с выходом блока и входом второго элемента НЕ, выход которого соединен с выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1462300A1 |

| Устройство для вычисления элементарных функций по алгоритму Волдера | 1982 |

|

SU1068933A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1497615A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1728861A1 |

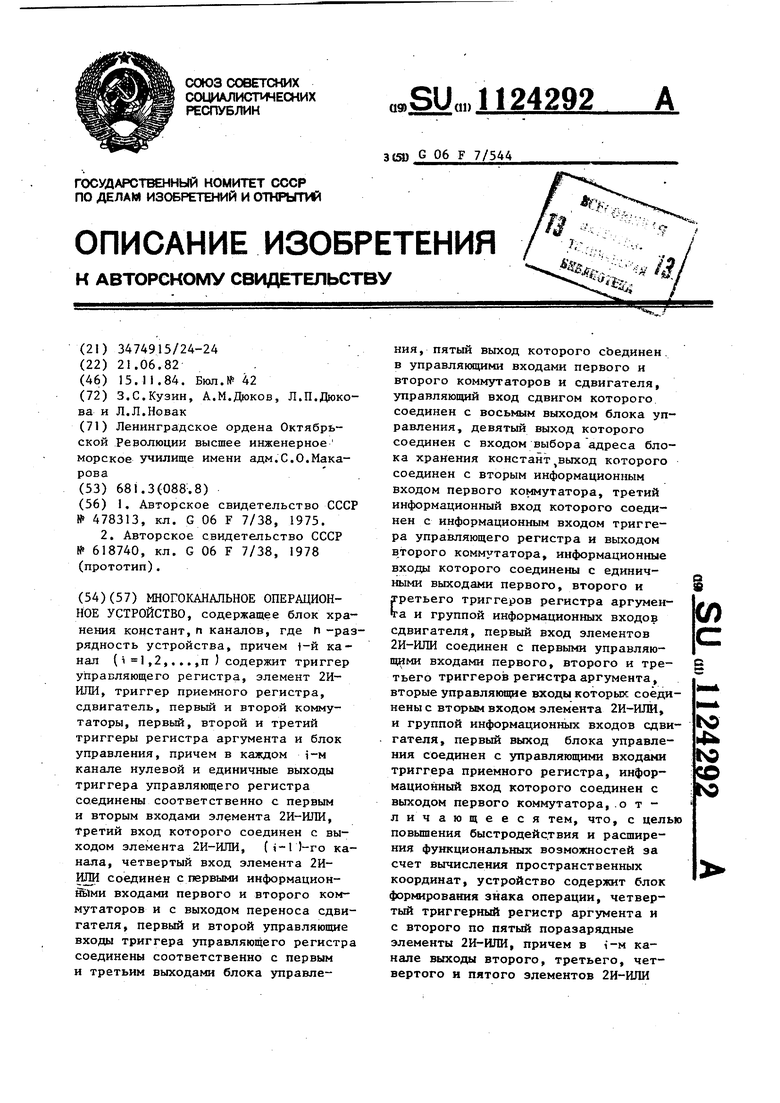

МНОГОКАНАЛЬНОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО, содержащее блок хранения констант, п каналов, где п -разрядность устройства, причем 1-й канал (i 1,2,...,п ) содержит триггер управляющего регистра, элемент 2ИИЛИ, триггер приемного регистра, сдвигатель, первый и второй коммутаторы, первый, второй и третий триггеры регистра аргумента и блок управления, причем в каждом i-м канале нулевой и единичные выходы триггера управляющего регистра Соединены соответственно с первым и вторым входами элемента 2И-ИПИ, Третий вход которого соединен с выходом элемента 2И-ШШ, (i-D-ro канала, четвертый вход элемента 2ИШШ соединен с первыми информацион1&1ми входами первого и второго коммутаторов и с выходом переноса сдвигателя, первый и второй управляющие входы триггера управляющего регистра соединены соответственно с первым и третьим выходами блока управления, пятый выход которого сЬединен. в управляющими входами первого и второго коммутаторов и сдвигателя, управляюпрШ вход сдвигом которого соединен с восьмым выходом блока управления, девятый выход которого соединен с входом выбора адреса блока хранения констант выход которого соединен с вторым информационным входом первого коммутатора, третий информационный вход которого соединен с информационным входом триггера управляющего регистра и выходом второго коммутатора, информационные входы которого соединены с единичными выходами первого, второго и третьего триггеров регистра аргумен(Л та и группой информационных входов сдвигателя, первый вход элементов 2И-ШШ соединен с первыми управляющими входами первого, второго и третьего триггеров регистра аргумента, вторые управляю1ще входы которых соединены с вторым входом элемента 2И-ШШ, KD и группой информационных входов сдви4 гателя, первый выход блока управлеto ния соединен с управляющими входами СО NP триггера приемного регистра, информационный вход которого соединен с выходом первого коммутатора,.отличающееся тем, что, с целью повыщения быстродействия и расширения функциональных возможностей за счет вычисления пространственных координат, устройство содержит блок формирова1шя знака операции, четвертый триггерный регистр аргумента и с второго по пятый поразарядные элементы 2И-ИЛИ, причем в i-м канале выходы второго, третьего, четвертого и пятого элементов 2И-ИЛИ

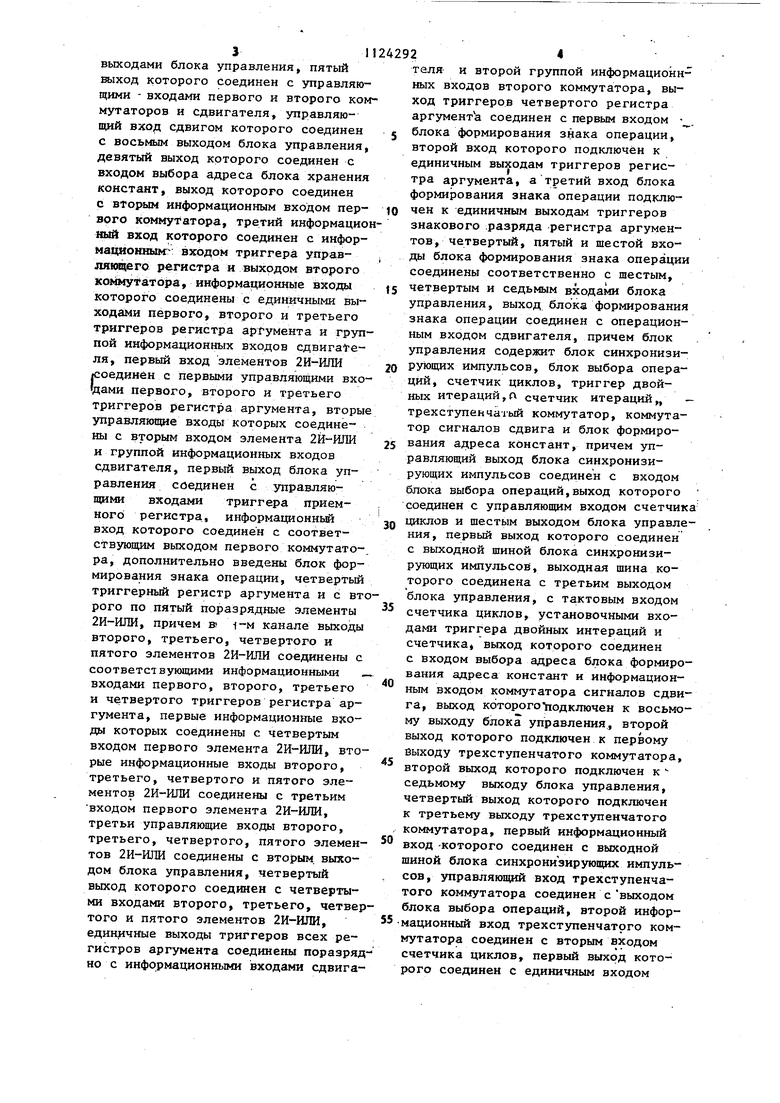

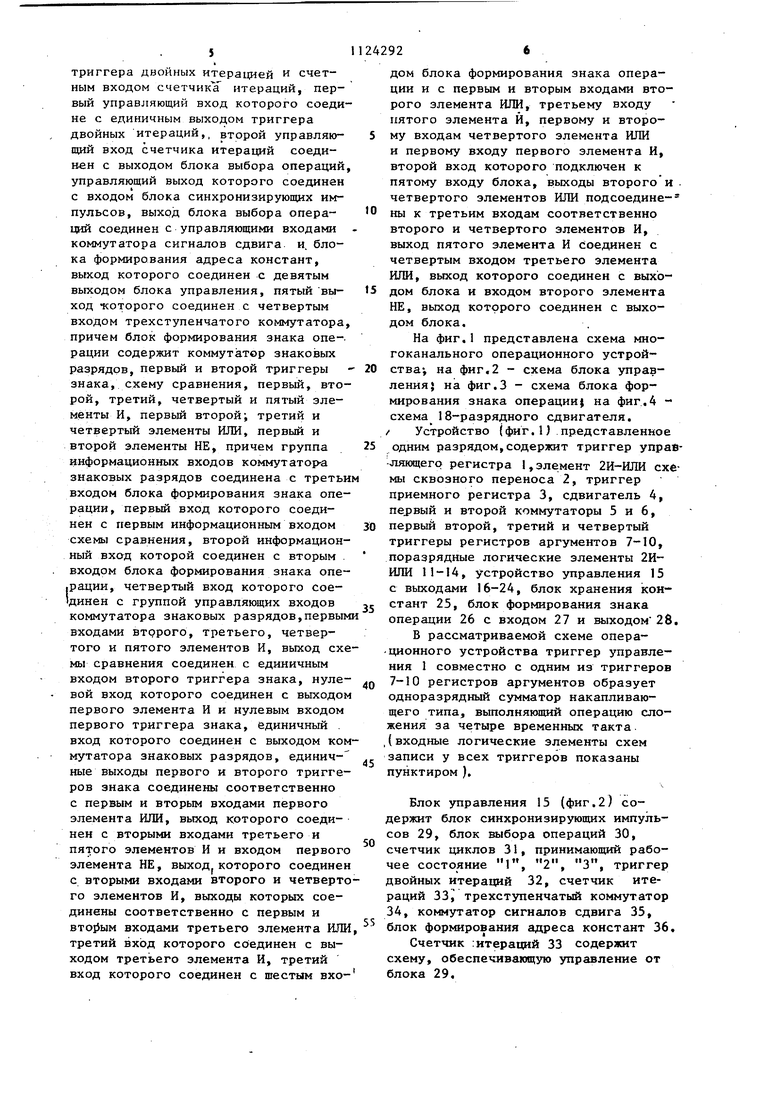

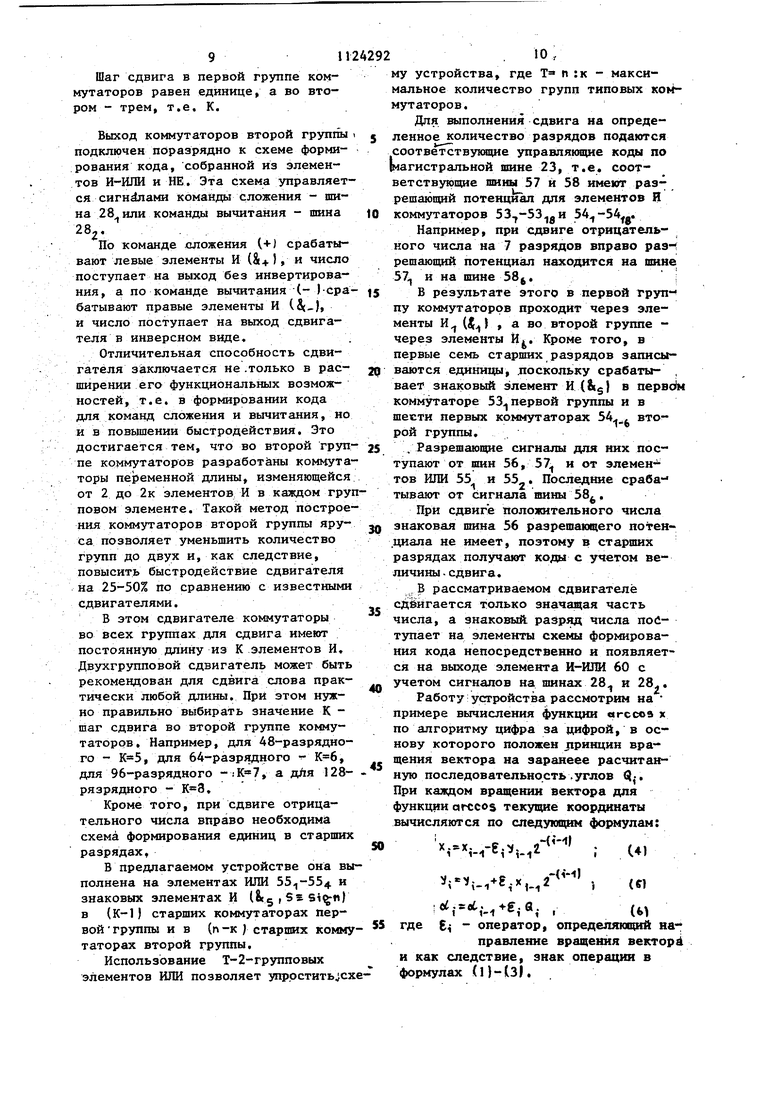

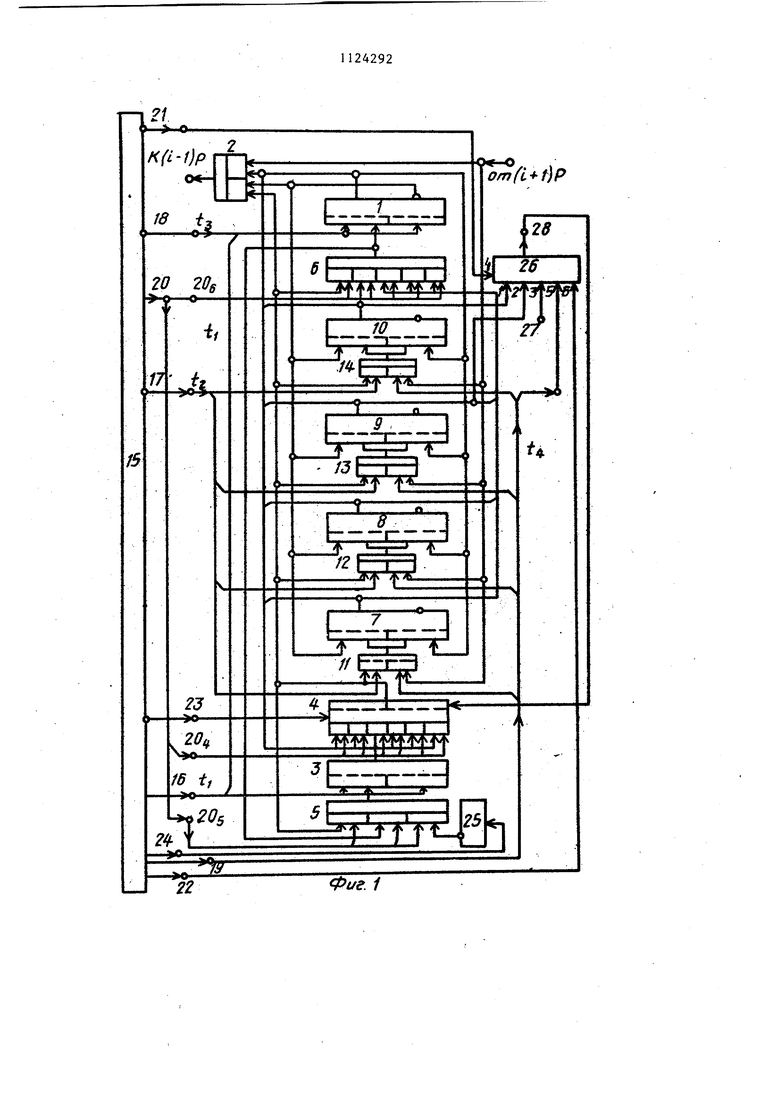

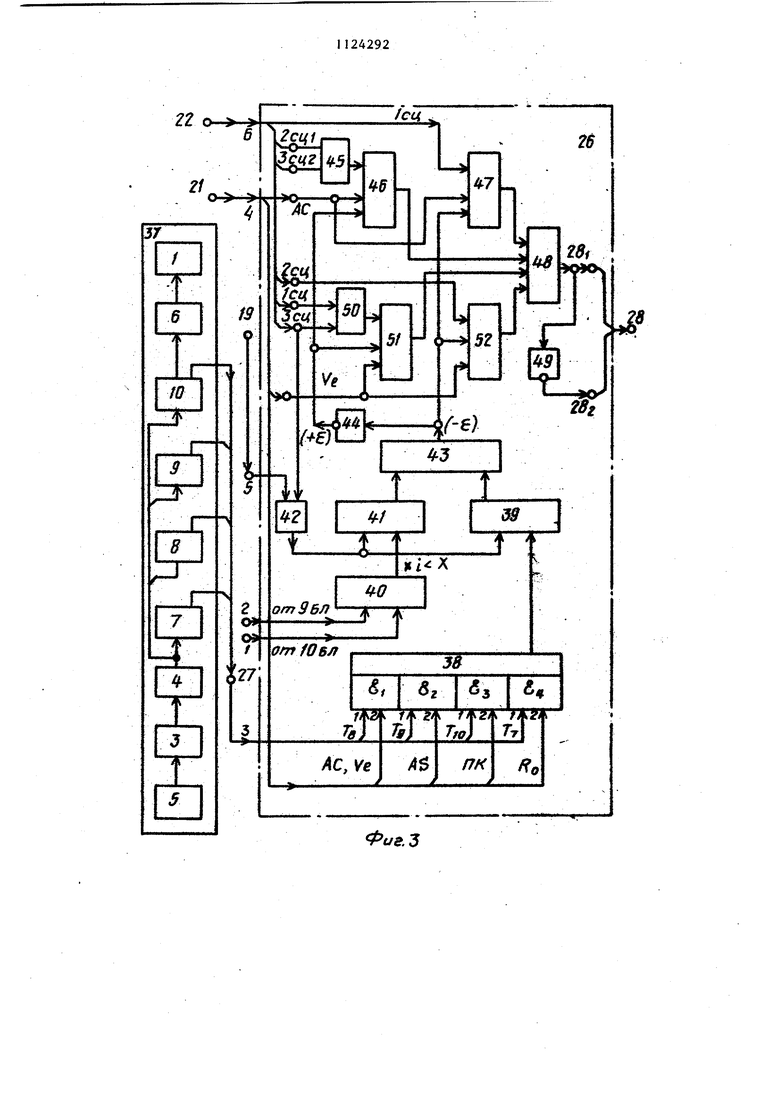

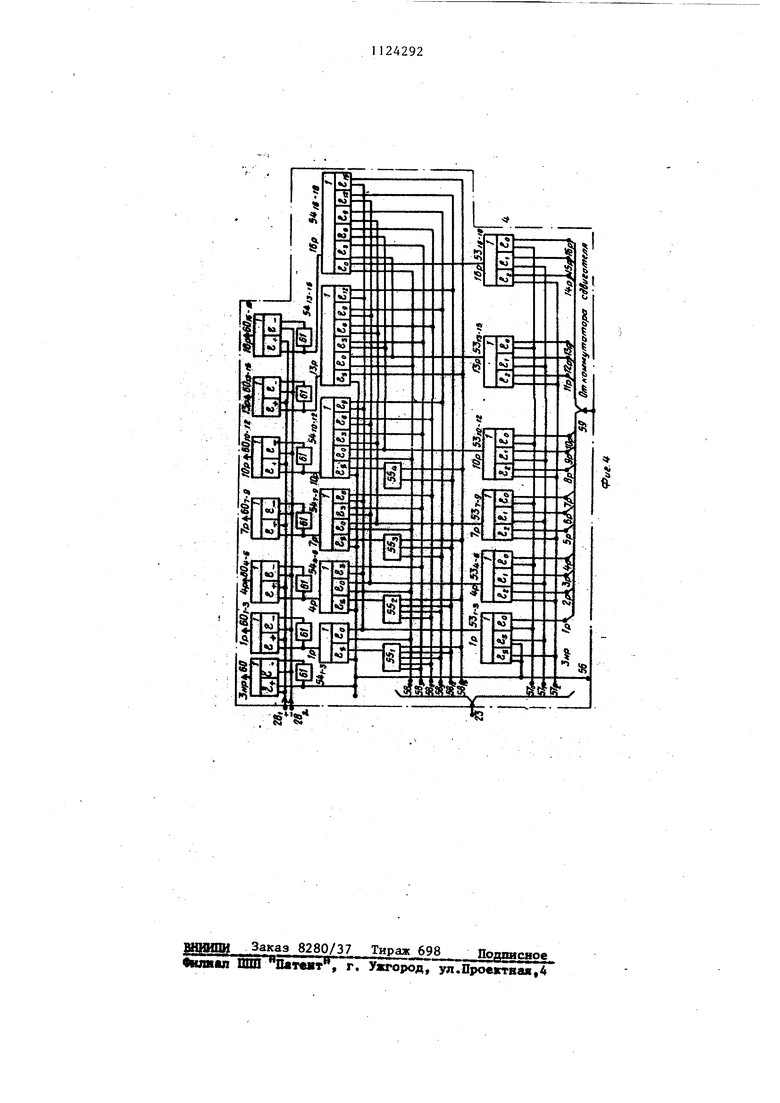

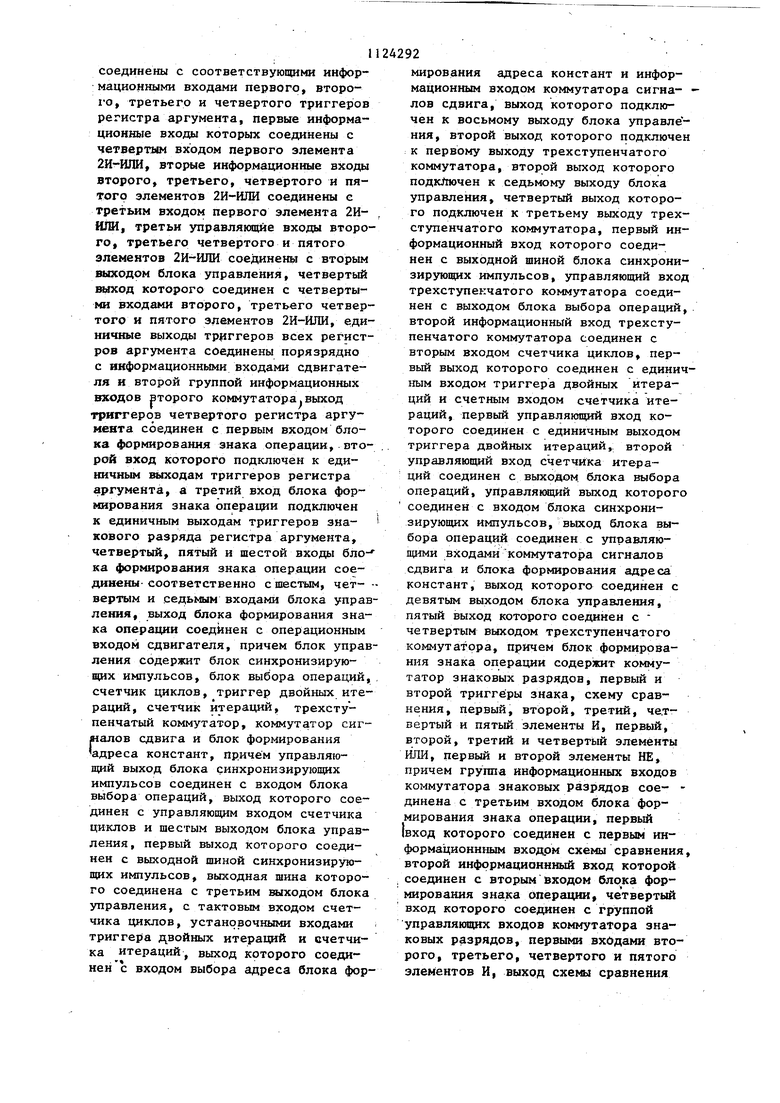

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе цифровой вычислительной машины. Известно вычислительное устройство с несколькими сумматорами последовательного действия, позволяющее аппаратурным способом вычислять сложные элементарные функции типа arc cos СО-Недостатком такого устройства является его низкая .производительность. Наиболее близким к изобретению по технической сущности является многоканальное операционное устройство, которое обладает повьшенной производительностью, например функция типа «rccoS вычисляется этим /устройством за время вьтолнения 8 комаид умножения 2. .ft Однако дальнейшее повьшение быстродействия на 25% может быть по лучено, если совместить во времени формирование знака операции для iинтерации с вычислительной процедурой (1-1)-й интерации. Кроме того, известное устройств обладает ограниченными возможностя например не позволяет непосредстве но вычислить пространственные координаты вектора. Цель изобретения - повышение быстродействия и расширение функциональных возможностей многоканального операционного устройства. Поставленная цель достигается тем, что многоканальное операционное устройство, содержащее блок хранения констант, п каналов, где празрядность устройства причем i-и канал, ( 1,2,...,п) содержит триггер управляющего регистра, элемент 2И-ИЛИ, триггер приемного регистра, сдвигатель, первый и второй коммутаторы, первый второй и третий триггеры регистра .аргументами блок управления, причем в каждом i-м канале нулевой и един ичные выходы триг- гера управляющнго регистра соединены соответственно с первым и вторым входами элемента 2И-ИЛИ, третий вход которого соединен с выходом элемента 2И-Ш1И {t-l)-ro канала, четвертый вход элемента 2И-ШШ соединен с первыми информационными входами первого и второго ко№4утаторов и с выходом переноса сдвигателя, первый и второй управляющие входы триггера управляющего регистра соединены соответственно с первым и третьим . выходами блока управления, пятый вь:ход которого соединен с управляющими - входами первого и второго ком мутаторов и сдвигателя, управляющий вход сдвигом которого соединен с восьмым выходом блока управления, девятый выход которого соединен с входом выбора адреса блока хранения констант, выход которого соединен с вторым информационным входом первого коммутатора, третий информацио ный вход которого соединен с информациокш11М : входом триггера управлякщего регистра и выходом второго ко Ь у атора, информационные входы которого соединены с единичными выходами первого, второго и третьего триггеров регистра apfyMeHTa и груп пой информационных входов сдвигателя, первый вход элементов 2И-ИЛИ соединен с первыми управляющими вхо дами первого, второго и третьего триггеров регистра аргумента, вторы управляющие входы которых соединены с вторым входом элемента 2Й-ИЛИ и группой информационных входов сдвигателя, первый выход блока управления соединен с управляющими входами триггера приемного регистра, информационный вход которого соединен с соответствующим выходом первого коммутатора, дополнительно введены блок формирования знака операции, четвертый триггерный регистр аргумента и с вт рого по пятый поразрядные элементы 2И-Ш1И, причем в 1-м канале выходы второго, третьего, четвертого и пятого элементов 2И-Ш1И соединены с соответствукмцими информационными входами первого, второго, третьего и четвертого триггеров регистра аргумента, первые информационные входы которых соединены с четвертым входом первого элемента 2И-ИЖ, вто рые информационные входы второго, третьего, четвертого и пятого элементов 2И-Ш1И соединены с третьим входом первого элемента 2И-ИЛИ, третьи управляющие входы второго, третьего, четвертого, пятого элемен тов 2И-ШШ соединены с вторым, выходом блока управления, четвертый выход которого соединен с четвертыми входами второго, третьего, четве того и пятого элементов 2И-ИЛИ, един 1чкые выходы триггеров всех регистров аргумента соединены поразря но с информационными входами сдвига 1 2 теля и второй группой информационнных входов второго коммутатора, выход триггеров четвертого регистра аргумента соединен с первым входом блока формирования знака операции, второй вход которого подключён к единичным выходам триггеров регистра аргумента, а третий вход блока формирования знака операции подключен к единичным выходам триггеров знакового .разряда регистра аргументов, четвертый, пятый и шестой входы блока формирования знака операции соединены соответственно с шестым, четвертым и седьмым входами блока управления, выход блока формирования знака операции соединен с операционным входом сдвигателя, причем блок управления содержит блок синхронизиРУЮЩИХ импульсов, блок выбора операций, счетчик циклов, триггер двойных итераций,fi счетчик итераций,, трехступенчатый коммутатор, коммутатор сигналов сдвига и блок формирования адреса констант, причем управляющий выход блока синхронизирующих импульсов соединен с входом блока выбора операций,выход которого соединен с управляющим входом счетчика циклов и шестым выходом блока управления, первый выход которого соединен с выходной шиной блока синхронизирующих импульсоб, выходная щина которого соединена с третьим выходом блока управления, с тактовым входом счетчика циклов, установочными входами триггера двойных интераций и счетчика, выход которого соединен с входом выбора адреса блока формирования адреса констант и информационным входом коммутатора сигналов сдвига, выход которогоТподключей к восьмому выходу блока управления, второй выход которого подключен к первому выходу трехступенчатого коммутатора, второй выход которого подключен к седьмому выходу блока управления, четвертый выход которого подключен к третьему выходу трехступенчатого коммутатора, первый информационный вход -которого соединен с выходной щиной блока синхронизирующих импульсов, управляющий вход трехступенчатого коммутатора соединен с выходом блока выбора операций, второй инфор-мационный вход трехступенчатого коммутатора соединен с вторым входом счетчика циклов, первый выхрд которого соединен с единичным входом триггера двойных итерацией и счетным входом счетчика итераций, первый управляющий вход которого соеди не с единичным выходом триггера двойных итераций,, второй управляющий вход счетчика итераций соединен с выходом блока выбора операций управляющий выход которого соединен с входом блока синхронизирующих импульсов, выход блока выбора операций соединен с управляющими входами коммутатора сигналов сдвига и. блока формирования адреса констант, выход которого соединен с девятым выходом блока управления, пятый выход -которого соединен с четвертым входом трехступенчатого коммутатора причем блок формирования знака oneрации содержит коммутатор знаковых разрядов, первый и второй триггеры знака, схему сравнения, первый, вто рой, третий, четвертый и пятый элементы И, первый второй; третий и четвертый элементы ИЛИ, первый и второй элементы НЕ, причем группа информационных входов коммутатора знаковых разрядов соединена с треть входом блока формирования знака опе рации, первый вход которого соединен с первым информационным входом схемы сравнения, второй информацион ный вхед которой соединен с вторым входом блока формирования знака опе .рации, четвертый вход которого соединен с группой управляющих входов коммутатора знаковых разрядов,первы входами втррого, третьего, четвертого и пятого элементов И, выход сх мы сравнения соединен с единичным входом второго триггера знака, нуле вой вход которого соединен с выходо первого элемента И и нулевым входом первого триггера знака, единичный . вход которого соединен с выходом ко мутатора знаковых разрядов, единичные выходы первого и второго тригге ров знака соединены соответственно с первым и вторым входами первого элемента ИЖ, выход которого соединен с вторыми входами третьего и пятого элементов И и входом первог элемента НЕ, выход которого соедине с вторыми входами второго и четверт го элементов И, выходы которых соединены соответственно с первым и вто15ым входами третьего элемента ИЛ третий вход которого соединен с выходом третьего элемента И, третий вход которого соединен с шестым вхо дом блока формирования знака операции и с первым и вторым входами второго элемента ИЛИ, третьему входу пятого элемента И, первому и второму входам четвертого элемента ИЛИ и первому входу первого элемента И, второй вход которого подключен к пятому входу блока, выходы второго и . четвертого элементов Ptfttl подсоедине- ны к третьим входам соответственно второго и четвертого элементов И, выход пятого элемента И соединен с четвертым входом третьего элемента ИЛИ, выход которого соединен с выходом блока и входом второго элемента НЕ, выход которого соединен с выходом блока. На фиг.1 представлена схема многоканального операционного устрой- ства-, на фиг.2 - схема блока управления} на фиг.З - схема блока формирования знака операции} на фиг.4 схема 18-разрядного сдвигателя. Устройство (фиг. П представленное одним разрядом,содержит триггер управ-ляющего регистра I,элемент 2И-Ш1И схемы сквозного переноса 2, триггер приемного регистра 3, сдвигатель 4, первый и второй коммутаторы 5 и 6, первый второй, третий и четвертый триггеры регистров аргументов 7-10, поразрядные логические элементы 2ИИПИ 11-14, устройство управления 15 с выходами 16-24, блок хранения констант 25, блок формирования знака операции 26 с входом 27 и выходом 28. В рассматриваемой схеме операционного устройства триггер управления 1 совместно с одним из триггеров 7-10 регистров аргументов образует одноразрядный сумматор накапливающего типа, выполняющий операцию сложения за четыре временных такта (входные логические элементы схем записи у всех триггеров показаны пунктиром ), Блок управления 15 (фиг.2) содержит блок синхронизирующих импульсов 29, блок выбора операций 30, счетчик циклов 31, принимающий рабочее состояние 1, 2, 3, триггер двойных итераций 32, счетчик итераций 33, трехступенчатый коммутатор 34, коммутатор сигналов сдвига 35, блок формирования адреса констант 36. Счетчик :итераций 33 содержит схему, обеспечивающую управление от блока 29. Коммутатор 34 представляет собой трехступенчатый дешифратор, в котором первая cTjrneHb распшфровывает состояние счетчика циклов 31 и йыдаат сигнал на вшну 22 для управления блоком 26. Вторая ступень дешифратора распшфровывает состояние блока 30 и выдает управляющий сигнал на шину. 20. Третья ступень с учетом сигналов по всем входам выдает сигналы тактовых импульсов t- н t4 на шины 17 к 19. V Шина 21 нспользуется для управления блоком 26 от блока 30. Блок формирования знака операции 26 (фиг.3) показан в развернутом виде его связи по шине знаковых разрядов 27, с триггерами знакового разряда 37 регистров аргументов содержит коммутатор знаковых разрядов 38,первый триггер знака 39,схему сравнения 40,второй триггер знака 41.элементы , 42, элемент ШШ 43, элементы НЕ 44, выходную шину 28. : .:. - ,-. - Знаковый разряд 37 имеет структуру и .соединения, аналогичные фиг.1, поэтому на фиг.З он показан в упрощенном виде. Триггеры Т7- Т одноименшлх регистров 7-10 управляют пер выми входами коммутатора 38 блока 26. На вторые входы элементов И и коммутатора 38 поступают Управлякицие сигналы по шине 21 от блока 30 по входу блока 26 при выполнении соответствующих операций. В качестве примера на фиг.3 показаны управляющие сигналы при выполнении следующих операций: йгссоз -AC,e t-cSih -AS, пространственные координаты -ПК, полярные координаты - Vg, прямоуголь ные координаты - KQ. Через коммутатор 38 в первый триггер знака 39 записывается код 1 или из соот вествующего триггера 7-10 знакового разряда 37 операционного устройтсва с целью формирования оператора (±). Знаковый оператор зависит от собт ношения чисел х - X , поэтому для их сравнения предусмотрена схема сравнения 40, результат которой записывается во второй триггер знака 41, причем запись осуществляется под управлением элемента И 42 по завершению каждого третьего цикла обра ботки информации, поэтому элемент И 42 згаравляется третьим состоянием счетчика циклов 3 через коммутатор 34. Элементами ИЛИ - 43 и инвертором 44 формируются сигналы соответственно .(-) и (+6) . В качестве примера показан вариант формнрования сигналов для команды сложения (+ и вычитания (-) при выполнении операций АС и Vg. Для формирования знака в операции С1ГСС09 используются приведенные формулы(4)-(6), а для операции Tg формулы имеют следующий вид: ..... („ (2) . : (Я Е 51§-п :f,.. ii . . . Для операции «ГСcos -АС используются злементы ИЛИ 45, И 46, И 47, ИЛИ 48, НЕ 49, а для операции полярные координаты вектора-Vg используются злементы ИЛИ 50, И 51, И 52, ИЛИ 48, НЕ 49. На выходе элементаППИ 48 на шине 28 получается сигнал команды сложения ( + )., а на шине 282получается сигнал команды вычитания С -). Эти сигналы магистрально по шИне 28 поступают на операционный вход сдвигателя 4. Наиболее оптимальный вариант выполнения сдвигателя 4 представлен в виде схемы 18-разрядного сдвигателя (в целях упрощения сдвигатель показан без входного коммутатор, схема которого имеет Ьид типа коммутатора 38 в блоке 26.). Сдвигатель 4 содержит первую и вторую группы из логических коммутаторов 53 и 54, группу логических элементов ИЛИ 55, знаковую шину числа 56, шины сдвига вправо в первой группе коммутаторов 57, 57, 57, , предназначенмле соответственно для сдвига на 0,1,2 разряда, шины сдвиги вправо во второй группе коммутаторов яруса 58о, 58, 58,, 585, 58 и 58irt выполняющие сдвиг соответствен но на 0,3,6,9,12 и 15 разрядов, коммутаторы первой группы информационными входами соединены с соответствзяощими разрядными шинами входного слова 59 . Схема формирования кода состоит из элемента 2И-ШШ 60 и элемента НЕ 61. На чертеже показаны коммутаторы и соединения для 1,4,7, 10,13,16 разрядов, причем эти коммуаторы являются типовыми для группы разрядов, указанной нидексом. Шаг сдвига в первой группе коммутаторов равен единице, а во втором - трем, т.е. К. Выход коммутаторов второй групгш подключен поразрядно к схеме формирования кода, собранной из элементов И-ИЛИ и НЕ. Эта схема управляет ся сигналами комайды сложения - шина 28 или команды вычитания - шина По команде хшожения (+) срабатывают левые элементы И (&+ ), и число поступает на выход без инвертирования, а по команде вычитания (-) ера батывают правые элементы И (3), и число поступает на выход сдвига- теля в инверсном виде. Отличительная способность сдвигатёля заключается не .только в рас ширении его функциональных возможностей, т.е. в формировании кода для команд сложения и вычитания, но и в повьшении быстродействия. Это достигается тем, что во второй груп пе коммутаторов разработаны коммута торы переменной длины, изменяющейся от 2 до 2к элементов И в каждом гру повом элементе. Такой метод построе ния коммутаторов второй группы яруса позволяет уменьшить количество групп до двух и, как следствие, повысить быстродействие сдвигателя на 25-50% по сравнению с известными сдвигателями. В этом сдвигателе коммутаторы во всех группах для сдвига имеют постоянную длину из К элементов И. Двухгрупповой сдвигатель может быть рекомендован для сдвига слова практически любой длины. При этом нужно правильно выбирать значение К шаг сдвига во второй группе коммутаторов. Например, для 48-разрядного - , для 64-разрядного - , для 96-разрядного , а для 128рязрядного - . Кроме того, при сдвиге отрицательного числа вправо необходима схема формирования единиц в старших разрядах, В предлагаемом устройстве она вы полнена на элементах ИЛИ и знаковых элементах И (Ei , Ss ) в (K-l) старших коммутаторах первой группы ив (п -к ; старших комму таторах второй группы. Использование Т-2-групповых элементов ИЛИ позволяет упррстить сх му устройства, где п :к - максимальное количество групп типовых коммутаторов. Для выполнения сдвига на определенное количество разрядов подаются соответствующие управляющие коды по (магистральной шине 23, т.е. соответствующие шины 57 и 58 имеют разрешающий потенциал для элементов Я коммутаторов и . Например, при сдвиге отрицательного числа на 7 разрядов вправо разрешающий потенциал находится на шине 57, и на шине 58(. ; В результате этого в первой труппу коммутаторов проходит через элементы И ( , а во второй группе через элементы Й. Кроме того, в первые семь старших разрядов записываются единицы, .поскольку срабаты- , вает знаковый элемент И (Sig) в первс1м коммутаторе 53., первой группы ив шести первых коммутаторах 54.., второй группы. .Разрешающие сигналы для них поступают от шин 56, 57 и от элементов ИЛИ 55 и 552. срабатывают от сигнала шины 58. При сдвиге положительного числа знаковая шина 56 разрешающего потен.циала не имеет, поэтому в старших разрядах получают коды с учетом величины - сдвига. В рассматриваемом сдвигателе сдвигается только значащая часть числа, а знаковый: разряд числа пойтупает на элементы схемы форьшрования кода непосредственно и появляется на выходе элемента И-ШШ 60 с учетом сигналов на шинах 28., и 28.. Работу усггройства рассмотрим на примере вычисления функции «гссоа х по алгоритму цифра за цифрой, в основу которого положен принцин вращения вектора на заранеее расчитанную последовательность ,углов Q,-. При каждом вращении вектора для функции arccos текущие координаты вычисляются по следующим формулам: -.-,-,.,2 .,-e,x,.,2 ,-«, f, - оператор, опредеяяю1ций направление вращения вектор к как следствие, знак операции в формулах (1)-13|.

, если x.x V .,0 , иначе f - +1.

Перед началом работы исходные коо динаты вектора (XQ 0; УрИ/к ; oi F/2) записываются соответственно в 9,8 и 7 регистры аргументов, а в чет вертый регистр 10 записывается управляющий параметр -аргумент X, что и позволяет сформировать значение f

С целью повьшения быстродействия, реализацию алгоритма целесообразно начинать с вычитания Х. что позврляет блоку формирования знака операции 26 за время выполнения (1 -U итерации сформировать оператор g. для с-й итерации.

Каждая координата вектора, вычисленная по формулам (4 )-(6), реализуется за четыре тактовых импульса в соответствии с принципом работы накапливающего сумматора. Например, первым тактовым импульсом t, Xj. из регистра 9 через коммутаторы 6 и 5 переписывается в регистры 1 и 3, Вторым импульсом t происходит сложение по. модулю два чисел ,Xi-i и Vi-1 2- . Третьим импульсом i, содержимое регистра 9 переписывается в регистр 1 через коммутатор 6 под управлением сигнала по шине 20, после чего начинает распространяться сигнал сквозного переноса через логические элементы 2 в сторону старших разрядов. Четвертым импульсом i4 регистре 9 формируется окончательная сумма с учетом сигнала переноса из младшего разряда .

Вычисленное значение X,- из регистра 9 поступает на блок 26 для формированиято время как текущая:итерация; продолжает выполняться аналогично описанному по формулам (5 ) и (6).

Управляющие сигналы,, необходимые для выполнения каждой итерации, вырабатываются блоком управления 15.

Счетчик итерации 33 формирует необходимое количество итерации дпя вычисления функции а для вьтолнения С-и итерации предусмотрен триггер двойных итераций 32. Учитывая, что в каждой итерации необходимо произвести последовательно вычисления по трем формулам (4)-(б1, счётчик циклов 31 формирует первое

состояние (1СЦ| для вычисления координаты К( , второе состояние (2СЦ/ для координаты у,- , а третье состояние (ЗСЦ } - для угловой координаты aL , Перечисленные состояния счетчика циклов 31 через коммутатор 34 по входу 6 используются блоком 26 для выработки знака операции.

Тактовые импульсы i и

i- поступают в операционные устройства непосредственно от блока синхронизирующих импульсов 29, а импульсы t и t поступают через коммутатор 34, управляемый счетчикам циклов 31 и блоком операций 30.

В коммутаторе 34 выходы 2 и 3

tj и

для импульсов

являются ма(Гистральными, т.е. эти импульсы используются для управления соответствующим регистром 7-10, а на четвертом выходе формируются потенциальные управляющие сигналы, которые по магистральной шине 20 поступают на коммутаторы,.блоков 4,5,6 для коммутации соответствукяцих входов (фиг .2)

Каждое состояние счетчика : итераций 33 используется для выработки сигналов сдвига на шине 23 и для формирования адреса константы Q,- на шине 24 для блока 25.

После выполнения п двойных ите раций в регистре 9 имеем

;( 0050

в регистре 8

в регистре

cL 0(ГСС05 X

Предлагаемое устройство позволяет уменьшить время вычисления фунции типаагссобна время выполнения двух команд умножения.

Кроме того, устройство обладает расширенными функциональными возможностями, например оно позволяет аппаратурным способом вычислить пространственные координаты вектора. Дпя зтрго необходимо в четвертый регистр 10 записать третью линейную координату вектора Z , а в регистры 9,8,7 соответственно-Х,У и О,

Применяя дважды известную операцию вычисления полярных координат вектора, в ответе получаем

х..

oi drct - tarctgФиё. г

to

JP

fff

отВВЛ

ат/Овл

3

АС, Уе А$

Jj Ж

Ж

§Г 5;

л

.

7/Г

ггт/

Фиг.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления обратного кругового синуса | 1973 |

|

SU478313A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное операционное устройство | 1975 |

|

SU618740A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1982-07-21—Подача