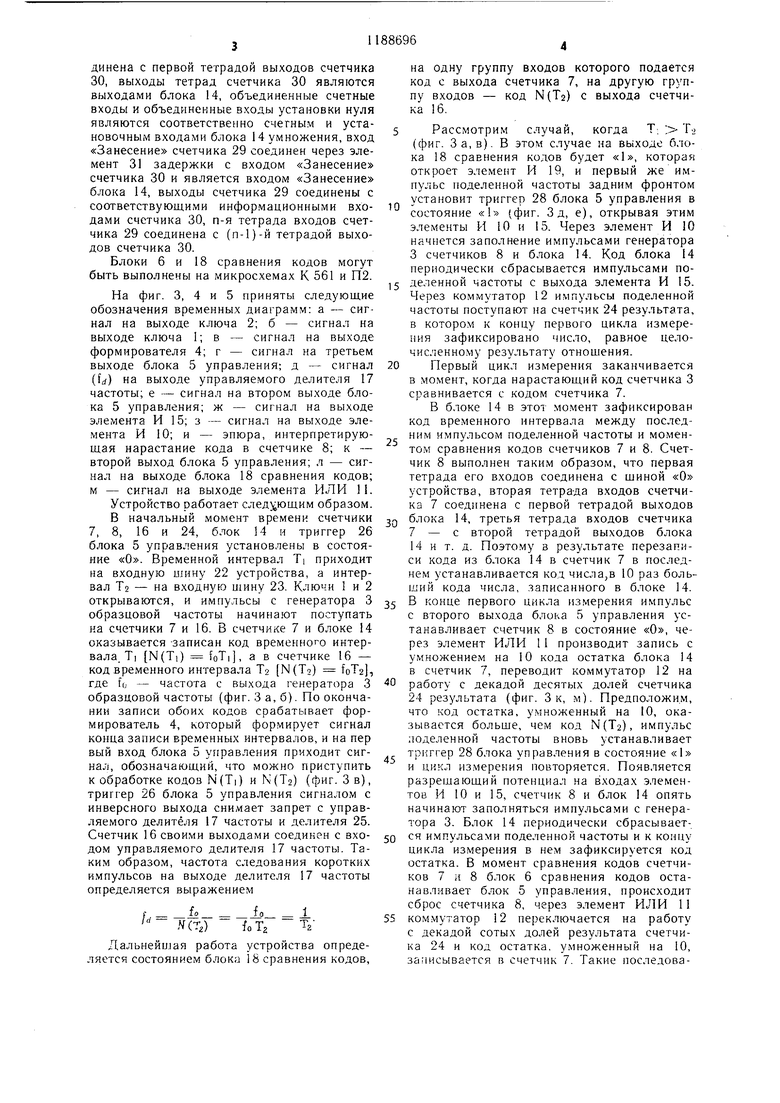

2. Измеритель по п. 1, отличающийся тем, что блок умножения содержит два счетчика и элемент задержки, причем первая тетрада входов первого счетчика соединена с шиной логического нуля измерителя, вторая тетрада входов первого счетчика соединена с первой тетрадой выходов второго счетчика, «-Я тетрада входов первого счетчика соединена с (п-1)-й тетрадой выходов второго счетчика, выходы тетрад второго счетчика являются выходами блока умножения, объединенные счетные входы первого и второго счетчиков являются счетным входом блока умножения, объединенные входы установки нуля первого и второго счетчиков являются входом установки нуля блока умножения, вход «Занесение первого счетчика, соединенный через дополнительный элемент задержки с входом «Занесение второго счетчика, является входом «Занесение блока умножения, выходы первого дополнительного счетчика соединены с соответствующими информационными входами второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель отношения временных интервалов | 1984 |

|

SU1226399A1 |

| Устройство для измерения средней длительности временных интервалов | 1987 |

|

SU1506433A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Цифровой измеритель отношения временных интервалов | 1986 |

|

SU1390595A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Цифровой измеритель отношения временных интервалов | 1981 |

|

SU983644A1 |

| Устройство для умножения частоты | 1991 |

|

SU1829111A1 |

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

| Умножитель частоты | 1979 |

|

SU834697A1 |

| Кодек для передачи информации с помощью имитостойких последовательностей сигналов сложной формы | 1987 |

|

SU1451719A1 |

1. ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ОТНОШЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ, содержащий два ключа, первый блоксравнения кодов, блок управления, формирователь импульсов, управляемый делитель частоты, коммутатор, три счетчика, счетчик результата, первый элемент ИЛИ, два элемента И и генератор образцовой частоты, выход которого соединен с первыми входами первого и второго ключей, входом управляемого делителя частоты и первым входом первого элемента И, другие входы первого и второго ключей соединены соответственно с первой и второй входными шинами измерителя, выход первого ключа соединен с входом первого счетчика и первым входом формирователя импульсов, второй вход которого соединен с выходом второго ключа и входом второго счетчика, выход формирователя импульсов соединен с первым входом блока управления, второй вход которого соединен с выходом блока сравнения кодов, первый выход.блока управления соединен с вторым входом первого элемента И и с первым входом второго элемента И, второй вход которого соединен с выходом управляемого делителя частоты, а выход соединен с входом коммутатора, выходы которого соединены с входами счетчика результата, выход первого элемента И соединен с одним входом третьего счетчика, другой вход которого соединен с вторым выходом блока управления, группа выходов третьего счетчика соединена с первой группой входов блока сравнения кодов, вторая группа входов которого соединена с группой выходов первого счетчика, группа выходов второго счетчика соединена с информационными входами управляемого делителя частоты, отличающийся тем, что, с целью повышения быстродействия измерителя, в него введены второй элемент ИЛИ, третий и четвертый элементы И, элемент НЕ, делитель частоты с постоянным коэффициентом деления, блок умножения, элемент задержки и второй б/юк сравнения кодов, первая группа входов которого соединена с группой выходов первого счетчика, вторая группа входов соединена с группой выходов второго счетчика, а выход подключен непосредственно к первому входу третьего и через элеме; т НЕ к первому о входу четвертого элементов И, выход последнего из которых соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с вторым выходом блока управления, а выход - с управляютцим входом коммутатора, входом «Занесенне первого счетчика и через элемент задержки - с входом «Занесение блока умножения, и вход установки нуля которого соедине ; с выходом второго элемента И. первый и вто00 рой входы второго элемента ИЛИ соедиоо непы соответственно с выходом первого клю05 ча н выходом первого элемента И. С-вход делителя частоты с постоянным коэффициентом деления соединен с выходо.м генераО5 тора образцовой частоты, -вхол объединен с входом установки нуля управляемого делителя частоты и соединен с третьим выходом блока управления, выход делителя частоты с постоянным коэфцЬициентом деления соединен с вторым входом четвертого элемента И, второй вход третьего э,1емента П с выходом управляемого делителя частоты, а его выход - с тре-.ъим входом блока управления, выход второго элемента ИЛИ подключен к счетному входу блока умножения, выходы которого соединены с группоГ; входов первого счетчика.

Изобретение относится к цифровой измерительной технике и может быть использовано как в качестве автономного прибора, так и в качестве устройства, используемого в информационно-измерительном комплексе.

Цель изобретения - повышение быстродействия измерителя за счет сокращения времени умножения кода делимого до одного цикла измерения.

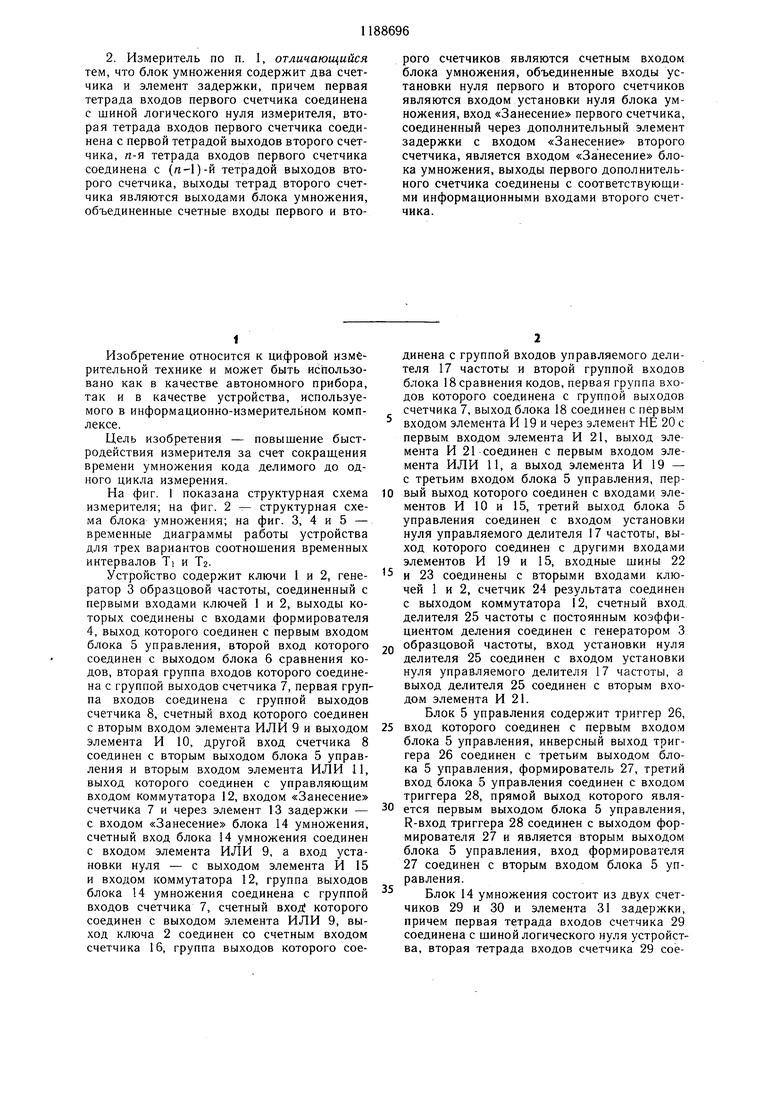

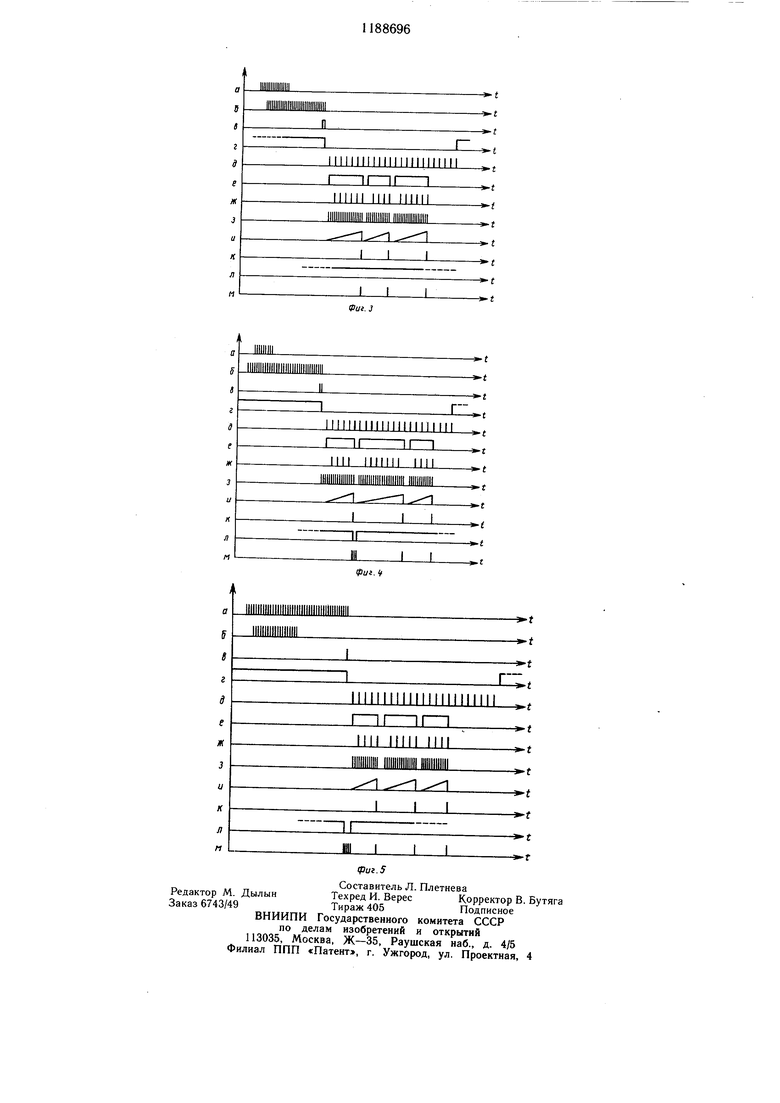

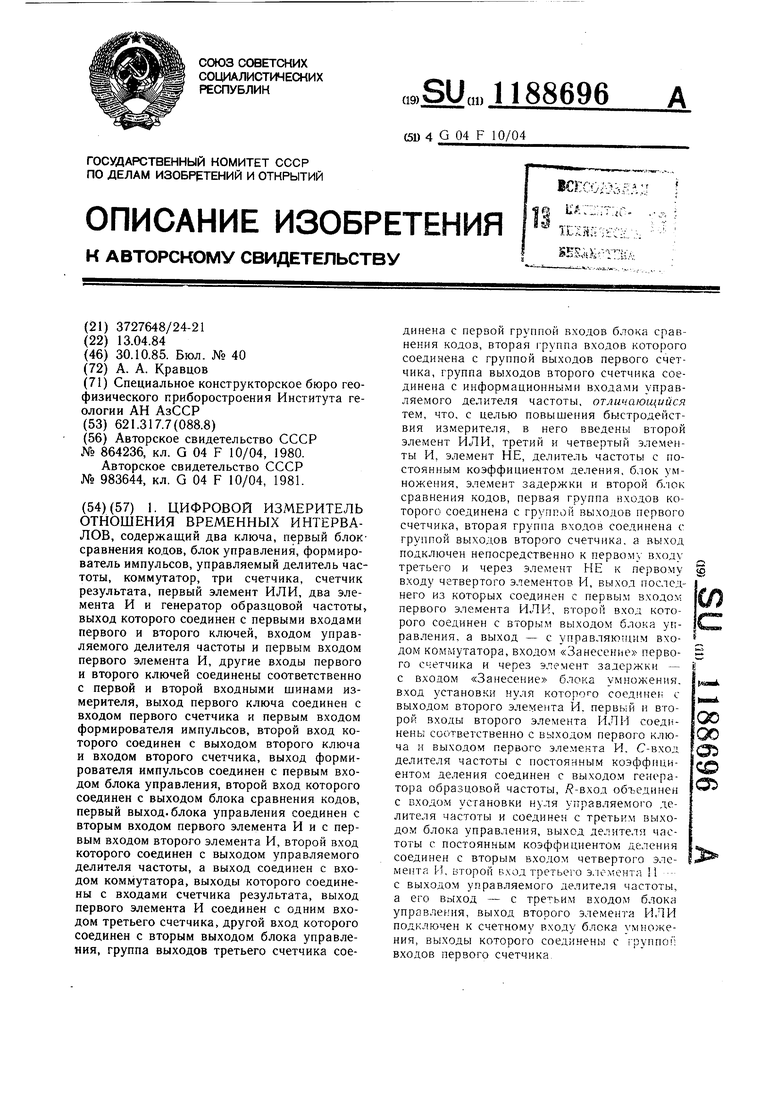

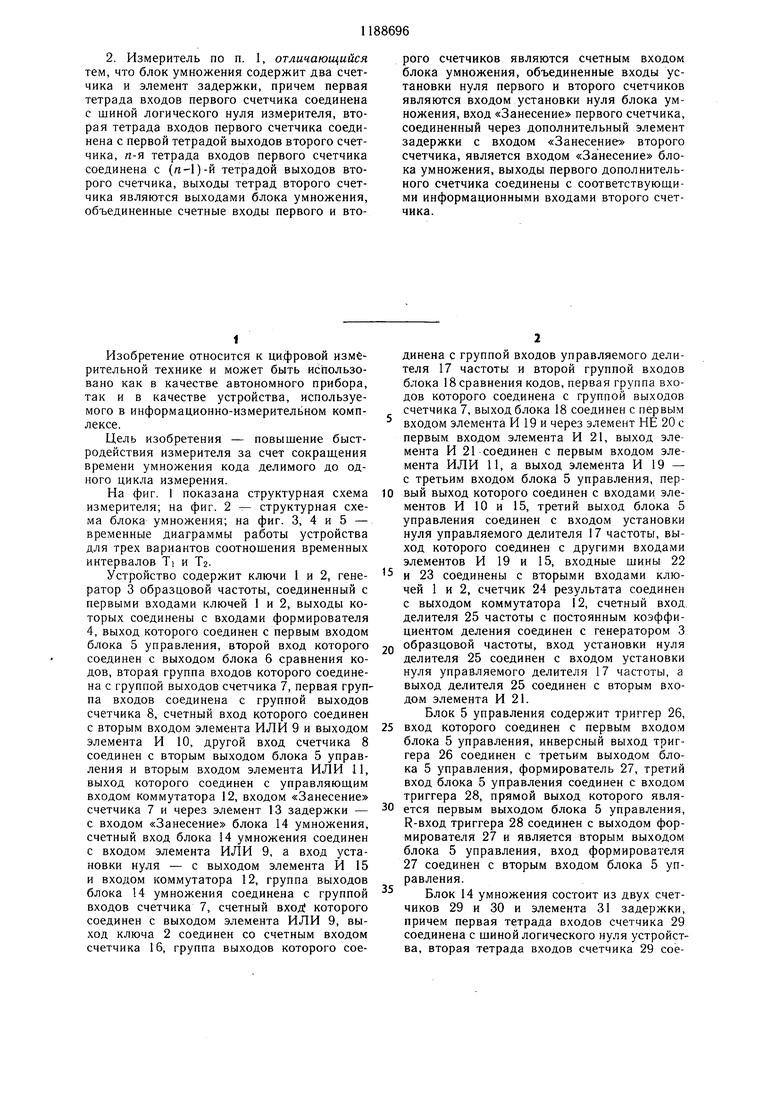

На фиг. 1 показана структурная схема измерителя; на фиг. 2 - структурная схема блока умножения; на фиг. 3, 4 и 5 - временные диаграммы работы устройства для трех вариантов соотношения временных интервалов Ti и Т2.

Устройство содержит ключи i и 2, генератор 3 образцовой частоты, соединенный с первыми входами ключей 1 и 2, выходы которых соединены с входами формирователя 4, выход которого соединен с первым входом блока 5 управления, второй вход которого соединен с выходом блока 6 сравнения кодов, вторая группа в.чодов которого соединена с группой выходов счетчика 7, первая группа входов соединена с группой выходов счетчика 8, счетный вход которого соединен с вторым входом элемента ИЛИ 9 и выходом элемента И 10, другой вход счетчика 8 соединен с вторым выходом блока 5 управления и вторым входом элемента ИЛИ 11, выход которого соединен с управляющим входом коммутатора 12, входом «Занесение счетчика 7 и через элемент 13 задержки - с входом «Занесение блока 14 умножения, счетный вход блока 14 умножения соединен с входом элемента ИЛИ 9, а вход установки нуля -- с выходом элемента И 15 и входом коммутатора 12, группа выходов блока 14 умножения соединена с группой входов счетчика 7, счетный вход которого соединен с выходом элемента ИЛИ 9, выход ключа 2 соединен со счетным входом счетчика 16, группа выходов которого соединена с группой входов управляемого делителя 17 частоты и второй группой входов блока 18 сравнения кодов, первая группа входов которого соединена с группой выходов счетчика 7, выход блока 18 соединен с первым

входом элемента И 19 и через элемент НЕ 20 с первым входом элемента И 21, выход элемента И 21 соединен с первым входом элемента ИЛИ 11, а выход элемента И 19 - с третьим входом блока 5 управления, первый выход которого соединен с входами элементов И 10 и 15, третий выход блока 5 управления соединен с входом установки нуля управляемого делителя 17 частоты, выход которого соединен с другими входами элементов И 19 и 15, входные шины 22

и 23 соединены с вторыми входами ключей 1 и 2, счетчик 24 результата соединен с выходом коммутатора 12, счетный вход делителя 25 частоты с постоянным коэффициентом деления соединен с генератором 3

образцовой частоты, вход установки нуля делителя 25 соединен с входом установки нуля управляемого делителя 17 частоты, а выход делителя 25 соединен с вторым входом элемента И 21.

Блок 5 управления содержит триггер 26,

вход которого соединен с первым входом блока 5 управления, инверсный выход триггера 26 соединен с третьим выходом блока 5 управления, формирователь 27, третий вход блока 5 управления соединен с входом триггера 28, прямой выход которого является первым выходом блока 5 управления, R-вход триггера 28 соединен с выходом формирователя 27 и является вторым выходом блока 5 управления, вход формирователя 27 соединен с вторым входом блока 5 управления.

Блок 14 умножения состоит из двух счетчиков 29 и 30 и элемента 31 задержки, причем первая тетрада входов счетчика 29 соединена с шиной логического нуля устройства, вторая тетрада входов счетчика 29 соединена с первой тетрадой выходов счетчика 30, выходы тетрад счетчика 30 являются выходами блока 14, объединенные счетные входы и объединенные входы установки нуля являются соответственно счетным и установочным входами блока 14 умножения, вход «Занесение счетчика 29 соединен через элемент 31 задержки с входом «Занесение счетчика 30 и является входом «Занесение блока 14, выходы счетчика 29 соединены с соответствующими информационными входами счетчика 30, п-я тетрада входов счетчика 29 соединена с (п-1)-й тетрадой выходов счетчика 30.

Блоки 6 и 18 сравнения кодов могут быть выполнены на микросхемах К 561 и П2.

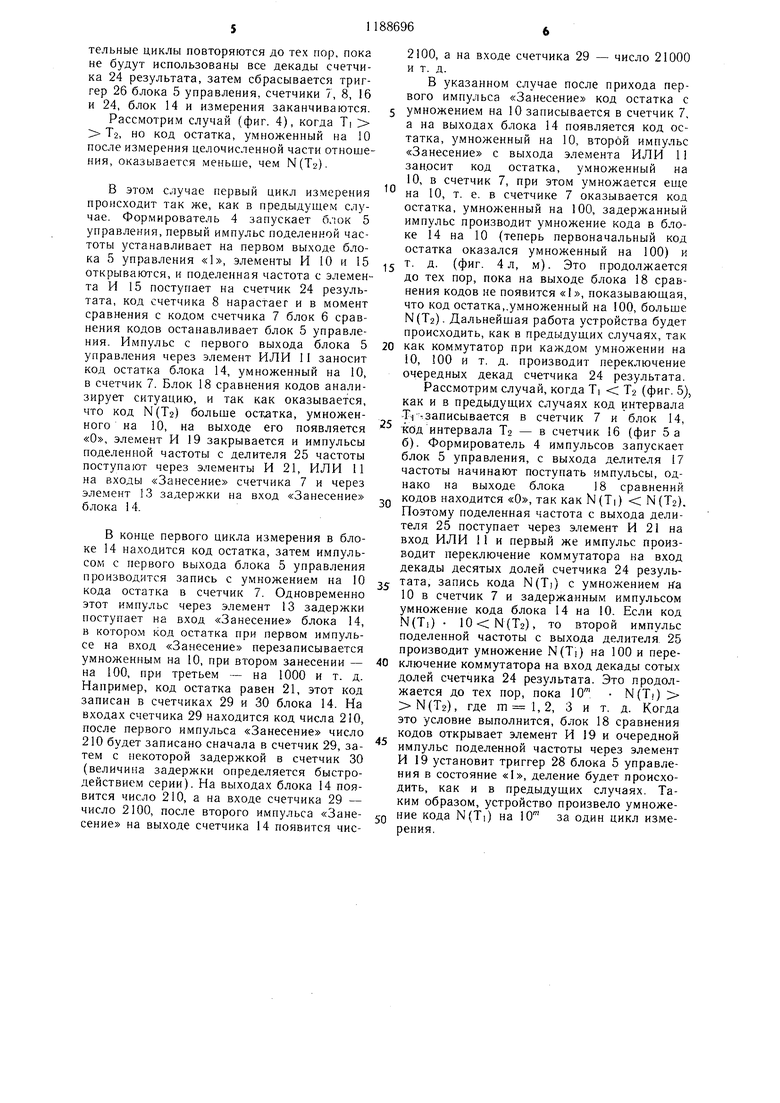

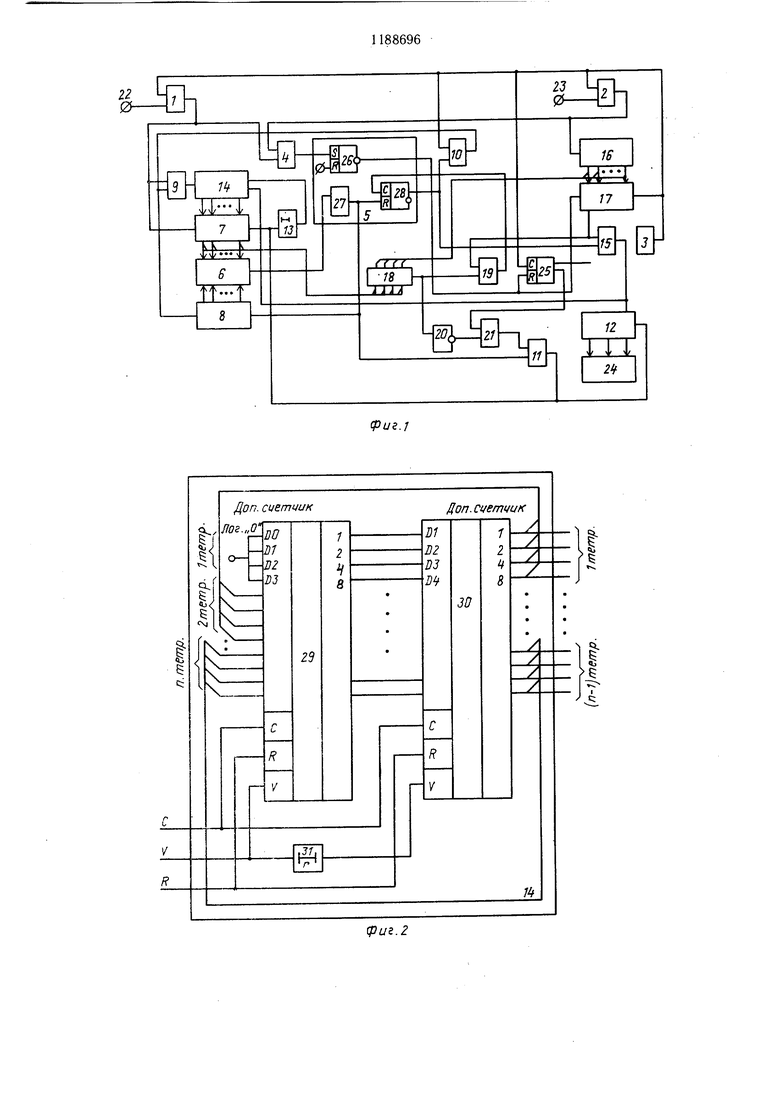

На фиг. 3, 4 и 5 приняты следующие обозначения временных диаграмм: а - сигнал на выходе ключа 2; б - сигнал на выходе ключа 1; в - сигнал на выходе формирователя 4; г - сигнал на третьем выходе блока 5 управления; д - сигнал (frf) на выходе управляемого делителя 17 частоты; е - сигнал на втором выходе блока 5 управления; ж - сигнал на выходе элемента И 15; з - сигнал на выходе элемента И 10; и - эпюра, интерпретирующая нарастание кода в счетчике 8; к - второй выход блока 5 управления; л - сигнал на выходе блока 18 сравнения кодов; м - сигнал на выходе элемента ИЛИ 11.

Устройство работает образом.

В начальный момент времени счетчики 7, 8, 16 и 24, блок 14 и триггер 26 блока 5 управления установлены в состояние «О. Временной интервал Ti приходит на входную шину 22 устройства, а интервал Т2 - на входную шину 23. Ключи 1 и 2 открываются, и импульсы с генератора 3 образцовой частоты начинают поступать на счетчики 7 и 16. В счетчике 7 и блоке 14 оказывается -записан код временного интервала, Ti N(Ti) foT|, а в счетчике 16 - код временного интервала Та N(T9) foT2, где fo - частота с выхода генератора 3 образцовой частоты (фиг. 3 а, б). По окончании записи обоих кодов срабатывает формирователь 4, который фор.мирует сигнал конца записи временных интервалов, и на пер вый вход блока 5 управления приходит сигнал, обозначающий, что можно приступить к обработке кодов N(T|) и N(12) (фиг. Зв), триггер 26 блока 5 управления сигналом с инверсного выхода снимает запрет с управляемого делителя 17 частоты и делителя 25. Счетчик 16 своими выходами соединен с входом управляемого делителя 17 частоты. Таким образом, частота следования коротких импульсов на выходе делителя 17 частоты определяется выражением

f io ± Я(Тг)foT2 TgДальнейшая работа устройства определяется состоянием блока 18 сравнения кодов.

на одну группу входов которого подается код с выхода счетчика 7, на другую группу входов - код N(T2) с выхода счетчика 16.

5 Рассмотрим случай, когда Т; ; То (фиг. За, в). В этом случае на выходе блока 18 сравнения кодов будет «1, которая откроет элемент И 19, и первый же импульс поделенной частоты задним фронтом установит триггер 28 блока 5 управления в состояние «1 (фиг. 3 д, е), открывая этим элементы И 10 и 15. Через элемент И 10 начнется заполнение импульсами генератора 3 счетчиков 8 и блока 14. Код блока 14 периодически сбрасывается импульсами поделенной частоты с выхода элемента И 15. Через коммутатор 12 импульсы поделенной частоты поступают на счетчик 24 результата, в котором к концу первого цикла измерения зафиксировано число, равное целочисленному результату отношения.

0 Первый цикл измерения заканчивается в момент, когда нарастающий код счетчика 3 сравнивается с кодом счетчика 7.

В блоке 14 в этот момент зафиксирован код временного интервала между последним импульсом поделенной частоты и моментом сравнения кодов счетчиков 7 и 8. Счетчик 8 выполнен таким образом, что первая тетрада его входов соединена с шиной «О устройства, вторая тетрада входов счетчика 7 соединена с первой тетрадой выходов

g блока 14, третья тетрада входов счетчика 7 - с второй тетрадой выходов блока 14 и т. д. Поэтому в результате перезаписи кода из блока 14 в счетчик 7 в последнем устанавливается код числа,в 10 раз больший кода числа, записанного в блоке 14.

5 В конце первого цикла измерения импульс с второго выхода блока 5 управления устанавливает счетчик 8 в состояние «О, через элемент ИЛИ 11 производит запись с умножением на 10 кода остатка блока 14 в счетчик 7, переводит коммутатор 12 на

0 работу с декадой десятых долей счетчика 24 результата (фиг. 3 к, м). Предположим, что код остатка, умноженный на 10, оказывается больше, чем код N(T2), импульс поделенной частоты вновь устанавливает триггер 28 блока управления в состояние «1 и цикл измерения повторяется. Появляется разрешающий потенциал на входах элементов И 10 и 15, счетчик 8 и блок 14 опять начинают заполняться импульсами с генератора 3. Блок 14 периодически сбрасывается импульсами поделенной частоты и к концу цикла измерения в нем зафиксируется код остатка. В момент сравнения кодов счетчиков 7 и 8 блок 6 сравнения кодов останавливает блок 5 управления, происходит сброс счетчика 8, через элемент ИЛИ II

5 коммутатор 12 переключается на работу с декадой сотых долей результата счетчика 24 и код остатка, умноженный на 10, записывается в счетчик 7. Такие последовательные циклы повторяются до тех пор, пока не будут использованы все декады счетчика 24 результата, затем сбрасывается триггер 26 блока 5 управления, счетчики 7, 8, 16 и 24, блок 14 и измерения заканчиваются. Рассмотрим случай (фиг. 4), когда Ti 7.2, но код остатка, умноженный на 10 после измерения целочисленной части отношения, оказывается меньше, чем N(T2).

В этом случае первый цикл измерения происходит так же, как в предыдущем случае. Формирователь 4 запускает блок 5 управления, первый импульс поделенной частоты устанавливает на первом выходе блока 5 управления «1, элементы И 10 и 15 открываются, и поделенная частота с элемента И 15 поступает на счетчик 24 результата, код счетчика 8 нарастает и в момент сравнения с кодом счетчика 7 блок 6 сравнения кодов останавливает блок 5 управления. Импульс с первого выхода блока 5 управления через элемент ИЛИ 11 заносит код остатка блока 14, умноженный на 10, в счетчик 7. Блок 18 сравнения кодов анализирует ситуацию, и так как оказывается, что код N(T2) больше остлтка, умноженного на 10, на выходе его появляется «О, элемент И 19 закрывается и импульсы поделенной частоты с делителя 25 частоты поступают через элементы И 21, ИЛИ 11 на входы «Занесение счетчика 7 и через элемент 13 задержки на вход «Занесение блока 14.

В конце первого цикла измерения в блоке 14 находится код остатка, затем импульсом с первого выхода блока 5 управления производится запись с умножением на 10 кода остатка в счетчик 7. Одновременно этот импульс через элемент 13 задержки поступает на вход «Занесение блока 14, в котором код остатка при первом импульсе на вход «Занесение перезаписывается умноженным на 10, при втором занесении - на 100, при третьем - на 1000 и т. д. Например, код остатка равен 21, этот код записан в счетчиках 29 и 30 блока 14. На входах счетчика 29 находится код числа 210, после первого импульса «Занесение число 210 будет записано сначала в счетчик 29, затем с некоторой задержкой в счетчик 30 (величина задержки определяется быстродействием серии). На выходах блока 14 появится число 210, а на входе счетчика 29 - число 2100, после второго импульса «Занесение на выходе счетчика 14 появится чис2100, а на входе счетчика 29 - число 21000 и т. д.

В указанном случае после прихода первого импульса «Занесение код остатка с умножением на 10 записывается в счетчик 7, а на выходах блока 14 появляется код остатка, умноженный на 10, второй импульс «Занесение с выхода элемента ИЛИ 11 заносит код остатка, умноженный на 10, в счетчик 7, при этом умножается енхе

на 10, т. е. в счетчике 7 оказывается код остатка, умноженный на 100, задержанный импульс производит умножение кода в блоке 14 на 10 (теперь первоначальный код остатка оказался умноженный на 100) и

5 т. д. (фиг. 4л, м). Это продолжается до тех пор, пока на выходе блока 18 сравнения кодов не появится «1, показывающая, что код остатка,.умноженный на 00, больше N(T2). Дальнейшая работа устройства будет происходить, как в предыдущих случаях, так

0 как коммутатор при каждом умножении на 10, 00 и т. д. производит переключение очередных декад счетчика 24 результата.

Рассмотрим случай, когда Ti Тг (фиг. 5), как и в предыдущих случаях код интервала -Т-г записывается в счетчик 7 и блок 14,

код интервала Тг - в счетчик 16 (фиг 5 а б). Формирователь 4 импульсов запускает блок 5 управления, с выхода делителя 17 частоты начинают поступать импульсы, однако на выходе блока 18 сравнений кодов находится «О, так как N{T|) N(T2). Поэтому поделенная частота с выхода делителя 25 поступает через элемент И 21 на вход ИЛИ 11 и первый же импульс производит переключение коммутатора на вход декады десятых долей счетчика 24 резульr- тата, запись кода N(Tj) с умножением ila 10 в счетчик 7 и задержанным импульсом умножение кода блока 14 на 10. Если код N(Ti) (T2), то второй импульс поделенной частоты с выхода делителя 25 производит умножение N(Ti) на 100 и переключение коммутатора на вход декады сотых долей счетчика 24 результата. Это продолжается до тех пор, пока Ю N(T,i) N(T2), где m 1,2, 3 и т. д. Когда это условие выполнится, блок 18 сравнения кодов открывает элемент И 19 и очередной импульс поделенной частоты через элемент И 19 установит триггер 28 блока 5 управления в состояние «I, деление будет происходить, как и в предыдущих случаях. Таким образом, устройство произвело умножение кода N(Ti) на за один цикл измерения.

puz.2

X

111 I I I I I I I I I I I I I

jc:;.

iiiiiiiiiiiiiiiiiiiiiii .

| Цифровой измеритель отношения временных интервалов | 1979 |

|

SU864236A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Цифровой измеритель отношения временных интервалов | 1981 |

|

SU983644A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-10-30—Публикация

1984-04-13—Подача