Изобретение относится к автоматике и вычислительной технике и предназначено для умножения частоты выходных импульсов с изменяющимся коэффициентом умножения. .

Целью изобретения является расширение функциональных возможностей устройства, при умножении частоты с расширенным частотным диапазоном.

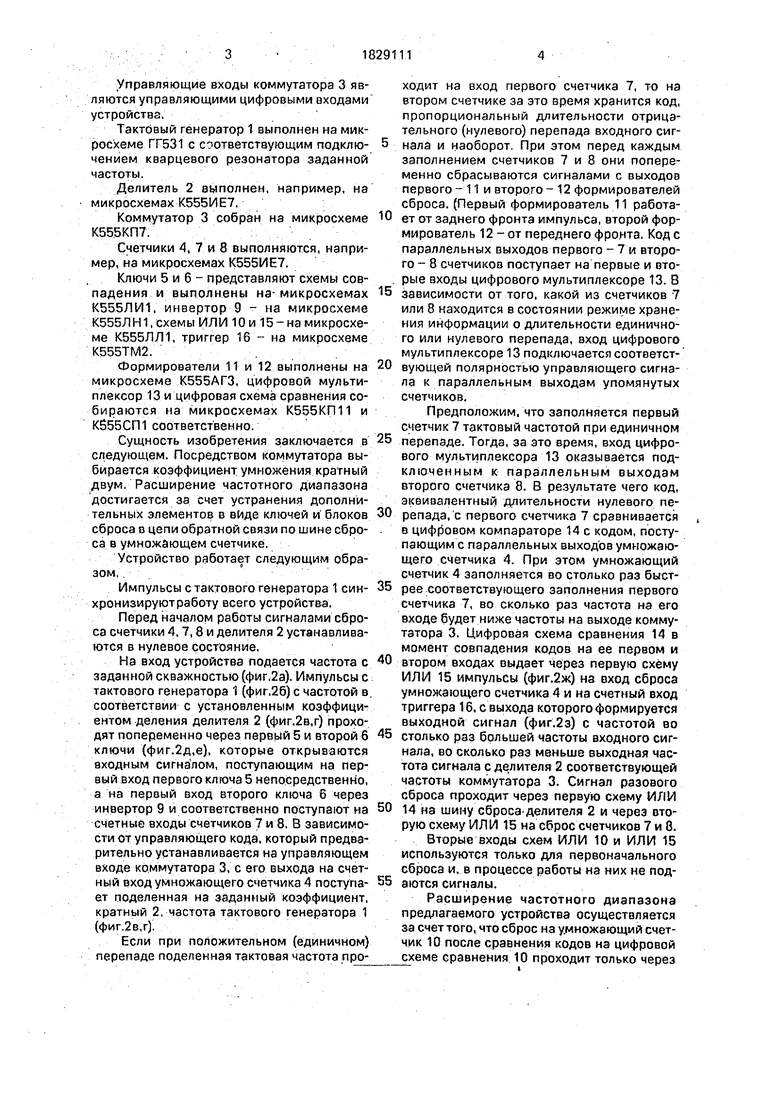

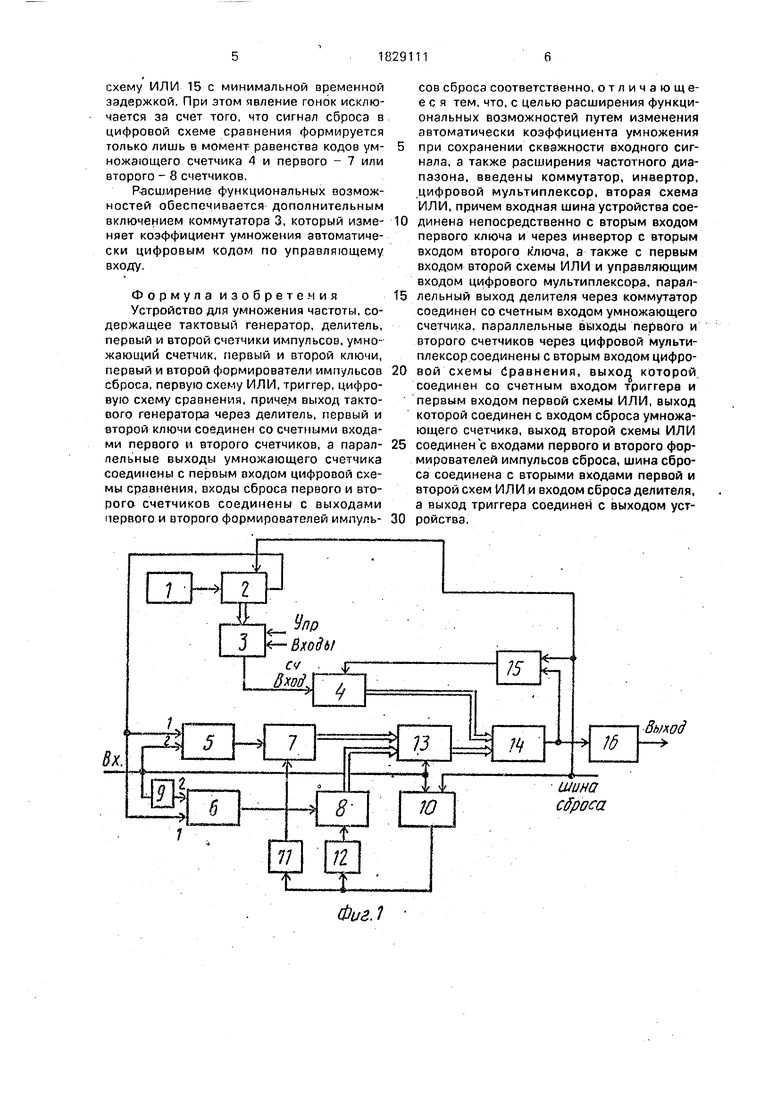

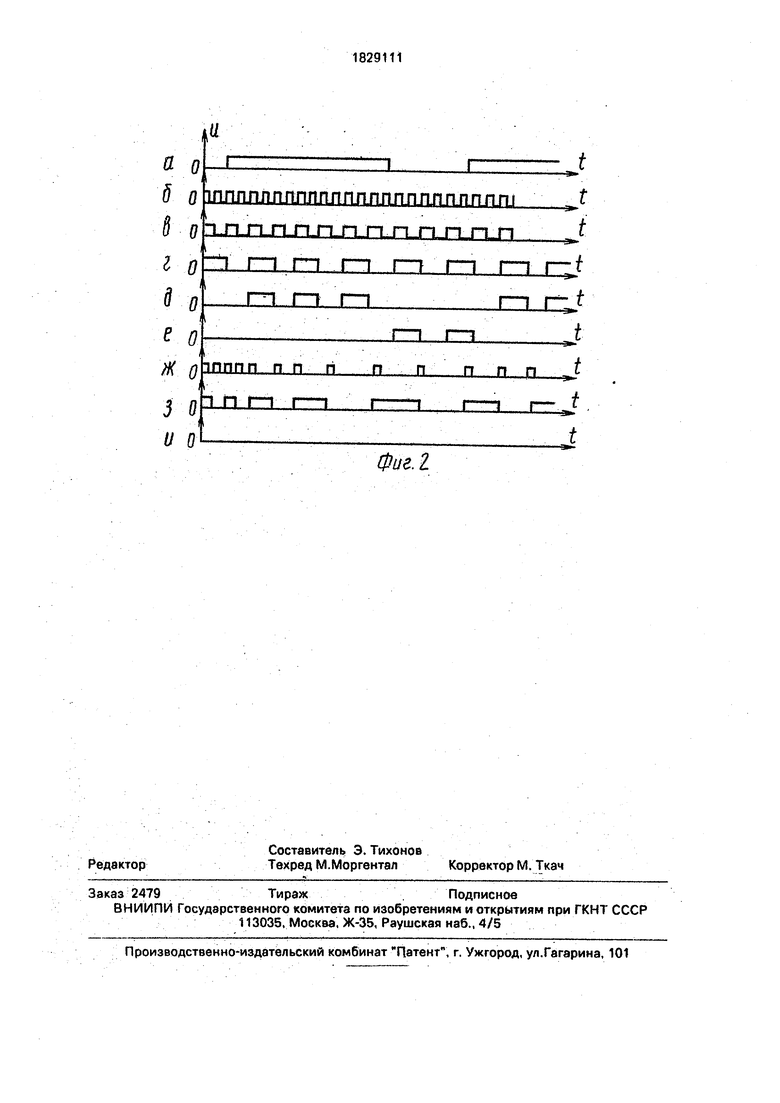

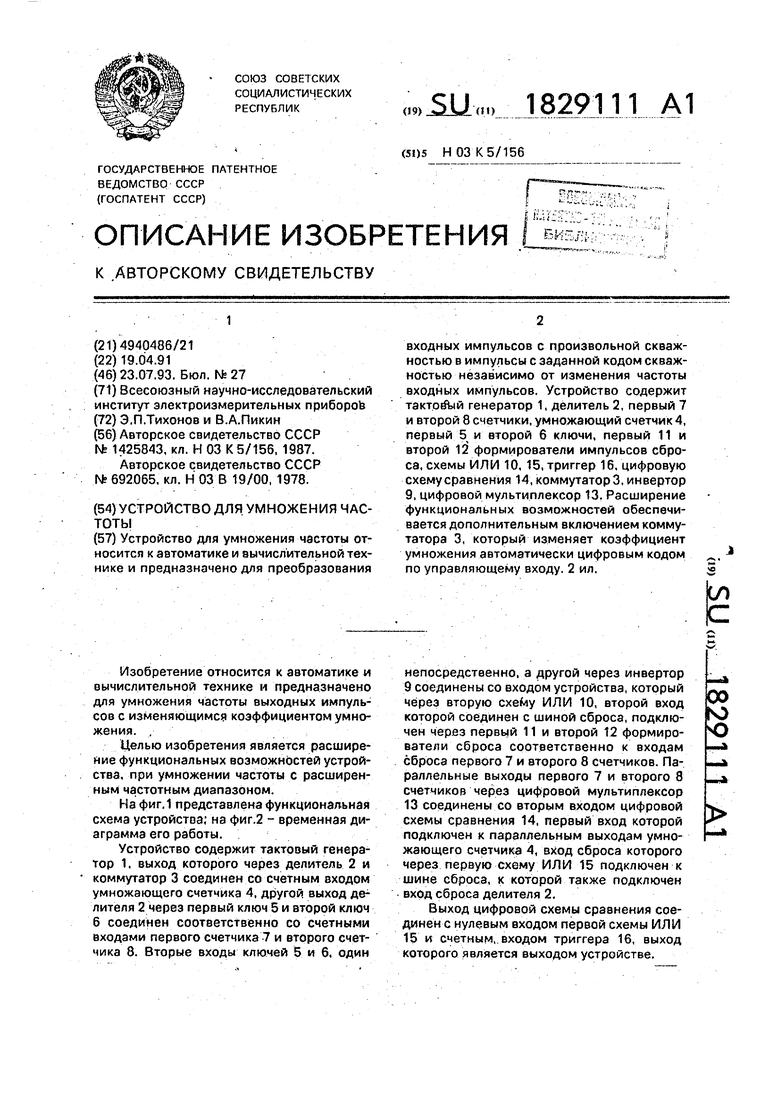

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - временная диаграмма его работы.

Устройство содержит тактовый генератор 1, выход которого через делитель 2 и коммутатор 3 соединен со счетным входом умножающего счетчика 4, другой выход де1 лителя 2 через первый ключ 5 и второй ключ 6 соединен соответственно со счетными входами первого счетчика 7 и второго счетчика 8. Вторые входы ключей 5 и 6, один

непосредственно, а другой через инвертор 9 соединены со входом устройства, который через вторую схему ИЛИ 10, второй вход которой соединен с шиной сброса, подключен через первый 11 и второй 12 формирователи сброса соответственно к входам сброса первого 7 и второго 8 счетчиков. Параллельные выходы первого 7 и второго 8 счетчиков через цифровой мультиплексор 13 соединены со вторым входом цифровой схемы сравнения 14, первый вход которой подключен к параллельным выходам умножающего счетчика 4, вход сброса которого через первую схему ИЛИ 15 подключен к шине сброса, к которой также подключен вход сброса делителя 2.

Выход цифровой схемы сравнения соединен с нулевым входом первой схемы ИЛИ 15 и счетным, входом триггера 16, выход которого является выходом устройстве.

Управляющие входы коммутатора 3 являются управляющими цифровыми входами устройства.

Тактовый генератор 1 выполнен на микросхеме ГГ531 с соответствующим подклю- чением кварцевого резонатора заданной частоты.

Делитель 2 выполнен, например, на микросхемах К555ИЕ7.

Коммутатор 3 собран на микросхеме К555КП7.

Счетчики А, 1 и 8 выполняются, например, на микросхемах К555ИЕ7.

Ключи 5 и 6 - представляют схемы совпадения и выполнены на-микросхемах К555ЛИ1. инвертор 9 - на микросхеме К555ЛН1, схемы ИЛИ 10 и 15-на микросхеме К555ЛЛ1, триггер 16 - на микросхеме К555ТМ2.

Формирователи 11 и 12 выполнены на микросхеме К555АГЗ, цифровой мультиплексор 13 и цифровая схема сравнения собираются на микросхемах К555КП11 и К555СП1 соответственно.

Сущность изобретения заключается в следующем. Посредством коммутатора выбирается коэффициент умножения кратный двум. Расширение частотного диапазона достигается за счет устранения дополнительных элементов в виде ключей и блоков сброса в цепи обратной связи по шине сбро- са в умножающем счетчике.

Устройство работает следующим образом, .

Импульсы с тактового генератора 1 син- хронизируютработу всего устройства,

Перед началом работы сигналами сброса счетчики 4.7,8 и делителя 2 устанавливаются в нулевое состояние.

На вход устройства подается частота с заданной скважностью (фиг,2а), Импульсы с тактового генератора 1 (фиг.2б) с частотой в соответствии с установленным коэффициентом деления делителя 2 (фиг.2в,г) проходят попеременно через первый 5 и второй 6 ключи (фиг.2д,е), которые открываются входным сигналом, поступающим на первый вход первого ключа 5 непосредственно, а на первый вход второго ключа 6 через инвертор 9 и соответственно поступают на счетные входы счетчиков 7 и 8. В зависимости от управляющего кода, который предварительно устанавливается на управляющем входе коммутатора 3, с его выхода на счетный вход умножающего счетчика 4 поступа- ет поделенная на заданный коэффициент, кратный 2, частота тактового генератора 1 (фиг.2в,г).

Если при положительном (единичном) перепаде поделенная тактовая частота проходит на вход первого счетчика 7, то на втором счетчике за это время хранится код, пропорциональный длительности отрицательного (нулевого) перепада входного сигнала и наоборот. При этом перед каждым заполнением счетчиков 7 и 8 они попеременно сбрасываются сигналами с выходов первого - 11 и второго - 1.2 формирователей сброса. (Первый формирователь 11 работает от заднего фронта импульса, второй формирователь 12 - от переднего фронта. Код с параллельных выходов первого - 7 и второго - 8 счетчиков поступает на первые и вторые входы цифрового мультиплексоре 13. 8 зависимости от того, какой из счетчиков 7 или 8 находится в состоянии режиме хранения информации о длительности единичного или нулевого перепада, вход цифрового мультиплексоре 13 подключается соответствующей полярностью управляющего сигнала к параллельным выходам упомянутых счетчиков.

Предположим, что заполняется первый счетчик 7 тактовый частотой при единичном перепаде. Тогда, за это время, вход цифрового мультиплексора 13 оказывается подключенным к параллельным выходам второго счетчика 8. В результате чего код, эквивалентный длительности нулевого перепада, с первого счетчика 7 сравнивается в цифровом компараторе 14 с кодом, поступающим с параллельных выходов умножающего счетчика 4. При этом умножающий счетчик 4 заполняется во столько раз быстрее соответствующего заполнения первого счетчика 7, во сколько раз частота на его входе будет ниже частоты на выходе коммутатора 3. Цифровая схема сравнения 14 в момент совпадения кодов на ее первом и втором входах выдает через первую схему ИЛИ 15 импульсы (фиг.2ж) на вход сброса умножающего счетчика 4 и на счетный вход триггера 16, с выхода которого формируется выходной сигнал (фиг.2з) с частотой во столько раз большей частоты входного сигнала, во сколько раз меньше выходная частота сигнала с делителя 2 соответствующей частоты коммутатора 3. Сигнал разового сброса проходит через первую схему ИЛИ 14 на шину сброса делителя 2 и через вторую схему ИЛИ 15 на сброс счетчиков 7 и 8.

Вторые входы схем ИЛИ 10 и ИЛИ 15 используются только для первоначального сброса и. в процессе работы на них не подаются сигналы.

Расширение частотного диапазона предлагаемого устройства осуществляется за счет того, что сброс на умножающий счетчик 10 после сравнения кодов на цифровой схеме сравнения 10 проходит только через

схему ИЛИ 15 с минимальной временной задержкой. При этом явление гонок исключается за счет того, что сигнал сброса в цифровой схеме сравнения формируется только лишь в момент- равенства кодов ум- ножающего счетчика 4 и первого - 7 или второго - 8 счетчиков.

Расширение функциональных возможностей обеспечивается дополнительным включением коммутатора 3, который изме- няет коэффициент умножения автоматически цифровым кодом по управляющему входу.

Формула изобретен и я-

Устройство для умножения частоты, содержащее тактовый генератор, делитель, первый и второй счетчики импульсов, умножающий счетчик, первый и второй ключи, первый и второй формирователи импульсов сброса, первую схему ИЛИ. триггер, цифровую схему сравнения, причем выход тактового генератора через делитель, первый и второй ключи соединен со счетными входами первого и второго счетчиков, а парал- лельные выходы умножающего счетчика соединены с первым входом цифровой схемы сравнения, входы сброса первого и второго счетчиков соединены с выходами первого и второго формирователей имлуль-

сов сброса соответственно, отличающееся тем, что, с целью расширения функциональных возможностей путем изменения автоматически коэффициента умножения при сохранении скважности входного сигнала, а также расширения частотного диапазона, введены коммутатор, инвертор, цифровой мультиплексор, вторая схема ИЛИ, причем входная шина устройства соединена непосредственно с вторым входом первого ключа и через инвертор с вторым входом второго ключа, а также с первым входом второй схемы ИЛИ и управляющим входом цифрового мультиплексора, параллельный выход делителя через коммутатор соединен со счетным входом умножающего счетчика, параллельные выходы первого и второго счетчиков через цифровой мультиплексор соединены с вторым входом цифровой схемы Сравнения, выход которой соединен со счетным входом триггера и первым входом первой схемы ИЛИ, выход которой соединен с входом сброса умножающего счетчика, выход второй схемы ИЛИ соединение входами первого и второго формирователей импульсов сброса, шина сброса соединена с вторыми входами первой и второй схем ИЛИ и входом сброса делителя, а выход триггера соединен с выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазометр мгновенных значений | 1981 |

|

SU980015A1 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Цифровой умножитель частоты | 1987 |

|

SU1596444A1 |

| Цифровой формирователь с умножением частоты | 1990 |

|

SU1775839A1 |

| Умножитель частоты | 1984 |

|

SU1179334A1 |

| Устройство для измерения объема бревен | 1985 |

|

SU1380808A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

Устройство для умножения частоты относится к автоматике и вычислительной технике и предназначено для преобразования входных импульсов с произвольной скважностью в импульсы с заданной кодом скважностью независимо от изменения частоты входных импульсов. Устройство содержит тактовой генератор 1, делитель 2, первый 7 и второй 8 счетчики, умножающий счетчик 4, первый 5 и второй 6 ключи, первый 11 и второй 12 формирователи импульсов сброса, схемы ИЛИ 10, 15, триггер 16, цифровую схему сравнения 14, коммутатор 3, инвертор 9, цифровой мультиплексор 13, Расширение функциональных возможностей обеспечивается дополнительным включением коммутатора 3, который изменяет коэффициент умножения автоматически цифровым кодом по управляющему входу. 2 ил.

Фиг.1

Выход

шина сброса

Фаг. I

| Преобразователь кода в пачку импульсов | 1987 |

|

SU1425843A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дискретный умножитель частоты повторения импульсов | 1977 |

|

SU692065A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-07-23—Публикация

1991-04-19—Подача