00

00 00

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| Устройство для ввода информации | 1986 |

|

SU1383330A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Кодек блочного кода | 1985 |

|

SU1358098A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Многоканальное устройство для измерения температуры | 1990 |

|

SU1791731A1 |

| Устройство для измерения токов через клеточную мембрану | 1986 |

|

SU1405814A1 |

УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ, содержащее аналого-цифровой преобразователь, последовательно соединенные цифроаналоговый преобразователь и аналоговый сумматор, отличающееся тем, что, с целью увеличения быстродействия, в него введены счетчик, инвертор, элемент И, регистр сдвига, цифровой сумматор, блок элементов И, выходы которого являются выходной шиной, первые входы объединены и подключены к выходу элемента И, вторые входы соединены с выходами цифрового сумматора, первые входы которого соединены с выходами регистра сдвига, а вторые входы объединены с первыми входами регистра сдвига и подключены к выходам аналого-цифрового преобразователя, второй вход которого объединен с вторым входом регистра сдвига и первым входом элемента И и подключен к выходу инвертора, вход которого объединен с входом счетчика и является первой входной шиной, выходы счетчика соединены с вторым и третьим входами элемента И и входами цифроаналогового преобразователя, причем второй вход § аналогового сумматора является второй входной шиной. (Л

ф ф ф ф ф

USbix. щлрр.

Vuz.l

Изобретение относится к вычислительной и цифровой измерительной технике.

Целью изобретения является увеличение быстродействия.

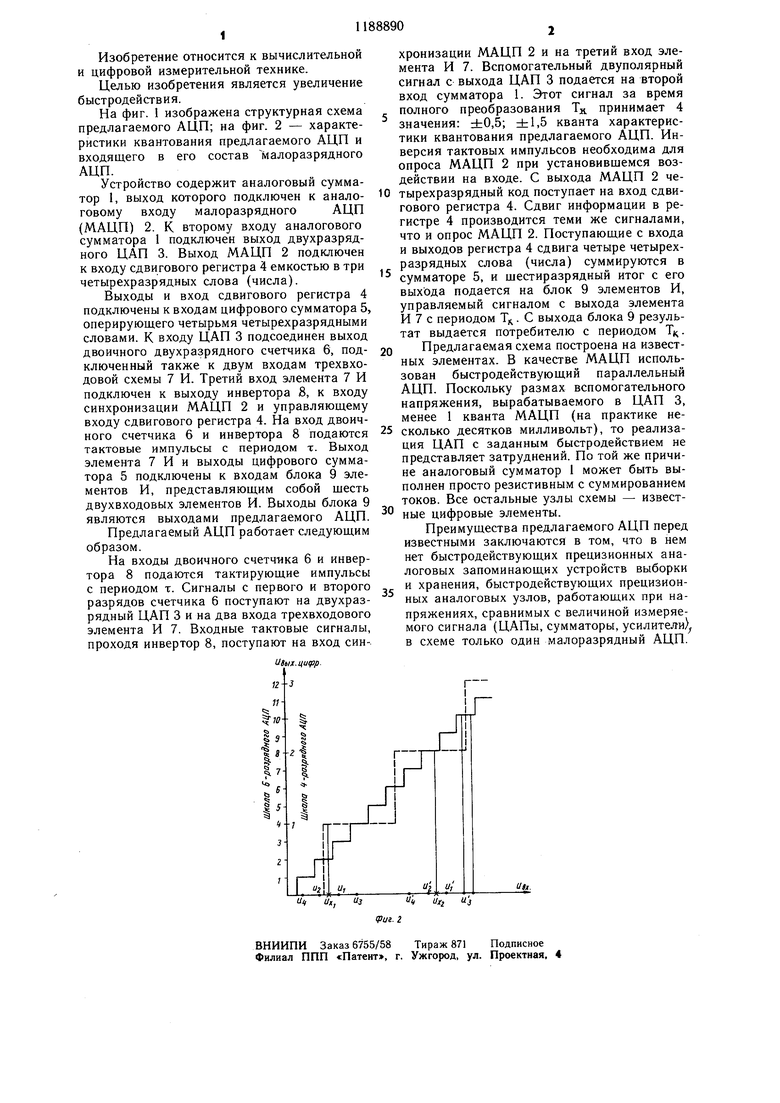

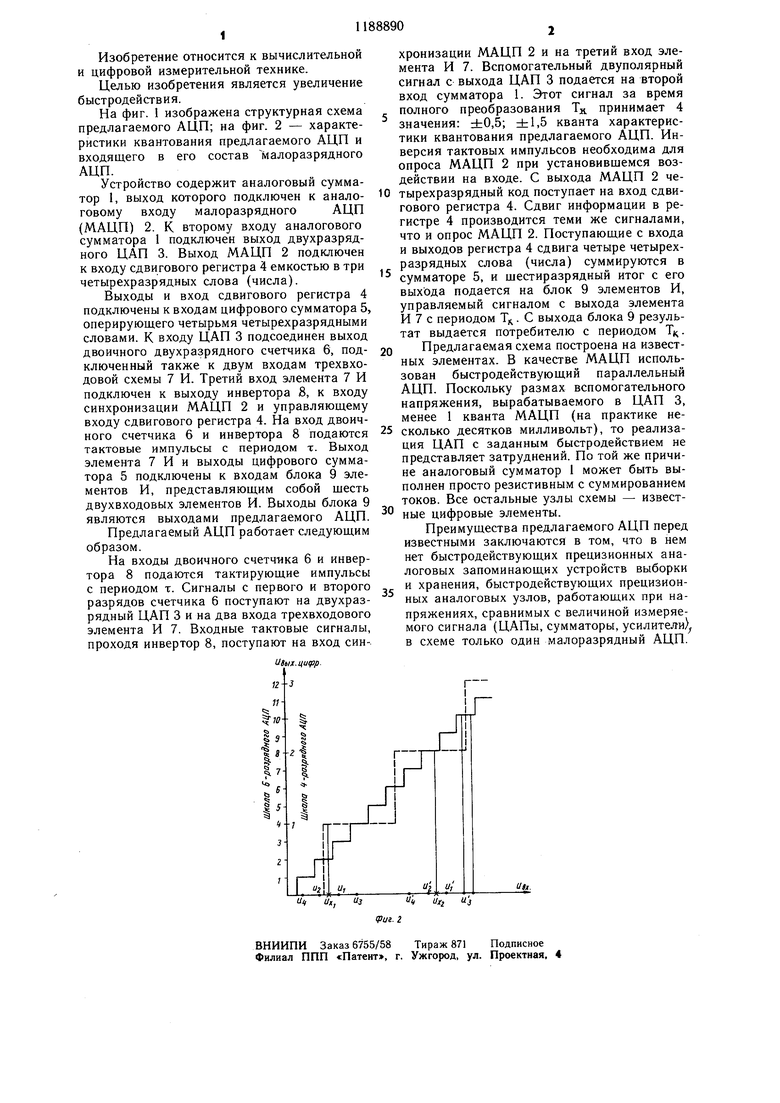

На фиг. 1 изображена структурная схема предлагаемого АЦП; на фиг. 2 - характеристики квантования предлагаемого АЦП и входящего в его состав малоразрядного АЦП.

Устройство содержит аналоговый сумматор 1, выход которого подключен к аналоговому входу малоразрядногоАЦП (МАЦП) 2. К второму входу аналогового сумматора 1 подключен выход двухразрядного ЦАП 3. Выход МАЦП 2 подключен к входу сдвигового регистра 4 емкостью в три четырехразрядных слова (числа).

Выходы и вход сдвигового регистра 4 подключены к входам цифрового сумматора 5, оперирующего четырьмя четырехразрядными словами. К входу ЦАП 3 подсоединен выход двоичного двухразрядного счетчика 6, подключенный также к двум входам трехвходовой схемы 7 И. Третий вход элемента 7 И подключен к выходу инвертора 8, к входу синхронизации MAU,n 2 и управляющему входу сдвигового регистра 4. На вход двоичного счетчика 6 и инвертора 8 подаются тактовые импульсы с периодом т. Выход элемента 7 И и выходы цифрового сумматора 5 подключены к входам блока 9 элементов И, представляющим собой щесть двухвходовых элементов И. Выходы блока 9 являются выходами предлагаемого АЦП. Предлагаемый АЦП работает следующим образом.

На входы двоичного счетчика 6 и инвертора 8 подаются тактирующие импульсы с периодом т. Сигналы с первого и второго разрядов счетчика 6 поступают на двухразрядный ЦАП 3 и на два входа трехвходового элемента И 7. Входные тактовые сигналы, проходя инвертор 8, поступают на вход синUSiH.nuipp

хронизации МАЦП 2 и на третий вход элемента И 7. Вспомогательный двуполярный сигнал с выхода ЦАП 3 подается на второй вход сумматора 1. Этот сигнал за время полного преобразования Т принимает 4 значения: ±0,5; ±1,5 кванта характеристики квантования предлагаемого АЦП. Инверсия тактовых импульсов необходима для опроса МАЦП 2 при установивщемся воздействии на входе. С выхода МАЦП 2 четырехразрядный код поступает на вход сдвигового регистра 4. Сдвиг информации в регистре 4 производится теми же сигналами, что и опрос МАЦП 2. Поступающие с входа и выходов регистра 4 сдвига четыре четырехразрядных слова (числа) суммируются в

сумматоре 5, и щестиразрядный итог с его выхода подается на блок 9 элементов И, управляемый сигналом с выхода элемента И 7 с периодом Т. С выхода блока 9 результат выдается потребителю с периодом Т.

0 Предлагаемая схема построена на известных элементах. В качестве МАЦП использован быстродействующий параллельный АЦП. Поскольку размах вспомогательного напряжения, вырабатываемого в ЦАП 3, менее 1 кванта МАЦП (на практике несколько десятков милливольт), то реализация ЦАП с заданным быстродействием не представляет затруднений. По той же причине аналоговый сумматор 1 может быть выполнен просто резистивным с суммированием токов. Все остальные узлы схемы - известные цифровые элементы.

Преимущества предлагаемого АЦП перед известными заключаются в том, что в нем нет быстродействующих прецизионных аналоговых запоминающих устройств выборки и хранения, быстродействующих прецизионных аналоговых узлов, работающих при напряжениях, сравнимых с величиной измеряемого сигнала (ЦАПы, сумматоры, усилители), в схеме только один малоразрядный АЦП.

| Аналого-цифровые преобразователи Под ред | |||

| Г | |||

| Д | |||

| Бахтиарова | |||

| М.: Сов | |||

| радио, 1980, с | |||

| Эксцентричный фильтр-пресс для отжатия торфяной массы, подвергшейся коагулированию и т.п. работ | 1924 |

|

SU203A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Гнатек Ю | |||

| Р | |||

| Справочник по цифроаналоговым и аналого-цифровым преобразователям | |||

| М.: Радио и связь, 1982, с | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-10-30—Публикация

1983-11-11—Подача