второго счетчика, первый информационый вход мультиплексора блока управления подключен к выходу третьего счетчика блока управления, счетный вход которого объединен с выходом второго элемента задержки и соеди нен с выходом пятого элемента И блока управления, первый, второй и третий управляющие входы блока выбора центрального отсчета подключены соответственно к выходам первого элемента И, второго элемента задержки и третьего элемента И блока управления, первый выход блока выбора центрального отсчета соединен с третьим входом третьего элемента И и через третий элемент НЕ - с вторым входом четвертого элемента И блока управления, второй выход блока выбора центрального отсчета подключен к второму информационному входу мультиплексора блока управления, выход одйовибратора соединен с управляющим входом Коммутатора, выход мультиплексора блока управления подкдючен к адресному входу мультиплексора, выход которого соединен с информационным входом коммутатора, первый информационный выход которого подкключен к первому информационному входу блока выбора центрального отсчета, второй информационный вход которого объединен с информационным входом мультиплексора и соединен с выходом регистра, тактовый вход которого объединен с тактовым входом аналого-цифрового преобразователя и подключен к выходу первого элемента И блока управления, второй выход коммутатора является выходом устройства.

2, Устройство по п.1, отличающееся тем, что блок выбора центрального отсчета содержит группу и m компараторов, две группы из rt элементов И, две груп91920

пы из m элементов ИЛИ, группу из m реверсивных счетчиков, группу из т элементов НЕ, группу из m элементов ИЛИ-НЕ, элемент , группу элементов памяти, -й вход которого подключен к выходу -го

элемента ИЛИ-НЕ группы, (где 1...т) и объединен с i-м входом элемента ИЛИ-НЕ, , j-й вход (где 4 1.,.К-1 ) -го элемента ИЛИ-НЕ группы соединен с J-M выходом разряда -го счетчика, выход k-ro разряда которого подключен к первому входу 1-го элемента И первой группы и через элемент НЕ - к первому входу -го , элемента И второй группы, выходы

J-X элементов И первой и второй групп . соединены с первыми входами элементов ИЛИ одноименных групп, вторые входы которых подключены соответственно к первому и второму выходам 1-го компаратора, выход -j-ro элемента ИЛИ первой группы соединен с входом сложения i-го реверсивного счетчика группы, вход вычитания которого подключен к выходу i-го элемента ИЛИ второй группы, информационные входы реверсивных счетчиков группы объединены и являются первым входом блока выбора дентрального отсчета, управляющие входы компараторов объединены и являются вторым .. входом блока выбора центрального . отсчета, вторые входы элементов И первой и второй групп объединены и являются третьим входом блока выбора центрального отсчета, первым выходом которого является выход элемента ИЛИ-НЕ, вторым выходом блока выбора центрального отсчета является выход группы элементов памяти, первые входы компараторов объедине- . ны и являются первым информационным входом блока выбора центрального отсчета, вторые входы компараторов являются вторым информационным входом блока выбора центрального отсчета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения момента разладки случайных процессов | 1985 |

|

SU1260973A1 |

| Сглаживающее устройство | 1984 |

|

SU1265797A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1423982A1 |

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

| ОДНОКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393491C2 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Устройство для управления @ -фазным шаговым двигателем | 1987 |

|

SU1473066A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

1

Изобретение относится к специализированным средствам вычислительной техники и может быть использовао

НО ДЛЯ аппаратурного анализа случайных процессов в системах сбора и обработки информации. . ,

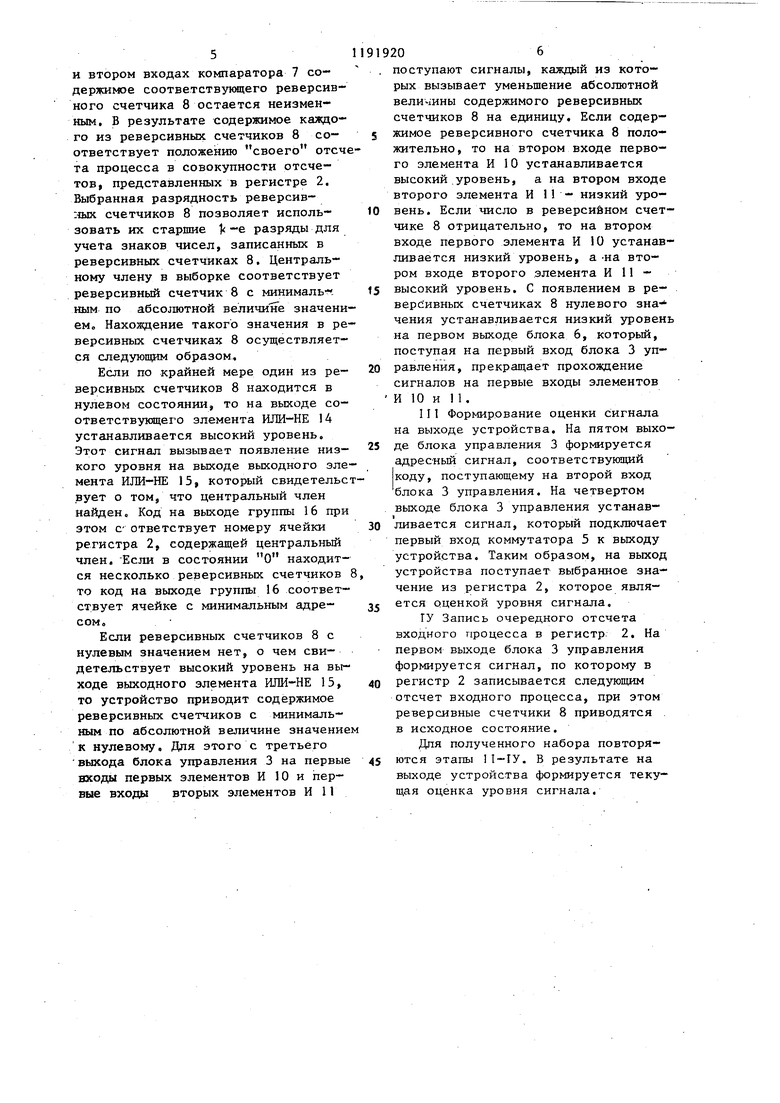

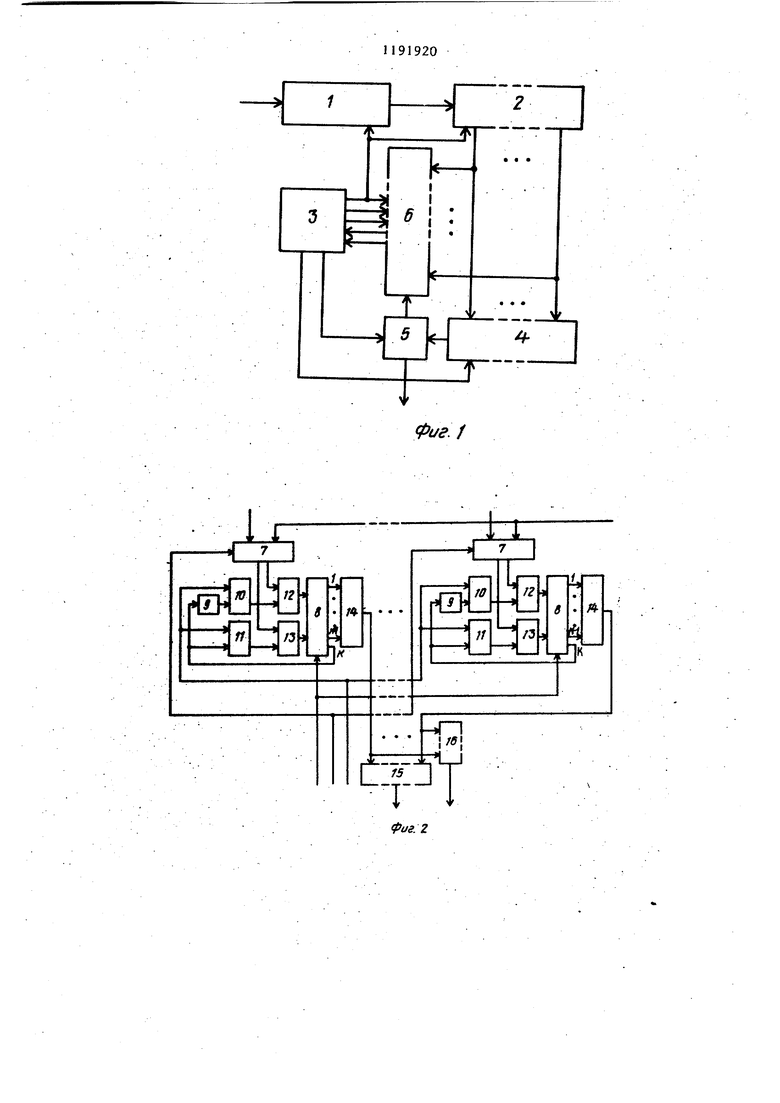

На фиг,1 представлена блок -схе . устройства;на фиг.2 - блок-схеМа бка выбора центрального отсчета:; на фиг.З - блок-схема блока управления ...

- Устройство для текущей оценки уровня сигнала содержит аналогоцифровой преобразователь 1, регистр 2, блок 3 управления, мультиплексор 4, коммутатор 5 и блок 6 выбора центрального отсчета. Блок 6 содержит компараторы 7, реверсивные счетчики 8, элеме т НЕ 9, элементы И 10 и 11, элементы ИЛИ 12 и 13, элементы ИЛИ-НЕ 14 выходной элемент ИЛИ-НЕ 15, группу 16 элементов памяти.

Блок 3 содержит генератор 17 с непрерывной последовательностью импульсов, счетчики 18 и 19, триггеры 20 и 21, счетчик 22, мультиплексор 23, элементы задержки 24 и 25, одновибратор 26, элементы НЕ 27-29, элемент ИЛИ-НЕ 30, элемент И-НЕ 31, элементы И 32 - 36 и вывод 37 начальной установки.

Количество ячеек регистра 2, представляющего собой регистр сдвига, равно т(П1нечетно ). Разрядность реверсивных счетчиков 8 равна k и выбирается из условия 2 /т-1.

Сущность работы устройства заключается в выборе в. качестве текущей оценки неизвестного уровня сигнала центрального члена в совокупности отсчетов процесса, предсталенных в регистре 2.Этапы работы устройства для текущей оце.нки уровня сигнала следую- .

I Заполнение регистра 2. Исследуемая реализация, представляющая собой сумму кусочно-постоянного сигнала и аддитивной помехи, лосту,пает с входа устройства на первый вход аналого-цифрового преобразователя 1, На первом выходе блока 3 управления формируется m сигналор, которые поступают на второй вход аналого-цифрового преобразователя 1, первый вход регистра 2 и через первый управляющий вход блока 6 на третьи входы реверсивных

9204

счетчиков 8, Под воздействием эти сигналов на выходе аналого-хщфрового Преобразователя 1 устанавлив ются отсчеты входной функции в виде параллельного кода, которые записьшаются в регистр 2. Реверсивные счетчики 8 под действием первого же сигнала, поступившего на их третьи входы, устанавливаются в нулевое состояние,

Если содержимое своей ячейки меньше содержимого очередной ячейки, то на первом выходе компарато- ра 7 появляется сигнал, если больше, то сигнал появляется на втором выходе компаратора 7. Соответственно появляется сигнал либо на выходе первого элемента ИЛИ 12 и первом входе реверсивного счетчика 8, либо на выходе второго элемента ИЛИ 13 и втором входе реверсивного счетчика 8. В первом случае содержимое реверсивного счетчика 8 уменьшается на единицу, во втором случае - увеличивается на единицу. При равенстве значений на первом

5

и втором входах компаратора 7 содержимое соответствующего реверсив ного счетчика 8 остается неизменным, В результате содержимое каждого из реверсивных счетчиков 8 соответствует положению своего отсчта процесса в совокупности отсчетов, представленных в регистре 2. Выбранная разрядность реверсив:и к счетчиков 8 позволяет использовать их старшие 1 -е разряды для учета знаков чисел, записанных в реверсивных счетчиках 8. Центральному члену в выборке соответствует реверсивный счетчик 8 с минималь-. ным по абсолютной величине значением. Нахождение такого значения в реверсивных счетчиках 8 осуществляется следующим образом.

Если по крайней мере один из реверсивных счетчиков 8 находится в нулевом состоянии, то на выходе соответствующего элемента ИЛИ-НЕ 14 устанавливается высокий уровень. Этот сигнал вызывает появление низ- кого уровня на выходе выходного элемента ИЛИ-НЕ 15, который свидетельсвует о том, что центральный член найден. Код на выходе группы 16 при зтом с- ответствует номеру ячейки регистра 2, содержащей центральный член. Если в состоянии О находится несколько реверсивных счетчиков то код на выходе группы 16 соответствует ячейке с минимальным адре- сом.

Если реверсивных счетчиков 8 с нулевым значением нет, о чем свидетельствует высокий уровень на выходе выходного элемента ИЛИ-НЕ 15, то устройство приводит содержимое реверсивных счетчиков с минимальным по абсолютной величине значение к нулевому. Для этого с третьего выхода блока управления 3 на первые входы первых элементов И 10 и первые входы вторых элементов И 11

206

поступают сигналы, каждый из которых вызывает уменьшение абсолютной величины содержимого реверсивных счетчиков 8 на единицу. Если содержимое реверсивного счетчика 8 положительно, то на втором входе первого элемента И 10 устанавливается высокий.уровень, а на втором входе второго элемента И 11 - низкий уровень. Если число в реверсийном счетчике 8 отрицательно, то на втором входе первого элемента И 10 устанавливается низкий уровень, а-на втором входе второго элемента И 11 высокий уровень. С появлением в реверсивных счетчиках 8 нулевого зна- чения устанавливается низкий уровень на первом выходе блока 6, который, поступая на первый вход блока 3 управления, прекращает прохождение сигналов на первые входы элементов

И 10 и 11.

111 Формирование оценки сигнала на выходе устройства. На пятом выходе блока управления 3 формируется адресный сигнал, соответствующий коду, поступающему на второй вход блока 3 управления. На четвертом выходе блока 3 управления устанавливается сигнал, который подключает первый вход коммутатора 5 к выходу устройства. Таким образом, на выход устройства поступает выбранное значение из регистра 2, которое является оценкой уровня сигнала.

ГУ Запись очередного отсчета входного процесса в регистр. 2. На первом выходе блока 3 управления формируется сигнал, по которому в регистр 2 записывается следующим отсчет входного процесса, при этом реверсивные счетчики 8 приводятся в исходное состояние.

Для полученного набора повторяются этапы 11-1У. В результате на выходе устройства формируется текущая оценка уровня сигнала.

фиг /

ti

L..

Фиг. 3

| Авторское свидетельство СССР :№ 762009, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления текущей оценки среднего значения | 1977 |

|

SU619924A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-15—Публикация

1984-05-07—Подача