Объединены и подключены к выходу второго блока памяти, выход ключа соединен с вторым входом сумматора, вторые входы первого и второго компараторов соответственно являются первым и вторым управляющими входами коррелятора, выходы первого и второго компараторов соединены соответственно с первым и вторым управляющими входами блока выбора значащих разрядов случайного сигнала, выход которого соединен с информационным входом второго регистр1а, управляющий вход которого подключен к выходу дешифратора блока управления, выход второго регистра соединен с информационным входом первого регистра, управляющий вход которого подключен к выходу старшего разряда второго счетчика блока управления, выход первого регистра является вторым выходом коррелятора.

2. Коррелятор по п. 1, о т л ичающийся тем, что блок переполнения содержит мультиплексор и п элемент ИЛИ, выход которого соединен с нулевым разрядом информационного входа мультиплексора, первьй разряд информационного входа которого объединен с первым входом элемента ИЛИ, второй, третий и седьмой разряды информационного входа мультиплексора объединены и подключены к шине нулевого потенциала, четвертый, пятый и шестой разряды информационного входа мультиплексора объединены и подключены к шине единичного потенциала.

нулевой и первый разряды управляющего входа мультиплексора являются управляющим входом блока, первый и второй входы элемента ИЛИ и второй разряд управляющего входа мультиплексора являются информационным входом блока, выход мультиплексора является выходом блока.

3, Коррелятор по п. 1, о т л ичающийся. тем, что блок выбора значащих разрядов случайного сигнала содержит первьш, второй и третий элементы НЕ, элемент ЗИ-ИЛИ и элемент 4И-ИЛИ, первый и второй входы, которого объединены с первьм и вторым входами элемента ЗЙ-ИЛИ, третий и четвертый входы элемента 4И-И1Ш и третий вход элемента ЗИ-ИПИ объединены и подключены к выходу первого элемента НЕ, пятый и шестой входы элемента 4И-ИЛИ и четвертый вход элемента ЗИ-ИЛИ объединены и подключены к выходу второго элемента НЕ, седьмой и восьмой входы элемента 4И-ИЛИ объединены и подключены к выходу третьего элемента НЕ, девятый и десятий входы элемента 4И-ИЖ соответственно объединены с входами первого и второго элементов НЕ и являются соответственно первым и вторым управляющими входами блока, одиннадцатый вход элемента 4И-ИЛИ объединен с входом третьего элемента НЕ с пятым и шестым входами элемента ЗИ-ИЖ и является информационным входом блока, выходы элементов ЗИИЛИ и 4Иг-ИЛИ являются выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления скользящего среднего | 1984 |

|

SU1193688A1 |

| Устройство для регистрации аналогового процесса | 1986 |

|

SU1429171A1 |

| Устройство для анализа распределений случайных процессов | 1984 |

|

SU1226487A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1439619A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Устройство для ввода информации | 1989 |

|

SU1645949A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Устройство поиска шумоподобного сигнала | 1988 |

|

SU1540020A1 |

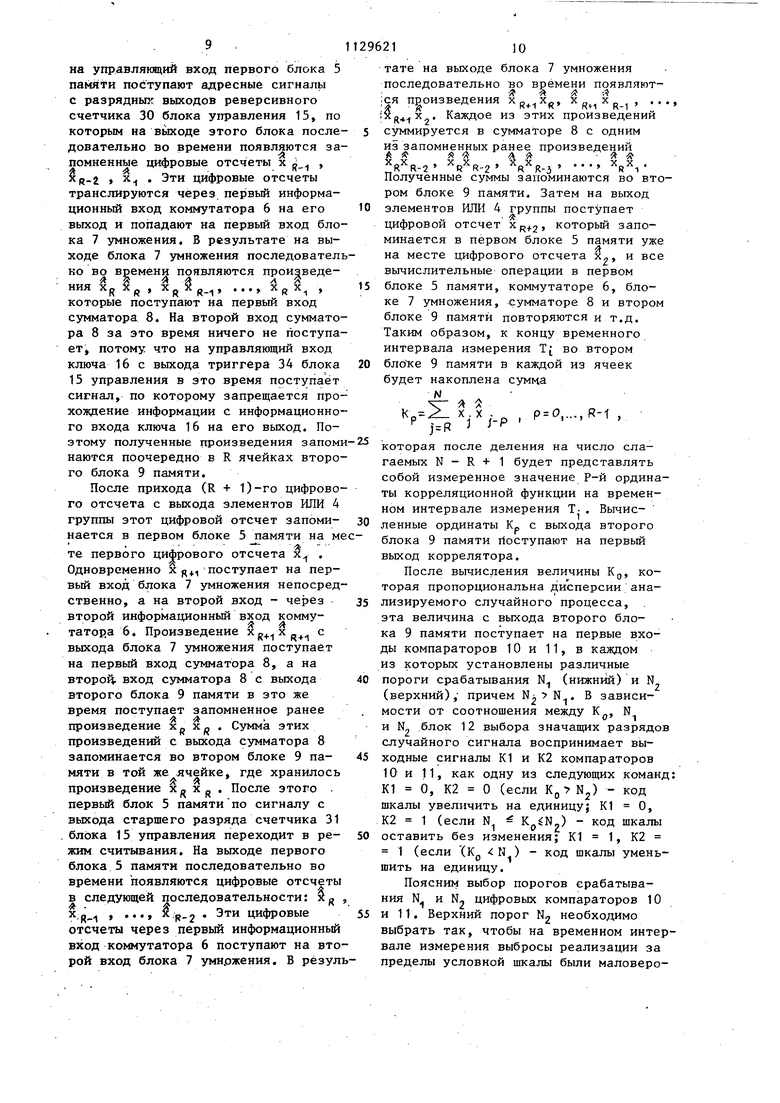

ЦИФРОВОЙ КОРРЕЛЯТОР, содержащий ключ, аналого-цифровой преобразователь,, информационный вход которого является информационным входом коррелятора, первьй блок памяти, выход которого соединен с первым информационным входом коммутатора, выход которого соединен с первым входом блока умножение, второй вход которого объединен с вторым информационным входом коммутатсзра, выход блока умножения соединен с первым входом сумматора, выход которого соединен с информационным входом второго блока памяти, выход которого является первым выходом коррелятора, блок управления, содержащий реверсивный счетчик f- дешифратор, триггер, первый и второй счетчики, генератор импульсов, выход которого соединен с суммирзгющим входом .реверсивного счетчика, информационным входом первого счетчика, зыход старшего разряда которого соединен с вычитающим входом реверсивного счетчика, информационным входом второго счетчика и первым входом дешифратора второй вход которого соединен с разрядными выходами второго счетчика, выходы промежуточного и старшего разрядов которого соединены соответственно с нулевым и единичным установочными входами триггера, выход которого соединен с управляющим входом ключа, выход генератора импульсов и разрядные выходы первого счетчика блока управления объединены ,и подключены к управляющему входу второго блока памяти, выход старшего разряда первого счетчика блока управления соединен с управляющими входами коммутатора и аналого-цифрового преобразователя, выход-.реверсивного счетчика блока управления соединен с выходом старшего разряда первого счетчика и подключен к выходу первого блока памяти, отличающийс я тем, что, с целью расширения динамического диапазона, в него введены первьм и второй регистры, первый и второй компараторы, группа эле.ментов ИЛИ, блок выбора значащих разрядов случайного сигнала мультиплексор и блок переполнения, информационньй вход которого объединен с информационным входом мультиплексора и подключен к выходу аналого-цифрового преобразователя, управляющий вход блока переполнения объединен с управлякицим входом мультиплексора, информационным входом блока выбора значащих разрядов случайного сигнала и подключен к выходу первого регистра, выход блока переполнения соединен с первыми входами элементов ИЛИ группы, вторые входы которых подключены соответственно к выходам мультиплексора, вьгходы элементов ИЛИ группы соединены с информационным входом первого блока памяти и вторым информационным входом коммутатора, первые входы компараторов, управляющий вход ключа

1

Изобретение относится к измерительной и вычислительной технике и предназначено для измерения корреляционной функции нестационарного слзгчайного процесса.

ИзвестноУстройство, работающее по методу умножения, содержащее аналого-цифровой преобразователь .(АЦП), блок памяти, умножитель, накапливающий сумматор и блок управления Cl.J.

Недостатком указанного устройства является малый динамический диапазон

(диапазон амплитуд реализаций анализируемого случайного процесса).

Наиболее близким к предлагаемому по технической сущности является

5 цифровой коррелятор, содержащий АЦП, первьй и второй блоки памяти, коммутатор,, умножитель, сумматор, ключ, блок управления, а также блок модификации адреса 2.

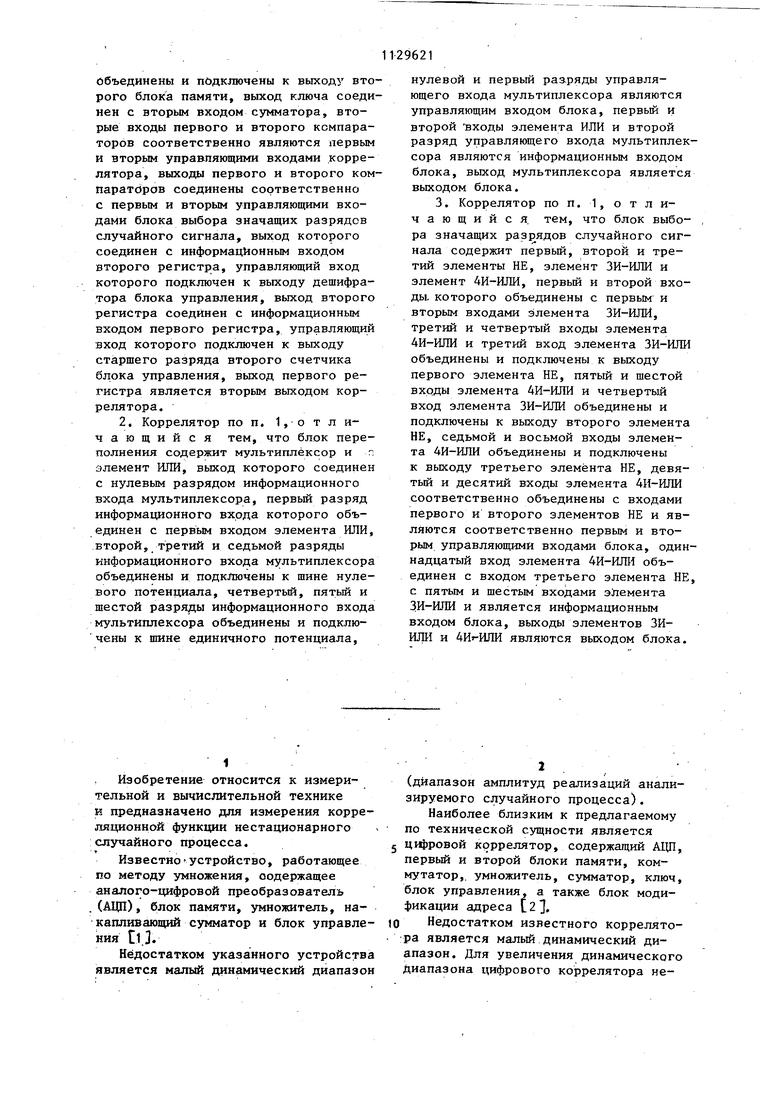

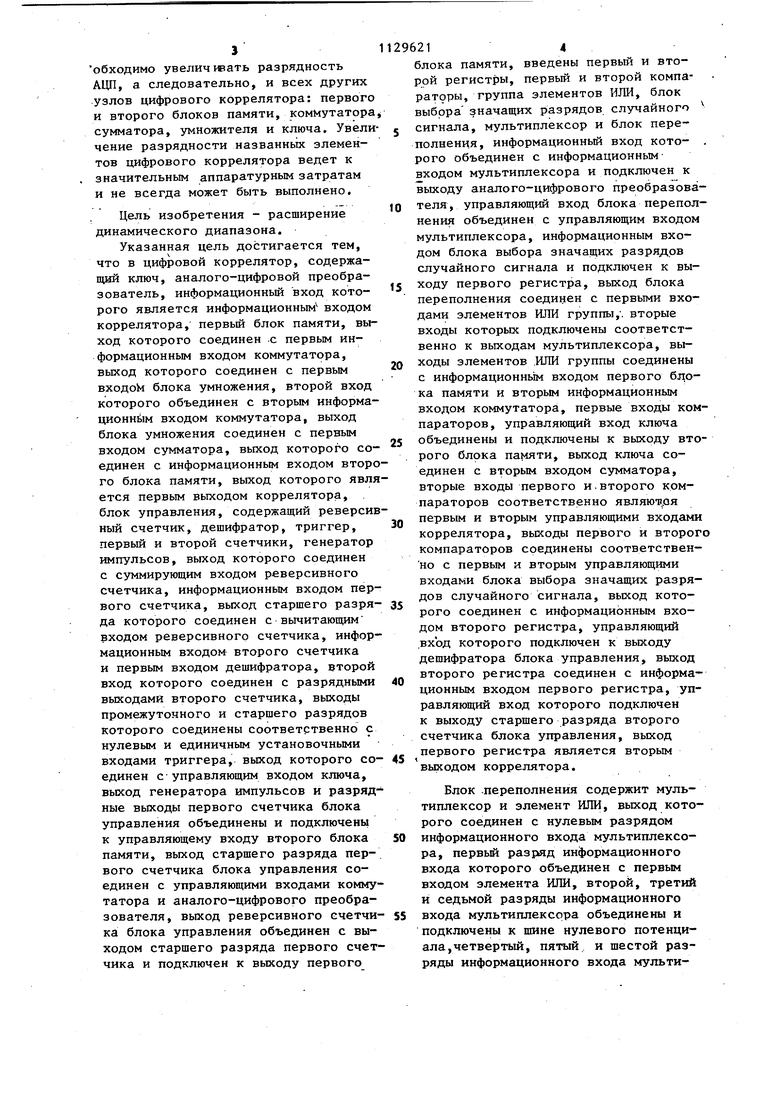

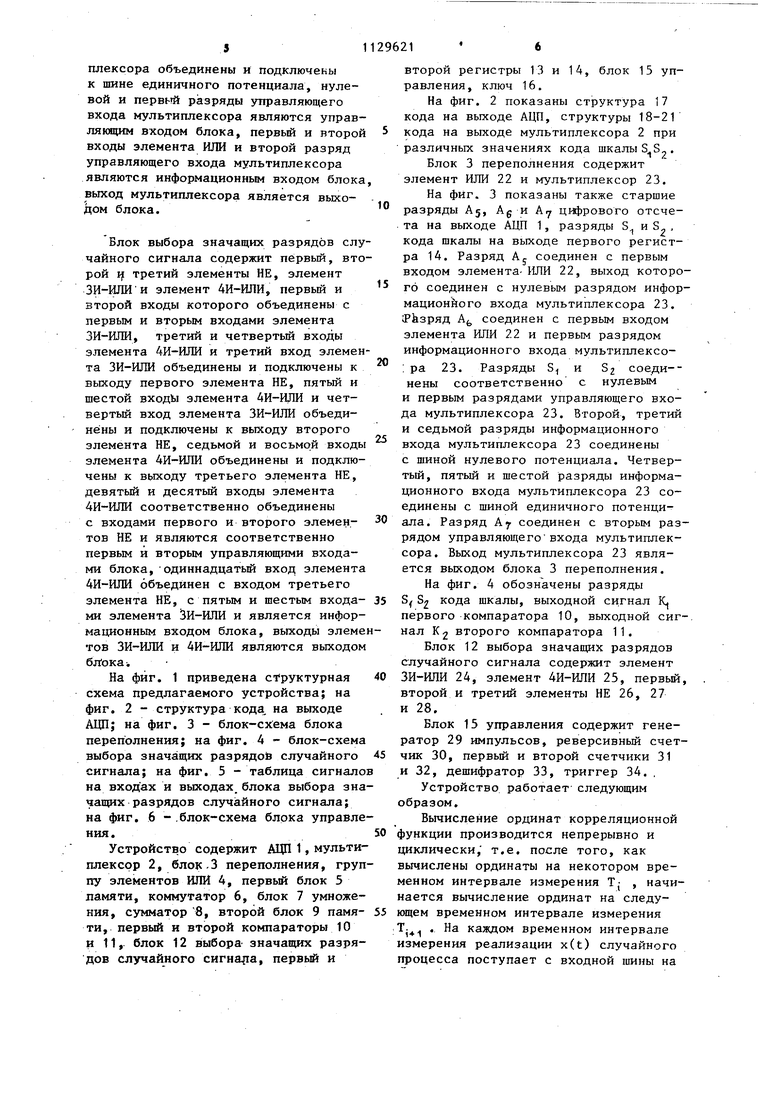

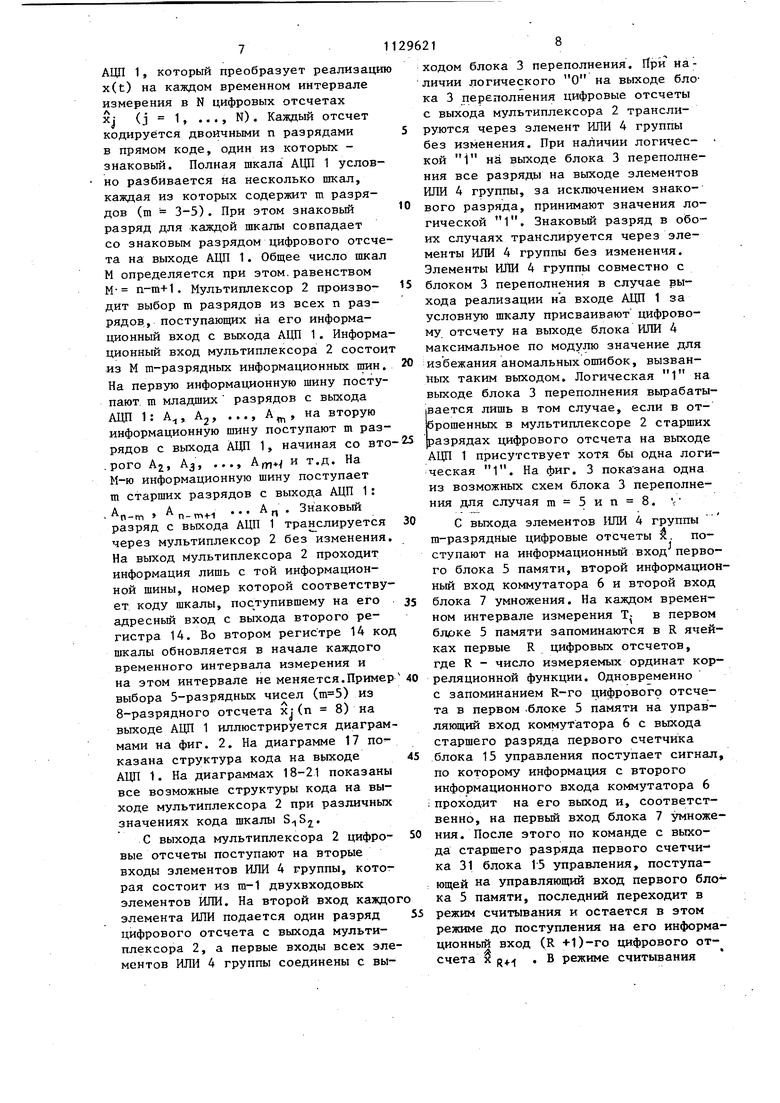

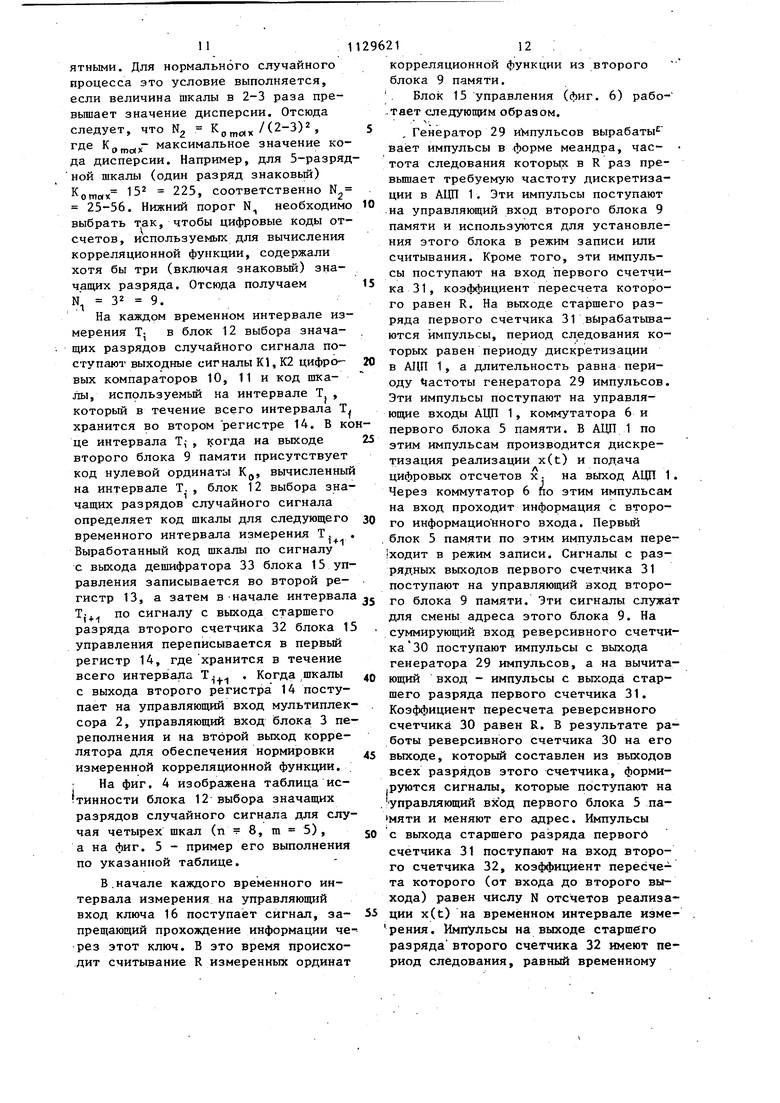

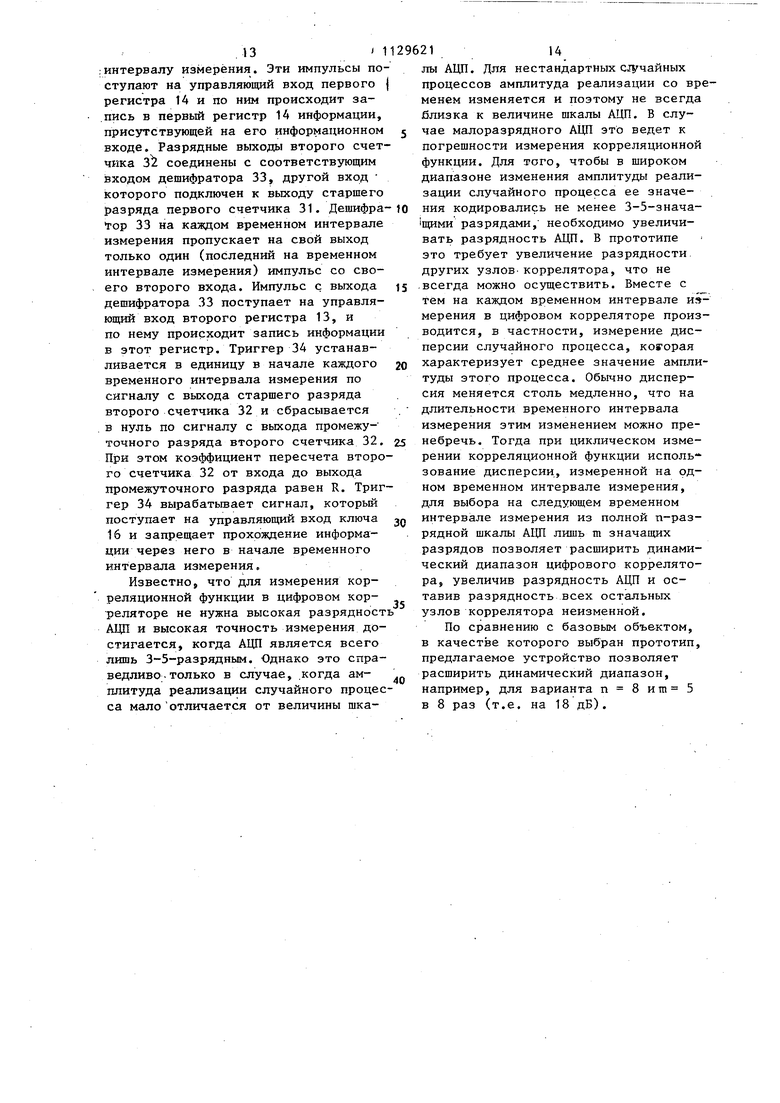

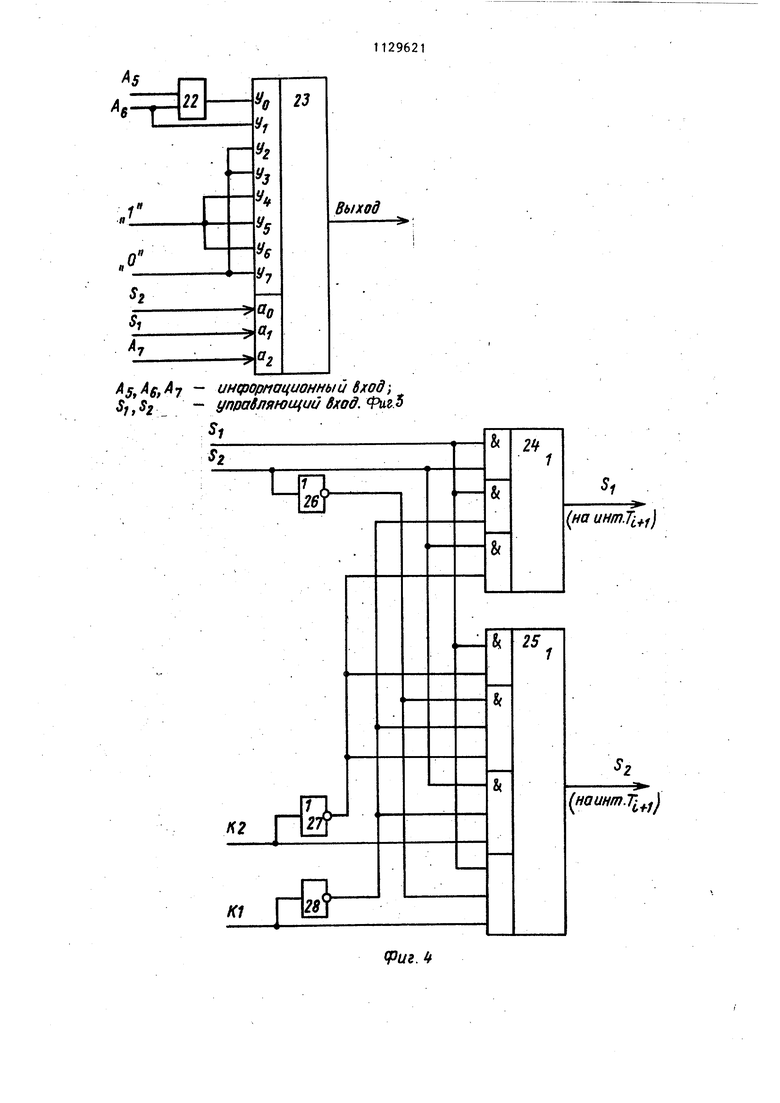

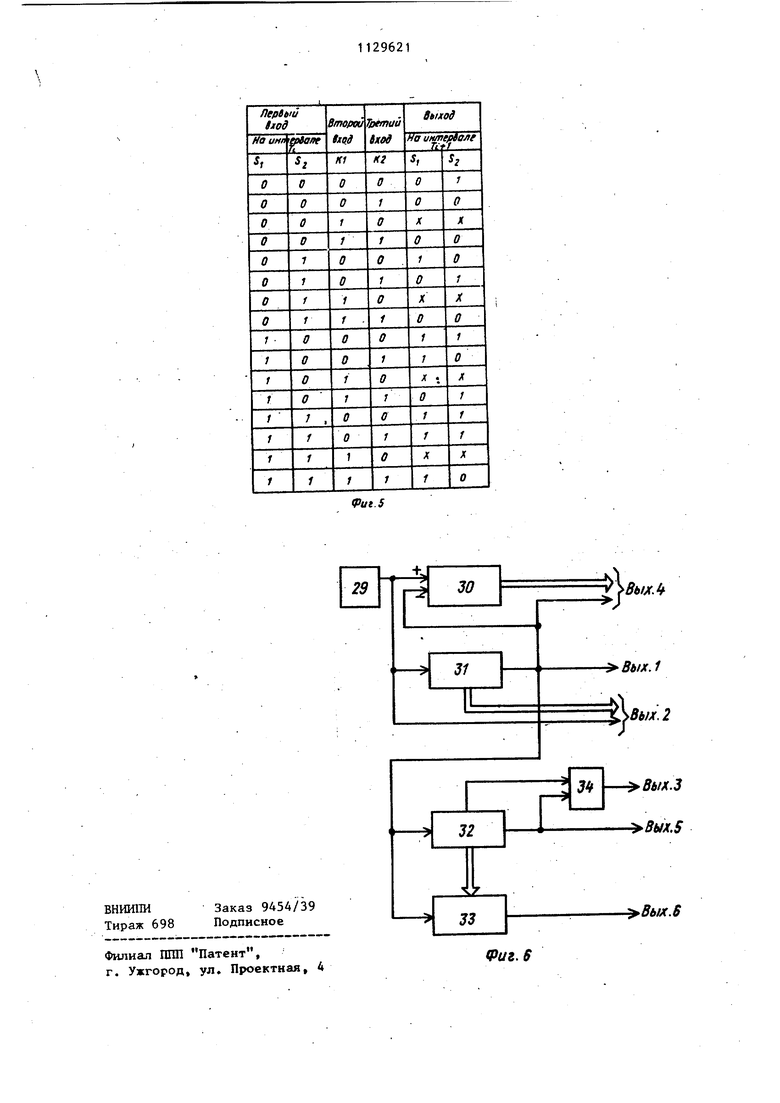

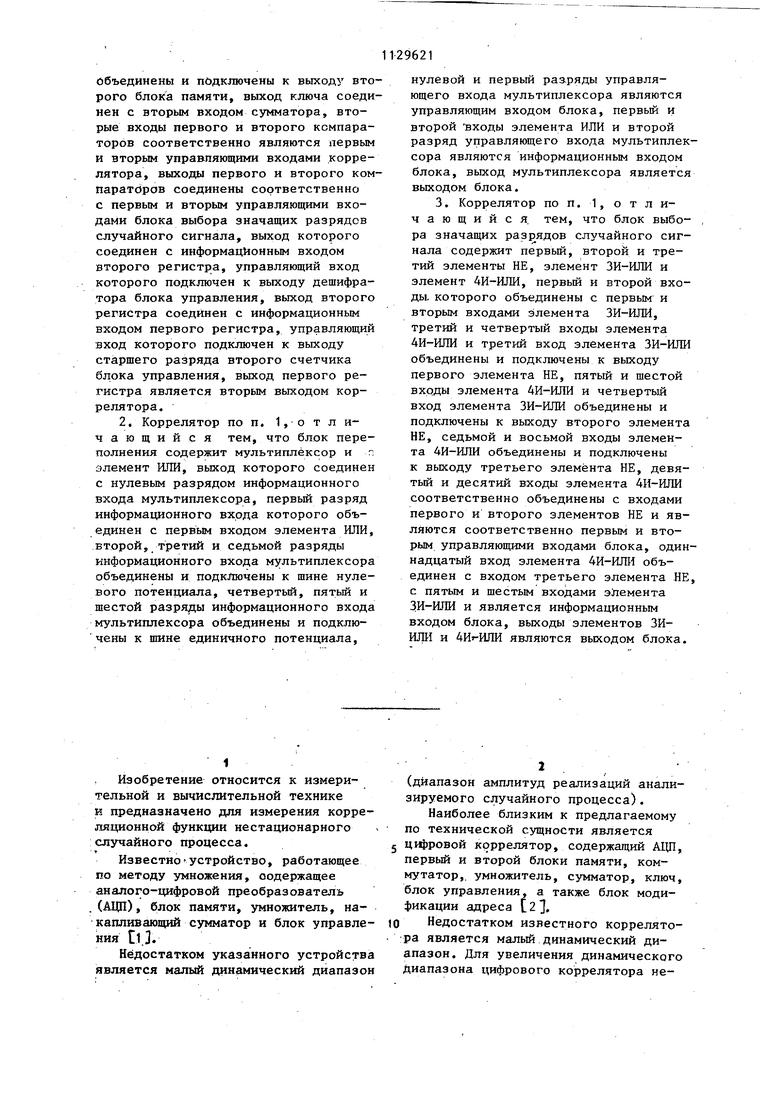

(О Недостатком известного коррелято:ра является мальй динамический диапазон. Для увеличения динамического Диапазона цифрового коррелятора неЭобходимо увелич рвать разрядность АЩ1, а следовательно, и всех других узлов цифрового коррелятора: первого и второго блоков памяти, коммутатора сумматора, умножителя и ключа. Увели чение разрядности названньЬс элементов цифрового коррелятора ведет к значительным аппаратурным затратам и не всегда может быть выполнено. Цель изобретения - расширение динамического диапазона. Указанная цель достигается тем, что в цифровой коррелятор, содержапщй ключ, аналого-цифровой преобразователь, информационный вход которого является информационным входом коррелятора, первый блок памяти, выход которого соединен с первым информационным входом коммутатора, выход которого соединен с первым входом блока умножения, второй вход которого объединен с вторым информа ционнбм входом коммутатора, выход блока умножения соединен с первым входом сумматора, выход которого со единен с информационным входом втор го блока памяти, выход которого явл ется первым выходом коррелятора, . блок управления, содержащий реверси ный счетчик, дешифратор, триггер, первый и второй счетчики, генератор импульсов, выход которого соединен с суммирующим входом реверсивного счетчика, информационным входом пер вого счетчика, выход старшего разря да которого соединен с вычитающим входом реверсивного счетчика, инфор мационным входом- второго счетчика и первым входом дешифратора, второй вход которого соединен с разрядными выходами второго счетчика, выходы промежуточного и старшего разрядов которого соединены соответственно с нулевым и единичным установочными входами триггера, выход которого со единен с управляющим входом ключа, выход генератора импульсов и разряд ные выходы первого счетчика блока управления объединены и подключены к управляющему входу второго блока памяти, выход старшего разряда первого счетчика блока управления соединен с управляющими входами комму татора и аналого-цифрового преобразователя, выход реверсивного счетчи ка блока управления объединен с выходом старшего разряда первого счет чика и подключен к выходу первого 214 блока памяти, введены первый и второй регистры, первый и второй компараторы, группа элементов ИЛИ, блок выбора значащих разрядов случайного сигнала, мультиплексор и блок переполнения, информационный вход кото- . рого объединен с информационнымвходом мультиплексора и подключен к выходу аналого-цифрового преобразова- теля, управляющий вход блока переполнения объединен с управляющим входом мультиплексора, информационным входом блока выбора значащих разрядов случайного сигнала и подключен к выходу первого регистра, выход блока переполнения соединен с первыми входами элементов ИЛИ группы,, вторые входы которых подключены соответственно к выходам мультиплексора, выходы элементов .ИЛИ группы соединены с информационньЫ входом первого блока памяти и вторым информационным входом коммутатора, первые входы компараторов, управляющий вход ключа объединены и подключены к выходу второго блока памяти, выход ключа соединен с вторым входом сумматора, вторые входы первого и.второго компараторов соответственно являютйя первым и вторым управляющими входами коррелятора, выходы первого и второго компараторов соединены соответствен- но с первым и вторым управляющими входами блока выбора значащих разрядов случайного сигнала, выход которого соединен с информационным входом второго регистра, управляющий вход которого подключен к выходу дешифратора блока управления, выход второго регистра соединен с информационным входом первого регистра, управляющий вход которого подключен к выходу старшего разряда второго счетчика блока управления, выход первого регистра является вторым вькодом коррелятора. Блок .переполнения содержит мультиплексор и элемент ИЛИ, выход которого соединен с нулевым разрядом информационного входа мультиплексора, первый разряд информационного входа которого объединен с первым входом элемента ИЛИ, второй, третий и седьмой разряды информационного входа мультиплексора объединены и подключены к шине нулевого потенциала, четвертый, пятый и шестой разряды информационного входа мультиплексора объединены и подключены к шине единичного потенциала, нулевой и первьтй разряды управляющего входа мультиплексора являются управлякидим входом блока, первый и второй входы элемента ИЛИ и второй разряд управляющего входа мультиплексора являются информационным входом блока выход мультиплексора является выходом блока. Блок выбора значащих разрядов слу чайного сигнала содержит первый, вто рой ц третий элементы НЕ, элемент ЗИ-ИЖ и элемент 4И-ИЛИ, первый и второй входы которого объединены с первым и вторым входами элемента ЗИ-ИЛИ, третий и четвертый входы элемента 4И-ИЛИ и третий вход элемен та ЗИ-ИЛИ объединены и подключены к выходу первого элемента НЕ, пятый и шестой входы элемента 4И-ИЛИ и четвертый вход элемента ЗИ-ИЛИ объединены и подключены к выходу второго элемента НЕ, седьмой и восьмой входы элемента 4И-ИЛИ объединены и подключены к выходу третьего элемента НЕ, девятый и десятый входы элемента 4И-ИЛИ соответственно объединены с входами первого и второго элементон НЕ и являются соответственно первым и вторым управляющими входами блока,одиннадцатый вход элемента 4И-ИЛИ объединен с входом третьего элемента НЕ, с пятым и шестым входами элемента ЗИ-ИЛИ и является информационным входом блока, выходы элеме тов ЗИ-ИЛИ и 4И-ШШ являются выходом блока На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - структура кода на выходе АЦП; на фиг. 3 - блок-схема блока переполнения; на фиг. 4 - блок-схема выбора значащих разрядов случайного сигнала; на фиг. 5 - таблица сигнало на входах и выходах,блока выбора зна чащих разрядов случайного сигнала; на фиг. 6 - .блок-схема блока управле ния. Устройство содержит АЦП 1, мультиплексор 2, блок-З переполнения, груп пу элементов ИЛИ 4, первый блок 5 памяти, коммутатор 6, блок 7 умножения, сумматор 8, второй блок 9 памяти, первый и второй компараторы 10 и 11, блок 12 выбора значащих разрядов случайного сигнала, первый и второй регистры 13 и 14, блок 15 управления, ключ 16. На фиг. 2 показаны структура 17 кода на выходе АЦП, структуры 18-21 кода на выходе мультиплексора 2 при различных значениях кода шкалы .. Блок 3 переполнения содержит элемент ИЛИ 22 и мультиплексор 23. На фиг. 3 показаны также старшие разряды Aj, Ag и А цифрового отсчета на выходе АЦП 1, разряды S и S , кода шкалы на выходе первого регистра 14. Разряд AJ соединен с первым входом элемента-ИЛИ 22, выход которого соединен с нулевьм разрядом информационйого входа мультиплексора 23. ЗЬзряд А соединен с первым входом элемента ИЛИ 22 и первым разрядом информационного входа мультиплексо: ра 23. Разряды S и Si соеди-нены соответственно с нулевым и первым разрядами управляющего входа мультиплексора 23. Второй, третий и седьмой разряды информационного входа мультиплексора 23 соединены с шиной нулевого потенциала. Четвертый, пятый и шестой разряды информационного входа мультиплексора 23 соединены с шиной единичного потенциала. Разряд А7 соединен с вторым разрядом управляющеговхода мультиплексора. Выход мультиплексора 23 является выходом блока 3 переполнения. На фиг. 4 обозначены разряды S| $2 кода шкалы, выходной сигнал К, первого компаратора 10, выходной сиг-, нал К2 второго компаратора 11. Блок 12 выбора значащих разрядов случайного сигнала содержит элемент ЗИ-ИЛИ 24, элемент 4И-ИЛИ 25, первый, второй и третий элементы НЕ 26, 27 и 28. Блок 15 управления содержит генератор 29 импульсов, реверсивный счетчик 30, первый и второй счетчики 31 и 32, дешифратор 33, триггер 34. , Устройство работает следующим образом. Вычисление ординат корреляционной ункции производится непрерывно и циклически, т.е. после того, как ычислены ординаты на некотором вреенном интервале измерения Т; , начиается вычисление ординат на следущем временном интервале измерения .. . На каждом временном интервале змерения реализации x(t) случайного процесса поступает с входной шины на АЦП 1, который преобразует реализаци x(t) на каждом временном интервале измерения в N цифровых отсчетах XJ (j 1 . N). Каждый отсчет кодируется двоичными п разрядами в прямом коде, один из которых знаковый. Полная шкала АЦП 1 условно разбивается на несколько шкал, каждая из которых содержит m разрядов (т 3-5). При этом знаковый разряд для каждой шкалы совпадает со знаковым разрядом цифрового отсче та на выходе АЦП 1. Общее число шкал М определяется при этом.равенством М- п-т+1, Мультиплексор 2 производит выбор m разрядов из всех п разрядов, поступающих на его информационный вход с выхода АЦП 1. Информа ционный вход мультиплексора 2 состои из М т-разрядных информационных пган На первую информационную шину посту пают m младших разрядов с выхода АЦП 1: А, АЗ, ..., А , на вторую информационную шину поступают m раз рядов с выхода АЦП 1, начиная со вт . рого А, АЗ, ... тЧ R- На М-ю информационную шину поступает m старших разрядов с выхода АЦП 1: А„ , , ... АП . Знаковый разряд с выхода АЦП 1 транслируется через мультиплексор 2 без изменения На выход мультиплексора 2 проходит информация лишь с той информационной шины, номер которой соответству ет коду шкалы, поступившему на его адресный вход с выхода второго регистра 14. Во втором регистре 14 ко шкалы обновляется в начале каждого временного интервала измерения и на этом интервале не меняется.Приме выбора 5-разрядных чисел () из 8-разрядного отсчета х;(п 8) на выходе АЦП 1 иллюстрируется диаграм мами на фиг. 2. На диаграмме 17 показана структура кода на вьтходе АЦП 1. На диаграммах 18-21 показаны все возможные структуры кода на выходе мультиплексора 2 при различных значениях кода шкалы . С выхода мультиплексора 2 цифровые отсчеты поступают на вторые входы элементов ИЛИ 4 группы, которая состоит из т-1 двухвходовых элементов ШШ. На второй вход каждо элемента ИЛИ подается один разряд цифрового отсчета с выхода мультиплексора 2, а первые входы всех эле ментов ИЛИ 4 группы соединены с вы218ходом блока 3 переполнения. При на личии логического О на выходе блока 3 переполнения цифровые отсчеты с выхода мультиплексора 2 транслируются через элемент ИЛИ 4 группы без изменения. При наличии логичес- кой 1 на выходе блока 3 переполнения все разряды на выходе элементов ИЛИ 4 группы, за исключением знакового разряда, принимают значения логической 1. Знаковый разряд в обоих случаях транслируется через элементы ИЛИ 4 группы без изменения. Элементы ИЛИ 4 группы совместно с блоком 3 переполнения в случае выхода реализации на входе АЦП 1 за условную шкалу присваивают цифровому отсчету на выходе блока ИЛИ 4 максимальное по модулю значение для избежания аномальных ошибок, вызванных таким выходом. Логическая 1 на выходе блока 3 переполнения вырабатывается лишь в том случае, если в отброшенных в мультиплексоре 2 старших разрядах цифрового отсчета на выходе АЦП 1 присутствует хотя бы одна логическая 1. На фиг. 3 показана одна из возможных схем блока 3 переполнения для случая m 5 и п 8. V С выхода элементов ИЛИ 4 группы го-разрядные цифровые отсчеты и. поступают на информационный вход первого блока 5 памяти, второй информационный вход коммутатора 6 и второй вход блока 7 умножения. На каждом временном интервале измерения Т- в первом бл(оке 5 памяти запоминаются в R ячейках первые R цифровых отсчетов, где R - число измеряемых ординат корреляционной функции. Одновременно с запоминанием R-ro цифрового отсчета в первом .блоке 5 памяти на управляющий вход коммутатора 6 с выхода старшего разряда первого счетчика блока 15 управления поступает сигнал, по которому информация с второго информационного входа коммутатора 6 проходит на его выход и, соответственно, на первый вход блока 7 умножения. После этого по команде с выхода старшего разряда первого счетчика 31 блока 15 управления, поступающей на управляющий вход первого бло ка 5 памяти, последний переходит в режим считывания и остается в этом режиме до поступления на его информационный вход (R +1)-го цифрового отсчета X g4 . В режиме считывания на управляняций вход первого блока 5 памяти поступают адресные сигналы с разрядных выходов реверсивного счетчика 30 блока управления 15, по которым на выходе этого блока последовательно во времени появляются запомненные цифровые отсчеты х , , х . Эти цифровые отсчеты транслируются через первьй информационный вход коммутатора 6 на его выход и попадают на первый вход блока 7 умножения, В результате на выходе блока 7 умножения последовател проидведеемени появляются в л S 1 R R - R R-1 которые поступают на первый вход сумматора 8. На второй вход сумматора 8 за это время ничего не поступает, потому что на управляющий вход ключа 16 с выхода триггера 34 блока 15 управления в это время поступает сигнал, по которому запрещается прохождение информации с информационного входа ключа 16 на его выход. Поэтому полученные произведения запоми наются поочередно в R ячейках второго блока 9 памяти. После прихода (R + 1)-го цифрового отсчета с выхода элементов ИЛИ 4 группы этот цифровой отсчет запоминается в первом блоке 5 памяти на ме те первого цифрового отсчета х . Одновременно х g, поступает на первый вход блока 7 умножения непосредственно, а на второй вход - через второй информационный вход коммутатора 6, Произведение с выхода блока 7 умножения поступает на первый вход сумматора 8, а на второй, вход сумматора 8 с выхода второго блока 9 памяти в это же время поступает запомненное ранее произведение х х , Сумма этих произведений с выхода сумматора 8 запоминается во втором блоке 9 памяти в той же ячейке, где хранилось произведение х х, . После этого . первьй блок 5 памятипо сигналу с выхода старшего разряда счетчика 31 . блока 15 управления переходит в режим считывания. На выходе первого блока 5 памяти последовательно во времени появляются цифровые отсчеты в следующей последовательности: х ц Эти цифровые отсчеты через первый информационный вход коммутатора 6 поступают на вто рой вход блока 7 умножения. В рёзул 2110 тате на выходе блока 7 умножения последовательно во времени появляют;ся произведения , х х j , ... ло.хХ„. Каждое из этих произведений R+1 в сумматоре 8 с одним суммируется из запомненных ранее произведений Л « R iПолученные суммы запоминаются во втором блоке 9 памяти, Затем на выход элементов ИЛИ 4 группы поступает цифровой отсчет который запоминается в первом блоке 5 памяти уже на месте цифрового отсчета х, и все вычислительные операции в первом блоке 5 памяти, коммутаторе 6, блоке 7 умножения, сумматоре 8 и втором блоке 9 памяти повторяются и т.д. Таким образом, к концу временного интервала измерения Tj во втором бпбке 9 памяти в каждой из ячеек будет накоплена сумма N. p 0,...,R-1 которая после деления на число слагаемых N - R + 1 будет представлять собой измеренное значение Р-й ординаты корреляционной функции на временном интервале измерения Т-. Вычисленные ординаты Кр с выхода второго блока 9 памяти йоступают на первый выход коррелятора. После вычисления величины Kg, которая пропорциональна дисперсии анализируемого случайного процесса, . эта величина с выхода второго блока 9 памяти поступает на первые входы компараторов 10 и 11, в каждом из которых установлены различные пороги срабатывания N (нижний) и N (верхний), причем NJ N-, В зависимости от соотношения между К, N и N2 блок 12 выбора значащих разрядов случайного сигнала воспринимает выходные сигналы К1 и К2 компараторов 10 и 11, как одну из следующих команд: К1 О, К2 О (если К, N) - код шкалы увеличить на единицу; К1 0, К2 1 (если N - KjjiN) - код шкалы оставить без изменения; К1 1, К2 1 (если (Кр N ) - код шкалы уменьшить на единицу. Поясним выбор порогов срабатываНИЯ N и N цифровых компараторов 10 И 11, Верхний порог Ng необходимо выбрать так, чтобы на временном интервале измерения выбросы реализации за пределы условной шкалы были маловероятными. Для нормального случайного процесса это условие выполняется, если величина шкалы в 2-3 раза превьппает значение дисперсии. Отсюда «2 к„,/(2-з) следует, где К„, - максимальное значение кода дисперсии. Например, для 5-разряд ной шкалы (один разряд знаковый) соответственно N - 15 225, 25-56. Нижний порог N необходимо выбрать так, чтобы цифровые коды отсчетов, используемых для вычисления корреляционной функции, содержали хотя бы три (включая знаковый) значащих разряда. Отсюда получаем N 3 9. На каждом временном интервале из мерения Т- в блок 12 выбора значащих разрядов случайного сигнала поступают выходные сигналы К1, К2 цифровых компараторов 10, 11 и код шкалы, используемьй на интервале Т , который в течение всего интервала Т хранится во втором регистре 14. В к це интервала Т , когда на выходе второго блока 9 памяти присутствует код нулевой ординаты К, вычисленны на интервале Т., блок 12 выбора зна чащих разрядов случайного сигнала определяет код шкалы для следующего временного интервала измерения Т. Выработанный код шкалы по сигналу с выхода дешифратора 33 блока 15 уп равления записывается во второй регистр 13, а затем в начале интервал Т- по сигналу с выхода старшего разряда второго счетчика 32 блока 1 управления переписывается в первый регистр 14, где хранится в течение всего интервала Т., . Когда шкалы с выхода второго регистра 14 поступает на управляющий вход мультиплек сора 2, управляющий вход блока 3 пе реполнения и на второй выход коррелятора для обеспечения нормировки измеренной корреляционной функции. На фиг. 4 изображена таблица истинности блока 12 выбора значащих разрядов случайного сигнала для слу чая четырех шкал (и 8, m 5), а на фиг. 5 - пример его выполнения по указанной таблице. В,начале каждого временного интервала измерения на управляющий вход ключа 16 поступает сигнал, запрещающий прохождение информации че рез этот ключ. В это время происходит считывание R измеренных ординат 2112 . корреляционной функции из второго блока 9 памяти. . Блок 15 управления (фиг. 6) рабо.тает следующим образом. Генератор 29 импульсов вырабаты ваёт импульсы в форме меандра, час- тота следования которь1Х в R раз превьш1ает требуемую частоту дискретизации в АЦП 1. Эти импульсы поступают на управляющий вход второго блока 9 памяти и используются для установления этого блока в режим записи или считывания. Кроме того, эти импульсы поступают на вход первого счетчика 31, коэффициент пересчета которого равен R. На выходе старшего разряда первого счетчика 31 вырабатьшаются импульсы, период следования которых равен периоду дискретизации в А1Щ 1, а длительность равна периоду Частоты генератора 29 импульсов. Эти импульсы поступают на управляющие входы АЦП 1, коммутатора 6 и первого блока 5 памяти. В АЦП 1 по этим импульсам производится дискретизация реализации x(t) и подача цифровых отсчетов х. на выход АЦП 1. Через коммутатор 6 по этим импульсам на вход проходит информация с второго информационного входа. Первый блок 5 памяти по этим импульсам пере ходит в режим записи. Сигналы с разрядных выходов первого счетчика 31 поступают на управляющий вход второго блока 9 памяти. Эти сигналы служат для смены адреса этого блока 9. На суммирующий вход реверсивного счетчика 30 поступают импульсы с выхода генератора 29 импульсов, а на вычитающий вход - импульсы с выхода старшего разряда первого счетчика 31. Коэффициент пересчета реверсивного счетчика 30 равен R. В результате работы реверсивного счетчика 30 на его выходе, который составлен из выходов всех разрядов этого счетчика, форми.руются сигналы, которые поступают на управляющий вхЪд первого блока 5 памяти и меняют его адрес. Импульсы с выхода старшего разряда первого счетчика 31 поступают на вход второго счетчика 32, коэффициент пересчета которого (от входа до второго выхода) равен числу N отсчетов реализации x(t) на временном интервале измерения. Импульсы на выходе старшего разряда второго счетчика 32 имеют период следования, равный временному .интервалу измерения. Эти импульсы по ступают на управляющий вход первого регистра 14 и по ним происходит запись в первый регистр 14 информации, присутствующей на его информационном входе. Разрядные выходы второго счет чика 32 соединены с соответствующим входом дешифратора 33, другой вход которого подключен к выходу старшего разряда первого счетчика 31. Дешифра Тор 33 на каждом временном интервале измерения пропускает на свой выход только один (последний на временном интервале измерения) импульс со своего второго входа. Импульс с выхода дешифратора 33 поступает на управляющий вход второго регистра 13, и по нему происходит запись информации в этот регистр. Триггер 34 устанавливается в единицу в начале каждого временного интервала измерения по сигналу с выхода старшего разряда второго счетчика 32 и сбрасывается в нуль по сигналу с выхода промежуточного разряда второго счетчика 32. При этом коэффициент пересчета второ го счетчика 32 от входа до выхода промежуточного разряда равен R. Триг гер 34 вырабатьшает сигнал, который поступает на управляющий вход ключа 16 и запрещает прохождение информации через него в начале временного интервала измерения. Известно, что для измерения корреляционной функции в цифровом корреляторе не нужна высокая разрядност АЦП и высокая точность измерения достигается, когда АЦП является всего лишь 3-5-разрядным. Однако это справедливо-только в случае, .когда амплитуда реализации случайного процес са малоотличается от величины шкалы АЦП. Для нестандартных с чайных процессов амплитуда реализации со временем изменяется и поэтому не всегда близка к величине шкалы АЦП. В случае малоразрядного АЦП это ведет к погрешности измерения корреляционной функции. Для того, чтобы в широком диапазоне изменения амплитуды реализации случайного процесса ее значения кодировались не менее 3-5-знача1щими разрядами, необходимо увеличивать разрядность АЦП. В прототипе это требует увеличение разрядности других узлов- коррелятора, что не .всегда можно осуществить. Вместе с тем на каждом временном интервале измерения в цифровом корреляторе производится, в частности, измерение дисперсии случайного процесса, коуорая характеризует среднее значение амплитуды этого процесса. Обычно дисперсия меняется столь медленно, что на длительности временного интервала измерения этим изменением можно пренебречь. Тогда при циклическом измерении корреляционной функции исполь зование дисперсии, измеренной на одном временном интервале измерения, для выбора на следующем временном интервале измерения из полной п-разрядной шкалы АЦП лишь m значащих разрядов позволяет расширить динамический диапазон цифрового коррелятора, увеличив разрядность АЦП и оставив разрядность всех остальных узлов коррелятора неизменной. По сравнению с базовым объектом, в качестве которого выбран прототип, предлагаемое устройство позволяет расширить динамический диапазон, например, для варианга п 8 ит 5 в 8 раз (т.е. на 18 дБ).

Bxoi

Знак

18

ig 3Haf( Ag AH I Ay A2 Ko9шкалы:Sj 2

AS AS Aif АЗ Код шкалы: 0

Знак

20

Знак

21

Bux.f litut.2

A2 A, I Код шкалы:

AS A If Код шкалы: Sj S 11

Фик.г

AS, AS, 7 UH(f)optiai4uoHHbiu Вход; Sj,S2 - управляющий Вход, f

Si

&

2

Si

(HauHmJi

k

25

K2

&

(HauHm.)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| КОРРЕЛЯТОР ДЛЯ ОПЕРАТИВНОГО АНАЛИЗА СЛУЧАЙНЫХ ПРОЦЕССОВ | 0 |

|

SU264789A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Составной прокатный валок | 1977 |

|

SU639619A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-15—Публикация

1983-08-17—Подача