второго одновибратора и к инверсному выходу элемента ИЛИ соответственно, а выход - к входу управления сдвигом кольцевого регистра сдвчга, вход второго одновибратора подключен к выходу управления сдвигом блока селекции запросов, выход сброса которого подключен к входам установки в

79364

О регистра кода выбора направлений и кольцевого регистра сдвига, выход младшего разряда мультиплексора подключен к входу синхронизации регистра кода выбора направлений и через Элемент задержки к входу синхронизации кольцевого регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРОВ В ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ, содержащее блок коммутации, информационные входывыходы которого являются информационными входами-выходами устройства, блок селекции запросов, входы которого являются входами запросов .устройства, первая, и вторая группы входов управления блока коммутации подключены к выходам готовности устройства и выходам запроса устройства соответственно, первую группу элементов И, регистр кода выбора направлений, выходы которого поразрядно подключены к первым входам элементов И первой группы, вторую группу элементов И И регистр адреса, отличающееся тем, что, с целью повышения пропускной способности устройства, оно содержит мультиплексор, информационные входы которого подключены к выходам блока коммутации, а выходы мультиплексора - к информационньм входам регистра кода выбора направлений, три схемы сравнения, входы первой группы первой и второй схемы сравнения подключены к выходам старших разрядов регистра кода выбора направлений, входы второй группы второй схемы сравнения и входы первой группы третьей схемы сравнения- подключены к выходам младших разрядов регистра кода выбора направления, входы второй группы первой и третьей схем сравнения подключены к выходам старших и младших разрядов регистра адреса соответственно, информационные входы регистра адреса являются адресными входами устройства, а вход синхронизации регистра адреса - входом синхронизации записи адреса уств ройства, шифратор, входы которого подключены к выходам Меньше и Равно схем сравнения, кольцевой регистр сдвига, информационные входы которого подключены к выходам шифратора, а выходы - к первьм входам элементов И второй группы и являются выходами запроса устройства., «Ч вторые входы элементов И второй СО О9 группы являются входами готовности устройства, элемент ИЛИ, входы которого подключены к выходам элементов И второй группы, первьй одновибратор, вход которого подключен к прямому выходу элемента ИЛИ, а выход - к вторым входам элементов И первой группы, выходы которых подключены к входам управления третьей группы блока коммутации, выходы запросов блока селекции запросов подключены к адресным входам мультиплексора и являются выходами готовности устройства, второй одновибратор, элемент И, первьй и второй входы которого подключены к выходу

1

Изобретение относится к вычислительной технике и может быть использовано для сопряжения процессоров в однородные вычислительные системы.

Цель изобретения - повышение пропускной способности устройства путем реализации адаптивного алгоритма коммутации устройства и организации прямой передачи сообщения по настроенному каналу обмена без запоминания данных в переприемных устройствах сопряжения,

На фиг. 1 и 2 представлена функциональная схема устройства для сопряжения процессоров в однородной вычислительной системе; на фиг. 3 функциональная схема блока селекции запросов; на фиг. 4 - функциональная схема блока коммутации.

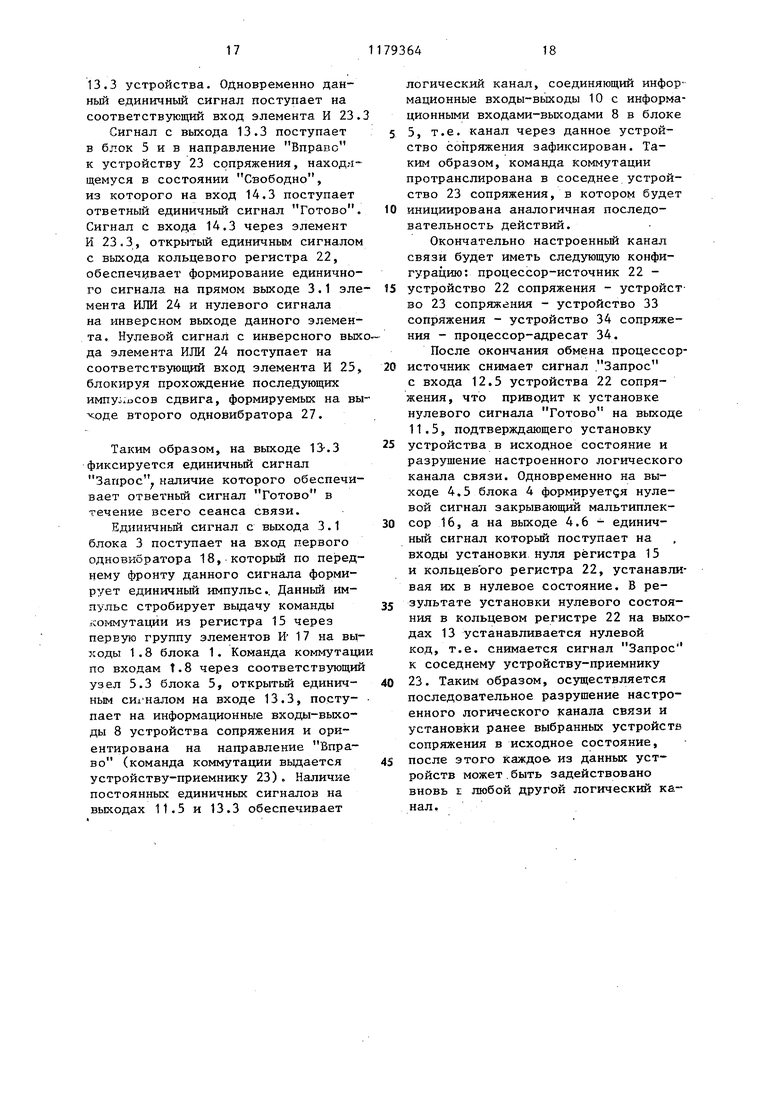

Устройство для сопряжения процессоров в однородной вычислительной системе содержит блок 1 приемавьщачи команд с информационными входами 1.1-1.5, выходами 1.6 старших разрядов, выходами 1.7 младших разрядов и выходами 1.8, блок 2 выбора направлений с адресньми входами 2.1 устройства и входом 2.2 синхронизации записи адреса устройства, блок 3 опроса с выходом 3.1, блок 4 селекции запросов с выходами 4.1-4.5 запросов, выходом 4.6 сброса и выходом 4.7 управления сдвигом, блок 5 коммутации, информационные входы-выходы 6-10 устройства, выходы 11 готовности устройства, входы 12 запросов устройства, выходы 13 запросов устройства и входы 14 готовности устройства.

Блок 1 содержит регистр 15 кода выбора направлений, мультиплексор 16 с выходом 16.1 младшего разряда.

первую группу элементов И 17 и первьй одновибратор 18.

Блок 2 состоит из регистра 19 адреса с выходами 19.1 и 19.2 старших и младших разрядов адреса соответственно, трех схем 20.1-20.3 сравнения и шифратора 21.

Блок 3 содержит кольцевой регистр 22 сдвига, вторую группу элементов И 23.1-23.5, элемент ИЛИ 24, элемент И 25, элемент 26 задержки и второй одновибратор 27.

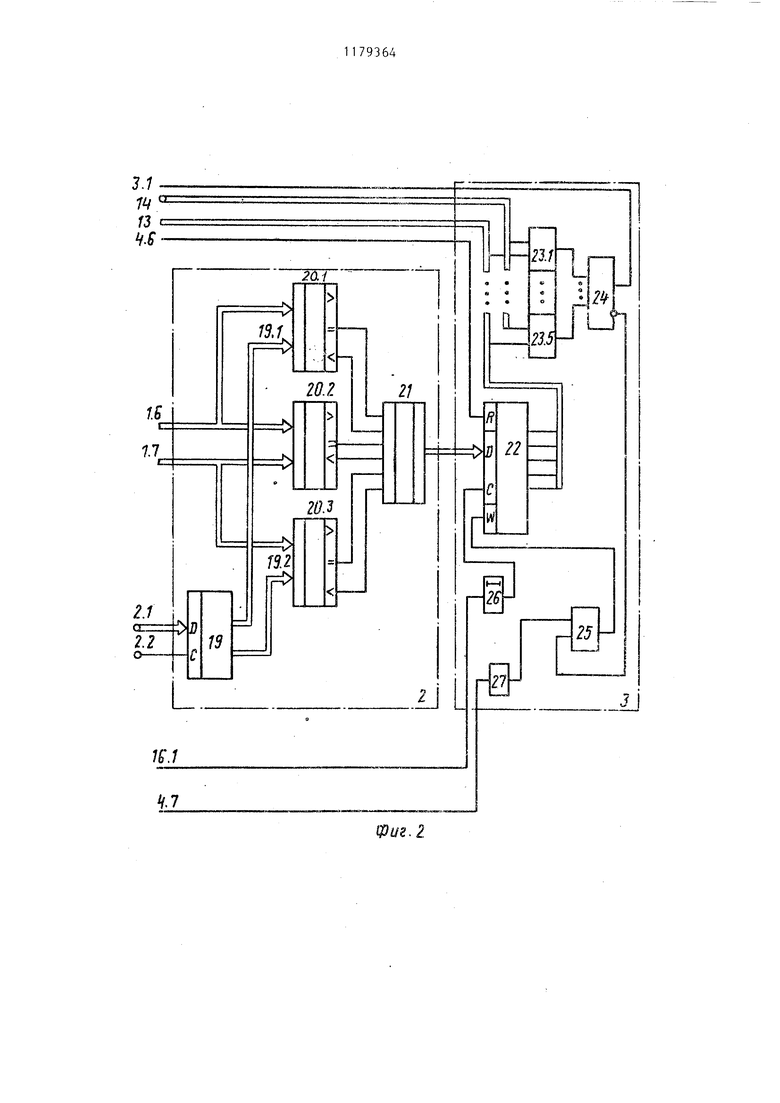

Блок 4 (фиг. 3) состоит из генератора 28 импульсов, дешифратора 29 направлений, счетчика 30 направлений, счетчика 31 опроса, группы элементов И 32.1-32.5, элемента ИЛИ 33, элементов ИЛИ-НЕ 34 и 35, элемента И 36 и элемент И-НЕ 37.

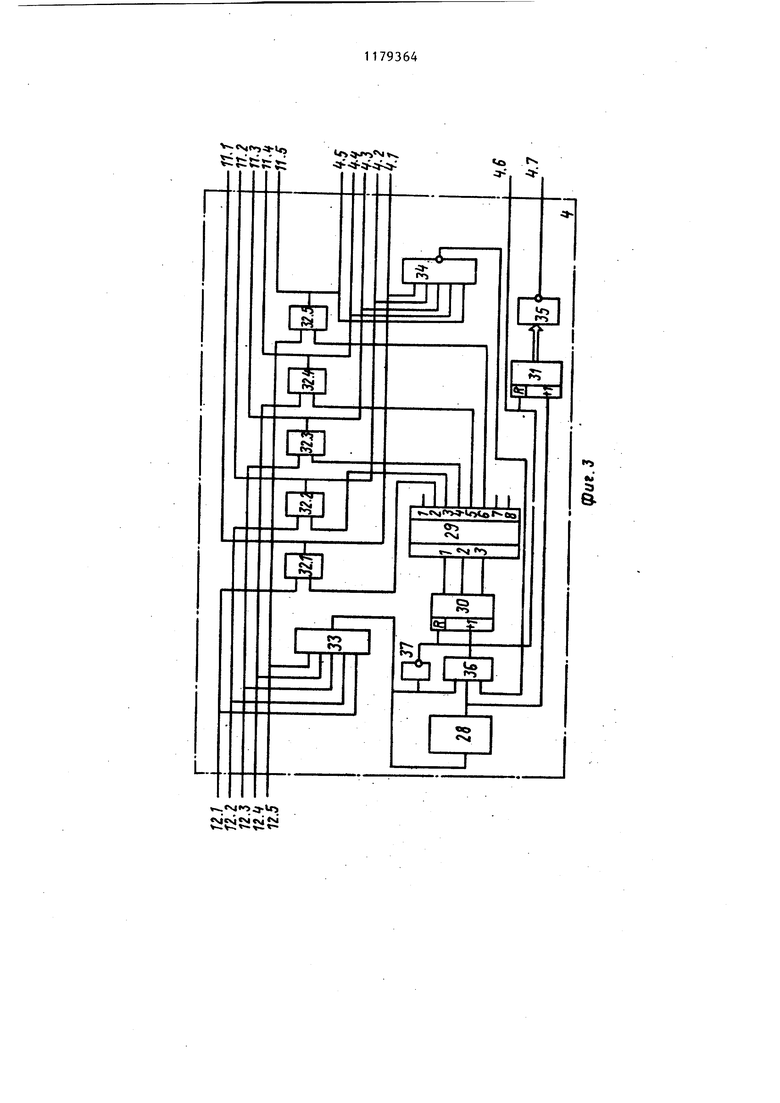

Блок 5 (фиг. 4) содержит группу узлов 5.1-5.5 коммутации с управляющими входами 11.1-11.5, 13.1-13. и 1.8, информационными входамивыходами 6-10 и информационными выходами 1.1-1.5, причем каждьй узе 5.1-5.5 состоит из групп элементов И 38.1-38.5 и 39.1-39.5 и группы элементов ИЛИ 40.1-40.5.

Применение устройства в однородной вычислительной системе, составленной в виде матрицы из п nj процессоров (где м, гл - количество, процессоров по строкам и столбцам матрицы соответственно).

Каждьй процессор системы подключен к одной из групп информационных входов-вькодов 6-10, к одному из входов 12 и к одному из выходов 14, причем процессор и устройство имеют одноименный адрес, соответствующий их расположению в матрице вычислительной системы. Адрес устройства

3

записывается в регистр 19 с адресным входом 2,1 устройства синхронизирующим сигналом, поступающим на вход 2.2 устройства, в период комплексирования технических средст вьиислительной системы.

Для удобства описания приняты обозначения возможных направлений коммутации через устройство: Вверх Вниз Вправо, Влево, Собственный процессор.

Процессор-источник - это процессор, который выдает адрес для настройки логического канала связи, процессор-адресат - это процессор, к которому должен быть настроен логический канал связи.

Первое устройство для сопряжения в цепочке устройств настроенного канала связи является соответственно устройством-источником, а последнее - устройством-адресатом. Кроме того, устройство-приемник - это устройство, к которому поступает команда с адресом процессора-адресата на данном этапе коммутации.

Буквой обозначены старшие разряды поступившего адресаj i - старшие разряды собственного адреса, j - младигие разряды поступившего адреса; Г - младшие разряды собственного адреса; ij , il - значения старших разрядов соответственно поступившего и собственного адресов, , Ljl значения младших разрядов соответственно поступившего и собственного адресов.

Устройство работает следуюищм образом.

В исходном состоянии на входах 12 и выходах 13 устройства установлены нулевые сигналы запроса к устройству сопряжения и от него к одному из устройств-приемников. На выходах 11 и входах 14 устройства установлены нулевые сигналы готовности. Регистр 15, кольцевой рег,л.1тр 22 и счетчики 30 и 31 установлены в нулевое состояние.

При поступлении на одну из групп информационных входов-выходов 6-10 команды коммутации, которая транслируется через блок 5 на соОтветствуЮ1цие информационные входы мультиплексора 16, формируется единичный сигнал на соответствующем выходе 4.1-4.5, стробирующий передачу команды коммутации через мультиплек793644

сор 16 на информационные входы регистра 15. Запись команды коммутации в регистр 15 осуществляется младшим разрядом команды, который 5 поступает на вход синхронизац1П1 регистра 15.

Команда коммутации имеет следующую структуру. Младший разряд команды коммутации является битом 0 синхронизации, следующие m младших разрядов - 1 - полем команды, а оставшиеся m старших разрядов (-полем команды. С выхода регистра 15 команда коммутации поступает 5 на входы схем 20 сравнения, где сравнивается с собственным адресом устройства. Схема 20.2 сравнения предназначена для сравнения старших л разрядов собственного адреса со старшими ГЦ разрядами приня-. того адреса, схема 20.1 сравнения для сравнения ст1рших и младш;их vn разрядов принятого адреса между собой, схема 20.3 сравнения - для сравнения младших m разрядов собственного адреса с младшими m разрядами принятого адреса коммутации. В результате анализа поступивших на вход кодов каждая из схем 20.120.3 сравнения вырабатывает один из трех признаков Меньше, Равно или Больше.

Шифратор 21 формирует коды возможных направлений коммутации и работает под управлением признаков Равно и Меньше, поступающих с соответствующих выходов схем 20.1-20.3 сравнения (признак Больше не используется из-за избыточности полного набора признаков).

Реализуемые шифратором 21 функции имеют следующий вид:

5

, X,V,

ij.XjXj + X,Xiy4 2 5 ;

14 (г z

ij Х,зХс i

6 ,,Х4Х

,Х,Хэ -I- XjXjX s i

1а Х5Хб4Х45 е-1-Х2,УбХ;t, XiX,jX6;

, - Xg X , i

,4 x,y 4 х,Уб.., где X, , и у. Хэ и х сигналы с выходов Равно и Меньш схем 20.1-20.3 сравнения соответственно, Исходя из зависимости значения выходов шифратора 21 от состояний его входов, характеризующих направ ления коммутации, формируемьй на выходах шифратора 21 код содержит три поля по пять разрядов. Каждое поле содержит унитарньй код, едини ное значение в соответствующем раз ряде которого однозначно указывает на направление коммутации. В зависимости от адреса процессора-адресата, поступающего в какое-либо переприемное устройство сопряжения на этапе настройки логического канала связи, и собственного адреса устройства возмож ны три варианта построения канала связи. 1.Код адреса процессора-адреса та, поступивший на входы 1.6 и. 1.7 блока 2, совпадает с кодом адреса устройства-приемника, хранящимся в регистре 19. Следовательно, команд настройки поступила в устройствоадресат, которое непосредственно сопряжено с требуемым процессоромадресатом, и срабатывается один унитарный пятиразрядньй код на выходах шифратора 21, указывающий направление к Собственному процес сору. При этом конкретное значение кода на группе выходов блока 2 имеет согласно системе (1) следу щий вид: 00001.0000 0000, 2.Совпадают либо -поля, либо j-поля адресов. В этом случае возможны следующиа ситуации: -если предлагаемое устройство находится в одной строке с процессором-адресатом 3 С . то выбор направления канала связи зави11сит от сравнения j и j разрядов адресов. Пусть Это оз чает, что процессор-адресат находи ся в строке левее устройства (ситуация 2-А1). Выбирается направлен Влево. На первых пяти выходах шифратора 21 устанавливается код 10000 (Влево); -если LJ} с Lj то процессор адресат находится правее предлагае мого устройства (ситуация 2-А2). Выбирается направление Вправо. На первых пяти выходах шифратора 21 устанавливается код 00100 (Вправо) -если занято основное направление по строке, предусмотрены два обходных направления: на- одну строку в матрице Вверх или на одну строку Вниз от строки, в которой находится устройство-приемник. Соответственно, на остальных выходах шифратора 21 устанавливается код 01000 00010 (Вверх, Вниз); - если устройство находится в одном столбце с процессором-адресатом j то выбор направления зависит от сравнения i и i разрядов адресов, -если процессор-адресат находится в столбце вьш1е устройства-приемника , t i3 «1 , то выбирается на правление Вверх (ситуация 2-В1), На первьк пяти выходах шифратора 21 устанавливается код 01000 (Вверх); -если C lftO J т.е. процессор-адресат находится ниже устройства-приемника (ситуация 2-В2). На первых пяти выходах шифратора 21 устанавливается код 00010 (Вниз); -если занято основное направление по столбцу, предусмотрены два обходных: на один столбец Влево, на один столбец Вправо. На 6-15 выходах шифратора 21 устанавливается код 10000 00100 (Влево, Вправо). 3. Поля адресов процессора-адресата и устройства-приемника не совпадают. В этом случае направление выбирается по методу наименьших квадратов. В данном варианте возможны следующие ситуации: -ситуация 3-А1 (аналогична ситуации 2-А1) , j 7 t j J т.е. процессор-адресат находится левее устройства. Выбирается направление Влево, код 10000, -ситуация 3-А2 (аналогична ситуации 2-А2) , ,T.e. процессор-адресат находится правее устройства. Вырабатывается направление Вправо, код.00100, -ситуация 3-В1 (аналогична ситуации 2-В1), C lj ® ро цессор-адресат расположен вьш1е

устройства-приемника. Выбирается направление Вверх, код 01000.

-ситуация 3-В2 (аналогична ситуации 2-В2) -П - J т.е. означает, что процессор-адресат находится ниже устройства сопряжения. Выбирается направление Вниз, код 00010.

Установка сформированных кодов на соответствующих выходах шифратора 21 происходит в зависимости от результатов сравнения разницы значаний |Ci -t;ri и irn-Cjil

между собой.

Яри этом возможны следующие случаи, соответствующие комбинациям ситуаций 3-А1, 3-А2 и 3-В1, 3-В21

-ситуация 3-А1/В 1 )

и , причем 1 Г i1-Г-П 1

1г-,-|-| ГТ|. 11-44 ujji

Ij-T.e. число переприемных устройств сопряжения при движении по строке, в которой находится устройство-приемник, меньше, чем при движении по столбцу матрицы соответствия. Поэтому на выходах шифратора 21 устанавливается код, соответствующий движению Влево, Вверх, Пустой цикл,

-ситуация 3-А1/В2, Jl tiJ , причем f t jl -) I

выходах шифратора 21 устанавливается код, соответствующий движению Влево, Вниз, Пустой цикл

-ситуагщя 3-A2/B1,j ti

и дЗ Qi , причем 1у ILil till . На выходахiшифратора 21 устанавливается код, соответствующий движению Вправо, Вверх

,11 Пустой цикл

21 устанавливается код, соответствующий движению Вправо, Вниз, Пустой

. - ситуация 3-В 1/А 1, 3-В2/А1, 3-В1/А2 и 3-В2/А2 аналогичны ситуациffi-s 3-А1/В1, 3-А1/В2, 3-А2/В1 и 3-А2/В2 соответственно, с той разницей, 4To|rn- n)ltt -Cill и, соответственно, на выходах 1-5 группы выходов преобразователя 21 формируется код Вверх (Вниз), а на выходах 6 -. 10 формируется код Влево BnpaBOJ соответственно.

Таким образом, метод наименьших квадратов предполагает, в первую очередь, достижение строки или столбца, на которых расположен согласно матрице соответствия процессор-адресат. В случае достижения данной строки или столбца выбор направления осуществляется согласно второму варианту, в первую очередь, по строке (по столбцу) до устройства-адресата, а затем в соответствии с первым вариантом- к Собственному процессору. Если в результате работы устройства по напрайлениям, полученным согласно второму варианту, основное направление занято и канал настроен по дополнительному направлению, следующее устройство-приемник работает согласно третьему варианту - по методу наименьших квадратов.

Таким образом, блок 2 является комбинационной схемой и изменение исходньк (нулевых) выходных сигналов группы выходов -происходит в том случае, если поступает отличньй от нуля код адреса на входы 1.6 и 1.7.

Блок 3 опроса предназначен для хранения кодов направлений и их последовательного опроса посредство формирования сигнала Запрос на входе запросов соответствующего устройства-приемника .

Кольцевой регистр 22 предназначен для приема кода с выходов блока 2, организации последовательности циклов опроса возможных направлений коммутации и их хранения до момента полного окончания процесса обмена по настроенному каналу связи между процессором-источником и процессором-адресатом. Занесение кодов направлений с выходов блока 2 стробируется управляющим сигналом с входа 16.1 через элемент 26 задержки. Сдвиг пятиразрядных унитарных кодов направлений инициируется сигналом с выхода 4.7 через второй одновибратор 27, формирующий еди- ничньй положительньй импульс по переднему фронту сигнала, и элемент И 25, открытый в исходном состоянии единичным сигналом с инверсного выхода элемента ИЛИ 24. При этом в кольцевом регистре 22 осзтцествляется циклический сдвиг. Смена значени

в соответствующих разрядах регистра 22 осуществляется в следующем порядке: 1-5, 6-10, 6-10, 11-15, 11-15, 1-5. На выходах кольцевого регистра 22 в каждом цикле опроса установлен код, соответствующий разрядам 1-5, что позволяет осуществлять опрос: одного текущего направления в каждом цикле. Унитарный код с вьпсодов кольцевого регистра 22 поступает на выходы 13 устройства. Единичный сигнал i -го (.5) разряда данного кода является сигналом Запрос и инициирует опрос выбранного i -го направления устройстваприемника. Одновременно данный сигнал поступает на вход элемента И 23.1, Если устройство-приемник находится в состоянии Занято, то элемент И 23.i остается в закрытом состоянии, так как нулевой сигнал на выходе 14.i устройства от данного направления (устройстваприемника) осается неизменным.. В данном случае на выходах всех элементов И 23.1-23.5 присутствуют нулевые сигналы, что обеспечивает наличие единичного сигнала на инверсном выходе элемента ИЛИ 24, которьй поддерживает элемент И 25 в открытом состоянии. Поэтому очередной управляющий сигнал, поступающий на вход 4.7, приводит к циклическому сдвигу кодов в кольцевом регистре 22, т.е. опрашивается следующее возможное направление. Опрос продолжается до тех пор, пока какое-либо из возможных направлений устройства-приемника не перейдет в состояние Свободно и в текущем цикле опроса поступит единичньй сигнал Готово на соответствующий вход 14.(. В данном случае на выходе элемента И 23.1 присутствует единичньй сигнал, которьй приводит к формированию нулевого сигнала на инверсном выходе элемента ИЛИ 24, которьй закрывает элемент И 25, запрещая последующие сдвиги кодов и кольцевом регистре 22, следовательно, опрос других направлений. Одновременно единичньй сигнал с прямого выхода элемента ИЛИ 24 поступает на выход 3.1,инициируяпередь.чу командыко мутации устройству-приемникуиз блока

В блоке 4 в исходном состоянии сигналы на выходах 12.1-12.5 отсутствуют, что обеспечивает наличие нулевого на выходе элемента ИЛИ 33. Данньй сигнал поддерживает генератор 28 в состоянии Останов, когда тактовые импульсы на его выходе не вьфабатываются. Одновременно он обеспечивает наличие единичного сигнала на выходе элемента И-НЕ 37, который поступает на входы асинхронной установки нулевого состояния счетчиков 30 и 31, поддерживая их в нулевом состоянии, а та1сже поступает на выход 4.6 блока 4. Нулевой код с группы выходов счетчика 30 поступает на группу входов дешифратора 29, обеспечивая формирование единичного сигнала на его нулевом выходе (не используется) . Нулевой код с группы выходов счетчика 31 поступает на группу входов элемента И-НЕ 35, обеспечивая наличие постоянного единичного сигнала на выходе 4.7 блока в исходном состоянии.

На входах всех элементов И 32.1- 32.5 присутствуют нулевые сигналы с соответствующих входов 12.1-12.5 и выходов дешифратора 29, что обеспечивает наличие нулевого сигнала на их выходах. Данные сигналы поступают на соответствующие входы элемента ИЛИ-НЕ 34, обеспечивая на его выходе и соответствующем входе элемента И 36 единичный сигнал.

При поступлении единичного сигнала Запрос на вход 12. (i 1.5) сигнал с выхода элемента ИЖ 33 осуществляет запуск генератора 28, поступает на соответствующий вход элемента И 36 и элемента И-НЕ 37 и формирует на выходе последнего нулевой сигнал. Импульсы с выхода генератора 28 герез элемент И 36 поступают на суммирующий вход счетчика 30, обеспечивая последовательное увеличение его состояния. При отсутствии установки в счетчике 30 1-го (i 1.5) состояния на i -м выходе дешифратора 29 формируется единичньй сигнал, который через элемент И 32. , открытьй единичным сигналом с выхода 12.i , поступает на выход 11.:i. Сигнал, поступающий на выход 11, i, является сигналом Готов и инициирует выдачу команды

коммутации из устройства, выставившего сигнал Запрос. Одновременно сигнал с выхода элемента И 32. J поступает на выход 4.i (« 1.5) блока 4 и на соответствующий вход элемента ИЛИ-ИЕ 34, на выходе которого формируется нулевой сигнал. Данный нулевой сигнал поступает на соответствующий вход элемента И 36 и блокирует прохождение импульсов с выхода генератора 28 через элемент И 36 на суммирующий вход счетчика 30 | состояние счетчика 30 i остается без изменения, поддерживая единичный сигнал на i -м выходе дешифратора 29 и через элемент И 32.i и на выходе ll.i. Таким образом, обеспечивается поддерживание настроенного логического канала связи в течение времени настройки последзтощик переприемных устройств сопряжения и непосредственного обмена данными через них.

Появление нулевого сигнала на входе асинхронной установки нулевого состояния счетчика 31 разрешает его последовательное увеличение на единицу под действием импульсов, поступакицих с выхода генератора 28 на суммирующий вход данного счетчика. Отличное от нулевого состояния счетчика обеспечивает через элемент ИЛИ-НЕ 35 наличие нулевого сигнала на выходе 4.7. Счетчик 31 является кольцевым и после поступления ( -г импульса на его суммирующий вход переходит в нулевое состояние, обеспечивая, формирование единичного сигнала на выходе 4.7. Таким образом, счетчик 31 и элемент ИЛИ-НЕ 35осуществляет деление входной последовательности импульсов от генератора 28 в последовательность импульсов сдвига с большим периодом следования.

При одновременном поступлении си налов Запрос, например, на входы 12.2 и 12.4 блока 4, единичный сигнал с выходов 12.2, 12.4 через элемент ИЛИ 33 запускает генератор 28, на выходе которого начинает формироваться последовательность импульсов. Одновременно данный сигнал через элемент И-НЕ 37 разблокирует нулевым сигналом счетчики 30 и 31. Импульсы с,выхода генератора 28 через элемент И 36 последовательно увеличивают состояние счетчика 30 на единицу.

Состояние 1 счетчика 30 обеспечивает формирование па первом выходе дешифратора 29 единичного сигнала, прохождение которого через элемент 32.1 блокируется нулевым сигналом с входа 12.1. Состояние 2 счетчика 30 обеспечивает формирование на втором выкоде дешифратора 29 единичного сигнала, который через элемент И 32.2 открываемьй единичны сигналом с входа 12.2, поступает на-ВХОДЫ 11.2 (в ответ на сигнал Запрос, поступивший от второго направления, в данное направление вьщан сигнал Готово, свгздетельствующий о том, что устройство находится в состоянии Свободно и готово к приему команды коммутации). Одновременно единичный сигнал с выхода элемента И 32.2 поступает на выход 4.2 и обес11ечивает формирование нулевого сигнала на выходе элемента 34 ИЛИ-НЕ, который блокирует прохождение импульсов с выхода генератора 28 через элемент И 36.

Дальнейшее увеличение состояний счетчика 30 заблокировано и выбора других сигналов Запрос не происходит, т.е. сигнал Запрос с входа 12.4 не принимается на обслуживание (вьщавшее данньй сигнал устройство через время сдвига снимет данный сигнал с входа 12.4). Единичный сигнал на входе 12.2. и выходах 11.2, 4.2 присутствует в течение всего сеанса обмена данными, на выходе 4.7 периодически формируется импульс сдвига.

Об окончании обмена данными свидетельствует окончание единичного, сигнала на входе 12.2. Нулевой сигнал с данного входа через элемент ИЛИ 33 вызывает останов генератора 28 и через элемент И-НЕ 37 приводит счетчики 30 и 31 в исходное состояние и поступает далее на выход 4,6 блока 4.

.« коммутации предназначен для логического соединения пары из групп 6-10 информационных входоввыходов между собой на время настройки логического канала и обмена по нему.

Количество разрядов каждого из информационного входов-выходов 6-10 равно и (в- 2т +1), где ( + 1) число разрядов команды коммутации. что обеспечивает возможность передачи команды настройки на этапе настройки логического канала связи, а также данных и сопутствующих им управляющих сигналов в процессе обмена между процессором-источником и процессором-адресатом. Причем мла ший разряд, используемьй при передаче команды коммутации, при передаче данных не используется. Группа 1, i (i 1,5) информационных выходов является (2nrj +1)-разряд ной и используется для передачи команды коммутации в блок 1 устройства с соответствующих информационных входов-выходов 6-10. Третья гру па входов 1.8 управлений блока 5 является (21т1 + 1)-разрядной и исполь зуется для выдачи команды коммутации из блока 1 устройства через соо ветс- зующий узел 5. i (i 1.5) на соответствующий информационные вход выходы 6-10 устройства. На вход 11.1 ( i 1.5) узла, 5. i .поступает сигнал Готово, который открывает группу элементов И 39.ч разрешая передачу команды коммутаци через данньй блок на выходы 1, i или передачу данных с соответствующих выходов блока 5 через узел 5. j ( j 51 i ,j 1 .5) на соответству ющую группу 6-10 входов-выходов. В данном слзгчае на входе 13.i установлен нулевой сигнал, который поддерживает группу элементов И 38.1 в закрытом состоянии (выходы элемен тов данного блока находятся в состо нии высокопо сопротивления и не ока зывают влияние на информацию, посту пающую на вход соответствзтощей груп пы элементов И 39.0. , Допустим, сигнал Запрос поступает от второго направления, данное устройство свободно и выдает ответньш единичный сигнал Готово в данное направление (на выход 11.2 В этом случае открывается группа элементов И 39.2 в узле 5.2. На группу 7 входов-выходов поступает команда коммутации и через группу элементов И 39.2 по выходам 1.2 передается в блок 1. Предположим, что первым возможным направлением, выраббтанным на основе анализа команды является четвертое направление и устройствоприемник в данном направлении свг бодно. в этом случае на выходе 13.4 устройства появляется единичный сигнал Запрос к устройствуприемнику четвертого направления. Данный сигнал одновременно открьшает группу элементов И 39.4 в узле 5.4. От устройства-приемника поступает единичньй сигнал Готово (на вход 14.4 блока 3), который инициирует стробирование. выдачи команды коммутации из блока 1 данного устройства через элемент ИЛИ 40.4 через группу элементов И 38.4 на информационные входы-выходы 9 устройства к устройству-приемнику . Команда коммутации через блоки 40 поступает на входы всех групп элементов И 38 узлов 5.1-5.5, однако ее прохождение через данные блоки блокируется нулевым сигналом на соответствующем входе 13. Нулевой сигнал на входе 11.4 поддерживает группу элементов И 39.4 в закрытом состоянии, что обеспечивает состояние высокого сопротивления входов элементов. В этом случае данные элементы не оказьшают влияния на передачу информации с выходов группы элементов И 38.4 на информационные входы-выходы 9, с которыми о«и объединены по схеме МОНТАЖНОЕ ИЛИ. Кроме того, наличие единичных сигналов на входах 11.2 и 13.4 создает, в частности, возможность передачи данных в процессе обмена между процессором-источником и процессоромадресатом по следующему логическому каналу: информационные входы-выходы 7 - группа элементов И 39.2 группа элементов ИЛИ 40.4 - группа элементов И 38.4 - информационные входы-выходы 9. В конце обмена на входах 11.2 и 13.4 устанавливается нулевой сигнал, который разрушает настроенньй логический канал связи. Аналогичным образом может быть соединена любая пара информационных входов-выходов 6-10. I В качестве примера адаптивной настройки логических каналов связи рассмотрим однородную вьиислительную систему в виде матрицы из N - Л-Ш процессоров и соответствующих им устройств сопряжения, при этом п 6 (количество процессоров в строке) и щ 4 (количество процессоров в столбце матрица имеет следующий над:

12

14

13

15

16 26 36 46

23 24 33 34 43 (44)

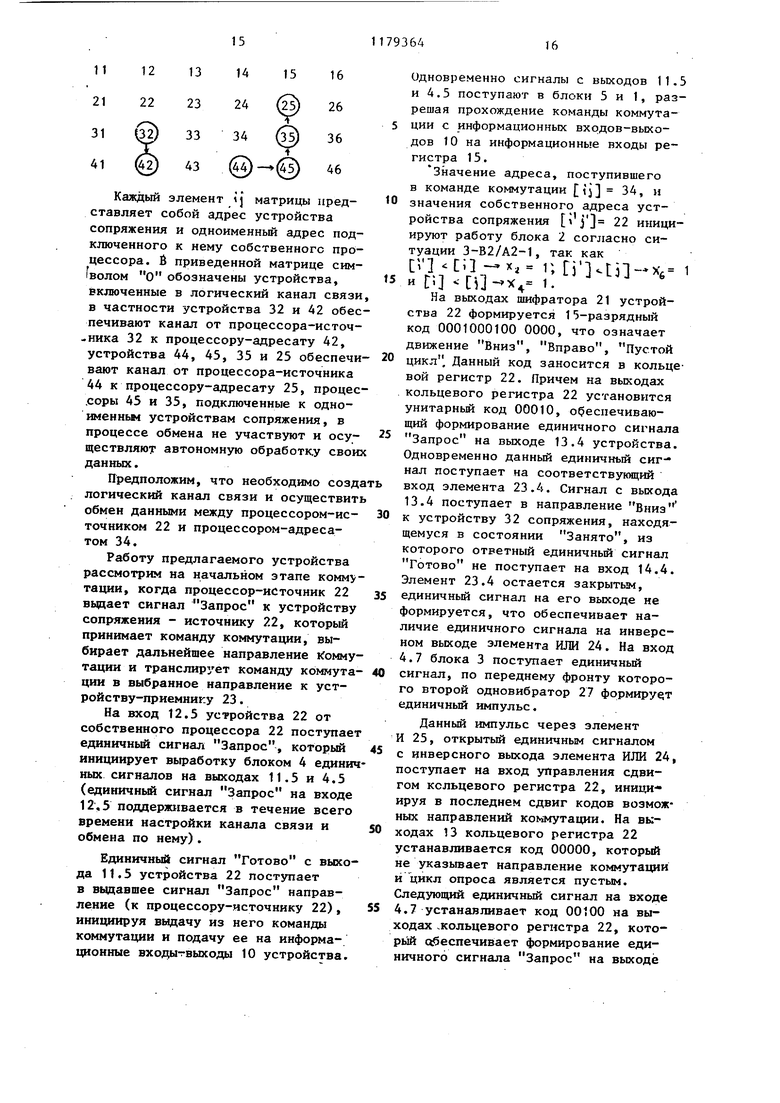

Каждый элемент tj матрицы представляет собой адрес устройства сопряжения и одноименный адрес подключенного к нему собственного процессора. В приведенной матрице сим волом о обозначены устройства, включенные в логический канал связи в частности устройства 32 и 42 обеспечивают канал от процессора-источ ника 32 к процессору-адресату 42, устройства 44, 45, 35 и 25 обеспечивают канал от процессора-источника 44 к процессору-адресату 25, процес.соры 45 и 35, подключенные к одноименньм устройствам сопряжения, в процессе обмена не участвуют и осуществляют автономную обработку своих данных.

Предположим, что необходимо созда логический канал связи и осуществить обмен данными между процессором-источником 22 и процессором-адресатом 34.

Работу предлагаемого устройства рассмотрим на начальном этапе коммутации, когда процессор-источник 22 вьщает сигнал Запрос к устройству сопряжения - источнику 22, который принимает команду коммутации, выбирает дальнейшее направление Коммутация и транслир1ет команду коммутации в выбранное направление к устройству-приемнику 23.

На вход 12.5 устройства 22 от собственного процессора 22 поступает единичный сигнал Запрос, который инициирует выработку блоком 4 единич ных сигналов на выходах 11.5 и 4.5 (единичный сигнал Запрос на входе 12.5 поддерживается в течение всего времени настройки канала связи и обмена по нему).

Единичный сигнал Готово с выхода 11.5 устройства 22 поступает в вьщавшее сигнал Запрос направление (к процессору-источнику 22), инициируя выдачу из него команды коммутации и подачу ее на информационные входытвыходы 10 устройства.

Одновременно сигналы с выходов 11.5 и 4.5 поступают в блоки 5 и 1, разрешая прохождение команды коммутации с информационных входов-выходов 10 на информационные входы регистра 15.

Значение адреса, поступившего в команде коммутации ij 34, и значения собственного адреса устройства сопряжения j 22 инициируют работу блока 2 согласно ситуации 3-В2/А2-1, так как

Г СП-х, г, i. и Г 1.

На выходах шифратора 21 устройства 22 формируется 1 5-разрядный код 0001000100 0000, что означает движение Вниз, Вправо, Пустой цикл. Данный код заносится в кольцевой регистр 22. Причем на выходах кольцевого регистра 22 установится унитарньй код 00010, обеспечивающий формирование единичного сигнала Запрос на выходе 13.4 устройства. Одновременно данный единичный сигнал поступает на соответствующий вход элемента 23.4. Сигнал с выхода 13.4 поступает в направление Вниз к устройству 32 сопряжения, находящемуся в состоянии Занято, из которого ответный единичньй сигнал Готово не поступает на вход 14.4. Элемент 23.4 остается закрытым, единичный сигнал на его выходе не формируется, что обеспечивает наличие единичного сигнала на инверсном выходе элемента ИЛИ 24. На вход 4.7 блока 3 поступает единичный сигнал, по переднему фронту которого второй одновибратор 27 формирует единичный импульс.

Данный импульс через элемент И 25, открытый единичным сигналом с инверсного выхода элемента ИЛИ 24 поступает на вход управления сдвигом кольцевого регистра 22, иници- ируя в последнем сдвиг кодов возможных направлений коммутации. На выходах 13 кольцевого регистра 22 устанавливается код 00000, который не указьгоает направление коммутации и цикл опроса является пустым. Следующий единичный сигнал на входе 4.7 устанавливает код 00100 на выходах кольцевого регистра 22, которьй (Обеспечивает формирование единичного сигнала Запрос на выходе

13,3 устройства. Одновременно данный единичный сигнал поступает на соответствующий вход элемента И 23.

Сигнал с выхода 13.3 поступает в блок 5 и в направление Вправо к устройству 23 сопряжения, находящемуся в состоянии Свободно, из которого на вход 14.3 поступает ответный единичный сигнал Готово. Сигнал с входа 14.3 через элемент И 23.3, открытый единичным сигналом с выхода кольцевого регистра 22, обеспечивает формирование единичного сигнала на прямом выходе 3.1 эле мента ИЛИ 24 и нулевого сигнала на инверсном выходе данного элемента. Нулевой сигнал с инверсного выхда элемента ИЛИ 24 поступает на соответствующий вход элемента И 25, блокируя прохождение последующих импу:ж сов сдвига, формируемых на выходе второго одновибратора 27.

Таким образом, на выходе 13-.3 фиксируется единичный сигнал Запрос наличие которого обеспечивает ответный сигнал Готово в течение всего сеанса связи.

Единичный сигнал с выхода 3.1 блока 3 поступает на вход первого одновибратора 18, который по переднему фронту данного сигнала формирует единичный импульс.. Данньй импульс стробирует выдачу команды .коммутации из регистра 15 через первую группу элементов И 17 на выходы 1.8 блока 1. Команда коммутаци по входам t.8 через соответствующий узел 5.3 блока 5, открытый единичным сигналом на входе 13.3, поступает на информационные входы-выходы 8 устройства сопряжения и ориентирована на направление Вправо (команда коммутации выдается устройству-приемнику 23). Наличие постоянных единичных сигналов на выходах 11.5 и 13.3 обеспечивает

логический канал, соединяющий информационные входы-вькоды 10 с информационными входами-выходами 8 в блоке 5, т.е. канал через данное устройство сопряжения зафиксирован. Таким образом, команда коммутации протранслирована в соседнее устройство 23 сопряжения, в котором будет инициирована аналогичная последовательность действий.

Окончательно настроенньй канал связи будет иметь следующую конфигурацию: процессор-источник 22 устройство 22 сопряжения - устройство 23 сопряжения - устройство 33 сопряжения - устройство 34 сопряжения - процессор-адресат 34.

После окончания обмена процессористочник снимает сигнал .Запрос с входа 12.5 устройства 22 сопряжения, что приводит к установке нулевого сигнала Готово на выходе 11.5, подтверждающего установку устройства в исходное состояние и разрушение настроенного логического канала связи. Одновременно на выходе 4,5 блока 4 формируется нулевой сигнал закрывающий мальтиплексор 16, а на выходе 4.6 - единичный сигнал которьй поступает на входы установки нуля регистра 15 и кольцевого регистра 22, устанавливая их в нулевое состояние. В результате установки нулевого состояния в кольцевом регистре 22 на выходах 13 устанавливается нулевой код, т.е. снимается сигнал Запрос к соседнему устройству-приемнику 23. Таким образом, осуществляется последовательное разрушение настроенного логического канала связи и установки ранее выбранных устройств сопряжения в исходное состояние, после этого каждое из данных устройств может.быть задействовано вновь Е любой другой логический канал ,

фиг.Г

| Авторское свидетельство СССР № 758128, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Промывально-вытяжная машина | 1927 |

|

SU8513A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-04-03—Подача