Изобретение относится к вычислительной технике и может быть использовано для распределения заданий процессорам в мультипроцессорных системах.

Известно устройство для распределения заданий процессорам, содержащее регистр готовности процессоров, регистр сдвигов, узел управления, элементы ИЛИ, группы элементов И [1].

Известно также устройство для распределения заявок по процессорам, содержащее группы регистров хранения, регистр готовности, три группы элементов И, блок управления, группу блоков элементов И, регистр сдвига, три группы элементов ИЛИ, элемент ИЛИ, элемент И [2].

Недостатком аналогов является то, что преобразование адресов при назначении производится с помощью сдвигового регистра, что делает невозможным взаимно однозначное соответствие логического адреса физическому и не удовлетворяет требованиям по быстродействию.

Наиболее близким по технической сущности к изобретению является устройство для распределения заявок по процессорам, содержащее группу регистров, регистр потребности, регистр готовности, блок назначения, блок управления, элементы И, ИЛИ, элементы задержки [3].

Недостатками этого устройства являются низкое быстродействие и невозможность назначения нескольких процессоров с разными кодами операций на задание, запоминание их на время решения и снятие по окончании решения задания.

В устройствах распределения заданий процессорам - аналогах не учитывается случай отказа одного или нескольких процессоров во время решения задания. Алгоритм обработки отказа в прототипе не удовлетворяет требованиям обработки отказа в системах с программируемой архитектурой, а именно при отказе процессора в процессе решения задания это задание не может быть завершено, так как произошла передача искаженных данных от отказавшего процессора связанным с ним процессорам, и оно должно быть снято с решения и назначено заново на заведомо исправные процессоры.

Целью изобретения является расширение функциональных возможностей устройства за счет автоматического преобразования логических адресов процессоров в физические в многозаданном режиме и обработки возникающих сбоев во время решения.

Цель достигается тем, что в устройство, содержащее группу регистров, регистр готовности, регистр потребности, блок назначения, блок управления, первую, вторую и третью группы блоков элементов И, группу элементов И, элемент ИЛИ, первую и вторую группы элементов ИЛИ, элемент задержки, введены регистр номера задания, дешифратор номера задания, регистр и шифратор номера отказавшего задания, регистр накопления, вторая и третья группы элементов И, третья и четвертая группы элементов ИЛИ, группа дешифраторов и группа шифраторов с соответствующими связями.

Наличие отличительных признаков, а именно регистра и дешифратора номера задания, регистров хранения назначений, регистра и шифратора номера отказавшего задания, расположение и содержимое узлов назначения в блоке назначений и связей между ними обусловливают соответствие заявляемого технического решению критерию "новизна".

Заявляемое техническое решение соответствует также критерию "существенные отличия", поскольку не обнаружено решений с признаками, сходными с признаками, отличающими заявляемое техническое решение от прототипа.

Возможность достижения цели изобретения обусловлена динамическим преобразованием логических адресов процессоров в физические и временным хранением назначений процессоров на задание на время его решения. Увеличение быстродействия в процессе преобразования адреса в блоке назначений обусловлено тем, что введен новый алгоритм прохождения сигнала, использующий диагональный перенос между узлами назначения.

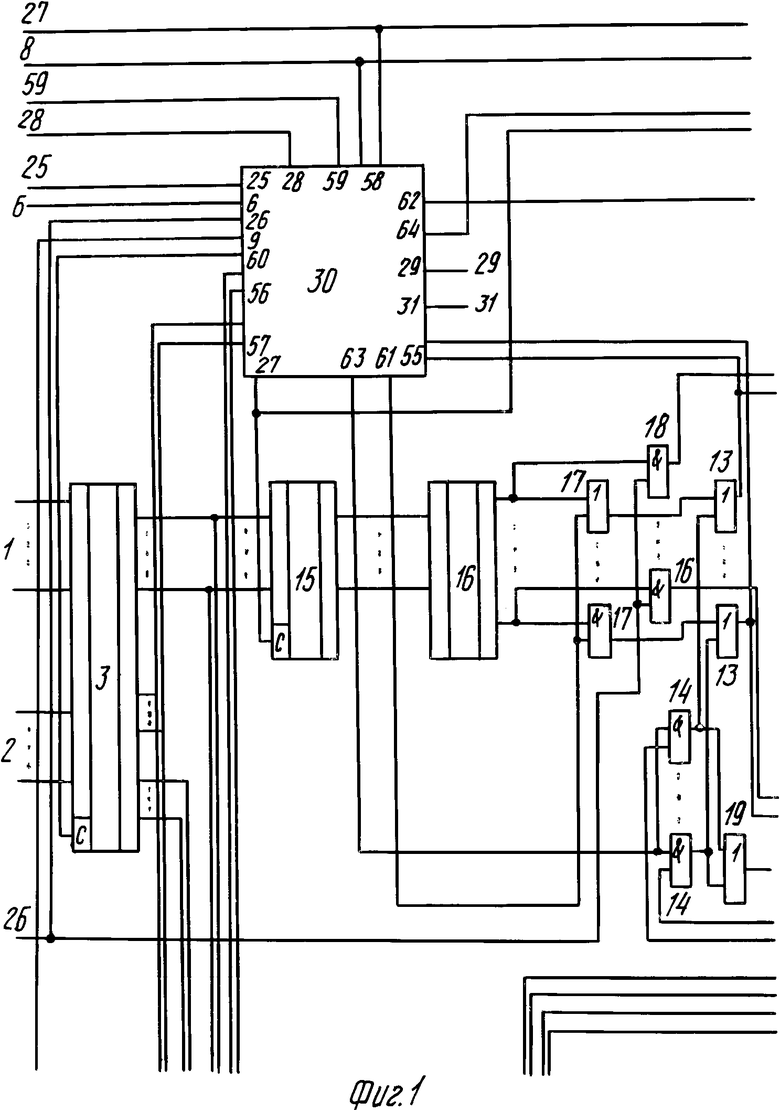

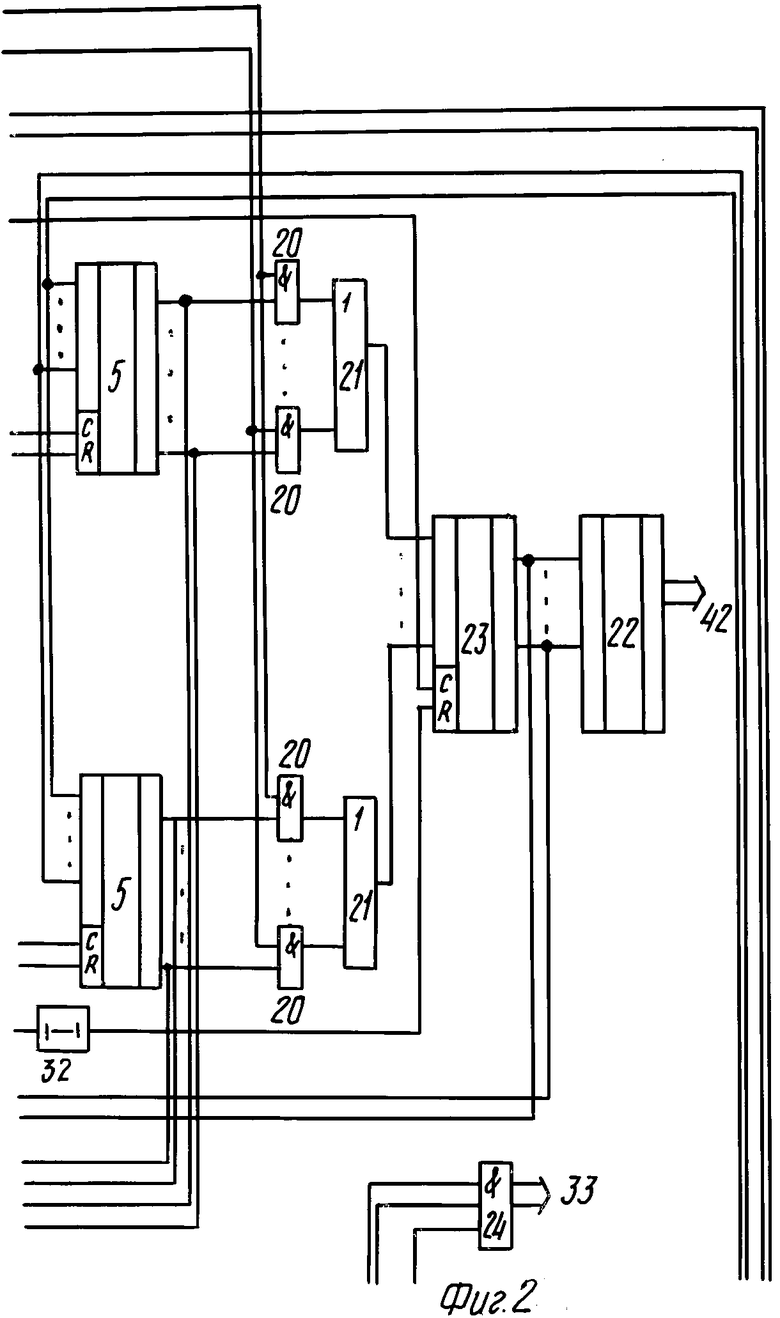

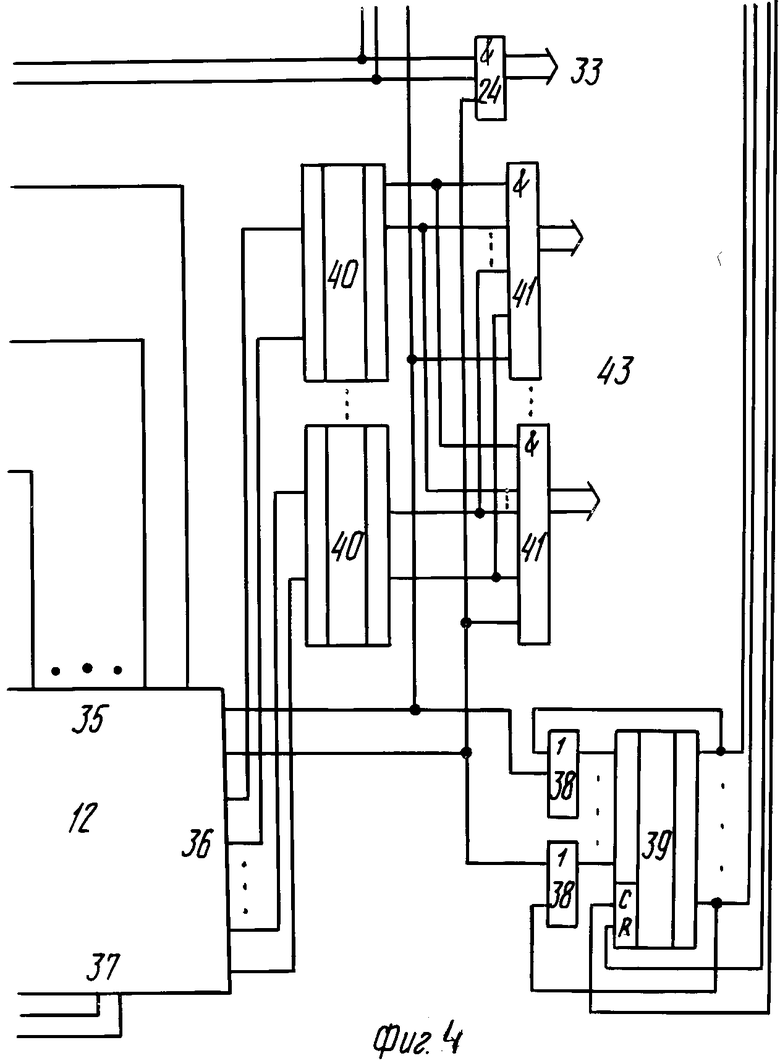

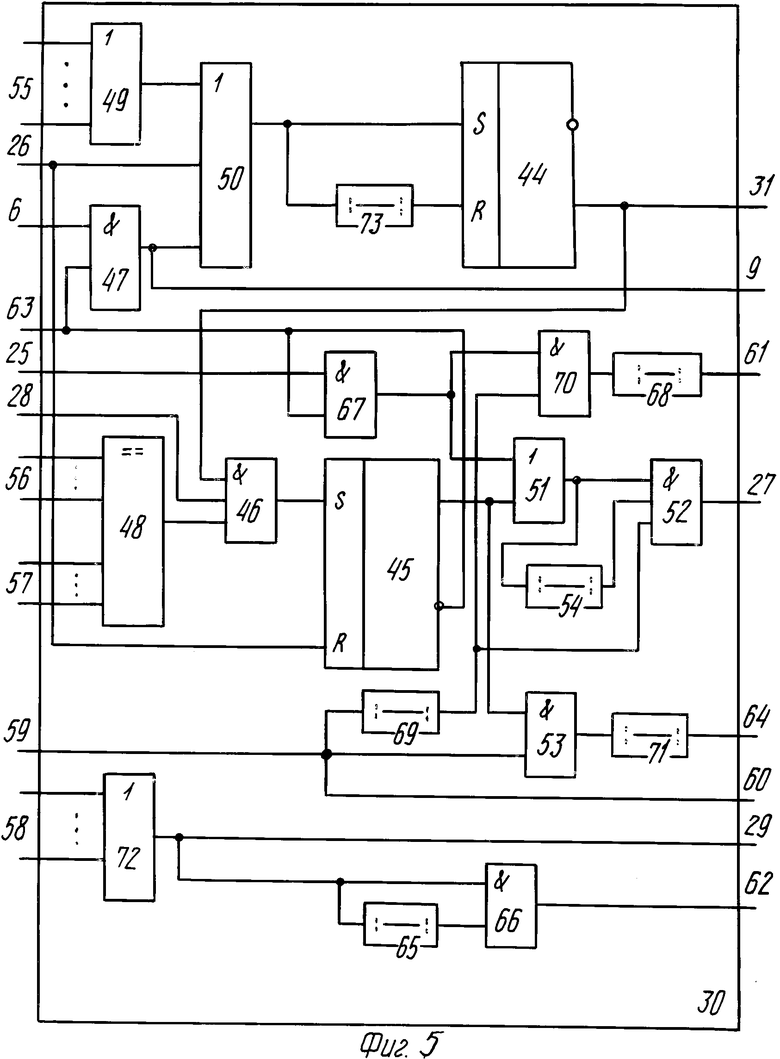

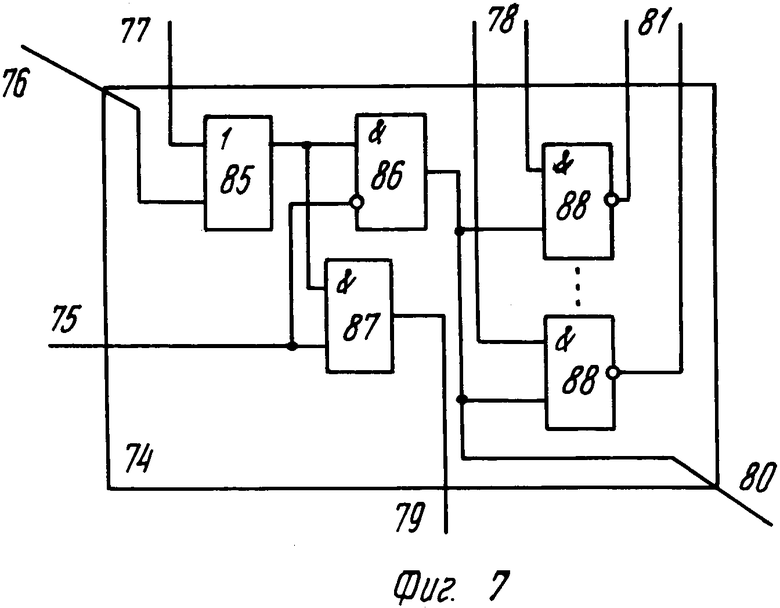

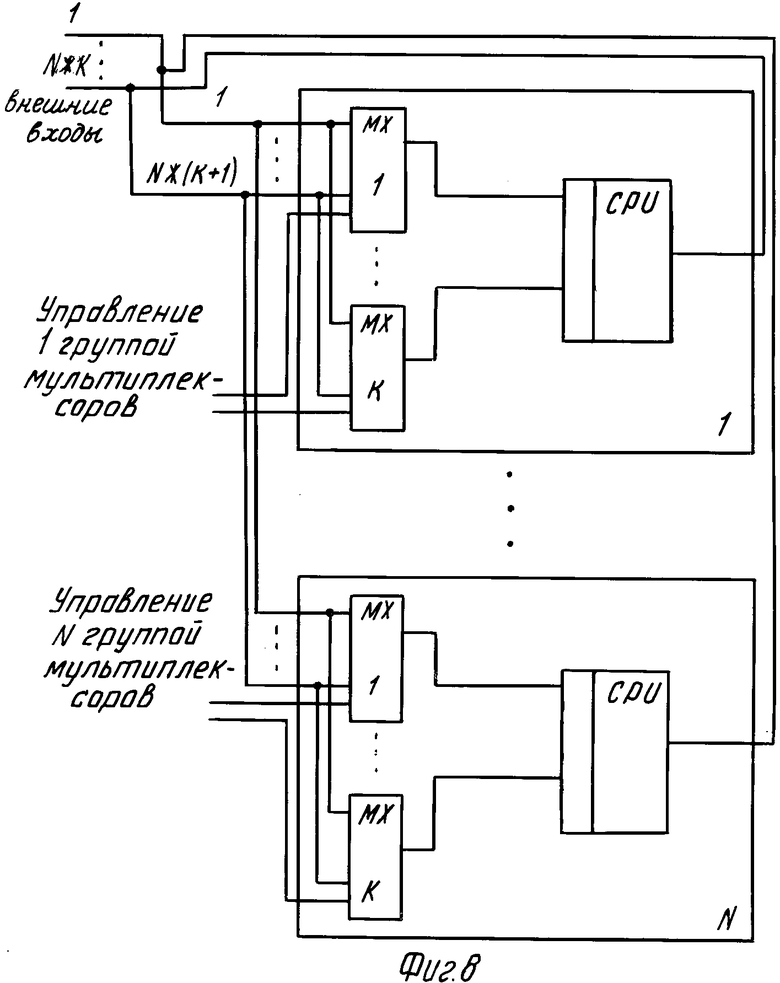

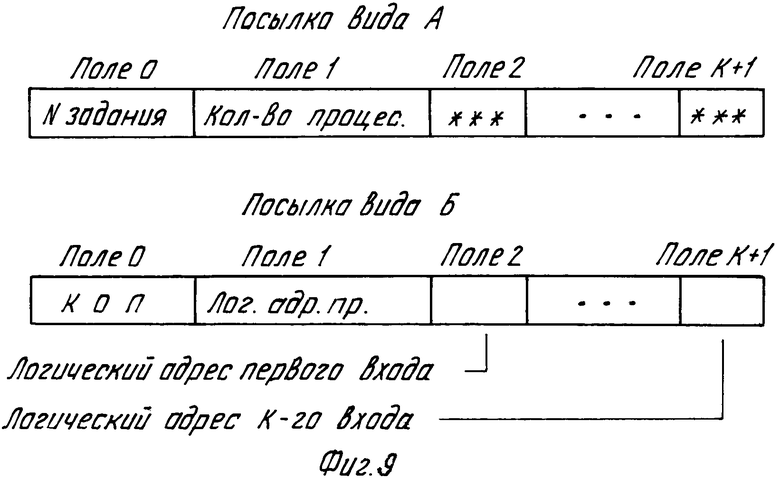

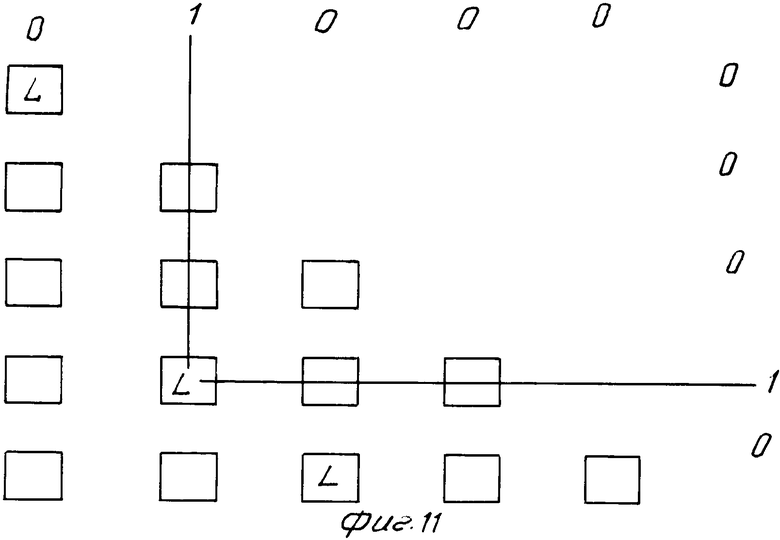

На фиг. 1-4 приведена структурная схема устройства; на фиг.5 - функциональная схема блока управления; на фиг.6 - структурная схема блока назначений; на фиг. 7 - функциональная схема узла назначения; на фиг.8 показано поле процессоров с матричным коммутатором; на фиг.9 - структура заявки на задание; на фиг.10 - пример реализации режима программирования в блоке назначений; на фиг.11 - пример реализации режима преобразования в блоке назначений.

Устройство распределения заданий по процессорам содержит первую 1 и вторую 2 группы информационных входов, регистр 3 потребности, регистр 4 готовности, регистры 5, вход 6 "Перезапись состояния", первую 7 и вторую 8 группы сигнальных входов, вход 9 "Запись в регистр готовности", четвертую группу элементов ИЛИ 10, группу дешифраторов 11, блок 12 назначений, вторую группу элементов ИЛИ 13, четвертую группу элементов И 14, регистр 15 номера задания, дешифратор 16 номера задания, третью и вторую группы элементов И 17 и 18, элемент ИЛИ 19, первую группу блоков элементов И 20, первую группу элементов ИЛИ 21, шифратор 22, регистр 23 номера отказавшего задания, третью группу блоков элементов И 24, вход 25 "Сброс задания", вход 26 "Конец загрузки задания", вход 27 "Задание принято", вход 28 "Запись сообщения", выход 29 "Сбой", блок 30 управления, выход 31 "Готовность", элемент 32 задержки, сигнальные выходы 33 для управления процессорами, вторую 34 и первую 35 группы входов блока назначений, первую, вторую 36 и третью 37 группы выходов блока назначений, третью группу элементов ИЛИ 38, регистр 39 накопления, группу шифраторов 40, вторую группу блоков элементов И 41, сигнальные выходы 42 кода номера задания отказавшего процессора, сигнальные выходы 43 на управление матричным коммутатором.

Блок 30 управления содержит (фиг.5) триггеры 44, 45, пятый 46 и первый 47 элементы И, схему 48 сравнения, третий 49, четвертый 50 и второй 51 элементы ИЛИ, третий 52 и шестой 53 элементы И, четвертый элемент 54 задержки с инверсией, четвертую 55, вторую 56, третью 57 и первую 58 группы входов и первый вход 59, четвертый 60, третий 61, пятый 62, первый 63 и седьмой 64 выходы, первый элемент 65 задержки с инверсией, седьмой 66 и четвертый 67 элементы И, второй 68 и пятый 69 элементы задержки, второй элемент И 70, шестой элемент 71 задержки, первый элемент ИЛИ 72, третий элемент 73 задержки.

Блок 12 назначений содержит (фиг. 6) узел 74 назначения, вход 75 "Горизонтальный перенос" (Рг), вход 76 "Диагональный перенос" (Рд), вход 77 "Вертикальный перенос" (Рв), группу запросных входов 78, выход 79 "Вертикальный перенос", выход 80 "Диагональный перенос" (Рд), группу ответных выходов 81, группу элементов ИЛИ 82, группу блоков элементов НЕ 83, шифратор 84. Узел 74 назначения содержит (фиг.7) элемент ИЛИ 85, первый 86 и второй 87 элементы И, группу элементов И-НЕ 88.

В мультипроцессорных системах с программируемой архитектурой имеется поле процессоров, связь между которыми может быть организована любым способом от полнодоступного до конвейерного соединения элементов. Соединение производится матричным коммутатором, на вход которого поступает информация из внешней среды - K * n слов (n - число процессоров в поле; К - количество входов процессора) и с выходов процессоров - n слов.

Поле процессоров с матричным коммутатором представлено на фиг.8. Матричный коммутатор можно представить как n групп по К блоков мультиплексоров (K+1)*n слов в одно. При реализации графсхемы операции на поле процессоров вершины представляются процессорами, а дуги - их информационными связями. Графсхема алгоритма, составленная программистом, после этапа трансляции выдается на поле процессоров в виде набора посылок, каждая из которых состоит из логического адреса загружаемого процессора, соответствующего одной из вершин графа, кода операции для этого процессора и К полей, представляющих логические адреса входов внешней среды и тех процессоров, выходы которых подсоединяются к информационным входам загружаемого процессора (подразумевается, что любая из вершин графа имеет не более К входящих и одну выходящую дуги). Количество посылок зависит от числа вершин в графе. Набор посылок, реализующих загрузку поля для реализации графа, называется заданием. Подготовка и управление последовательностью заданий, посылаемых на решение, возлагается на планирующую систему. Необходимость преобразования логических адресов в физические обусловлена тем, что в поле процессоров могут находиться отказавшие элементы или занятые решением ранее загруженных заданий. За счет такого динамического назначения повышается надежность решения задания на поле процессоров. Устройство распределения задания по процессорам предназначено для преобразования заявки, поступающей от планирующей системы, в коды управления загрузкой процессоров. Устройство может использоваться в мультипроцессорных системах с программируемой архитектурой или, как частный случай, в системах с программируемой структурой.

Структура заявки на задание, представленная на фиг.9, имеет два вида кодовых посылок с К+ 1 полями. Посылка вида А посылается планирующей системой вместе с сигналом "Запись сообщения". Поле 0 содержит номер задания, поле 1 - количество требуемых процессоров для этого задания. Содержимое остальных К полей несущественно. Если в поле процессоров число свободных элементов не меньше требуемого на задание, то оно может быть загружено (запомнен номер задания). Если задание было загружено, планирующая система активизирует посылки вида Б. В поле 0 содержится код операции загружаемого процессора, в поле 1 - его логический адрес, в поле с 2-го по (К+1)-й - логические адреса для настройки блока матричного коммутатора. Номер блока соответствует номеру загружаемого процессора (поле 1). Например, адрес из поля 2 управляет работой первого мультиплексора блока, осуществляющего связь К+1 входов с одним выходом.

Устройство работает следующим образом.

В начальный момент времени триггеры готовности 44, активности 45 и регистры 5 хранения назначений находятся в нулевом состоянии, формируется сигнал на входе 9 "Запись в регистр готовности" из сигнала на входе 6 "Перезапись состояния", который, пройдя через открытый элемент И 47, разрешает запись с информационных входов 7 в регистр 4 готовности и через элемент ИЛИ 50 устанавливает триггер 44 готовности в ноль. Сигналы с входов 7 изменяют содержимое регистра 4 и информацию на входах 34 блока назначений. При этом блок входит в режим программирования, на всю длительность которого триггер 44 готовности и сигнал "Готовность" устройства удерживаются в нулевом состоянии. По окончании режима программирования на выходе 37 блока назначений появляется двоичный код числа свободных процессоров. После этого устройство готово принимать заявки.

По сигналу на выходе 31 "Готовность", равному единице, планирующая система выставляет сигнал на входе 28 "Запись сообщения" и на информационные входы устройства подает посылку вида А. Причем на входы 1 поступает информация из поля 0, на входы 2 - остальная информация. Запись в регистр 3 потребности происходит по сигналу с выхода 60. В схеме 48 сравнения блока управления происходит сравнение числа требуемых процессоров из поля 1 заявки (вход 57) с имеющимся количеством свободных (вход 56), и если число свободных процессоров больше или равно числу требуемых, то на элемент И 46, открытый сигналами с входа 28 и выхода 31, поступает единичный сигнал, который устанавливает триггер 45 активности в единицу. При этом на элементе И 52 и элементе 54 с приходом задержанного тактового импульса с входа 59 формируется положительный импульсный сигнал 27 "Задание принято" и осуществляется запись в регистр 15 номера задания. По этому же импульсу происходит сброс регистра 39 накопления.

Если планирующая система получила сигнал "Задание принято" высокого уровня, то она выставляет на входы 1 и 2 устройства посылку вида Б. Информация из поля 1 посылки, содержащая код операции, поступает на входы группы блоков элементов И 24. Информация из полей c 1-го по (К+1)-й поступает на соответствующие схемы опроса состояния блока назначений с первой по (К+1)-ю логический адрес загружаемого процессора из поля 1 поступает на вход первого дешифратора группы дешифраторов 11, с его выхода через группу входов 35 блока назначений - на первые элементы И-НЕ узлов назначения и с них на первые элементы НЕ блока группы блоков элементов НЕ 83. На выходах этих элементов НЕ получают физический адрес процессора в позиционном коде. Этот код через выходы 36 блока назначений подается на соответствующий вход блоков элементов И 24, разрешая передачу кода операции загружаемому процессору, на вход блоков элементов И 41 и через группу элементов ИЛИ 38 на регистр 39, в котором запоминаются все процессоры, загрузка которых происходит в этом задании. (По окончании загрузки задания в регистре 39 содержится код с единицами в разрядах, соответствующих загруженным процессорам).

Логические адреса из полей с 2-го по (К+1)-й, пройдя через свои схемы опроса с выходов 36 блока назначений, поступают на соответствующий им шифратор группы шифраторов 40. С них двоичные коды физических адресов входов, предназначенные для управления работой группы блоков мультиплексоров матричного коммутатора, поступают на групповые входы блока элементов И 41. Сигналами разрешения для этих элементов И служат биты физического адреса загружаемого процессора (т.е. они определяют группы настройки мультиплексоров коммутатора).

Один за другим происходит распределение задания всем процессорам. По сигналу с входа 26 "Конец загрузки задания" информация из регистра 39 переписывается в один из регистров группы регистров 5 хранения назначений, определяемый номером загружаемого задания. После этого процессоры настроенного задания могут начать решение. Если в течение решения произошел сбой процессора, сигнал с него через входы 8 поступает на группы элементов И 20 и элемент ИЛИ 72, на котором формируется сигнал 29 "Сбой". На элементах И 20 и элементах ИЛИ 21 происходит выявление номера задания, при решении которого произошел сбой. В регистр 23 с выхода элементов ИЛИ 21 по сигналу с выхода 62 записывается позиционный код номера задания, а на выходе шифратора 22 получают двоичный код, выставляемый для планирующей системы на выходе 42. Сигнал на выходе 62 образуется в блоке управления из сигнала на выходе 29 путем формирования импульса из сигнала высокого уровня элементом 65 задержки и элементом И 66 для записи информации в регистр 23. Сброс задания производится, если в данный момент устройство не занято загрузкой задания, т. е. триггер 45 активности находится в нулевом состоянии при обнаружении сбоя через группы элементов И 14 и ИЛИ 13 (сброс регистра 23, содержащего код сбойного задания, производится по сигналу с выхода элемента ИЛИ 19 (сигнал сброса на одном из входов регистров), задержанному элементом 32 на минимальное время, необходимое для реакции планирующей системы на информацию по выходам 42 устройства, или по окончании его решения путем подачи на входы 1 устройства номера задания и сигнала с входа 25 "Сброс задания"). При этом на выходе элемента И 67 формируется сигнал "1", который, пройдя через элемент ИЛИ 51, на элементах 54 задержки и И 52 в присутствии задержанного тактового сигнала с входа 59 элементом 69 (на время задержки записи в регистр, схемы сравнения, двух логических элементов и триггера) формирует положительный импульс входа 27, по которому происходит запись в регистр 15 номера задания. Иными словами, импульс на входе 27 формируется в момент установки триггера 45 в единицу или при сбросе задания по задержанному тактовому сигналу с входа 59. Время задержки элемента 54 больше, чем у элемента 69 и меньше длительности такта. Сигнал на выходе 61, разрешающий прохождение сигналов сброса на регистры 5 через элементы И 17, формируется на элементе И 70 из выходных сигналов элемента И 67 и элемента 69 задержки c задержкой его на элементе 68 на время задержки одного логического элемента, дешифратора и записи в регистр 15. Сигнал на выходе 64, синхронизирующий запись в регистр 39, формируется, если идет назначение процессоров (в регистре 3 посылки второго вида и триггер 45 в "1"), из сигналов с входа 59 тактовой серии и прямого выход а триггера 45 активности на элементе И 53 при задержке выходного сигнала элементом 71 на время задержки срабатывания регистра, дешифратора и двух логических элементов. На элементах ИЛИ 10 группы происходит формирование входной информации для входов 34 блока назначений. q-й бит входного слова равен единице (т.е. соответствующий процессор не свободен), если q-й бит регистра готовности находится в "1" (процессор отказал) или q-й бит одного из регистров группы регистров 5 - в "1" (процессор занят ранее загруженным заданием). В результате на входах 34 имеются нулевые сигналы в битах, соответствующих процессорам, на которые может быть назначено задание. Сигнал с выхода 31 "Готовность" устройства равен нулю во время прохождения режима программирования в блоке назначений, который возникает после изменения информации на входах 35 блока. Информация может измениться, если произошла перезапись регистра 4 готовности (сигнал на входе 9 высокого уровня) или изменилась информация в одном из регистров 5: загрузилось задание (сигнал на входе 26 высокого уровня) или произошел сброс задания (на одном из входов группы входов 55 сигнал "1", на выходе элемента ИЛИ 49 сигнал высокого уровня). На выходе элемента ИЛИ 50 формируется сигнал высокого уровня, устанавливающий триггер 44 готовности в ноль, а через время задержки элемента 73, равное длительности режима программирования блока назначений, перебрасывает его в единицу.

Блок назначений для поля из n процессоров состоит из (n ∧ 2 + n)/2 узлов 74 назначения, объединенных в треугольную матрицу, n-1 элементов ИЛИ, шифратора, К+1 групп по n инверторов. Каждый узел назначения содержит элемент ИЛИ 85, элементы И 86, 87, группу из К+1 элементов И-НЕ 88. На входы ячейки поступают сигналы с входа 75 "Горизонтальный перенос" (Рг), входа 76 "Диагональный перенос" (Рд), входа 77 "Вертикальный перенос" (Рв), с группы запросных входов 78. На выходах получают сигналы с выхода 79 "Вертикальный перенос" (Рв), выхода 80 "Диагональный перенос" (Рд), группы ответных выходов 81. На входы 75 "Горизонтальный перенос" каждого узла строки i подается i-й разряд слова с входа 34 блока назначений. На группу входов 78 узлов i-го столбца подаются j-е биты кодов логических адресов, выраженных в позиционном виде. С группы выходов 81 строки i снимают i-е биты позиционных кодов физических адресов. Выходы 79 узла i, j соединяется с входом 77 узла i+1, j, а выход 80 узла i, j соединяется с входом 76 узла i+1, j+1. На все входы 76 узлов левого (нулевого) столбца подается сигнал "0", на вход 77 узла верхней (нулевой) строки подается сигнал "1", а на остальные входы 77 диагональных узлов блока - сигналы "0". В узле назначения реализуется функции: Рв' = (Рв) V Рд) &Рг; Рд' = (Рв VРд) &' Рг. Это позволяет установить сигнал Рд' в единицу в том i-м узле j-го столбца, когда необходимо логический адрес, равный j, преобразовать в физический адрес, равный i. Следует отметить, что сигналы Рд и Рв являются взаимно исключающими, т. е. на входы какого-либо узла не могут поступать эти два сигнала одновременно и выработаться на выходе узла может только Рв' или только Рд' высокого уровня. Можно считать, что Рв и Рд являются активизирующими сигналами для узлов, в которых в зависимости от сигнала Рг формируются Рв' и Рд'.

Режим программирования показан на фиг.7. Символ L показывает, что в этой ячейке Рд' = 1. Если все процессоры свободны, то на правый (старший) вход шифратора 84 поступает единичный сигнал. Если отказавшие процессоры есть, то на входе шифратора появляется единица в соответствующем разряде. В показанном случае оказалось три свободных процессора. В режиме преобразования на вход узлов подается позиционный код логического адреса, на выходе получается позиционный код физического адреса. При m = 1,...,К+1 дешифратор m группы дешифраторов 11, m-е элементы И-НЕ 88 узлов назначения, m-е элементы НЕ 83 блока группы составляют m-ю схему опроса по столбцам состояния сигналов Рд' в блоке назначений. Все схемы опроса равноправны и используются для одновременного преобразования К+1 логических адресов в физические. В строке i m-е сигналы группы выходов 81 узлов объединены для реализации функции МОНТАЖНОЕ И, т.е. при появлении на m-м входе одного из узлов сигнала "0" на вход m-го элемента НЕ поступает сигнал "0"- на выходе его появляется "1". Появление сигнала на выходе m-го элемента И-НЕ узла i, j возможно в том случае, если Рд' этого узла равно единице и происходит опрос j-го столбца (j-й бит m-го дешифрато- ра равен единице, т.е. по m-й схеме опроса преобразуется логический адрес, равный j). Для простоты рассмотрим пример работы одной схемы опроса. Пусть в режиме программирования сигналы Рд' установились так, как это показано на фиг.8. Если на вход подать код 0 1 0 0 0 (логический адрес равен двум), то на выходе получают код 0 0 0 1 0 (физический адрес равен четырем).

Использование совокупности существенных признаков: введение регистра и дешифратора номера задания, блока назначений с К схемами опроса позволяет расширить функциональные возможности устройства за счет автоматического преобразования логических адресов процессоров в физические в многозаданном режиме и обработки возникающих сбоев во время решения, повысить быстродействие при преобразовании адресов. Используемый в прототипе блок назначений производит преобразование адреса за время Т = 2*n* t (n - разрядность адреса; t - задержка срабатывания узла назначения, равная 2 * t л.э. (t л.э. - задержка одного логического элемента), т.е. T = 4 *n* t л.э. Затраты оборудования при этом составляют 5 л.э. *n ∧ 2. В описываемом устройстве задержка режима программирования блока назначений составляет 2*n * t л.э., а преобразование адреса производится за 2*t л.э. Аппаратные затраты при этом составляют ((n ∧ 2 + n/2* *(3 л.э. + Кл.э.) + (n-1)л.;э.; + n*Kл.э. + [log2* *(n+1)]л.э., при К = 1 (как в прототипе) имеют 2*n ∧ 2 d+ 4 * n-1 + [log2 (n + 1)] (при n > = 2 получают экономию логических элементов по сравнению с прототипом).

Изобретение целесообразно реализовать на БМК, при этом потребуется около 1570 л.э.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1453406A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Адаптивное микропрограммное устройство управления | 1980 |

|

SU934471A1 |

| Устройство для формирования очереди | 1986 |

|

SU1446626A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1541608A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Изобретение относится к вычислительной технике и может быть использовано для распределения заданий по процессорам в мультиплексорных системах. Целью изобретения является расширение функциональных возможностей за счет автоматического преобразования логических адресов процессоров в физические в многозаданном режиме и обработки возникающих сбоев во время решения. Устройство содержит регистр потребности, регистр номера задания, регистр готовности, группу регистров, блок управления, блок назначений, группу дешифраторов, группу шифраторов, элементы И, ИЛИ. Устройство осуществляет прием кодов заданий, содержащих код номера задания, код числа потребных для ее решения процессоров, логические адреса назначаемых процессоров и их входов. Блок назначений производит преобразование логических адресов в физические с учетом состояния поля процессоров (процессоры могут отказать или быть заняты другими заданиями). При сбое процессора при решении задания его номер выводится в планирующую систему, которая может переназначить его на свободные процессоры. 1 з.п.ф-лы, 11 ил.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для распределения заявок по процессорам | 1987 |

|

SU1462314A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-07-30—Публикация

1991-08-09—Подача