Изобретение относится к вычислительной технике и может быть использовано для определения значения и аргумента максимума взаимной корреляционной функции (ВКФ) между случайными сигналами, подвергнутыми взаимному масштабновремен- ному искажению (МВИ)

Целью изобретения является повышение быстродействия

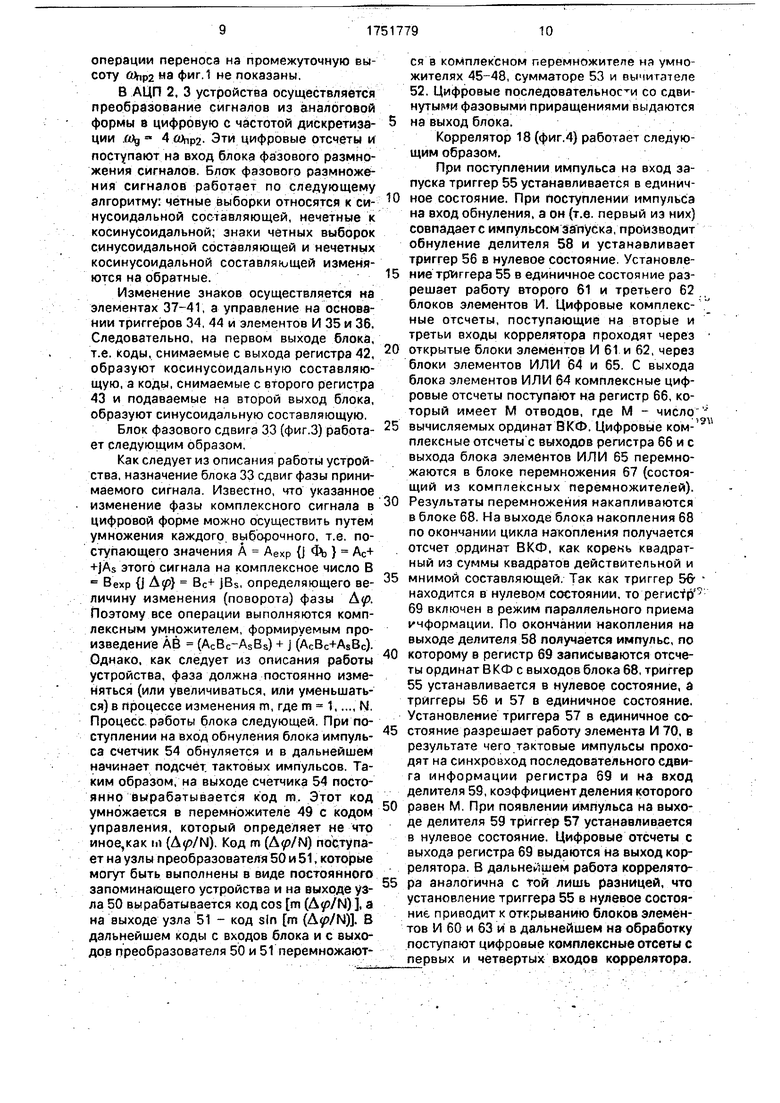

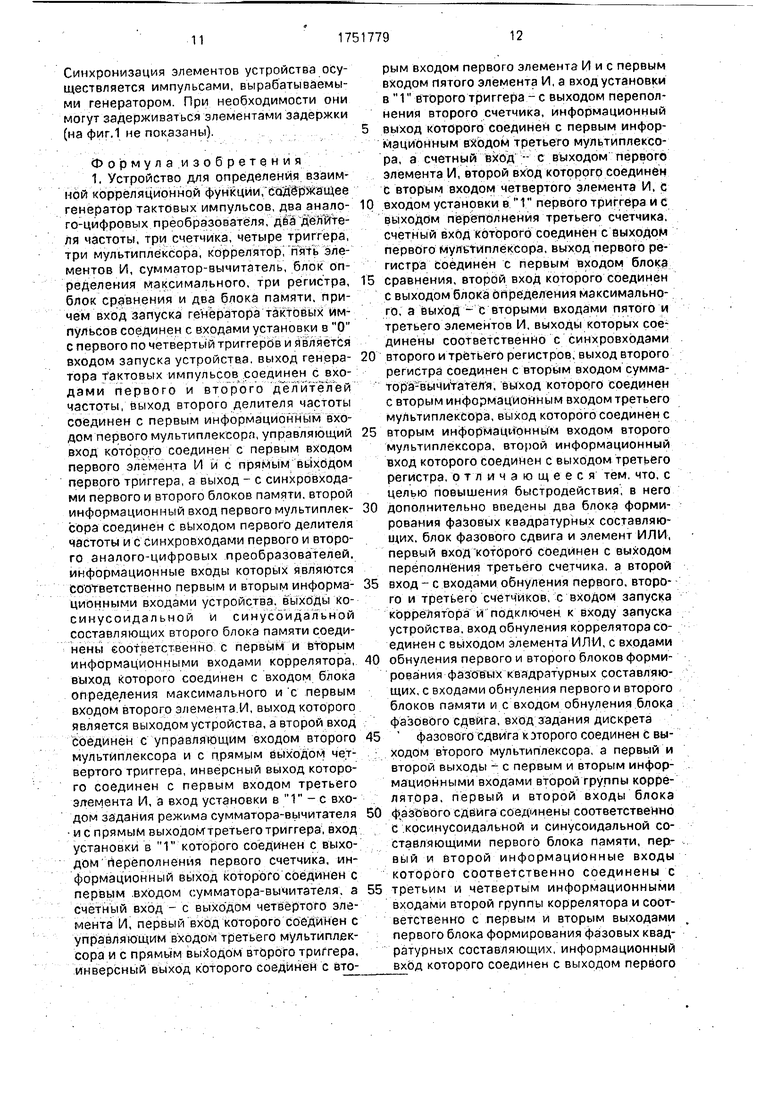

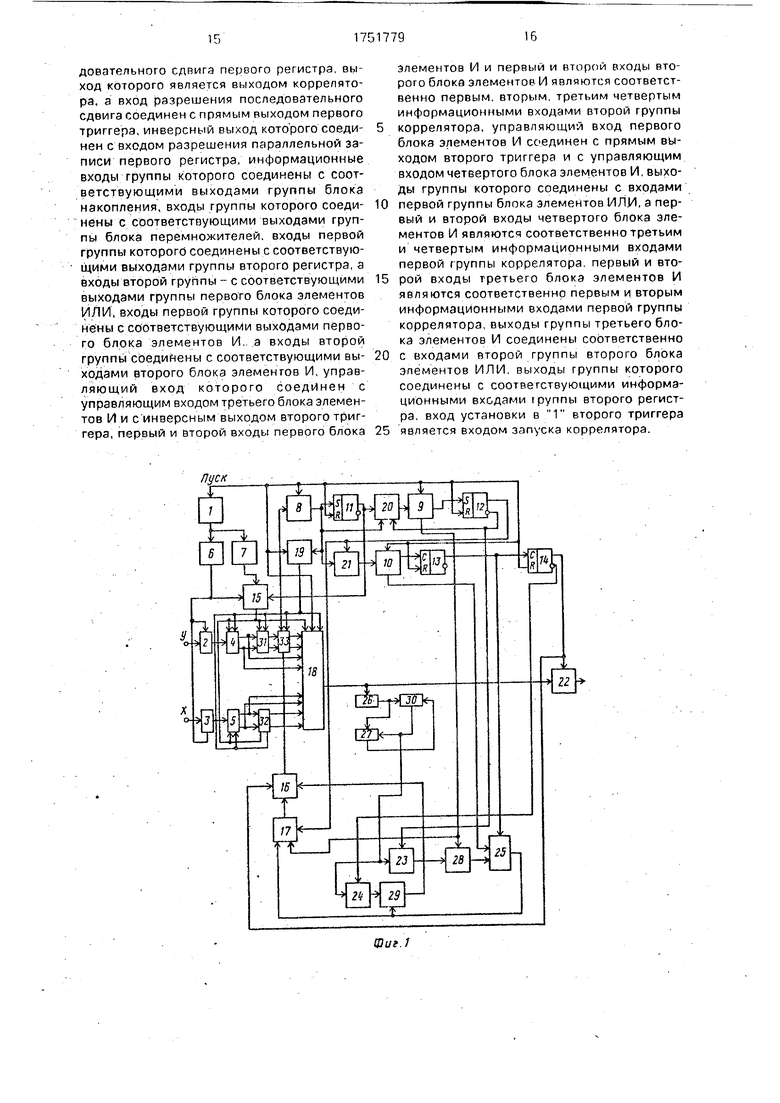

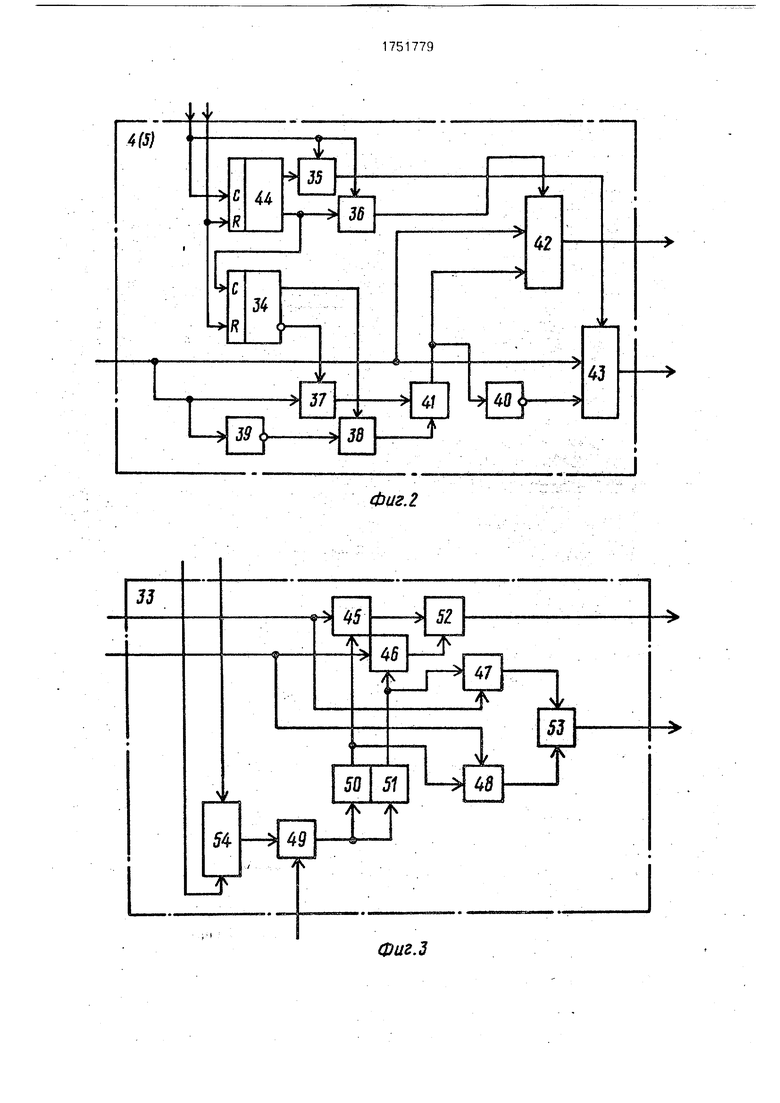

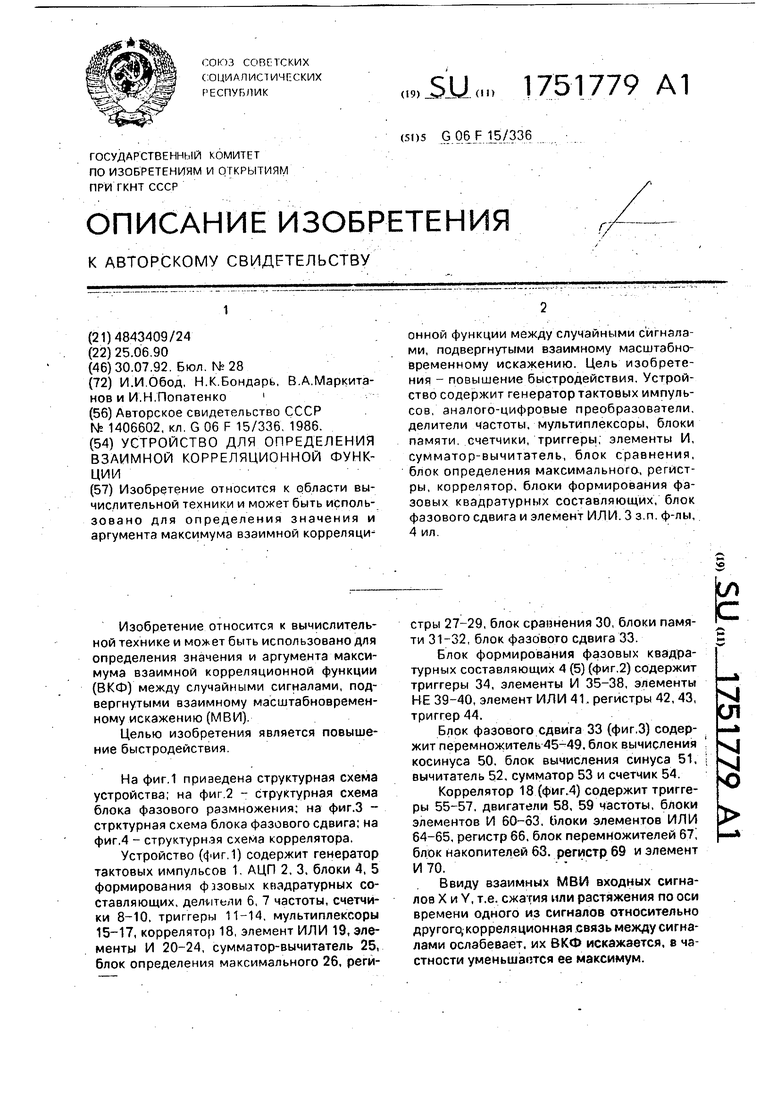

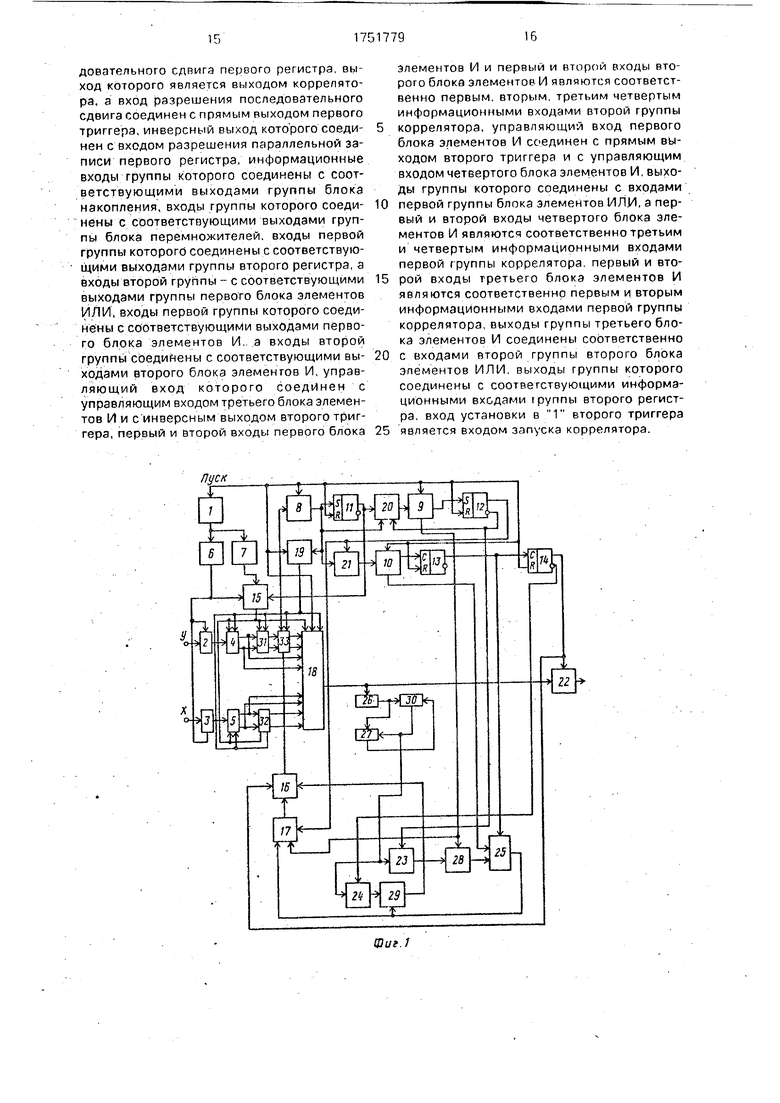

На фиг 1 приведена структурная схема устройства, на фиг 2 - структурная схема блока фазового размножения; на фиг.З - стрктурная схема блока фазового сдвига; на фиг 4 - структурнзя схема коррелятора.

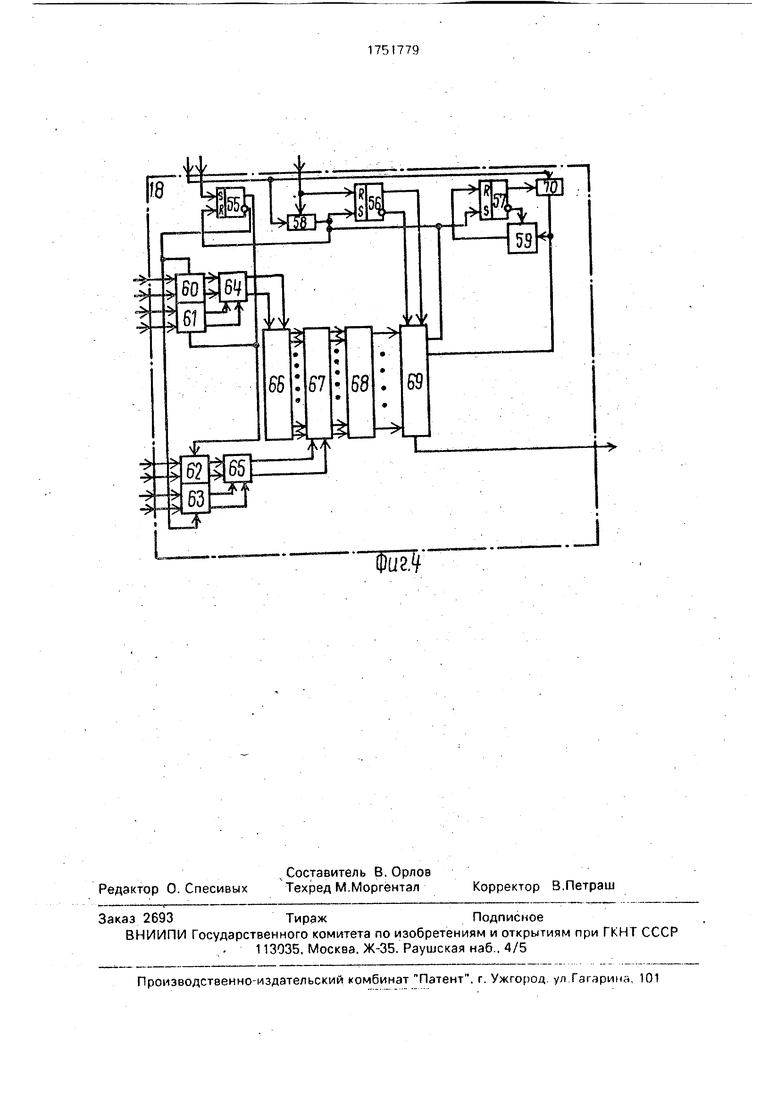

Устройство (Фиг 1) содержит генератор тактовых импульсов 1 АЦП 2, 3, блоки 4, 5 формирования фззовых квадратурных составляющих, делители 6, 7 частоты, счетчики 8-10, триггеры 11-14 мультиплексоры 15-17, коррелятор 18, элемент ИЛИ 19, элементы И 20-24, сумматор-вычитатель 25, блок определения максимального 26, регистры 27-29, блок сравнения 30, блоки памяти 31-32, блок фазового сдвига 33

Блок формирования фазовых квадратурных составляющих 4 (5) (фиг 2) содержит триггеры 34, элементы И 35-38, элементы НЕ 39-40, элемент ИЛИ 41. регистры 42, 43, триггер 44.

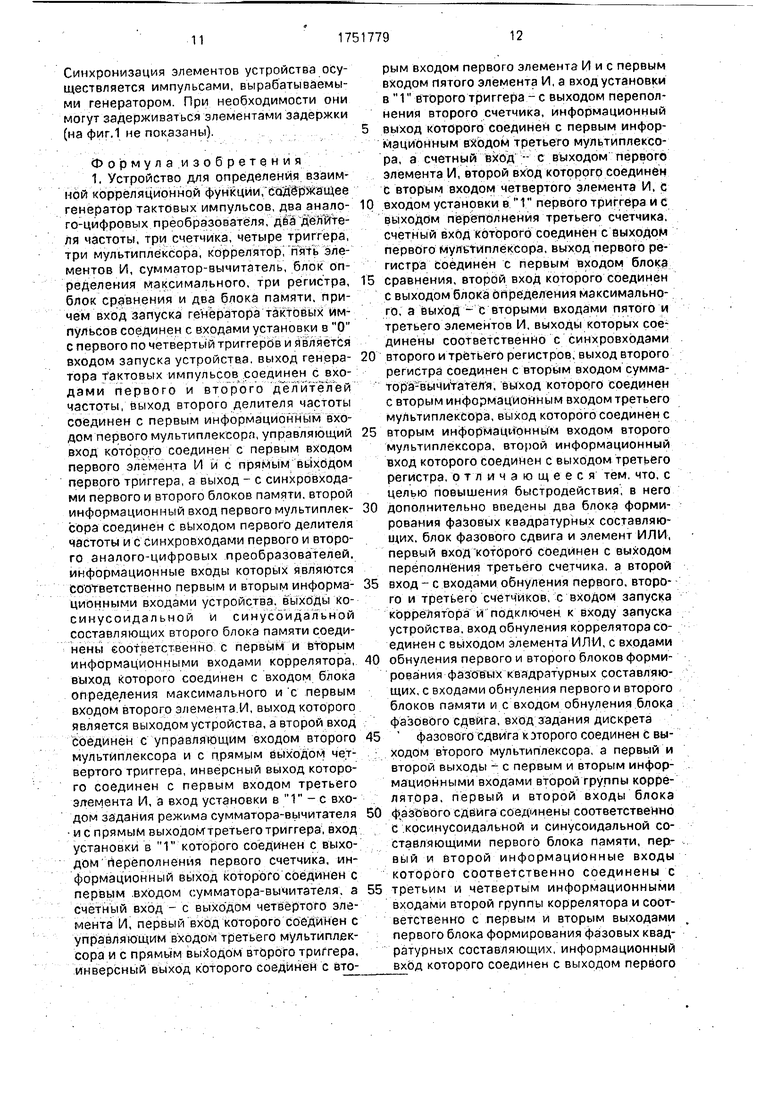

Блок фазового сдвига 33 (фиг 3) содержит перемножитель 45-49, блок вычисления косинуса 50. блок вычисления синуса 51, вычитатель 52, сумматор 53 и счетчик 54

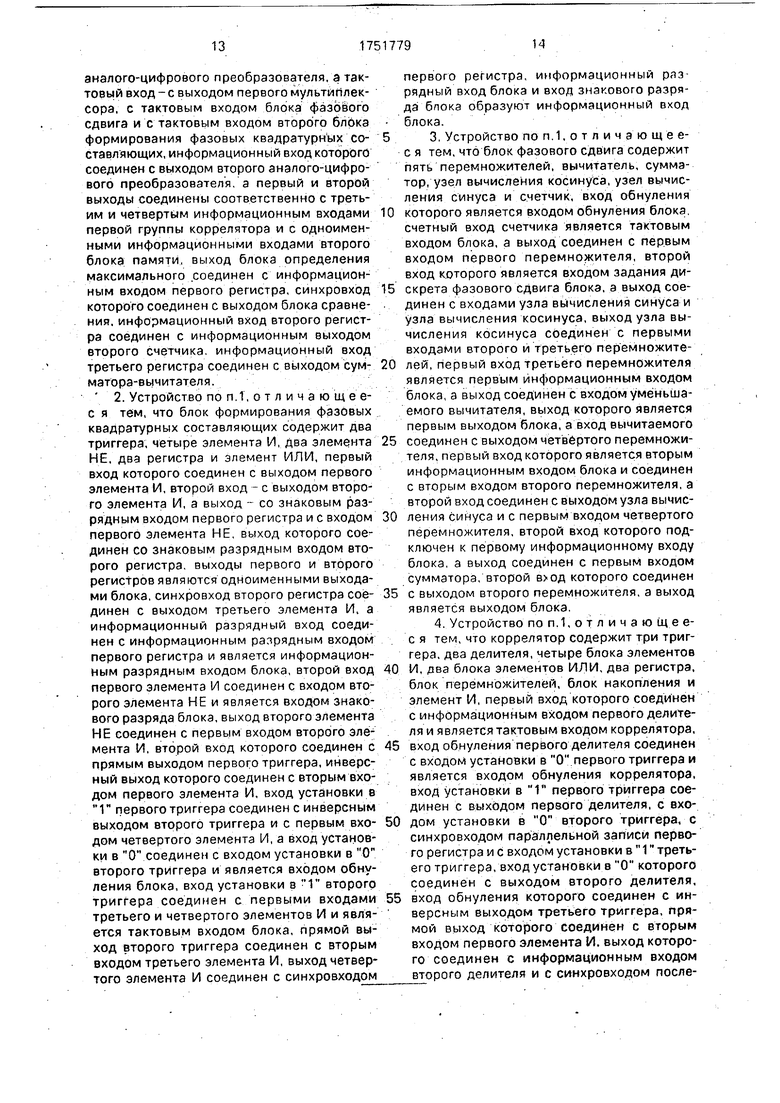

Коррелятор 18 (фиг.4) содержит триггеры 55-57, двигатели 58, 59 частоты, блоки элементов И 60-63, блоки элементов ИЛИ 64-65, регистр 66, блок перемножителей 67, блок накопителей 63. регистр 69 и элемент И 70.

Ввиду взаимных МВИ входных сигналов X и Y, т.е. сжатия или растяжения по оси времени одного из сигналов относительно другого, корреляционная связь между сигналами ослабевает, их ВКФ искажается, в частности уменьшается ее максимум.

Положим, чго МВИ сводится к сжатию во времени сигнала Y. Положим, также, что сигналы X и Y, спектр которых органичен верхней частотой fc, подвергается дискретизации с частотой f0 2fc. В результате дискретизации получается последовательность отсчетов, расположенных с интерзалом 1/f0, из которых можно восстановить исходный процесс. Наличие МВИ на фазовой плоскости приводит к соответствующему постоянному фазовому сдвигу. Следовательно, если одну из последовательностей производить фазовый сдвиг и затем вычислять ВКФ, этим удается компенсировать МВИ, повышать точность вычисления ВКФ.

Процесс определения ВКФ происходит в два этапа. На первом этапе изменяется фазовый сдвиг fi с дискретностью , причем для каждого значения fi I (I 0,1ni-1) определяется значение максимума соответствующей оценки ВКФ. Наибольшее из значений максимумов оценок, полученных на первом этапе, будет отличаться от максимума оценки ВКФ при полной компенсации МВИ не более чем на ЗдБ. Значение коэффициента р для этой оценки отличается от истинного коэффициента $ МВИ не более чем на

Если полученный результат не удовлетворяет требованиям по точности, то начинается второй этап, на котором происходит уточнение полученных на первом этапе результатов. Коэффициент компенсации МВИ в фазовой плоскости изменяется с дискретностью ( . При этом анализируется интервал изменения компенсирующего коэффициента от(де -У-)

до (р + -2 ) Значение р, соответствующее наибольшему из значений максимумов оценок ВКФ, полученных на втором этапе, отличается от истинного не более чем на ±Др2,

Выбор частоты дискретизации f0 2fc по условию Котельникова не является обязательным и использован только для наглядности рассуждений. В предлагаемом устройстве частота fo выбирается в зависимости от необходимого интервала Д т дискретизации и коррелограммы. а при использовании в корреляторе метода некоррелированных выборок - еще и в зависимости от значения интервала корреляции сигналов X и Yv

Устройство работает следующим образом.

В исходном состоянии счетчики 8-10, триггеры 11-14 и регистры 27-29 обнулены.

При таком положении мультиплексоры 15- 17 подключают выход делителя 6 к синхров- ходам блоков 4, 5, 31, 32, 33 и 18, а разрядные выходы счетчика 9, на которых присутствует слово, состоящее из логических нулей, к управляющему входу блока 33. Объемы блоков памяти (БП) 31 и 32 выбираются такими, чтобы в них поместились выборки реализаций входных сигналов X и

0 Y, обеспечивающих вычисление коррелограммы с необходимым фактором усреднения.

Нулевой цикл работы устройства на первом этапе начинается с приходом запу5 екающего импульса на вход запуска устройства, который включает тактовый генератор 1.. Тактовые импульсы, проходящие через делитель 6 частоты, поступают на синхронизирующие входы АЦП 2, 3, благодаря чему

0 входные аналоговые сигналы X и Y дискре- тизируются с одинаковой частотой. Цифровые отсчеты с выходом АЦП 2 и 3 поступают соответственно на входы блоков фазового размножения 4 и 5, с выходов которых сни5 маются комплексные составляющие входных отсчетов. Комплексные составляющие входных сигналов по импульсам, поступающим на синхровход блоков памяти 31 и 32 с выхода мультиплексора 15 записываются

0 соответственно в блоки памяти 31 и 32. Одновременно комплексные цифровые отсчеты с выходов блоков 4 и 5 поступают соответственно на вторые и третьи входы коррелятора 18, в котором вычисляются ор5 динаты ВКФ при нулевом фазовом сдвиге. Запись входных отсчетов в блоки памяти 31 и 32 и вычисление первой ВКФ осуществляется до переполнения счетчика 8. емкость которого определяется объемом выборки

0 входных реализацией, необходимой для построения коррелограммы, т.е. равна количеству отсчетов в выборке. По окончании записи выборки комплексных реализаций в БП 31 и 32 на выходе счетчика 8 формирует5 ся импульс, который поступает на счетный вход триггера 11 и передним фронтом устанавливает его в единичное состояние. Импульс с выхода счетчика 8 проходит через открытый элемент И 20 и переводит счетчик

0 9 в первое состояние. Установление триггера 11 в единичное состояние переключает мультиплексор (МП) 15 так, что он начинает пропускать на свой выход импульсы с выхода делителя 7. В корреляторе 18 в первом

5 цикле осуществляется вычисление ВКФ при нулевом фазовом сдвиге. Выход коррелятора 18 при этом отключен от выхода всего устройства, так как элемент И 22 закрыт низким потенциалом на прямом выходе триггера 14. Поэтому значения всех ординат

коррелограммы поступают только на блок

26,который выдает код максимальной ординаты на вход блока 30 сравнения. Этот блок сравнивает код с содержимым регистра 27. Если вновь поступившее от экстремального анализатора 26 число превышает код, хранящийся в регистре 27, то на выходе блока

30сравнения возникает импульс, который переписывает в регистр 27 новое значение максимальной ординаты, а в регистр 28 благодаря открытому элементу И 23 за счет высокого напряжения на инверсном выходе триггера 12 код счетчика 9, т.е. номер цикла. Таким образом, в нулевом цикле первого этапа блок 30 производит сравме- ние максимальной ординаты ВКФ и нулевого содержимого регистра 27. На выходе блока 30 появляется импульс и в регистр 27 записывается значение максимума ВФК, полученной в нулевом цикле, т.е. при одинаковых частотах дискретизации сигналов X и Y и без фазового сдвига. В регистр 28 зэно-х сится нулевое значение содержимого счетчика 9.

По окончании нулевого цикла, т.е. при появлении импульса на выходе переполнения счетчика 8, триггер 11 устанавливается в единичное состояние, а счетчик 9 на своем выходе формирует код единицы. Единичный код с выхода счетчика 9 проходит через МП 17 и 16 и поступает на управляющий вход блока фазового сдвига 33, благодаря чему блок 33 начинает осуществлять фазовый сдвиг поступающих комплексных цифровых отсчетов. В первом цикле цифровые комплексные отсчеты считываются с БП 31 и 32. Цифровые отсчеты с БП 32 поступают непосредственно на четвертые входы корре лятора 18, а цифровые отсчеты с выхода БП

31поступают на блок фазового сдвига 33, в котором осуществляется сдвиг по фазе поступающих цифровых отсчетов с целью растяжения их на временной оси. С выхода блока 33 цифровые отсчеты поступают на первые входы коррелятора 18. В корреляторе 18 осуществляется вычисление ВКФ между цифровыми сигналами X и растянутыми по временной оси цифровыми сигналами Y входа. После окончания определения ВКФ ее максимальная ордината с выхода блока 26 поступает на вход блока 30 сравнении и, если она превышает максимум предыдущей ВКФ, то заносится в регистр

27,а в регистр 28 записывается соответствующий ей номер цикла (в данном случае первый).

В завершении первого цикла на выходе переполнения счетчика 8 вырабатывается импульс, который проходит через элемент И 20 и увеличивает на единицу код счетчика 9.

Импульс с выхода счегчика 8 проводит тдк же элемент ИЛИ 19 и производит обнуление блокоз 4, 5, обнулены счетчики адреса в блоках памяти 31 и 32, обнуление блока 33

и коррелятора 18. Код счетчика 9 проходит через МП 17 и 16 и устанавливает новый код фазового сдвига блока 33. В этом цикле, как и в последующих, работа протекает аналогично: изменяется коэффициент фазового

сдвига блока 33, коррелятор 18 определяет ВКФ между сигналом X и еще более растянутым сигналом Y, экстремальный анализатор 26 выделяет максимальную ординату очередной ВКФ и сравнивает ее с максимальной предыдущей ВКФ и при выполнении условия превышения заносит ее в регистр 27, а в регистр 28 - соответствующий номер цикла.

Устройство работает в описанном режиме ш циклов, причем щ выбирается из соотношения (П1-1) , где макс- заранее известный максимальный коэффициент МВИ между входными сигналами. Таким образом, в течение гц циклов получены ВКФ между сигналом X и семейством растянутых по оси времени относительно сигнала Y сигналов Y. При этом исходное масштабно-временное искажение сигнала Y относительно X компенсировать шагами

величиной и при некотором (f --- (j щ-1) было скоменсировзчо с точностью до Т. При этом уровень корреляции сигналами X и Y стал отличаться от истинного не более чем на 3 дБ, а максимум

)-й ВКФ превысил максимум всех остальных ВКФ.

К моменту поступления на вход счетчика 9 п-го импульса с выхода элемента И 20 в регистре 27 хранится наибольший из ряда

максимумов ВКФ. т.е. максимум ВКФ цикла, в котором МВИ было скомпенсировано с точностью до Т, а в регистре 28 - номер этого цикла. При этом номер цикла совпадает с кодом, который управляет бло«ом фазового сдвига 33 в том же цикле.

Емкость счетчика 9 равна щ. По окончании (щ-1)-го цикла работы с выхода элемента И 20 поступает импульс, который переполняет счетчик 9. При этом счетчик 9

переходит в нулевое состояние, а импульс с его выхода устанавливает триггер 12 в единичное состояние. Благодаря этому закрывается элемент И 20, открывается элемент И 21 и МП 17 переключается во второе состояние, при котором на его выход проходит код с второго входа. С этого момента начинается второй этап работы устройства.

На этом этапе производится уточнение значения коэффициента, компенсирующего

таких шагов. Как и на первом

МВИ, с учетом того, что истинный коэффициент МВИ может отличаться от найденного на первом этапе р J не более чем на . Уточнение производится шагами Д , для чего требуется П2

2 АЯ/2 ЪФГ

этапе, поиск значения коэффициента МВИ производится путем изменения коэффициента фазового сдвига блока 33. При этом коэффициент фазового сдвига на выходе блока 33 изменяется вокруг значения J шагами . В первом цикле

второго этапа ( ) коэффициент

фазового сдвига равен (1 + j + . В сумматоре-вычитателе 25 номер I цикла второго этапа, соответствующий коду на выходе счетчика 10, складывается со значением j, хранящимся после первого этапа в регистре 28. Чтобы обеспечить меньший, чем на первом этапе шаг , вес кода счетчика 10 меньше веса кода, хранимого в регистре 28, в Л2 д / раз. Взвешивание кода 1

счетчика 10 производится в сумматоре-вычитателе 25, Емкость счетчика 10 циклов второго этапа равна П2/2,

Работа устройства на втором этапе, как и на первом, протекает циклами. В первых П2/2 циклах второго этапа по окончании каждого цикла импульс с выхода переполнения счетчика 8 через открытый элемент И 21 поступает на счетчик 10. Код состояния 1 счетчика 10 с соответствующим весом поступает на вход сумматора-вычитателя 25, работающего в режиме сложения благодаря поступающему на управляющий вход последнего уровня логической единицы с прямого выхода триггера 13. На другой вход сумматора-вычитателя 25 с выхода регистра 28 поступает код j номера цикла максимальной ВКФ, найденной на первом этапе. С выхода сумматора-вычитателя 25 код, определяющий коэффициент фазового сдвига, через МП 17 и 16 поступает на управляющий вход блока 33. Благодаря этому фазовый сдвиг блоком 33 становится равным (1 + +J + III ). Коррелятор 18определяет ВКФ выборки входных реализаций, записанных в блоках памяти 31 и 32. Экстремальный анализатор 26 выделяет максимальную ординату очередной ВКФ, а блок сравнения 30 сравнивает ее с ординатой, хранящейся в регистре 27, и по его импульсу в регистр 27 заносится максимальная из множества вычисленных за П2/2 циклов ординат ВКФ, а в регистр 29 импульс с выхода блока сравнения 30 через открытый элемент

И 24 записывает код с выхода сумматора- вычитателя 25.

По окончании первых пг/2 циклов второго этапа счетчик 10 переполняется импульсами с выхода элемента И 21, импульс с его выхода поступает на счетный вход триггера 13, и последний переключается в единичное состояние. Сигнал с его прямого выхода устанавливает арифметический блок

25 в режим вычитания. Благодаря этому на следующих п2/2 циклах второго этапа коэффициент фазового сдвига изменяется в пределах (1 + j + ||| Д). В остальном работа устройства протекает аналогично

первым П2/2 циклам второго этапа. По окончании второго этапа в регистре 29 хранится код, определяющий коэффициент фазового сдвига цифровых отсчетов, при котором МВИ скомпенсировано с точностью

. После последнего цикла второго этапа счетчик 10 снова переполняется и возвращает триггер 13 в нулевое состояние. Сигнал с выхода триггера 13 поступает на счетный вход триггера 14 и устанавливает

его в единичное состояние. Установление триггера 14 в единичное состояние приводит к открыванию элемента И 22, а МП 16 переключается в такое состояние, что пропускает код регистра 29 на свой выход. Теперь

фазовый сдвиг блоком 33 осуществляется тот, который необходим для компенсации его МВИ.

Результаты измерения ВКФ поступают теперь от коррелятора 18 на выход устройства через открытый элемент И 22 и могут использоваться для последующего анализа до тех пор, пока значение коэффициента МВИ не изменится или необходимо произвести анализ следующих входных сигналов.

Когда это произойдет, следует подать сигнал запуска и устройство в течение щ+п2 циклов настроится на новое значение коэффициента МВИ.

Устройство может работать и при противоположном знаке МВИ. В дальнейшем работа устройства аналогична.

Рассмотрим работу отдельных элементов устройства.

Блоки 4 (5) (фиг.2} работают следующим

образом. Как следует из описания работы основное назначение их выработать комплексные цифровые отсчеты с учетом того, что используется один АЦП в канале обработки.

На информационные входы устройства поступает сигналы на промежуточной частоте WnP2, которая удовлетворяет следующему-соотношению ШпР2 5: До, где Дш- полоса принимаемого сигнала. Аналоговые

операции переноса на промежуточную высоту 6UhP2 на фиг.1 не показаны.

В АЦП 2, 3 устройства осуществляется преобразование сигналов из аналоговой формы в цифровую с частотой дискретизации ft 4 Эти цифровые отсчеты и поступают на вход блока фазового размножения сигналов. Блох фазового размножения сигналов работает по следующему алгоритму: четные выборки относятся к синусоидальной составляющей, нечетные к косинусоидальной; знаки четных выборок синусоидальной составляющей и нечетных косинусоидальной составляющей изменяются на обратные.

Изменение знаков осуществляется на элементах 37-41, а управление на основании триггеров 34, 44 и элементов И 35 и 36. Следовательно, на первом выходе блока, т.е. коды, снимаемые с выхода регистра 42, образуют косинусоидальную составляющую, а коды, снимаемые с второго регистра 43 и подаваемые на второй выход блока, образуют синусоидальную составляющую,

Блок фазового сдвига 33 (фиг.З) работает следующим образом.

Как следует из описания работы устройства, назначение блока 33 сдвиг фазы принимаемого сигнала. Известно, что указанное изменение фазы комплексного сигнала в цифровой форме можно осуществить путем умножения каждого выборочного, т.е. поступающего значения А Аехр {J Фь } Ас+ +|AS этого сигнала на комплексное число В Вехр {J Вс+ jBs, определяющего величину изменения (поворота) фазы . Поэтому все операции выполняются комплексным умножителем, формируемым произведение АВ (AcBc-AsBs) + j (AcBc+AsBc). Однако, как следует из описания работы устройства, фаза должна постоянно изменяться (или увеличиваться, или уменьшаться) в процессе изменения т, где т 1N.

Процесс работы блока следующей. При поступлении на вход обнуления блока импульса счетчик 54 обнуляется и в дальнейшем начинает подсчет тактовых импульсов. Таким образом, на выходе счетчика 54 постоянно вырабатывается код т. Этот код умножается в перемножителе 49 с кодом управления, который определяет не что иное,как ы (). Код m () поступает на узлы преобразователя 50 и 51, которые могут быть выполнены в виде постоянного запоминающего устройства и на выходе узла 50 вырабатывается код cos m () , а на выходе узла 51 - код sin m (). В дальнейшем коды с входов блока и с выходов преобразователя 50 и 51 перемножаются в комплексном перемножителе на умно жителях 45-48, сумматоре 53 и еычигэтеле 52. Цифровые последовательности со сдвинутыми фазовыми приращениями выдаются на выход блока.

Коррелятор 18 (фиг.4) работает следующим образом.

При поступлении импульса на вход запуска триггер 55 устанавливается в единич0 ное состояние. При поступлении импульса на вход обнуления, а он (т.е. первый из них) совпадаете импульсом за пуска, производит обнуление делителя 58 и устанавливает триггер 56 в нулевое состояние. Установле5 ние триггера 55 в единичное состояние разрешает работу второго 61 и третьего 62 блоков элементов И. Цифровые комплексные отсчеты, поступающие на вторые и третьи входы коррелятора проходят через

0 открытые блоки элементов И 61 и 62, через блоки элементов ИЛИ 64 и 65. С выхода блока элементов ИЛИ 64 комплексные цифровые отсчеты поступают на регистр 66, который имеет М отводов, где М - число -

5 вычисляемых ординат ВКФ. Цифровые ком- 9г1 плексные отсчеты с выходов регистра 66 и с выхода блока элементов ИЛИ 65 перемножаются в блоке перемножения 67 (состоящий из комплексных перемножителей).

0 Результаты перемножения накапливаются в блоке 68. На выходе блока накопления 68 по окончании цикла накопления получается отсчет ординат ВКФ, как корень квадратный из суммы квадратов действительной и

5 мнимой составляющей. Так как триггер 561 находится в нулевом состоянии, то регистр 7 69 включен в режим параллельного приема информации. По окончании накопления на выходе делителя 58 получается импульс, по

0 которому в регистр 69 записываются отсчеты ординат ВКФ с выходов блока 68, триггер 55 устанавливается в нулевое состояние, а триггеры 56 и 57 в единичное состояние. Установление триггера 57 в единичное со5 стояние разрешает работу элемента И 70, в результате чего тактовые импульсы проходят на синхровход последовательного сдвига информации регистра 69 и на вход делителя 59, коэффициент деления которого

0 равен М. При появлении импульса на выходе делителя 59 триггер 57 устанавливается в нулевое состояние. Цифровые отсчеты с выхода регистра 69 выдаются на выход коррелятора. В дальнейшем работа коррелято5 ра аналогична с той лишь разницей, что установление триггера 55 в нулевое состояние приводит к открыванию блоков элементов И 60 и 63 и в дальнейшем на обработку поступают цифровые комплексные отсеты с первых и четвертых входов коррелятора.

Синхронизация элементов устройства осуществляется импульсами, вырабатываемыми генератором. При необходимости они могут задерживаться элементами задержки (на фиг.1 не показаны).

Формула изобретения 1. Устройство для определения взаимной корреляционной функции, содержащее генератор тактовых импульсов, два аналого-цифровых преобразователя, два Делителя частоты, три счетчика, четыре триггера, три мультиплексора, коррелятор, пять элементов И, сумматор-вычитатель, блок определения максимального, три регистра, блок сравнения и два блока памяти, причем вход запуска генератора тактовых импульсов соединен с входами установки в О с первого по четвертый триггеров и является входом запуска устройства, выход генератора faKTOBbtx импульсов соединен с входами первого и второго дел итёлей частоты, выход второго делителя частоты соединен с первым информационным входом первого мультиплексор, управляющий вход которого соединен с первым входом первого элемента И и с прямым выходом первого триггера, а выход - с синхровхода- ми первого и второго блоков памяти, второй информационный вход первого мультиплексора соединен с выходом первого делителя частоты и с синхровходами первого и второго аналого-цифровых преобразователей, информационные входы которых являются соответственно первым и вторым информационными входами устройства, выходы ко- синусоидальной и синусоидальной составляющих второго блока памяти соединены соответственно с первым и вторым информационными входами коррелятора, выход которого соединен с входом блока определения максимального и с первым входом второго элемента И, выход которого является выходом устройства, а второй вход соединен с управляющим входом второго мультиплексора и с прямым выходом четвертого триггера, инверсный выход которого соединен с первым входом третьего элемента И, а вход установки в 1 - с входом задания режима сумматора-вычитателя и с прямым выходомтретьего триггера, вход установки в 1 которого соединен с выходом переполнения первого счетчика, информационный выход которого соединен с первым входом сумматора-вычитателя, а счетный вход - с выходом четвертого элемента И, первый вход которого соединен с управляющим входом третьего мультиплексора и с прямым выводом второго триггера, инверсный выход которого соединен с вторым входом первого элемента И и с первым входом пятого элемента И, а вход установки в 1 второго триггера - с выходом переполнения второго счетчика, информационный

выход которого соединен с первым информационным входом третьего мультиплексора, а счетный вход - с выходом первого элемента И, второй вход которого соединен с вторым входом четвертого элемента И, с

0 входом установки в 1 первого триггера и с выходом переполнения третьего счетчика, счетный вход которого соединен с выходом первого мультиплексора, выход первого регистра соединен с первым входом блока

5 сравнения, второй вход которого соединен с выходом блока определения максимального, а выход - с вторыми входами пятого и третьего элементов И, выходы которых соединены соответственно с синхровходэми

0 второго и третьего регистров, выход второго регистра соединен с вторым входом сумматора-вычитателя, выход которого соединен с вторым информационным входом третьего мультиплексора, выход которого соединен с

5 вторым информационным входом второго мультиплексора, второй информационный вход которого соединен с выходом третьего регистра, отличающееся тем. что, с целью повышения быстродействия, в него

0 дополнительно введены два блока формирования фазовых квадратурных составляющих, блок фазового сдвига и элемент ИЛИ, первый вход которого соединен с выходом переполнения третьего счетчика, а второй

5 вход - с входами обнуления первого, второго и третьего счетчиков, с входом запуска коррелятора и подключен к входу запуска устройства, вход обнуления коррелятора соединен с выходом элемента ИЛИ, с входами

0 обнуления первого и второго блоков формирования фазовых квадратурных составляющих, с входами обнуления первого и второго блоков памяти и с входом обнуления блока фазового сдвига, вход задания дискрета

5 фазового сдвига которого соединен с выходом второго мультиплексора, а первый и второй выходы - с первым и вторым информационными входами второй группы коррелятора, первый и второй входы блока

0 фазового сдвига соединены соответственно с косинусоидальной и синусоидальной составляющими первого блока памяти, первый и второй информационные входы которого соответственно соединены с

5 третьим и четвертым информационными входами второй группы коррелятора и соответственно с первым и вторым выходами первого блока формирования фазовых квадратурных составляющих, информационный вход которого соединен с выходом первого

аналого-цифрового преобразователя, а тактовый вход - с выходом первого мультиплексора, с тактовым входом блока фазового сдвига и с тактовым входом второго блока формирования фазовых квадратурных составляющих, информационный вход которого соединен с выходом второго аналого-цифрового преобразователя, а первый и второй выходы соединены соответственно с третьим и четвертым информационным входами первой группы коррелятора и с одноименными информационными входами второго блока памяти, выход блока определения максимального соединен с информационным входом первого регистра, синхровход которого соединен с выходом блока сравнения, информационный вход второго регистра соединен с информационным выходом второго счетчика информационный вход третьего регистра соединен с выходом сум- матора-вычитателя.

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок формирования фазовых квадратурных составляющих содержит два триггера, четыре элемента И, два злемента НЕ. два регистра и элемент ИЛИ, первый вход которого соединен с выходом первого элемента И, второй вход - с выходом второго элемента И, а выход - со знаковым разрядным входом первого регистра и с входом первого элемента НЕ, выход которого соединен со знаковым разрядным входом второго регистра, выходы первого и второго регистров являются одноименными выходами блока, синхровход второго регистра соединен с выходом третьего элемента И, а информационный разрядный вход соединен с информационным разрядным входом первого регистра и является информационным разрядным входом блока, второй вход первого элемента И соединен с входом второго элемента НЕ и является входом знакового разряда блока, выход второго элемента НЕ соединен с первым входом второго элемента И, второй вход которого соединен с прямым выходом первого триггера, инверсный выход которого соединен с вторым входом первого элемента И, вход установки в Г первого триггера соединен с инверсным выходом второго триггера и с первым входом четвертого элемента И, а вход установки в О соединен с входом установки в О второго триггера и является входом обнуления блока, вход установки второго триггера соединен с первыми входами третьего и четвертого элементов И и является тактовым входом блока, прямой выход второго триггера соединен с вторым входом третьего элемента И, выход четвертого элемента И соединен с синхровходом

первого регистра, информационный раз рядный вход блока и вход знакового разряда блока образуют информационный вход блока.

3, Устройство по п.1, о т л и ч а ю щ е ес я тем, что блок фазового сдвига содержит пять перемножителей, вычитатель, сумматор, узел вычисления косинуса, узел вычисления синуса и счетчик, вход обнуления

0 которого является входом обнуления блока счетный вход счетчика является тактовым входом блока, а выход соединен с первым входом первого перемножителя, второй вход которого является входом задания ди5 скрета фазового сдвига блока, а выход соединен с входами узла вычисления синуса и узла вычисления косинуса, выход узла вычисления косинуса соединен с первыми входами второго и третьего перемножите0 лей, первый вход третьего перемножителя является первым информационным входом блока, а выход соединен с входом уменьшаемого вычитателя, выход которого является первым выходом блока, а вход вычитаемого

5 соединен с выходом четвертого перемножителя, первый вход которого является вторым информационным входом блока и соединен с вторым входом второго перемножителя, а второй вход соединен с выходом узла вычис0 ления синуса и с первым входом четвертого перемножителя, второй вход которого подключен к первому информационному входу блока, а выход соединен с первым входом сумматора, второй которого соединен

5 с выходом второго перемножителя, а выход является выходом блока.

4. Устройство поп.1,отличающее- с я тем, что коррелятор содержит три триггера, два делителя, четыре блока элементов

0 И, два блока элементов ИЛИ, два регистра, блок перемножителей, блок накопления и элемент И, первый вход которого соединен с информационным входом первого делителя и является тактовым входом коррелятора,

5 вход обнуления первого делителя соединен с входом установки в О первого триггера и является входом обнуления коррелятора, вход установки в 1 первого триггера соединен с выходом первого делителя, с вхо0 дом установки в О второго триггера, с синхровходом параллельной записи первого регистра и с входом установки в 1 третьего триггера, вход ус гановки в О которого соединен с выходом второго делителя,

5 вход обнуления которого соединен с инверсным выходом третьего триггера, прямой выход которого соединен с вторым входом первого элемента И. выход которого соединен с информационным входом второго делителя и с синхровходом последовательного сдвига первого регистра выход которого является выходом коррелятора, а вход разрешения последовательного сдвига соединен с прямым выходом первого триггера, инверсный выход которого соеди- нен с входом разрешения параллельной записи первого регистра, информационные входы группы которого соединены с соответствующими выходами группы блока накопления, входы группы которого соеди- нены с соответствующими выходами группы блока перемножителей, входы первой группы которого соединены с соответствующими выходами группы второго регистра, а входы второй группы - с соответствующими выходами группы первого блока элементов ИЛИ, входы первой группы которого соединены с соответствующими выходами первого блока элементов И а входы второй группы соединены с соответствующими вы- ходами второго блока элементов И управляющий вход которого соединен с управляющим входом третьего блока элементов И и с инверсным выходом второго триггера, первый и второй входы первого блока

элементов И и первый и второй входы второго блока элементов И являются соответственно первым вторым третьим четвертым информационными входами второй группы коррелятора, управляющий вход первого блока элементов И соединен с прямым выходом второго триггера и с управляющим входом четвертого блока элементов И выходы группы которого соединены с входами первой группы блока элементов ИЛИ, а первый и второй входы четвертого блока элементов И являются соответственно третьим и четвертым информационными входами первой (руппы коррелятора первый и второй входы третьего блока элементов И являются соответственно первым и вторым информационными входами первой группы коррелятора выходы группы третьего блока элементов И соединены соответственно с входами второй группы второго блока элементов ИЛИ выходы группы которого соединены с соответствующими информационными входами фуппы второго регистра вход установки в 1 второго триггера является входом запуска коррелятора

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Цифровой коррелятор | 1990 |

|

SU1824642A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Разделитель коррелограмм | 1988 |

|

SU1506453A1 |

| Цифровой коррелятор | 1990 |

|

SU1727133A1 |

| КОРРЕЛЯЦИОННОЕ УСТРОЙСТВО | 2002 |

|

RU2229156C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2011 |

|

RU2445690C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

Изобретение относится к области вычислительной техники и может быть исполь- зовано для определения значения и аргумента максимума взаимной корреляционной функции между случайными сигналами, подвергнутыми взаимному масштабно- временному искажению. Цель изобретения - повышение быстродействия Устройство содержит генератор тактовых импульсов аналого-цифровые преобразователи делители частоты, мультиплексоры, блоки памяти счетчики, триггеры, элементы И, сумматор-вычитатель, блок сравнения, блок определения максимального., регистры, коррелятор, блоки формирования фазовых квадратурных составляющих, блок фазового сдвига и элемент ИЛИ Ззп ф-лы, 4 ил

Фиг. 2

фиг.З

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

Авторы

Даты

1992-07-30—Публикация

1990-06-25—Подача