1 1

Изобретение относится к телевизионной технике и может быть использовано в приемной телевизионной алпаратуре.

Цель изобретения - повьшение помехозащищенности при одновременном упрощении устройства для выделения кадровых синхроимпульсов с обеспечением возможности работы от входного сигнала синхронизации без импульсов врезок и уравнивающих импульсов .

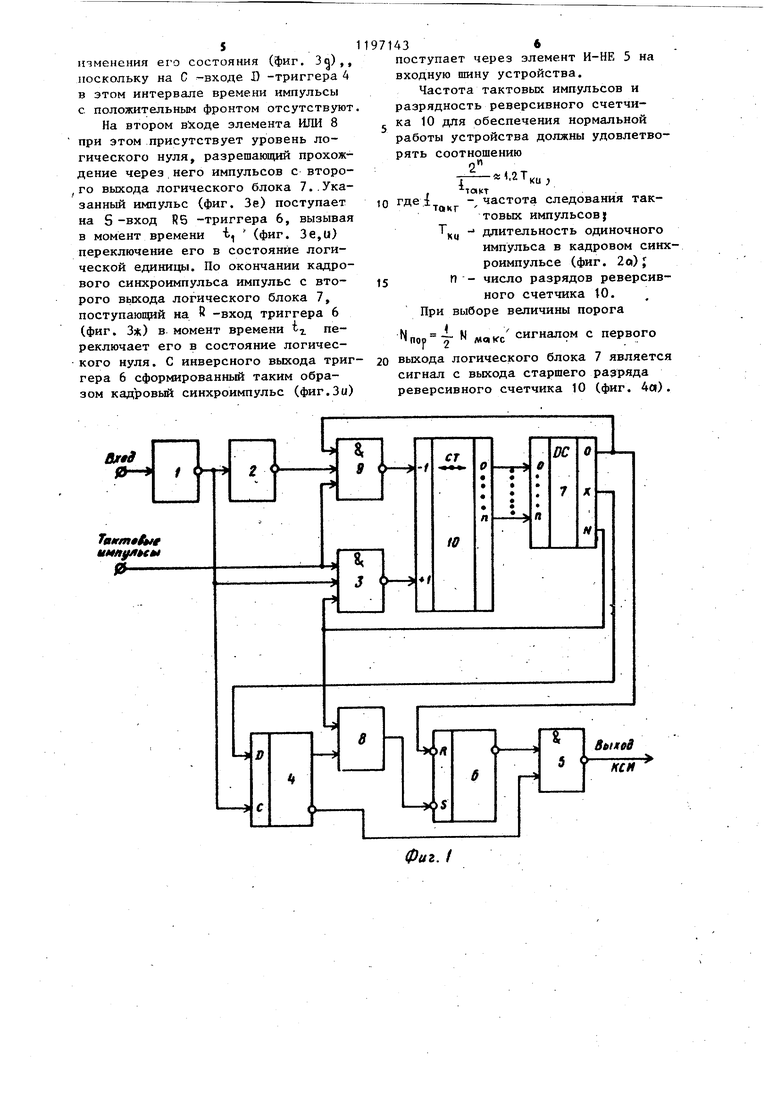

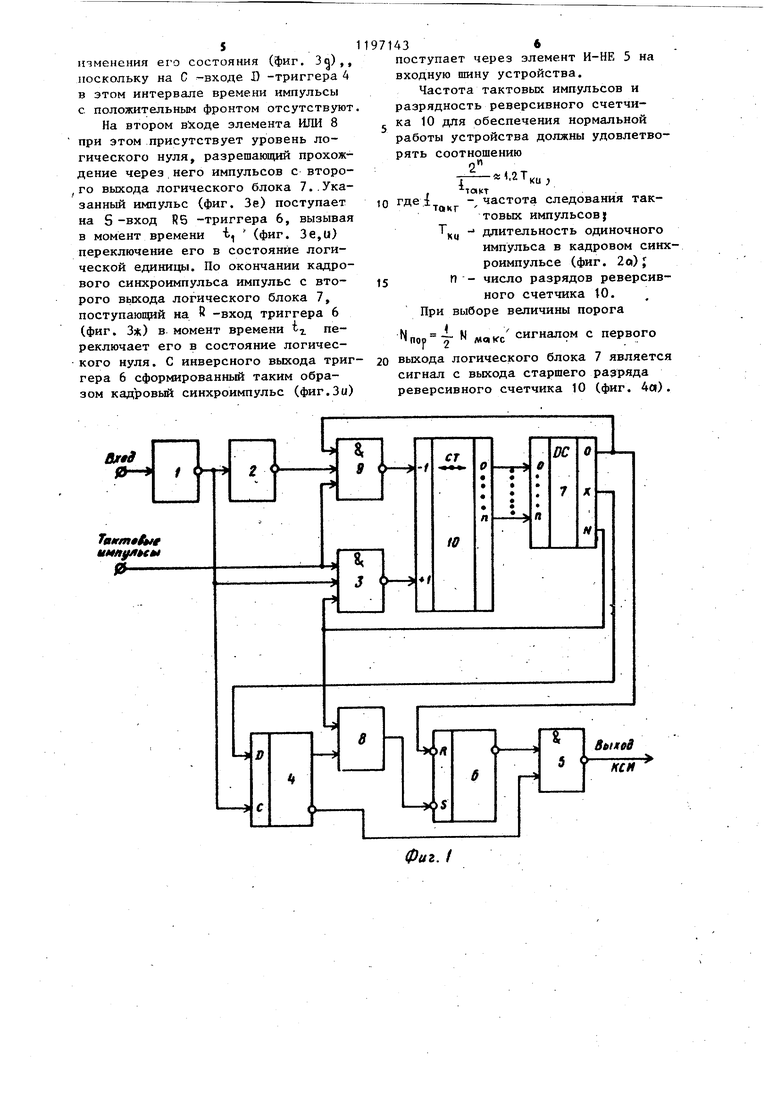

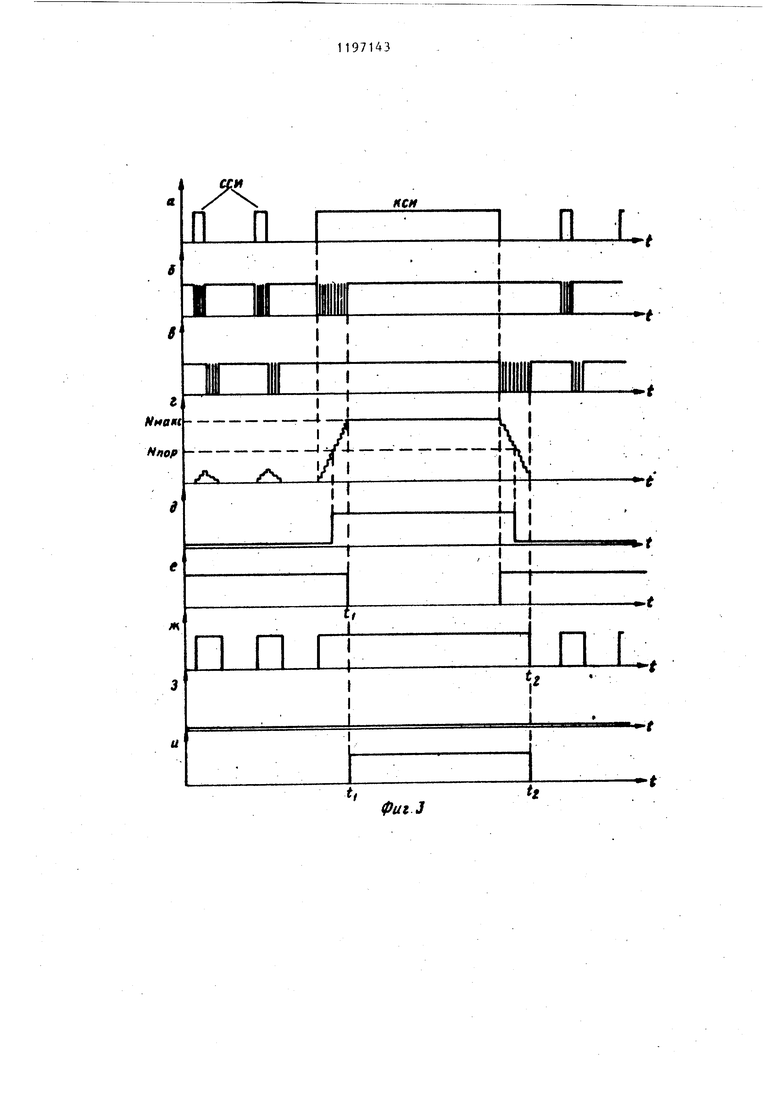

На фиг. 1 представлена структурная электрическая схема устройства для вьщеления кадровых синхроимпульсов , на фиг, 2 и 3 - временные диаграммы, поясняющие его работу; на фиг, 4 - варианты выполнения логического блока,

Устройство для выделения кадровых синхроимпульсов содержит первый инвертор 1, вход которого соединен с шиной сигнала синхронизации, а выход с входом второго инвертора 2 и первым входом первого элемента ИНЕ 3 и С -входом тактируемогоЭ-триггера 4, инверсный выход которого соединен с первым входом второго элемента И-НЕ 5, выход которого соединен с выходной шиной, Я5-триггер6, инверсный выход которого соединен с вторым входом второго элемента ИНЕ 5, логический блок 7, первый выход которого соединен с U-входом тактируемого О -триггера 4, элемент ИЛИ 8, выход которого соединен сS-входом R5 -триггера 6, выход второго инвертора 2 соединен с первым входом третьего элемента И-НЕ 9, второй вход которого соединен с вторым входом первого элемента И-НЕ 3 и шиной тактовых импульсов, третий вход соединен с вторым выходом логического блока 7 и R -входом R 5 -триггера 6, а выход соединен с входом вычитания реверсивного счетчика 10, вход сложения которого соединен с выходом первого элемента И-НЕ 3, а азрядные выходы соединены с соответствующими входами логического блока 7, прямой выход тактируемого -триггера 4 соединен с первым вхоом элемента ШШ 8, второй вход котоого соединен с третьим входом первого элемента И-НК 3 и третьим логического блока 7, Кроме того, огический блок 7 содержит инвертоы 11-1 - 11-4, цементы И-НЕ 12 и 13

97(43 I

(фиг. 4 ) и цифровые компараторы 1416 Сфиг. 4&).

Устройство для выделения кадровых синхроимпульсов работает следующим

5 образом.

Сигнал синхросмеси отрицательной полярности поступает на вход первого инвертора 1, являющегося буферным элементом и служащим для формирования сигнала с требуемой крутизной фронтов.

При поступлении на вход устройства стандартного сигнала синхронизации с импульсами врезок и уравнивающими импульсами (фиг. 2) синхроимпульсы положительной полярности с выхода первого инвертора 1 (фиг.2а) и отрицательной полярности с выхода второго инвертора 2 поступают на

20 первые входы соответственно первого 3 и третьего 9 элементов И-НЕ, на вторые входы которых поступают тактовые импульсы. При этом, в случае наличия синхроимпульса, тактовые импульсы поступают на суммирующий вход реверсивного счетчика 10 (фиг. 25), увеличивая его содержимое, а при отсутствии синхроимпульсов (паузе между ними) тактовые импульсы поступают на вычитакиций вход реверсивного счетчика 10 (фиг, 26), Изменение содержимого (состояния) реверсивного счетчика 10 условно показано на фиг. 2-2, где урооэнь N(ц соответствует модулю счета реверсивного счетчика 10,При поступлении на вход устройства строчньЕХ синхроимпульсов содержимое реверсивного счетчика увеличивается от О до (фиг, 2), после чего опять уменьшается до нуля , При счете в направлении уменьшения содержимое реверсивного счетчика 10 по достижении им состояния

Все нули на третьем выходе логического блока 7 формируется сигнал логического нуля (фиг, 2ж), который поступает на вход элемента И-НЕ 9, запрещая дальнейшее прохождение на

его выход тактовых импульсов. Тем самым исключается при работе реверсивного счетчика 10 в режиме вычитания переход его из состояния О в состояние N д,,. Аналогично осуществляет ся функционирование рассмотренных блоков при поступлении на вход устройства импульсов двойной строчной частоты с той разницей.

J

что за время действия указанных импульсов счетчик 10 достигает состояния N„1 . причем

trro ..

Н.7,,„ WcCU J

21стр

где i(,p - частота строк.

При поступлении на вход устройства кадрового синхроимпульса содержимое счетчика 10 начинает увеличиваться (интервал временив, фиг. 2г) до тех пор, пока не достигнет величины N д,д up , после чего на втором выходе логического блока 7 формируется уровень логического нуля (фиг. 2в), поступающий на вход элемента И-НЕ 3 и запрещающий дальнейшее прохождение на суммирующий Ьход реверсивного счетчика 10. тактовых импульсов (фиг. 2S).

Тем самым исключается переход счетчика 10 из состояния М;,, в состояние О при работе в режиме суммирования. В течение времени, когда содержимое счетчика 10 превышает величину и -- J.,|j , .на перWnop - 2 uafc

BOM выходе логического блока 7 формируется импульс (фиг. 2а), постпающий на J) -цход Ц -триггера 4. На его С -вход поступает сигнал синхросмес $, положительной полярности (фиг. 2а),при этом по переднему фронту импульса врезки происходит ,переход D -триггера 4 в состояние логической единицы,, а по переднему фронту импульса двойной строчной частоты (уравнивающего импульса) происходит переход D -триггера 4 в состояние логического нуля.

Таким образом, на выходе D -триггера 4 формируется кадровый синхроимпульс (фиг. 24, фронты которого жестко связаны с фронтами входного сигнала. Через элемент И-НЕ 5 сформированный кадровый синхроимпульс поступает на выходйую шИну устройства.

Формирование выходного импульса КЗ-триггером 6 не происходит (фиг.2и поскольку прохождение сигнала на его S-вход запрещается уровнем логической единицы, поступаюпщм на второй вход элемента ИЛИ 8,

Формирование логическим блоком 7 указанных сигналов осуществляется следующим образом. При поступлении на входы логического блока 7 сигнала Все единицы на выходе элемента И-НЕ 12 (фиг. 4q} формируется ,, уровень логического нуля. В случае

97143

поступления сигнала Все нули данный сигнал инвертируется инверторами 11-1 - 11-4 и поступает на входы элемента И-НЕ 13, на выходе которос го формируется уровень логического нуля. Логический блок 7 может быть выполнен также с применением цифровых компараторов (фиг.46). В этом случае число компараторов опрёделя10 ется числом дешифруемых состояний входа логического блока 7, т.е. равно трем. Входной сигнал поступает на первые входы всех трех компараторов 14-16, соединенные параллельJ5 но, а на вторые входы подаются коды чисел, при которых необходимо сформировать входной сигнал на каждом из выходов логического блока 7. В частности, на второй вход перво

20 го компаратора 14 поступает код Все единищ Г, в результате чего на выходе А В первого компаратора 14 при достижении входным сигналом логического блока 7 состояния

25 Все единицы формируется уровень логического нуля. Аналогично формируется уровень логического нуля на вькоде А S третьего компаратора 16 при достижении выходным сигналом логического блока 7 состояния Все

30 нули, а также уровень логической единицы на выходе А В второго компаратора при превьшении входным сигналом логического блока 7 величины N по в .

5

Рассмотрим работу устройства при поступлении на его вход сигнала синхронизации без импульсов врезок и уравнивающих импульсов (фиг. 3).

0 При наличии на входе устройства синхроимпульсов (фиг. За) тактовые импульсы через элемент И-НЕ 3 поступают на суммирующий вход реверсивного счетчика 10 (фиг. З), а

5 в интервале меязду синхроимпульсами - на его вычитающий вход через третий элемент И-НЕ 9 (фиг.ЗЬ). При достижении реверсивным счетчиком 10 (фиг. Зг) состояния 1 и

0 о соответственно на втором и третьем выходах логического блока 7 формируются уровни логического нуля (фиг. 3 е и ж). Положительный импульс (фиг. 3ч), формируемый на первом выходе логического блока 7 при превышении содержимым счетчика 10 величины N pop , поступает на Б -вход D-триггера 4, однако не вызывает

5 .

изменения eio состояния (фиг. Зо),,

поскольку на С входе I) -триггера 4 в этом интервале времени импульсы с положительным фронтом отсутствуют

На втором в5соде элемента ИЛИ 8 при этом присутствует уровень логического нуля, разрешающий прохождение через него импульсов с второ,го выхода логического блока 7..Указанный импульс (фиг. Зе) поступает на S -вход R5 -триггера 6, вызывая в момент времени t (фиг. Зе,и) переключение его в состояние логической единицы. По окончании кадрового синхроимпульса импульс с второго вькода логического блока 7, поступающий на R -вход триггера 6 (фиг. 3) в момент времени t переключает его в состояние логического нуля. С инверсного выхода триггера 6 сформированный таким образом кадровый синхроимпульс (фиг.Зи)

TatrmfA/f

miMlf tf

1971436

поступает через элемент И-НЕ 5 на входную шину устройства.

Частота тактовьк импульсов и разрядность реверсивного счетчика 10 для обеспечения нормальной работы устройства должны удовлетворять соотношению

,п

-«4,2Т,

1 KU J

такт

1

частота следования такгде

токг

товых импульсов}

TKUдлительность одиночного импульса в кадровом синхроимпульсе (фиг. 2о)J

П -число разрядов реверсивного счетчика tO. При выборе величины порога

IN

N

MoiKc сигналом с первого

Пор

20 выхода логического блока 7 является сигнал с выхода старшего разряда реверсивного счетчика 10 (фиг. 4о|).

Фиг. /

сен

J и fl П

KCtI

IViT

о

ппппг

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения синхроимпульсов | 1988 |

|

SU1660204A1 |

| Устройство для считывания графической информации с экрана электронно-лучевой трубки | 1989 |

|

SU1615759A1 |

| Устройство для считывания графической информации с экрана электроннолучевой трубки | 1987 |

|

SU1425736A1 |

| Устройство для формирования отрезка прямой линии на экране электронно-лучевой трубки | 1979 |

|

SU919163A1 |

| Устройство для выделения синхроимпульсов полей | 1986 |

|

SU1363533A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Формирователь стробирующего сигнала | 1977 |

|

SU680200A1 |

| Устройство управления матричным экраном | 1987 |

|

SU1518921A1 |

| Устройство управления режимом работы синхрогенератора | 1985 |

|

SU1322504A1 |

| Устройство коррекции строчной развертки | 1987 |

|

SU1515395A1 |

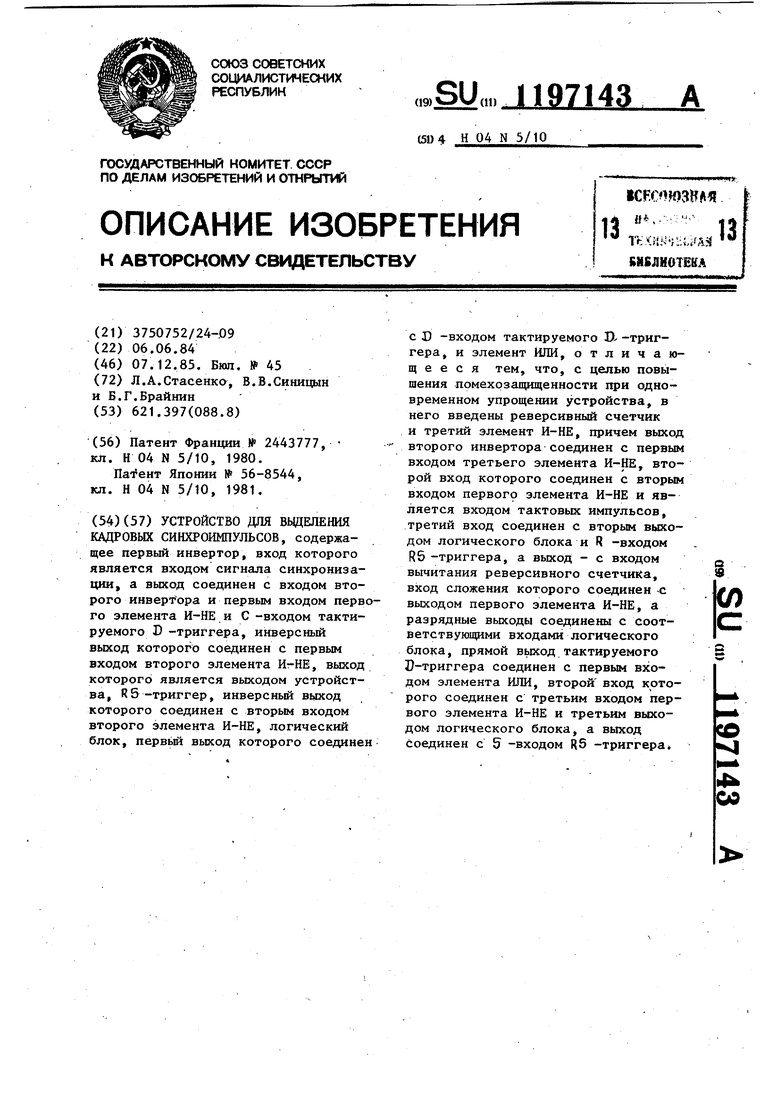

УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ КАДРОВЫХ СИНХРОИМПУЛЬСОВ, содержащее первый инвертор, вход которого является входом сигнала синхронизации, а выход соединен с входом второго инвертора и первьш входом первого элемента И-НЕ и С -входом тактируемого D -триггера, инверсный выход которого соединен с первым входом второго элемента И-НЕ, выход которого является выходом устройства, R5 -триггер, инверсный выход которого соединен с вторым входом второго элемента И-НЕ, логический блок, первьш выход которого соединен с О -входом тактируемого Д- -триггера, и элемент ШШ, отличающееся тем, что, с целью повышения помехозащищенности при одновременном упрощении устройства, в него введены реверсивный счетчик и третий элемент И-НЕ, причем выход второго инвертора соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с вторым входом первого элемента И-НЕ и является входом тактовых импульсов, третий вход соединён с вторым выходом логического блока и R -входом R5 -триггера, а выход - с входом i вычитания реверсивного счетчика, вход сложения которого соединен -с О) выходом первого элемента И-НЕ, а разрядные выходы соединены с соответствующими входами логического блока, прямой вькод тактируемого D-триггера соединен с первым входом элемента ШШ, второй вход которого соединен с третьим входом первого элемента И-НЕ и третьим выхосо дом логического блока, а выход соединен с 5 -входом RS -триггера. )u 00

1ПИП1

г

tfnaite Miu

П Л n n

irr/

JUl

ш

фиг 3

| СПОСОБ ОДНОМОМЕНТНОГО ОПРЕДЕЛЕНИЯ ДЛИНЫ ТЕЛОМЕР И КОЛИЧЕСТВА ДЕЛЕНИЙ ПОПУЛЯЦИИ ПРОЛИФЕРИРУЮЩИХ КЛЕТОК IN VITRO | 2010 |

|

RU2443777C2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-06—Подача