1

Изобретение относится к технике телевидения и может быть использовано в устройствах управления синхрогене- раторами.

Цель изобретения - повышение поме- 5 хоустойчивости и расширение функциональных возможностей.

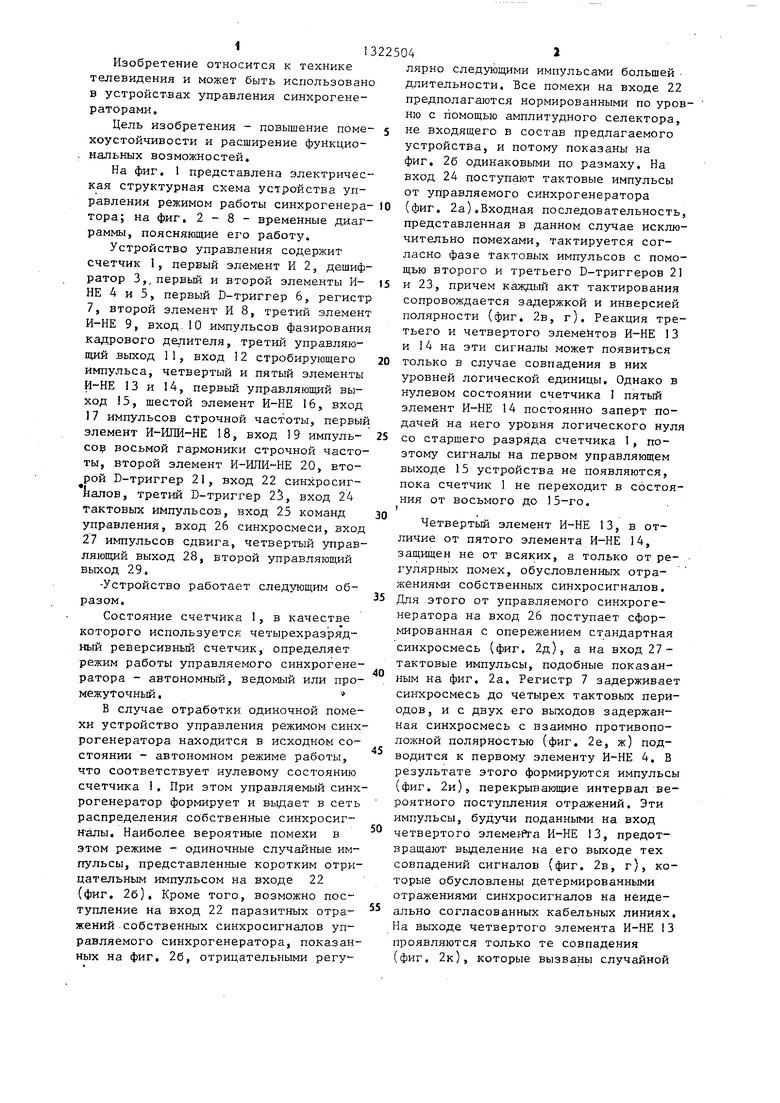

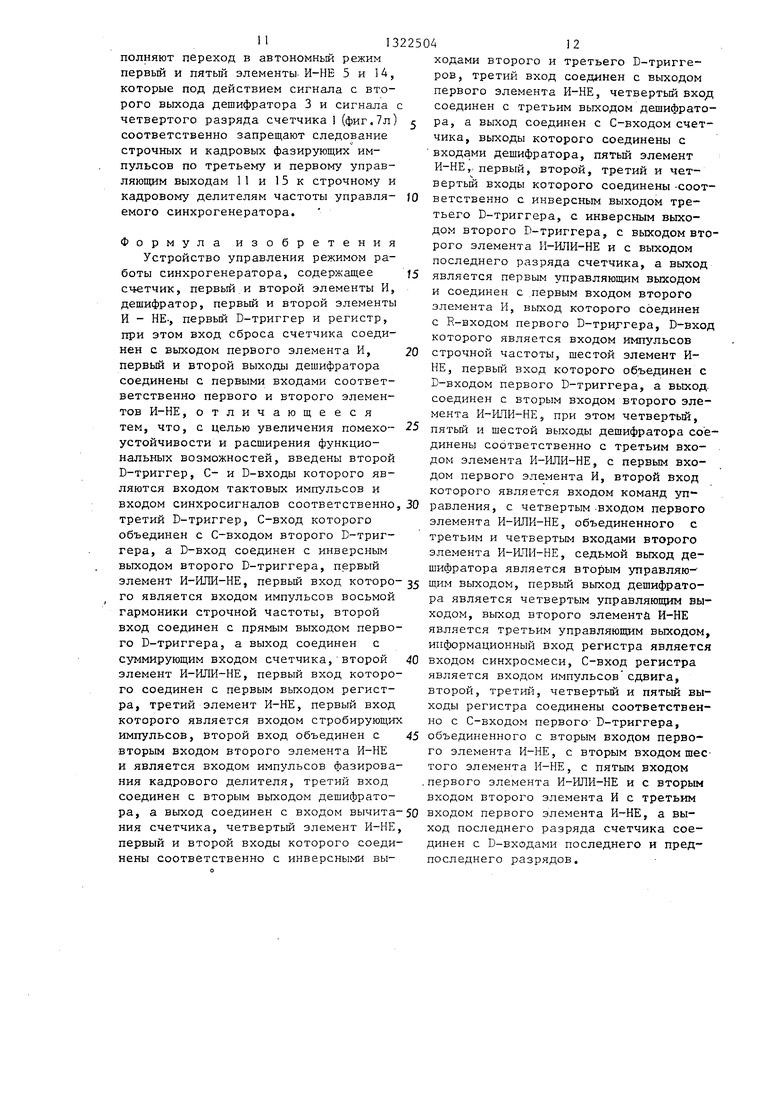

На фиг. 1 представлена электрическая структурная схема устройства уп322

15

20

25

30

равления режимом работы синхрогенера- 10 (фиг. 2а).Входная последовательность, тора; на фиг. 2 - 8 - временные диаграммы, поясняющие его работу.

Устройство управления содержит счетчик 1, первый элемент И 2, дешифратор 3,, первый и второй элементы PI- HE 4 и 5, первый D-триггер 6, регистр 7, второй элемент И 8, третий элемент И-НЕ 9, вход.10 импульсов фазирования кадрового делителя, третий управляющий выход 11, вход 12 стробирующего импульса, четвертый и пятый элементы И-НЕ 13 и 14, первый управляющий выход 5, шестой элемент И-НЕ I6, вход 17 импульсов строчной частоты, первый элемент И-РШИ-НЕ 18, вход 19 импуль- соэ восьмой гармоники строчной частоты, второй элемент И-ИЛИ-НЕ 20, второй D-триггер 21, вход 22 синхросиг- алов, третий D-триггер 25, вход 24 тактовых импульсов, вход 25 команд управления, вход 26 синхросмеси, вход 27 HNfflynbcoB сдвига, четвертый управляющий выход 28, второй управляющий выход 29.

-Устройство работает следующим образом.

Состояние счетчика 1, в качестве которого используется четырехразрядный реверсивный счетчик, определяет режим работы управляемого синхрогенератора - автономный, ведом1з1й или промежуточный .

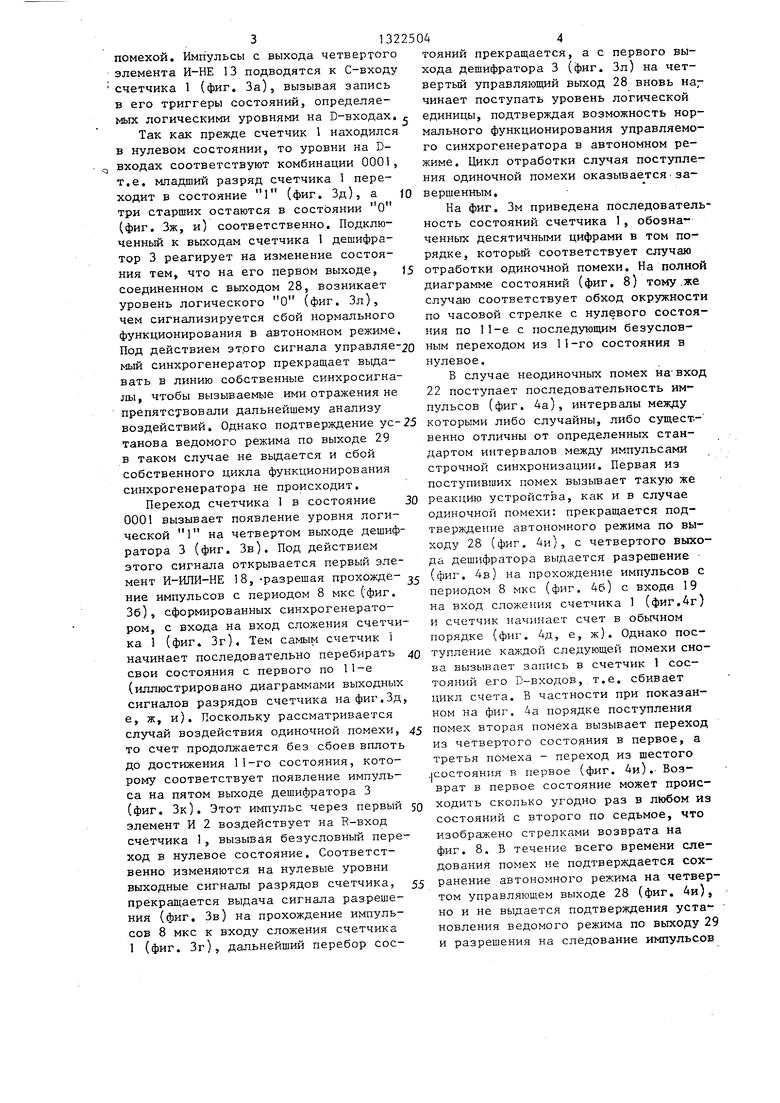

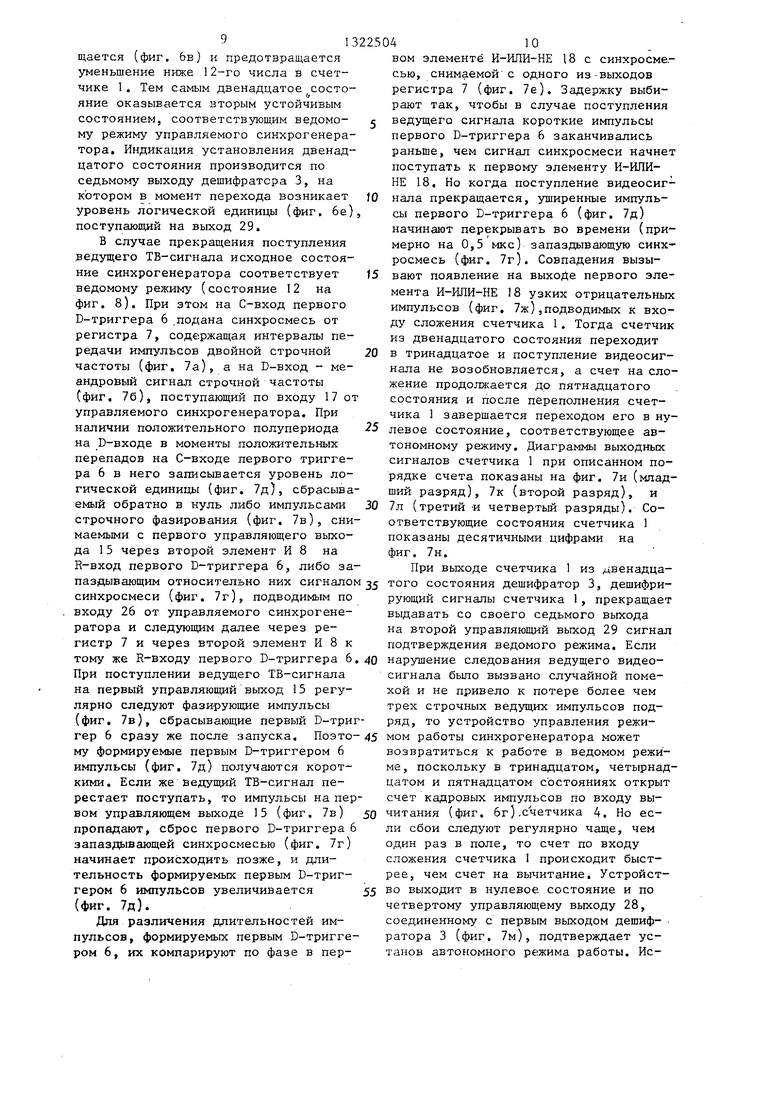

В случае отработки одиночной помехи устройство управления режимом синхрогенератора находится в исходном состоянии - автономном режиме работы, что соответствует нулевому состоянию счетчика I. При этом управляемый синх- рогенератор формирует и вьщает в сеть распределения собственные синхросиг- Н алы. Наиболее вероятные помехи в этом режиме - одиночные случайные импульсы, представленные коротким отрицательным импульсом на входе 22 (фиг. 2б). Кроме того, возможно поступление на вход 22 паразитных отражений -собственных синхросигналов управляемого синхрогенератора, показанных на фиг. 2б, отрицательными регу35

40

45

50

55

представленная в данном случае исключительно помехами, тактируется согласно фазе тактовых импульсов с помощью второго и третьего D-триггеров 21 и 23, причем каждый акт тактирования сопровождается задержкой и инверсией полярности (фиг. 2в, г). Реакция третьего и четвертого элементов И-НЕ 13 и 14 на эти сигналы может появиться только в случае совпадения в них уровней логической единицы. Однако в нулевом состоянии счетчика 1 пятый элемент И-НЕ 14 постоянно заперт подачей на него уровня логического нуля со старшего разряда счетчика 1, поэтому сигналы на первом управляющем выходе 15 устройства не появляются, пока счетчик 1 не переходит в состояния от восьмого до 15-го. т

Четвертый элемент И-НЕ 13, в отличие от пятого элемента И-НЕ 14, защищен не от всяких, а только от регулярных помех, обусловленных отражениями собственных синхросигналов. Для .этого от управляемого синхрогенератора на вход 26 поступает сформированная с опережением стандартная синхросмесь (фиг. 2д), а на вход 27- тактовые импульсы, подобные показанным на фиг. 2а. Регистр 7 задерживает синхросмесь до четырех тактовых периодов, и с двух его выходов задержанная синхросмесь с взаимно противоположной полярностью (фиг. 2е, ж) подводится к первому элементу И-НЕ 4. В результате этого формируются импульсы (фиг. 2и), перекрываюш 1е интервал вероятного поступления отражений. Эти импульсы, будучи поданными на вход четвертого элемента И-НЕ 13, предотвращают выделение на его выходе тех совпадений сигналов (фиг. 2в, г), которые обусловлены детермированными отражениями синхросигналов на неидеально согласованных кабельных линиях. На выходе четвертого элемента И-НЕ 13 проявляются только те совпадения (фиг, 2к), которые вызваны случайной

о

5

3225041

лярно следующими импульсами большей длительности. Все помехи на входе 22 предполагаются нормированными по уровню с помощью амплитудного селектора, не входящего в состав предлагаемого устройства, и потому показаны на фиг. 2б одинаковыми по размаху. На вход 24 поступают тактовые импульсы от управляемого синхрогенератора

(фиг. 2а).Входная последовательность,

представленная в данном случае исключительно помехами, тактируется согласно фазе тактовых импульсов с помощью второго и третьего D-триггеров 21 и 23, причем каждый акт тактирования сопровождается задержкой и инверсией полярности (фиг. 2в, г). Реакция третьего и четвертого элементов И-НЕ 13 и 14 на эти сигналы может появиться только в случае совпадения в них уровней логической единицы. Однако в нулевом состоянии счетчика 1 пятый элемент И-НЕ 14 постоянно заперт подачей на него уровня логического нуля со старшего разряда счетчика 1, поэтому сигналы на первом управляющем выходе 15 устройства не появляются, пока счетчик 1 не переходит в состояния от восьмого до 15-го. т

Четвертый элемент И-НЕ 13, в отличие от пятого элемента И-НЕ 14, защищен не от всяких, а только от регулярных помех, обусловленных отражениями собственных синхросигналов. Для .этого от управляемого синхрогенератора на вход 26 поступает сформированная с опережением стандартная синхросмесь (фиг. 2д), а на вход 27- тактовые импульсы, подобные показанным на фиг. 2а. Регистр 7 задерживает синхросмесь до четырех тактовых периодов, и с двух его выходов задержанная синхросмесь с взаимно противоположной полярностью (фиг. 2е, ж) подводится к первому элементу И-НЕ 4. В результате этого формируются импульсы (фиг. 2и), перекрываюш 1е интервал вероятного поступления отражений. Эти импульсы, будучи поданными на вход четвертого элемента И-НЕ 13, предотвращают выделение на его выходе тех совпадений сигналов (фиг. 2в, г), которые обусловлены детермированными отражениями синхросигналов на неидеально согласованных кабельных линиях. На выходе четвертого элемента И-НЕ 13 проявляются только те совпадения (фиг, 2к), которые вызваны случайной

помехой. Импульсы с выхода четвертого элемента И-НЕ I3 подводятся к С-входу счетчика 1 (фиг. За), вызывая запись в его триггеры состояний, определяемых логическими уровнями на D-входах. ,

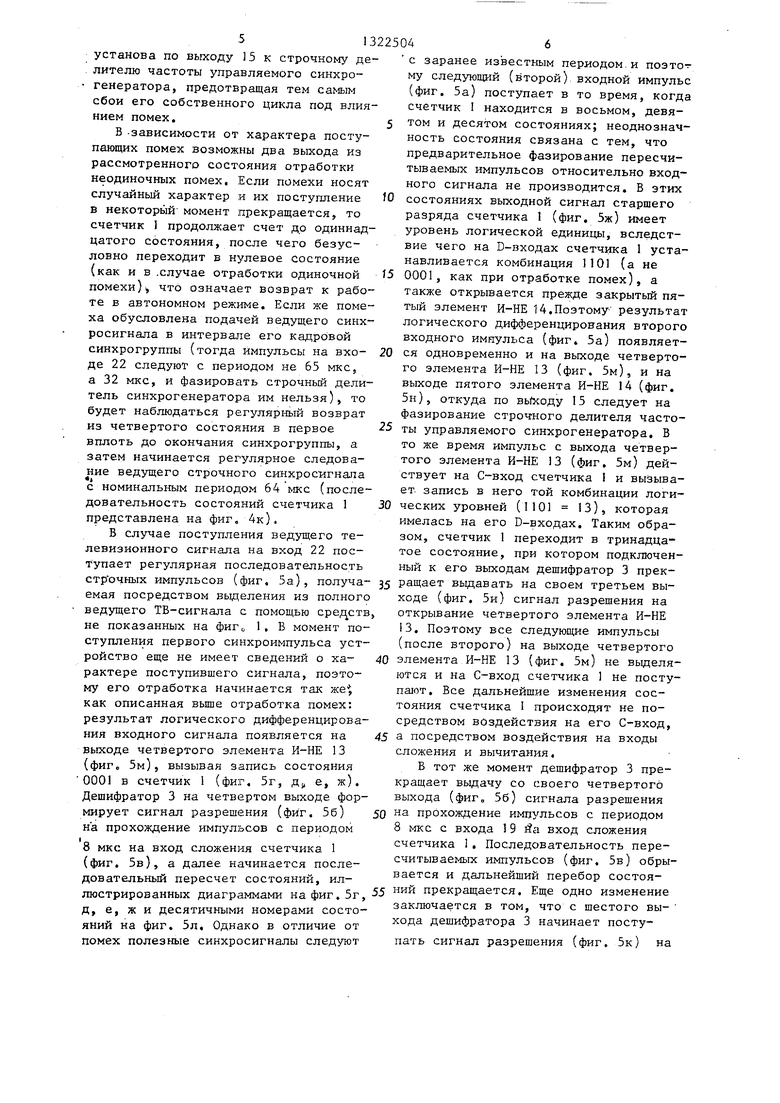

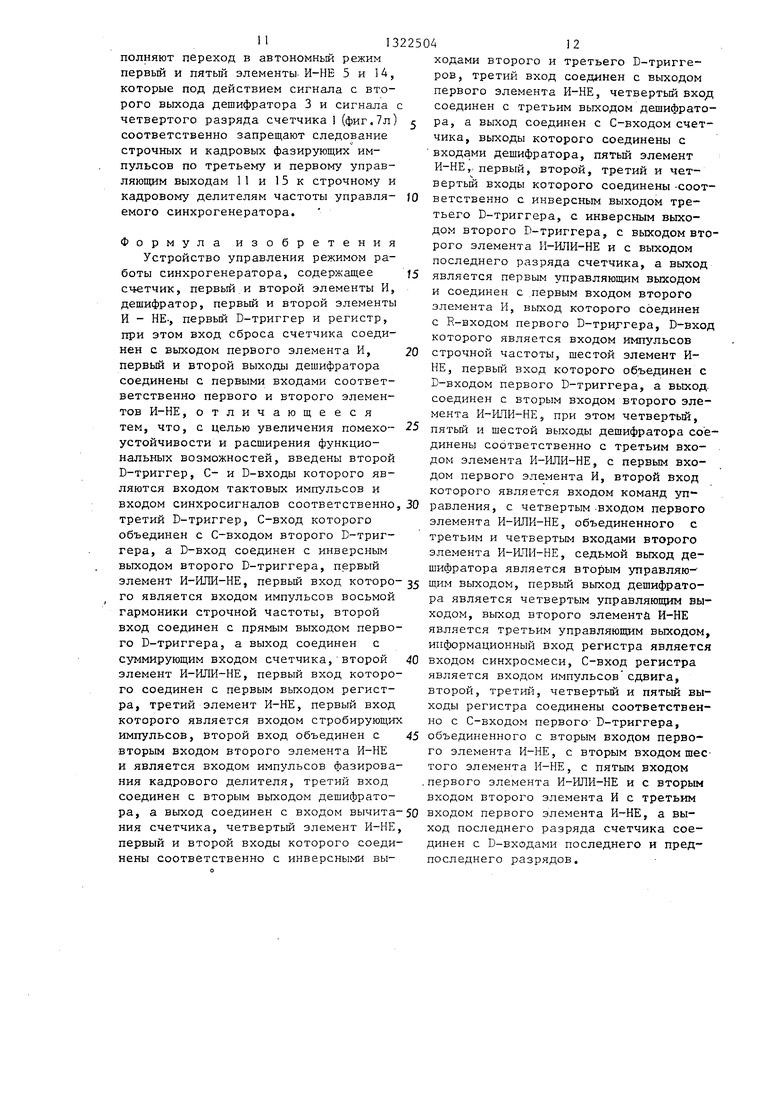

Так как прежде счетчик 1 находился в нулевом состоянии, то уровни на D- входах соответствуют комбинации 0001, т.е. мпадший разряд счетчика 1 переходит в состояние 1 (фиг. Зд), а 10 три старших остаются в состоянии О (фиг. Зж, и) соответственно. Подключенный к выходам счетчика 1 дешифратор 3 реагирует на изменение состояния тем, что на его первом выходе, 15 соединенном с выходом 28, возникает уровень логического О (фиг. 3л), чем сигнализируется сбой нормального функционирования в автономном режиме, Под действием этого сигнала управляе-20 мый синхрогенератор прекращает выдавать в линию собственные синхросигналы, чтобы вызываемые ими отражения не препятствовали дальнейшему анализу воздействий. Однако подтверждение ус-25 танова ведомого режима по выходе 29 в таком случае не выдается и сбой собственного цикла функционирования синхрогенератора не происходит.

Переход счетчика 1 в состояние 30 0001 вызывает появление уровня логической 1 на четвертом выходе дешифратора 3 (фиг. Зв). Под действием этого сигнала открывается первый элемент И-ИЛИ-НЕ 18, -разрешая прохожде- - ние импульсов с периодом 8 мкс ( фиг. Зб), сформированных синхрогенерато- ром, с входа на вход сложения счетчика I (фиг. Зг). Тем самым счетчик 1 начинает последовательно перебирать 0 свои состояния с первого по 11-е (иллюстрировано диаграммами выходных сигналов разрядов счетчика нафиг.Зд, е, ж, и). Поскольку рассматривается случай воздействия одиночной помехи, 45 то счет продолжается без сбоев вплоть до достижения 1 1-го состояния, которому соответствует появление импульса на пятом вьгходе дешифратора 3 (фиг. Зк). Этот импульс через первый 50 элемент И 2 воздействует на R-вход счетчика 1, вызывая безусловный переход в нулевое состояние. Соответственно изменяются на нулевые уровни выходные сигналы разрядов счетчика, 55 прекращается выдача сигнала разрешения (фиг. Зв) на прохождение импульсов 8 МКС к входу сложения счетчика 1 (фиг. Зг), дальнейший перебор состояний прекраш,ается, а с первого выхода дешифратора 3 (фиг. 3л) на четвертый управляющий выход 28 вновь на- чинает поступать уровень логической единицы, подтверждая возможность нормального функционирования управляемого синхрогенератора в автономном режиме. Цикл отработки случая поступления одиночной помехи оказывается завершенным.

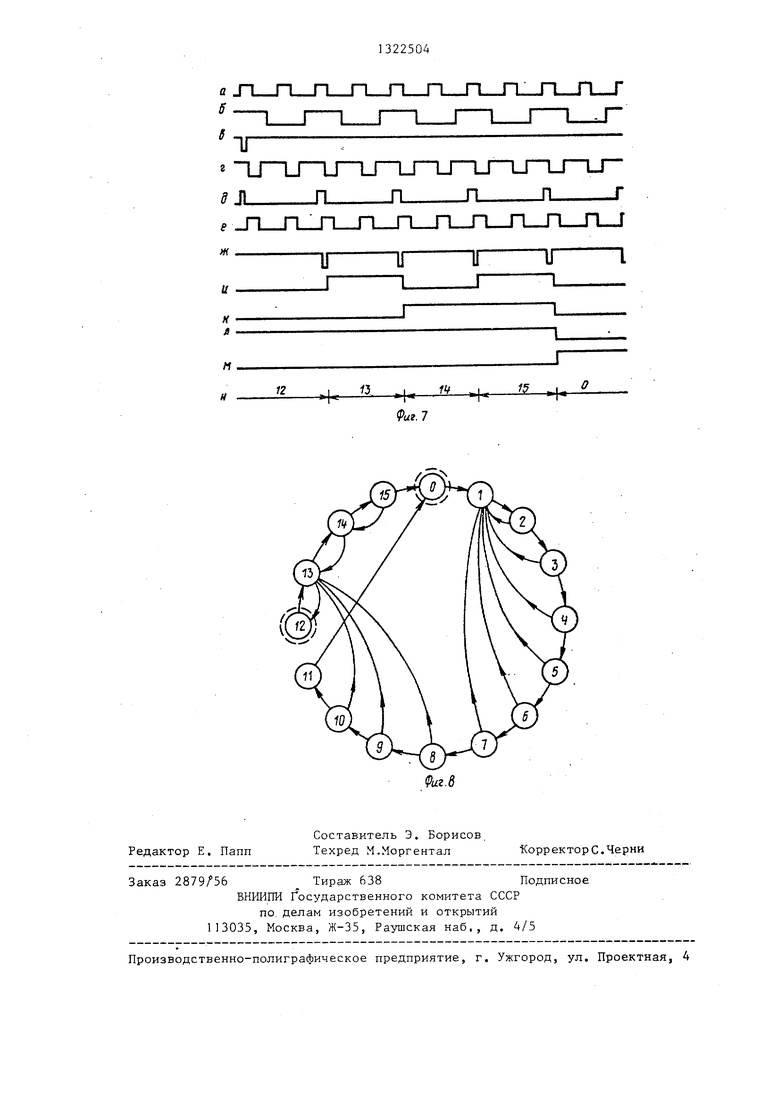

На фиг. 3м приведена последовательность состояний счетчика 1, обозначенных десятичными цифрами в том порядке, который соответствует случаю отработки одиночной помехи. На полной диаграмме состояний (фиг. 8) тому.же случаю соответствует обход окружности по часовой стрелке с нулевого состояния по 1 1-е с последующим безусловным переходом из 11-го состояния в нулевое.

В случае неодиночных помех на вход 22 поступает последовательность импульсов (фиг. 4а), интервалы между которыми либо случайны, либо сущест-- венно отличны от определенных стандартом интервалов между импульсами строчной синхронизации. Первая из поступивших помех вызывает такую же реакцию устройства, как и в случае одиночной помехи: прекращается подтверждение автономного режима по выходу 28 (фиг. 4и), с четвертого выхода дешифратора выдается разрещение (фиг. 4в) на прохождение импульсов с периодом В МКС (фиг. 4б) с входа 19 на вход сложения счетчика 1 (фиг.Аг) и счетчик начинает счет в обычном порядке (фиг. 4д, е, ж). Однако поступление каждой следующей помехи снова вызывает запись в счетчик 1 состояний его D-входов,,т.е. сбивает цикл счета. В частности при показанном на фиг. 4а порядке поступления помех вторая помеха вызывает переход из четвертого состояния в первое, а третья помеха - переход из шестого .|состояния в первое (фиг. 4и) . Возврат в первое состояние может происходить сколько угодно раз в любом из состояний с второго по седьмое, что изображено стрелками возврата на фиг. 8. В течение всего времени следования помех не подтверждается сохранение автономного режима на четвертом управляющем выходе 28 (фиг. 4и), но и не выдается подтверждения уста- новления ведомого режима по выходу 29 и разрешения на следование импульсов

513225046

установа по выходу 13 к строчному де- с заранее известным периодом.и поэтолителю частоты управляемого синхро-му следующий (второй), входной импульс

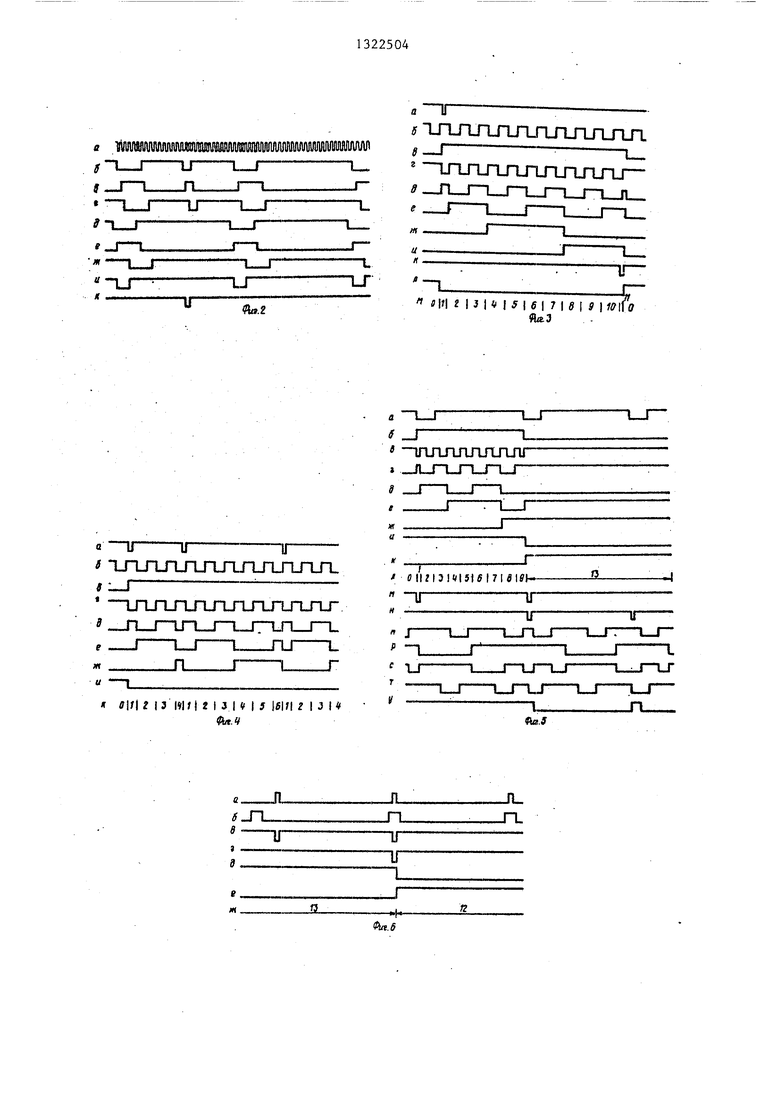

генератора, предотвращая тем самым(фиг. 5а) поступает в то время, когда

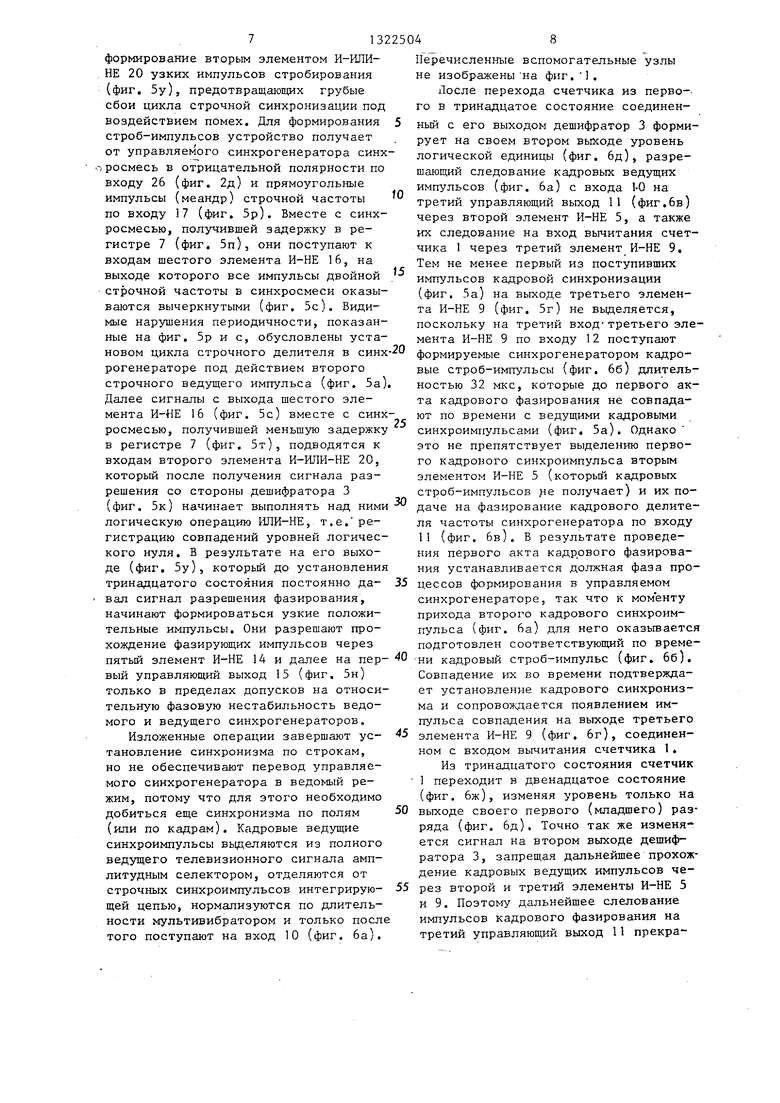

сбои его собственного цикла под влия-счетчик I находится в восьмом, девянием помех.5том и десятом состояниях; неоднозначВ-зависимости от характера посту-ность состояния связана с тем, что пающих помех возможны два выхода изпредварительное фазирование пересчи- рассмотренного состояния отработкитываемых импульсов относительно вход- неодиночных помех. Если помехи носятного сигнала не производится. В этих случайный характер и их поступление Wсостояниях выходной сигнал старшего в некоторый- момент прекращается, торазряда счетчика 1 (фиг. 5ж) имеет счетчик I продолжает счет до одиннад-уровень логической единицы, вследст- цатого состояния, после чего безус-вие чего на D-входах счетчика 1 уста- ловно переходит в нулевое состояниенавливается комбинация 1101 {а не (как и в .случае отработки одиночной J50001, как при отработке помех), а помехи)i что означает возврат к рабо-также открывается прежде закрытый пяте в автономном режиме. Если же поме-тый элемент И-НЕ 14.Поэтому- результат ха обусловлена подачей ведущего синх-логического дифференцирования второго росигнала в интервале его кадровойвходного импульса (фиг, 5а) появляет- синхрогруппы (тогда импульсы на вхо- 20ся одновременно и на выходе четверто- де 22 следуют с периодом не 65 мкс,го элемента И-НЕ 13 (фиг. 5м), и на а 32 МКС, и фазировать строчный дели-выходе пятого элемента И-НЕ 14 (фиг. тель синхрогенератора им нельзя), то5н), откуда по вьйсоду 15 следует на будет наблюдаться регулярный возвратфазирование строчного делителя часто- из четвертого состояния в первое ты управляемого синхрогенератора. В вплоть до окончания синхрогруппы, ато же время импульс с выхода четвер- затем начинается регулярное следова-того элемента И-НЕ 13 (фиг. 5м) дей- ние ведущего строчного синхросигналаствует на С-вход счетчика I и вызыва- с номинальным периодом 64 мкс (после-ет запись в него той комбинации логи- довательность состояний счетчика 1 30ческих уровней (1101 13), которая представлена на фиг, 4к),имелась на его D-входах. Таким обра- Б случае поступления ведущего те-зом, счетчик 1 переходит в тринадца левизионного сигнала на вход 22 пос-тое состояние, при котором подключен- тупает регулярная последовательностьный к его выходам дешифратор 3 прек- стр очных импульсов (фиг. 5а), получа- 35ращает выдавать на своем третьем вы- емая посредством вьщеления из полногоходе (фиг. 5и) сигнал разрешения на ведущего ТВ-сигнала с помощью ,открывание четвертого элемента И-НЕ не показанных на фиг о 1. В момент по-13. Поэтому все следующие импульсы отупления первого синхроимпульса уст-(после второго) на выходе четвертого ройство еще не имеет сведений о ха- 40элемента И-НЕ 13 (фиг. 5м) не выделя- рактере поступившего сигнсша, поэто-ются и на С-вход счетчика I не посту- му его отработка начинается так же дают. Все дальнейшие изменения сос- как описанная вьше отработка помех:тояния счетчика I происходят не по- результат логического дифферендирова-средством воздействия на его С-вход, ния входного сигнала появляется на 45а посредством воздействия на входы выходе четвертого элемента И-НЕ 13сложения и вычитания, (фиг. 5м), вызывая запись состояния В тот же момент дешифратор 3 пре- 000 в счетчик 1 (фиг, 5г, д е, ж).кращает выдачу со своего четвертого Дешифратор 3 на четвертом выходе фор-выхода (фиг, 56) сигнала разрешения мирует сигнал разрешения (фи г, 5б) 50« прохождение импульсов с периодом н а прохождение импульсов с периодом8 мкс с входа 9 Йа вход сложения

(..1счетчика I . Последовательность пере8 мкс на вход сложения счетчика 1/ж с к

, .. « считываемых импульсов (фиг. 5Bj обры(фиг. 5в), а далее начинается после-„ .,

„„вается и дальнейший перебор состоядовательный пересчет состоянии, ил- f f

л, R 5)НИИ прекращается. Еще одно изменение

люстрированных диаграммами нафиг.эг, JJ

1 -заключается в том, что с шестого вы- д. е. ж и десятичными номерами состо- -

. , .. „хода дешифратора 3 начинает посту- яний на фиг. 5л. Однако в отличие от м м .i- помех полезные синхросигналы следуютпать сигнал разрешения (фиг. 5к) на

25

формирование вторым элементом И-ИЛИ- НЕ 20 узких импульсов стробирования (фиг. 5у), предотвращающих грубые сбои цикла строчной синхронизации под воздействием помех. Для формирования 5 строб-импульсов устройство получает от управляемого синхрогенератора синхросмесь в отрицательной полярности по входу 26 (фиг. 2д) и прямоугольные импульсы (меандр) строчной частоты по входу 17 (фиг. 5р). Вместе с синх- росмесью, получившей задержку в регистре 7 (фиг. 5п), они поступают к входам шестого элемента И-НЕ 16, на выходе которого все импульсы двойной строчной частоты в синхросмеси оказываются вычеркнутыми (фиг. 5с). Видимые нарушения периодичности, показанные на фиг. 5р и с, обусловлены уста- новом цикла строчного делителя в синх-20 рогенераторе под действием второго строчного ведущего импульса (фиг. 5а). Дсшее сигналы с выхода шестого элемента И-НЕ 16 (фиг. 5с) вместе с синх-, росмесью, получившей меньшую задержку в регистре 7 (фиг. 5т), подводятся к входам второго элемента И-ИЛИ-НЕ 20, который после получения сигнала разрешения со стороны дешифратора 3 (фиг. 5к) начинает выполнять над ними - логическую операцию ИЛИ-НЕ, т.е. регистрацию совпадений уровней логического нуля. В результате на его выходе (фиг. 5у), который до установления тринадцатого состояния постоянно да- 35

вал сигнал разрешения фазирования, начинают формироваться узкие положительные импульсы. Они разрешают прохождение фазирующих импульсов через пятый элемент И-НЕ 14 и далее на пер- вый управляющий выход 15 (фиг. 5н) только в пределах допусков на относительную фазовую нестабильность ведомого и ведущего синхрогенераторов.

Изложенные операции завершают ус- тановление синхронизма по строкам, но не обеспечивают перевод управляемого синхрогенератора в ведомый режим, потому что для этого необходимо добиться еще синхронизма по полям 50 (или по кадрам). Кадровые ведущие синхроимпульсы выделяются из полного ведущего телевизионного сигнала амплитудным селектором, отделяются от строчных синхроимпульсов интегрирую- 55 щей цепью, нормализуются по длительности мультивибратором и только после того поступают на вход 10 (фиг. 6а).

5

0

0 5

Перечисленные вспомогательные узлы не изображены на фиг. 1.

После перехода счетчика из перво-. го в тринадцатое состояние соединенный с его выходом дешифратор 3 формирует на своем втором выходе уровень логической единицы (фиг. 6д), разрешающий следование кадровых ведущих импульсов (фиг. 6а) с входа 1-0 на третий управляющий выход 11 (фиг.бв) через второй элемент И-НЕ 5, а также их следование на вход вычитания счетчика 1 через третий элемент И-НЕ 9. Тем не менее первый из поступивших импульсов кадровой синхронизации (фиг, 5а) на выходе третьего элемента И-НЕ 9 (фиг. 5г) не выделяется, поскольку на третий вход-третьего элемента И-НЕ 9 по входу 12 поступают формируемые синхрогенератором кадровые строб-импульсы (фиг. 66) длительностью 32 МКС, которые до первого акта кадрового фазирования не совпадают по времени с ведущими кадровыми синхроимпульсами (фиг. За). Однако это не препятствует выделению первого кадрового синхроимпульса вторым элементом И-НЕ 5 (которьш кадровых строб-импульсов fie получает) и их подаче на фазирование кадрового делителя частоты синхрогенератора по входу 11 (фиг. 6в). В результате проведения первого акта кадрового фазирования устанавливается должная фаза процессов формирования в управляемом синхрогенераторе, так что к мом енту прихода второго кадрового синхроимпульса (фиг. 6а) для него оказывается подготовлен соответствующий по време- -ни кадровый строб-импульс (фиг. 6б). Совпадение их во времени подтверждает установление кадрового синхронизма и сопровохсдается появлением импульса совпадения на выходе третьего элемента И-НЕ 9 (фиг. 6г), соединенном с входом вычитания счетчика 1.

Из тринадцатого состояния счетчик 1 переходит в двенадцатое состояние (фиг. 6ж), изменяя уровень только на выходе своего первого (младшего) разряда (фиг. 6д). Точно так же изменяется сигнал на втором выходе дешифратора 3, запрещая дальнейшее прохождение кадровых ведущих импульсов через второй и третий элементы И-НЕ 5 и 9. Поэтому дальнейшее слелование импульсов кадрового фазирования на третий управляющий выход 11 прекращается (фиг, 6в) и предотвращается уменьшение ниже 12-го числа в счетчике 1. Тем самым двенадцатое состояние оказывается вторым устойчивым состоянием, соответствующим ведомо- му режиму управляемого синхрогенера- тора. Индикация установления двенадцатого состояния производится по седьмому выходу дешифратора 3, на котором в момент перехода возникает уровень логической единицы (фиг, бе) поступающий на выход 29.

В случае прекращения поступления ведущего ТВ-сигнала исходное состояние синхрогенератора соответствует ведомому режиму (состояние 12 на фиг, 8). При этом на С-вкод первого D-триггера 6 подана синхросмесь от регистра 7, содержащая интервалы передачи импульсов двойной строчной частоты (фиг. 7а), а на D-вход - ме- андровый сигнал строчной частоты Сфиг, 76), поступающий по входу 17 о управляемого синхрогенератора. При наличии положительного полупериода на D-входе в моменты положительных перепадов на С-входе первого триггера 6 в него записывается уровень логической единицьс (фиг. 7д), сбрасываемый обратно в нуль либо импульсами строчного фазирования (фиг. 7в), снимаемыми с первого управляющего выхода 15 через второй элемент И 8 на

При выходе счетчика 1 из двенадцаR-вход первого D-триггера 6, либо запаздывающим относительно них сигналом 35 того состояния дешифратор 3, дешифри- синхросмеси (фиг. 7г), подводимым по рующий сигналы счетчика 1, прекращает входу 26 от управляемого синхрогенератора и следующим далее через регистр 7 и через второй элемент И 8 к тому же R-входу первого D-триггера 6. 40 При поступлении ведущего ТВ-сигнала на первый управляющий выход 15 регулярно следуют фазирующие импульсы (фиг. 7в), сбрасывающие первый D-триг- гер 6 сразу же после запуска. Поэто-45 мом работы синхрогенератора может му формируемые первым D-триггером 6 возвратиться к работе в ведомом режи- импульсы (фиг. 7д) получаются короткими. Если же ведущий ТВ-сигнал перестает поступать, то импульсы на первом управляющем выходе 15 (фиг. 7в) 50

выдавать со своего седьмого выхода на второй управляющий выход 29 сигнал подтверждения ведомого режима. Если нарушение следования ведущего видеосигнала было вызвано случайной помехой и не привело к потере более чем трех строчных ведущих импульсов подряд, то устройство управления режиме, поскольку в тринадцатом, четырнадцатом и пятнадцатом состояниях открыт счет кадровых импульсов по входу вычитания (фиг. 6г),счетчика 4. Но если сбои следуют регулярно чаще, чем один раз в поле, то счет по входу сложения счетчика I происходит быстрее, чем счет на вычитание. Устройст- 55 во выходит в нулевое состояние и по четвертому управляющему выходу 28, соединенному с первым выходом дешиф- - ратора 3 (фиг. 7м), подтверждает ус- танов автономного режима работы. Испропадают, сброс первого D-триггера 6 запаздывающей синхросмесью (фиг. 7г) начинает происходить позже, и длительность формируемых первым D-триггером 6 импульсов увеличивается (фиг. 7д).

Для различения длительностей импульсов, формируемых первым D-триггером 6, их компарируют по фазе в первом элементе И-ИЛИ-НЕ 18 с синхросме- сью, снимаемой с одного из-выходов регистра 7 (фиг. 7е). Задержку выбирают так, чтобы в случае поступления ведущего сигнала короткие импульсы первого D-триггера 6 заканчивались раньше, чем сигнал синхросмеси начнет поступать к первому элементу И-ИЛИ- НЕ 18. Но когда поступление видеосигнала прекращается, уширенные импульсы первого D-триггера 6 (фиг. 7д) начинают перекрывать во времени (примерно на 0,5 мкс) запаздывающую синхросмесь (фиг. 7г). Совпадения вызывают появление на выходе первого элемента И-ИЛИ-НЕ I8 узких отрицательных импульсов (фиг. 7ж),подводимых к входу сложения счетчика 1, Тогда счетчик из двенадцатого состояния переходит в тринадцатое и поступление видеосигнала не возобновляется, а счет на сложение продолжается до пятнадцатого состояния и после переполнения счетчика 1 завершается переходом его в нулевое состояние, соответствующее автономному режиму. Диаграммы выходных сигналов счетчика 1 при описанном порядке счета показаны на фиг. 7и (младший разряд), 7к (второй разряд), и 7л (третий -и четвертый разряды). Соответствующие состояния счетчика 1 показаны десятичными цифрами на фиг. 7н,

При выходе счетчика 1 из двенадцатого состояния дешифратор 3, дешифри- рующий сигналы счетчика 1, прекращает мом работы синхрогенератора может возвратиться к работе в ведомом режи-

того состояния дешифратор 3, дешифри- рующий сигналы счетчика 1, прекращает мом работы синхрогенератора может возвратиться к работе в ведомом режи-

выдавать со своего седьмого выхода на второй управляющий выход 29 сигнал подтверждения ведомого режима. Если нарушение следования ведущего видеосигнала было вызвано случайной помехой и не привело к потере более чем трех строчных ведущих импульсов подряд, то устройство управления режитого состояния дешифратор 3, дешифри- рующий сигналы счетчика 1, прекращает мом работы синхрогенератора может возвратиться к работе в ведомом режи-

ме, поскольку в тринадцатом, четырнадцатом и пятнадцатом состояниях открыт счет кадровых импульсов по входу вычитания (фиг. 6г),счетчика 4. Но если сбои следуют регулярно чаще, чем один раз в поле, то счет по входу сложения счетчика I происходит быстрее, чем счет на вычитание. Устройст- во выходит в нулевое состояние и по четвертому управляющему выходу 28, соединенному с первым выходом дешиф- - ратора 3 (фиг. 7м), подтверждает ус- танов автономного режима работы. Исполняют переход в автономный режим первый и пятьш элементы- И-НЕ 5 и 1А, которые под действием сигнала с второго выхода дешифратора 3 и сигнала с четвертого разряда счетчика 1 (фиг,7л) соответственно запрещают следование строчных и кадровых фазирующих импульсов по третьему и первому управляющим выходам 11 и 15 к строчному и кадровому делителям частоты управляемого синхрогенератора.

Формула изобретения Устройство управления режимом работы синхрогенератора, содержащее счетчик, первый и второй элементы И, дешифратор, первый и второй элементы И - НЕ-, первый D-триггер и регистр, при этом вход сброса счетчика соединен с выходом первого элемента И, первый и второй выходы дешифратора соединены с первыми входами соответ- ветственно первого и второго элементов И-НЕ, отличающееся тем, что, с целью увеличения помехоустойчивости и расширения функциональных возможностей, введены второй D-триггер, С- и D-входы которого являются входом тактовых импульсов и

Ш

ходами второго и третьего D-тригге- ров, третий вход соединен с выходом первого элемента И-НЕ, четвертый Bxofl соединен с третьим выходом дешифратора, а выход соединен с С-входом счетчика, выходы которого соединены с входами дешифратора, пятый элемент И-НЕ, первый, второй, третий и четвертый входы которого соединены Соответственно с инверсным выходом третьего D-триггера, с инверсным выходом второго D-триггера, с выходом второго элемента И-ИЛИ-НЕ и с выходом последнего разряда счетчика, а выход является первым управляющим выходом и соединен с .первым входом второго элемента И, выход которого соединен с R-входом первого D-трид гера, D-вкод которого является входом импульсов строчной частоты, шестой элемент И- НЕ, первый вход которого объединен с D-входом первого D-триггера, а выход, соединен с вторым входом второго элемента И-ИЛИ-НЕ5 при этом четвертый, пятый и шестой выходы дешифратора соединены соответственно с третьим вхо- дом элемента И-ИЛИ-НЕ, с первым вхоf5

20

дом первого элемента И, второй вход которого является входом команд уп входом синхросигналов соответственно, 30 равления, с четвертым-входом первого третий D-триггер, С-вход которого элемента И-ИЛИ-НЕ, объединенного с объединен с С-входом второго D-триг- третьим и четвертым входами второго гера, а D-вход соединен с инверсным элемента И-ИЛИ-НЕ, седьмой выход де- выходом второго D-триггера, первый шифратора является вторым управляю- элемент И-ИЛИ-НЕ, первый вход которо- 35 щим выходом, первый выход дешифрато- го является входом импульсов восьмой ра является четвертым управляющим вы- гармоники строчной частоты, второй ходом, вьгкод второго элемента И-НЕ вход соединен с прямым выходом первого D-триггера, а выход соединен с

является третьим управляющим выходом, информационный вход регистра является

суммирующим входом счетчика, второй элемент И-ИЛИ-НЕ, первый вход которого соединен с первым выходом регистра, третий элемент И-НЕ, первый вход которого является входом стробирующих импульсов, второй вход объединен с вторым входом второго элемента И-НЕ и является входом импульсов фазирования кадрового делителя, третий вход соединен с вторым выходом дешифратора, а выход соединен с входом вычита-50 входом первого элемента И-НЕ, а вы- ния счетчика, четвертый элемент И-НЕ, ход последнего разряда счетчика сое- первый и второй входы которого соеди- динен с D-входами последнего и пред- нены соответственно с инверсными вы- последнего разрядов.

ходами второго и третьего D-тригге- ров, третий вход соединен с выходом первого элемента И-НЕ, четвертый Bxofl соединен с третьим выходом дешифратора, а выход соединен с С-входом счетчика, выходы которого соединены с входами дешифратора, пятый элемент И-НЕ, первый, второй, третий и четвертый входы которого соединены Соответственно с инверсным выходом третьего D-триггера, с инверсным выходом второго D-триггера, с выходом второго элемента И-ИЛИ-НЕ и с выходом последнего разряда счетчика, а выход является первым управляющим выходом и соединен с .первым входом второго элемента И, выход которого соединен с R-входом первого D-трид гера, D-вкод которого является входом импульсов строчной частоты, шестой элемент И- НЕ, первый вход которого объединен с D-входом первого D-триггера, а выход, соединен с вторым входом второго элемента И-ИЛИ-НЕ5 при этом четвертый, пятый и шестой выходы дешифратора соединены соответственно с третьим вхо- дом элемента И-ИЛИ-НЕ, с первым вхо5

0

дом первого элемента И, второй вход которого является входом команд уп равления, с четвертым-входом первого элемента И-ИЛИ-НЕ, объединенного с третьим и четвертым входами второго элемента И-ИЛИ-НЕ, седьмой выход де- шифратора является вторым управляю- щим выходом, первый выход дешифрато- ра является четвертым управляющим вы- ходом, вьгкод второго элемента И-НЕ

является третьим управляющим выходом, информационный вход регистра является

входом синхросмеси, С-вход регистра является входом импульсов сдвига, второй, третий, четвертый и пятый выходы регистра соединены соответственно с С-входом первого- D-триггера, объединенного с вторым входом первого элемента И-НЕ, с вторым входом шестого элемента И-НЕ, с пятым входом первого элемента И-ИЛИ-НЕ и с вторым входом второго элемента И с третьим

а тттттттт&тшшшмшшш

8

Ч.г

а-и:

5 TJTJTJlJTJbrUlJTJlJ-LrL

TJ nJlJlJTrLTLrLnj-

I l М 3 И I 5 I 9 Wtfff ЯлЗ

ж

Т

н и

12

f3

lif

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1394462A1 |

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1385327A1 |

| Синхрогенератор | 1985 |

|

SU1252971A1 |

| Устройство для обработки видеоинформации | 1986 |

|

SU1322320A1 |

| Устройство для определения положения кристалла | 1983 |

|

SU1175304A1 |

| Устройство управления матричным экраном | 1987 |

|

SU1518921A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Обучающее устройство | 1987 |

|

SU1501126A1 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

Изобретение относится к технике телевидения. Цель изобретения - повышение помехоустойчивости и расширение функциональных возможностей. Устройство содержит счетчик 1, элемент И 2 и 8, дешифратор 3, элементы И-НЕ 4, 5, 9, 13, 14 и 16, D-триггеры 6, 21 и 23, регистр 7 и элементы И - ИЛИ - НЕ 18 и 20t Состояние счетчика 1 определяет режим работы управляемого синхрогенератора - автономный, ведомый или промежуточный. При этом устройство отрабатывает как одиночную помеху, так и неодиночные помехи. Цель достигается введением элементов И - НЕ 9, 13, 14 и 16, элементов И - ИЛИ - НЕ 18 и 20 и D-триггеров 21 и 23. В ил. i о: с

ор Е. Папп 2879/56

Составитель Э. Борисов. Техред М.Моргентал

Ко По

Тираж 638 ВНИИПИ Государственного комитета СССР

по. делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Произ1водственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корр ектор С.Черни Подписное

| Устройство формирования сигнала кадровойСиНХРОНизАции | 1979 |

|

SU843301A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-07-07—Публикация

1985-11-10—Подача