Изобретение относится к вычислительной технике и может быть применено при исследовании алгоритмов операторской деятельности.

Цель изобретения - расширение области применения за счет моделирования операций алгоритма, допускающих устранение совершаемых оператором ошибок.

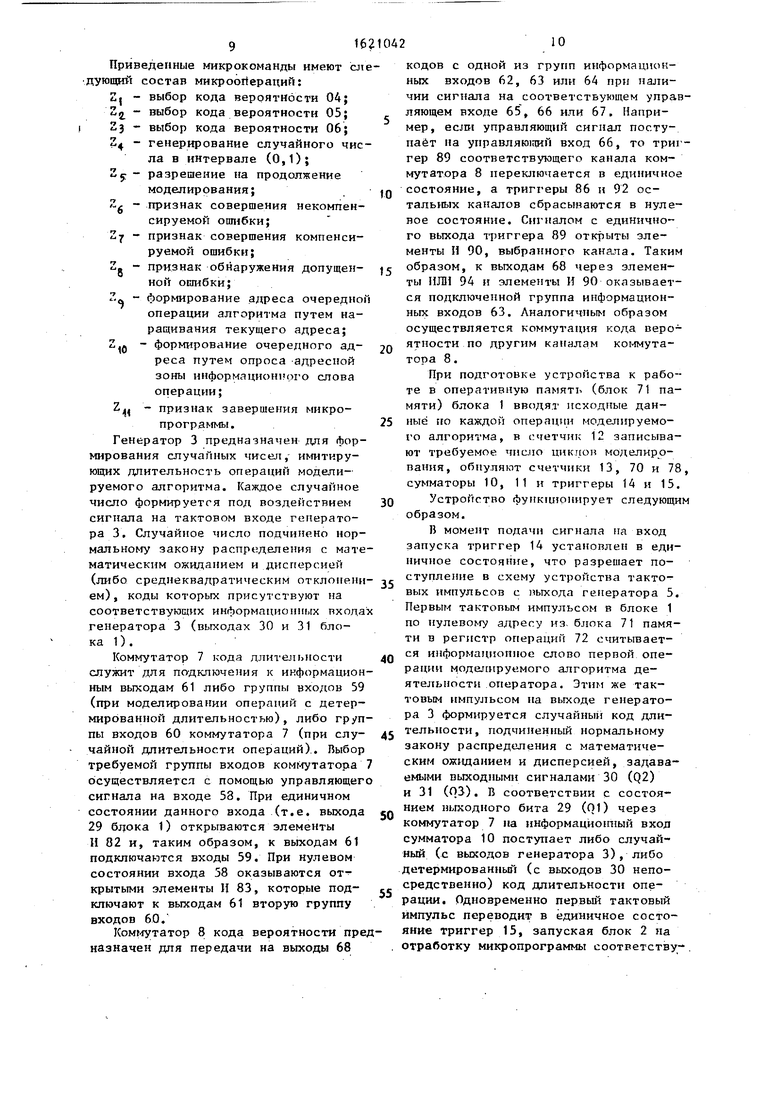

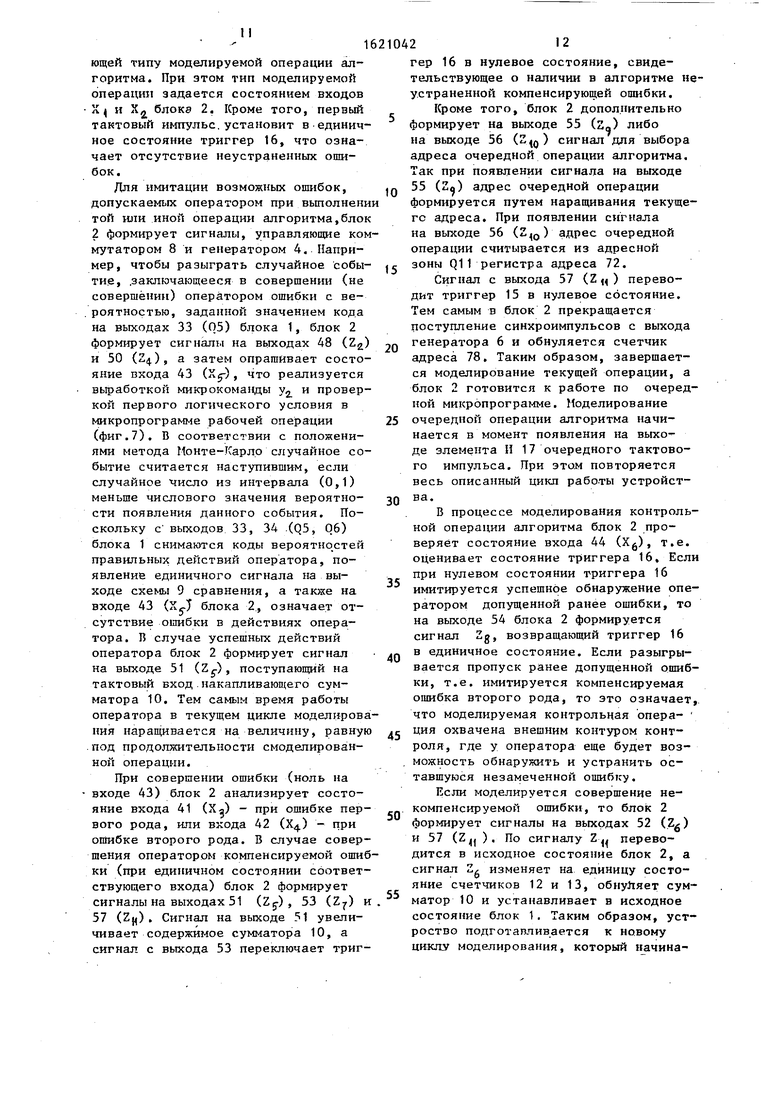

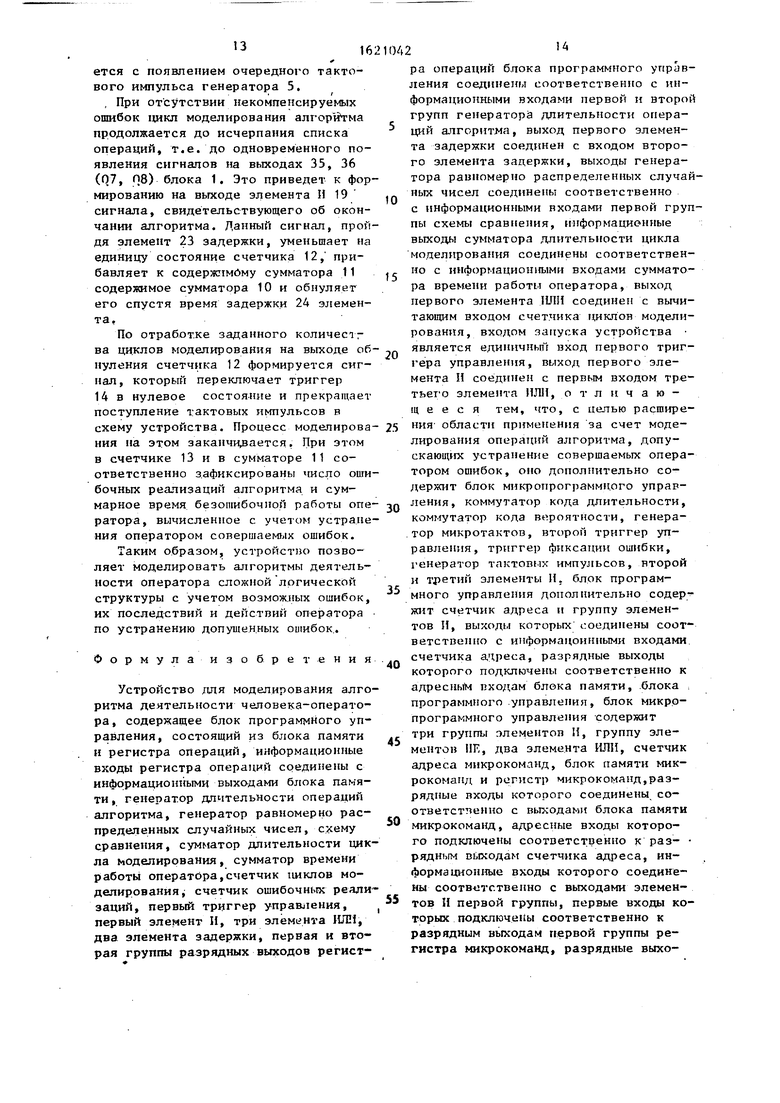

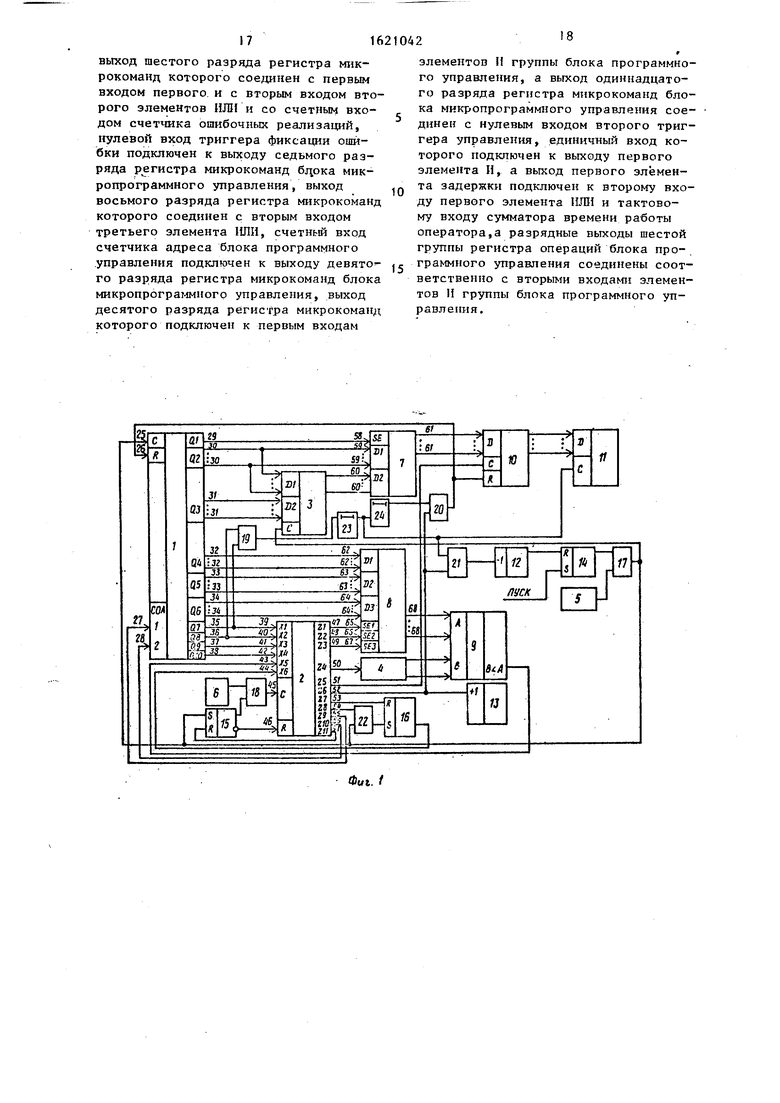

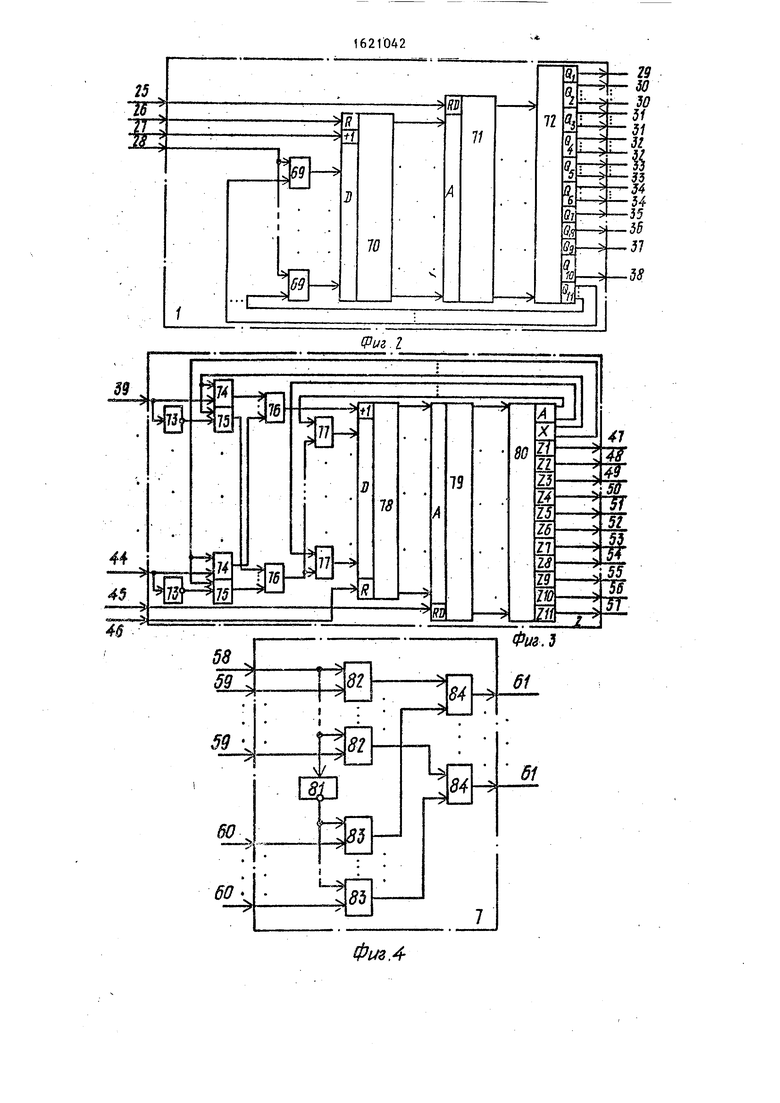

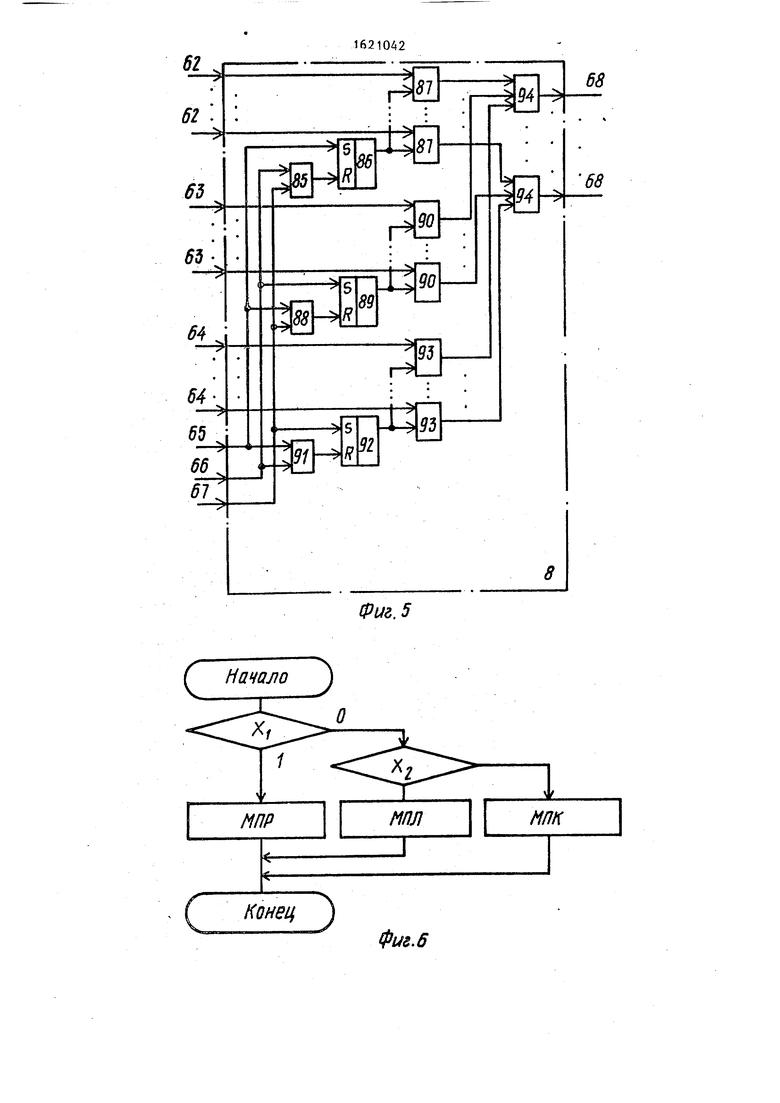

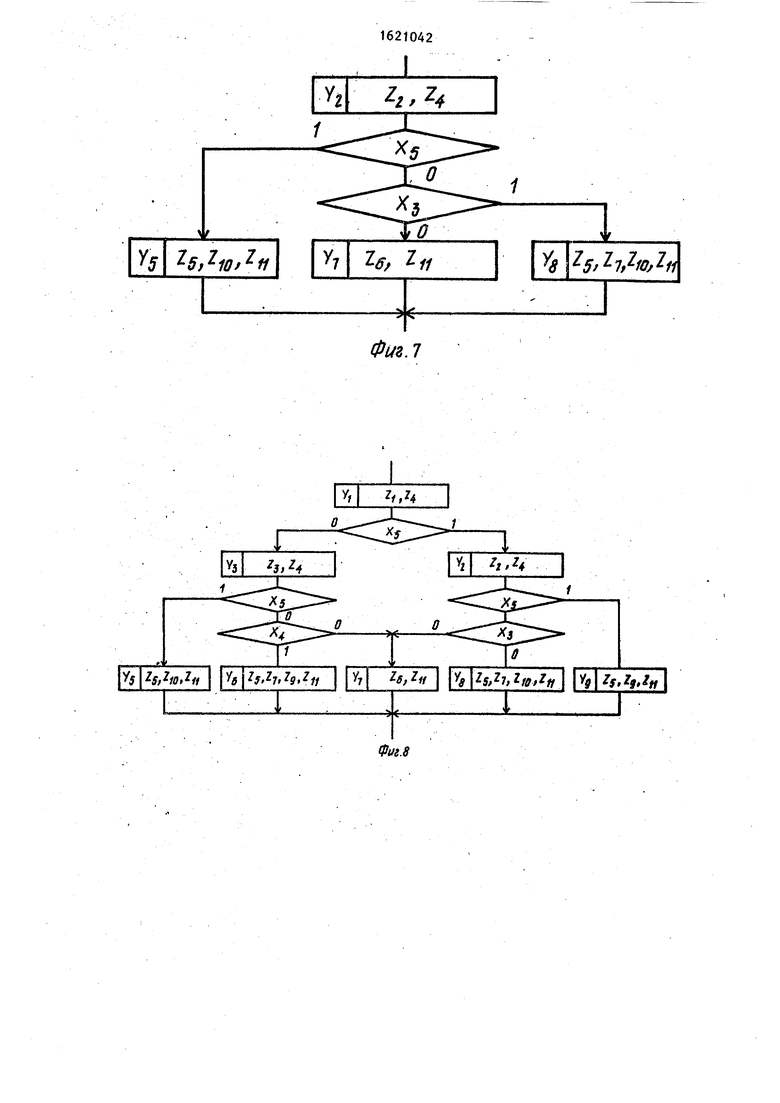

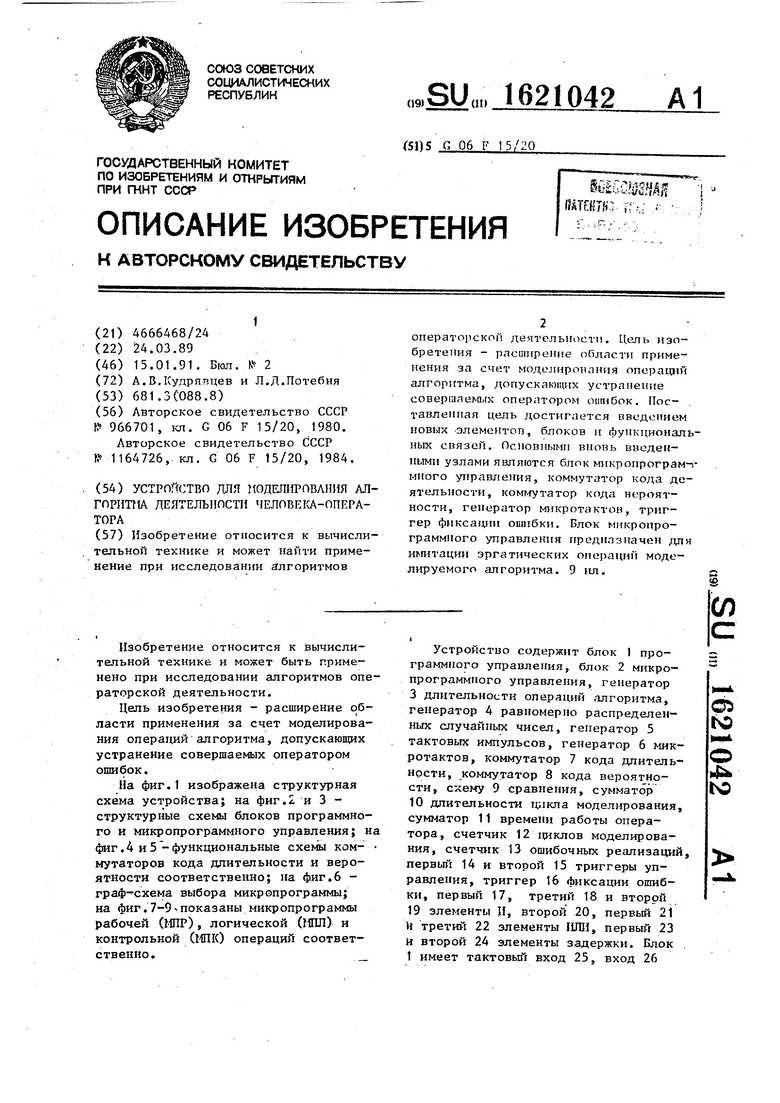

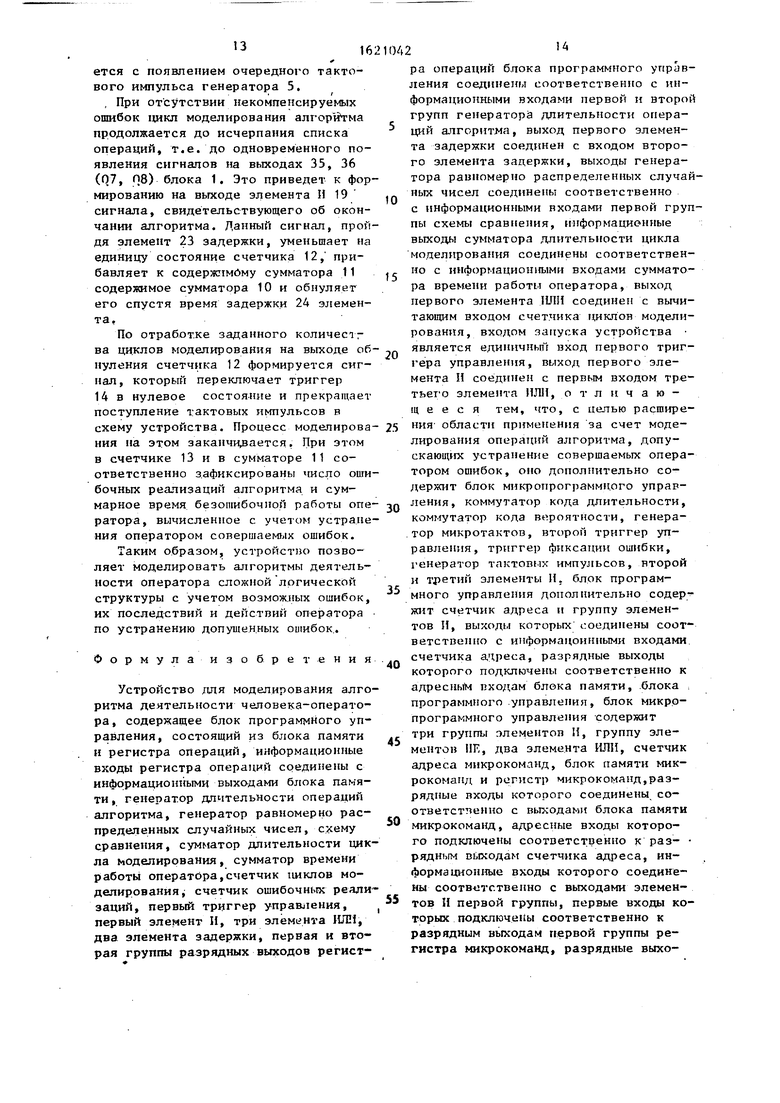

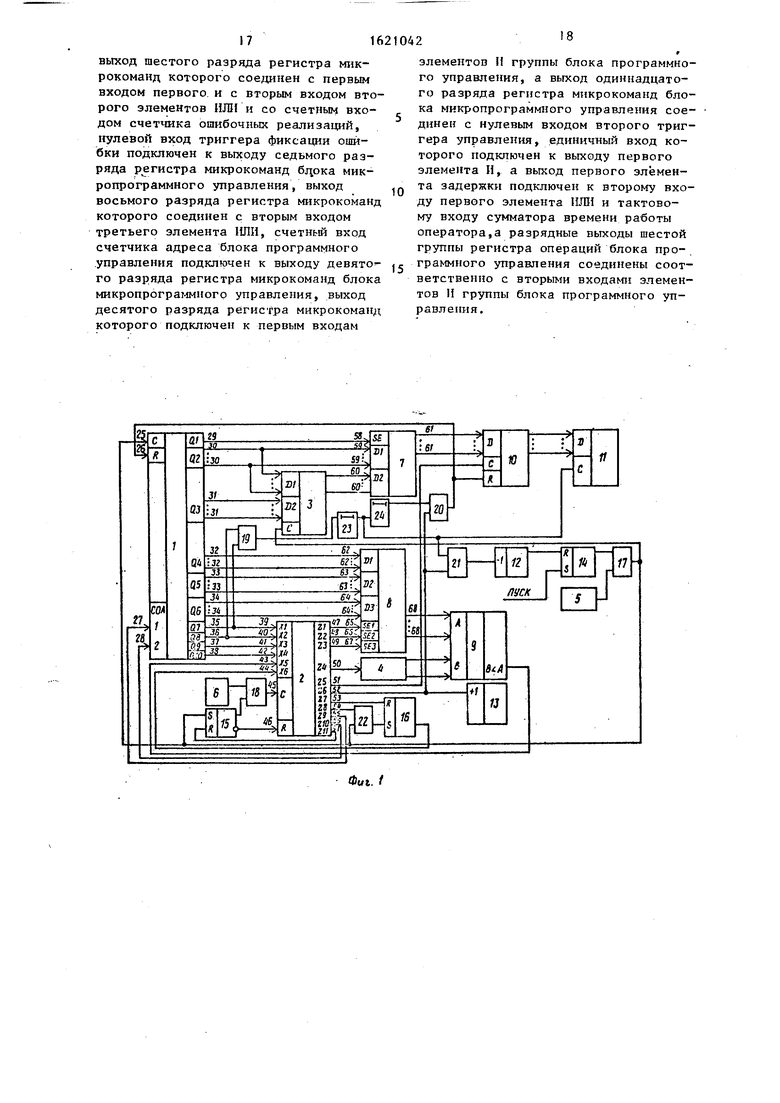

На фиг.1 изображена структурная схема устройства; на фиг.2 и 3 - структурные схемы блоков программного и микропрограммного управления; на фиг.4 и5-функциональные схемы ком- мутаторов кода длительности и вероятности соответственно; на фиг.6 - граф-схема выбора микропрограммы; на фиг.7-9-показаны микропрограммы рабочей (ШР), логической (ШШ) и контрольной (МПК) операций соответственно.

Устройство содержит блок 1 программного управления, блок 2 микропрограммного управления, генератор 3 длительности операций алгоритма, генератор 4 равномерно распределенных случайных чисел, генератор 5 тактовых импульсов, генератор 6 микротактов, коммутатор 7 кода длительности, коммутатор 8 кода вероятности, схему 9 сравнения, сумматор 10 длительности цикла моделирования, сумматор 11 времени работы оператора, счетчик 12 циклов моделирования, счетчик 13 ошибочных реализаций, первый 14 и второй 15 триггеры управления, триггер 16 фиксации ошибки, первый 17, третий 18 и второй 19 элементы И, второй 20, первый 21 и третий 22 элементы ИЛИ, первый 23 И второй 24 элементы задержки. Блок 1 имеет тактовый вход 25, вход 26

О

to

о

Јь N3

сброса, первый 27 и второй 28 управляющие входы, первый выход 29, первую 30, вторую 31, третью 32, четвертую 33 и пятую 34 группы выходов, второй 35, третий 36, четвертый 37 и пятый 38 выходы. Блок 2 имеет шесть информационных входов 39-44, тактовый вход 45, вход сброса 46 и одиннадцать выходов 47-57. Коммутатор 7 имеет управляющий вход 58, первую 59 и вторую 60 группы информационных входов, группу 61 выходов, Ком гутатор 8 имеет первую 62, вторую 63 и третью 64 группы информационных входов, первый 65, второй 66 и третий 67 управляющие входы и группу 68 выходов.

Блок 1 состоит из группы элементов И 69, счетчика 70 адреса, блока 71 памяти операций алгоритма и реги- стра 72 операций.

Блок 2 содержит группу элементов НЕ 73, третью 74 и вторую 75 группы элементов И, элементы ИЛИ 76, первую группу элементов И 77, счетчик адреса 78, блок 79 памяти микрокоманд и регистр 80 микрокоманд.

Коммутатор 7 состоит из элемента НЕ 81, первой 82 и второй 83 групп элементов И и группы 84 элементов ИЛИ.

Коммутатор 8 содержит первый элемент ИЛИ 85. первый триггер 86,.первую группу 87 элементов И, второй элемент ИЛИ 88, второй триггер 89, вторую группу 90 элементов И, третий элемент ИЛИ 91, третий триггер 92, третью группу 93 элементов И и группу 94 элементов ИЛИ.

Блок 1 программного управления предназначен для хранения и выдачи в схему устройства информации о моделируемом алгоритме. Считается, что алгоритм представляет собой логико- временную последовательность отдель- ных операций. К таким операциям относятся: операция задержки,представляющая собой детерминированный временной интервал, имитирующий бездействие оператора в период автомати- ческой работы оборудования; рабочая операция, отождествляемая с воздействием оператора на органы управления либо с восприятием и переработкой информации, поступающей от средств ото бражения, либо с запоминанием и извлечением информации из памяти; логическая операция, включающая в себя проверку оператором некоторых логических условий и принятие по результатам этой проверки решения на выбор одного из двух альтернативных путей дальнейших действий; контрольная операция, имитирующая проверку оператором логических условий, позволяющих оценить правильность ранее выполненных им действий и принять решение либо на продолжение предписанной последовательности действий, либо на устранение последствий выявленной ошибки.

Логические и контрольные операции по своей суги явгчются альтернативными операциями, т к как обеспечивают разветвления в алгоритме деятепьно- сти. Рабочие, логические и контрольные операции являются эргатическими операциями, так как описывают соответствующие действия оператора. Операции задержки являются техническим, так как служат для описания работы оборудования. Порядок следования перечисленных операций в алгоритме произвольный. Относитепьное количество операций любого типа не органи- чено. Суммарное число операций алгоритма не должно превышать числа информационных: слов (объема) блока 71 памяти. Каждое информационное слово содержит исходные данные для одной из операций моделируемого алгоритма. Оно имеет фиксированный формат (разрядность) и разбито на одиннадцать зон (фиг.2), за которыми закреплены следующие функции:

зона 01 - признак длительности операции (1 - детермированная, О - случайная);

зона 02 - двоичный код длительности технической операции либо код математического ожидания длительности эргатической операции;

зона Q3 - код дисперсии (среднего квадратического отклонения) длительности эргатической операции;

зона 04 - код вероятности принятия проверяемым логическим условием единичного значения;

зоны 05, Об - коды вероятностей безошибочного распознавания оператором единичного и нулевого значений проверяемого логического условия, а также отсутствия и наличия ошибки в ранее выполненных действиях;

зоны 07, 08 - чод моделируемой операции (00 - контрольная, 10

516210426

рабочая, 01 - логическая, -ко- считывается информационное слово нец алгоритма);

зона 09 - признак ошибкипервого

первой операции. Одновременно си лы с разрядных выходов регистра

10

рода (1 - компенсируемая, О - некоменсируемая);

зона 010 - признаки ошибки второго рода (1 - компенсируемая, О - некоменсируемая);

зона 011 - адрес (двоичный номер) очередной операции (количества разрядов зоны определяется максимально допустимой длиной алгоритма, то есть предельным числом операций).

Зоны Q1, Q7-010 имеют формат, рав- 15 ный одному биту. Формат зон 02-06 определяется точностью представления исходных данных, т.е. точностью моделирования. Введение зон Q9 и Q10 обусловлено наличием априорной информации о потенциальной возможности обнаружения (необнаружения) оператором допущенных ошибок. При этом предполагается, что при выполнении альтернативных (логических и контрольных) операций возможны ошибки первого и второго рода, связанные с отождествлением оператором одного фактического исхода операции с другим и наоборот. С точки зрения последствий для алгоритма все ошибки могут быть подразделены на компенсируемые и некомпенсируемые оператором. Ошибка считается компенсируемой, если соответствующая операция п алгоритме охвачена контуром контроля, а последствия ошибки поддаются исправлению. В противном случае ошибка считается некомпенсируемой. При совершении некомпенсируемой ошибки цикл моделирования прерывается и осуществляется переход к новому циклу. На этапе подготовки исходных данных в блок 71 памяти записывается необходимая ин, поступают с выходов блока в схем устройства и (с выходов зоны Q11 информационные-входы элементов И блока 1. Адрес очередной операции определяется вне блока 1 и задает состоянием управляющих входов 27 в соответствии с выражением:

ЛЛ; + 1

Q11 при наличии сиг на входе 27; при наличии сиг на входе 28,

где Л1 - адрес текущей операции.

Блок 2 микропрограммного упра

20 пня (фиг.З) предназначен дня ими ции эргатнческих операций алгори Причем моделирование1 отдельной оп ции занимает один такт работы вс устройства. В -зависимости от тип

25 опе рации (рабочая, логическая или контрольная) ее моделирование ос ствляется по соответствующей микр программе за определенное число м ротактов. Каждая микропрограмма

30 ставляет собой некоторую логикоменную последовательность мнкрок манд. Все микрокоманды размещены постоянной памяти (блок 79), прич каждое информационное слово микр команды содержит три зоны: адрес (Л), логических условий (X) и мик операции (Z). В адресной зоне ука адрес очередной микрокоманды па с чай невыполнения проверяемого лог

40 ческого условия, т.е. для нулевог состояния соответствующего информ ционного входа 39-44 блока 2. В з не логических условий (шесть разр дов) формируется (при необходимос

35

считывается информационное слово

первой операции. Одновременно сигналы с разрядных выходов регистра 72

поступают с выходов блока в схему устройства и (с выходов зоны Q11) на информационные-входы элементов И 69 блока 1. Адрес очередной операции Aj определяется вне блока 1 и задается состоянием управляющих входов 27, 28 в соответствии с выражением:

Л; + 1

Q11 при наличии сигнала на входе 27; при наличии сигнала на входе 28,

где Л1 - адрес текущей операции.

Блок 2 микропрограммного управлепня (фиг.З) предназначен дня имитации эргатнческих операций алгоритма. Причем моделирование1 отдельной операции занимает один такт работы всего устройства. В -зависимости от типа

опе рации (рабочая, логическая или контрольная) ее моделирование осуществляется по соответствующей микропрограмме за определенное число мик- ротактов. Каждая микропрограмма представляет собой некоторую логиковременную последовательность мнкроко- манд. Все микрокоманды размещены в постоянной памяти (блок 79), причем каждое информационное слово микрокоманды содержит три зоны: адресную (Л), логических условий (X) и микрооперации (Z). В адресной зоне указан адрес очередной микрокоманды па случай невыполнения проверяемого логического условия, т.е. для нулевого состояния соответствующего информационного входа 39-44 блока 2. В зоне логических условий (шесть разрядов) формируется (при необходимости).

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1989 |

|

SU1631542A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1377870A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

Изобретение относится к вычислительной технике и может найти применение при исследовании алгоритмов операторской деятельности. Цель изобретения - расширение области применения за счет моделирования операций алгоритма, допускающих устранение совершаемых оператором ошибок. Поставленная цель достигается введением новых элементов, блоков и Функциональных связей. Основными вновь введенными узлами являются блок микропрограмм- много управления, коммутатор кода деятельности, коммутатор кода вероятности, генератор микротактов, триггер фиксации ошибки. Блок микропрограммного управления предназначен для имитации эрратических операции моделируемого алгоритма. 9 ил. и

5С

формация о каждой операции моделиру- дд разрешающий сигнал для опроса состоя-

ния информационных входов блока 2, сопоставляемых в микропрограмме с соответствующими логическими условиями. При выполнении проверяемого логиче- « ского условия (1 на соответствующем информационном входе блока 2) адрес очередной микрокоманды формируется путем увеличения на единицу текущего адреса, т.е. состояния счет- t чика 78. Элементы 73-76 образуют селектор адреса, который служит для формирования адреса очередной микрокоманды в соответствии с текущим адресом и текущим состоянием информа-

емого алгоритма и обнуляют счетчик 70. В дальнейшем блок 1 программного управления работает под воздействием сигналов на входах 25-28. Рабо- та блока 1 заключается в циклическом воспроизведении моделируемого алгоритма. Кавдый цикл моделирования начинается с подачи на вход 26 блока 1 сигнала обнуления счетчика 70. Этим сигналом на входах блока 71 памяти устанавливается адрес начальной операции алгоритма. В момент появления на входе 25 тактового сигнала по дан-i ному адресу из блока 71 в регистр 72

716

цйонных входов 39-44 блока 2. Остальные элементы (77-80) блока 2 выполняют функции, аналогичные функциям соответствующих элементов блока 1 (69-72). Зона микроопераций (одиннадцать разрядов) служит для формирования в каждом конкретном микротакте определенной совокупности выходных управляющих сигналов Z к ,...,214 Конкретная комбина- ция выходных сигналов определяется типом (номером) выполняемой в текущий микротакт микрокоманды. Блок 2 функционирует в соответствии с граф- схемами микропрограмм (фиг.6, 7, 8, 9), имеющими в своем составе логические условия, микрокоманды и микрооперации. Логические условия реализуют следующие проверки:

Х

Х1

х3

г 1

м - 1

1 - рабочая операция,

0- альтернативная операция

1- логическая операция;

0- контрольная операция;

1- компенсируемая ошибка

первого рода,

0- некомпенсируемая .ошибка

первого рода;

1- компенсируемая ошибка

второго рода,

0- некомпенсируемая ошибка

второго рода;

1- операция выполнена

правильно,

Х5

О - операция выполнена с ошибкой;

V -

Х6 1 - отсутствие неустраненно ошибки,

О - наличие неустраненной

ошибки.

Физический смысл микрокоманд обусловлен типом операции алгоритма (типом микропрограммы). Для рабочей операции: YЈ - розыгрыш ошибки; YJ - имитация безошибочного выполнения операции;

8

0

5

0

5

0

5

о

5

0

V

Ч

Для Y, Т/

Ч

г 3

V

6

L7

V

8

Ч

Для

V

Х2

Y, YA -имитация выполнения операции с некомпенсируемой ошибкой;

-имитация выполнения операции с компенсируемой ошибкой.

логической операции: розыгрыш значения проверяемого оператором логического условия;

. розыгрыш ошибочного признания оператором фактического единичного исхода операции нулевым (ошибка первого рода); розыгрыш ошибочного признания оператором фактического нулевого исхода операции единичным (ошибка второго рода); имитация безошибочного выполнения операции при нулевом значении проверяемого оператором логического условия (отсутствие ошибки второго рода);

имитация выполнения операции с компенсируемой ошибкой второго рода;

то же, что и для рабочей операции ;

имитация выполнения операции с компенсируемой ошибкой первого рода;

имитация безошибочного выполнения операции при единичном значении проверяемого оператором логического условия (отсутствие ошибки первого рода).

контрольной операции: розыгрыш ошибочного признания оператором правильного результата предыдущих действий неправильным (ошибка первого рода);

розыгрыш ошибочного признания оператором неправильного результата предыдущих действий правильным (ошибка второго рода);

имитация обнаружения оператором ранее допущенной ошибки (отсутствие ошибки контроля второго рода); имитация безошибочного признания оператором правильных действий правильными (отсутствие оинбки первого рода); YJP , Ya - аналогичны соответствующим микрокомандам для логической операции алгоритма %

Приведенные микрокоманды имеют следующий состав микроопераций:

Zj - выбор кода вероятности 04;

Ј - выбор кода вероятности 05;

23 - выбор кода вероятности 06; Z4 - генерирование случайного числа в интервале (0,1); Zy - разрешение на продолжение

моделирования; Јg - признак совершения некомпенсируемой ошибки;

Zf - признак совершения компенсируемой ошибки;

Z. - признак обнаружения допущенной ошибки;

л - формирование адреса очередной операции алгоритма путем наращивания текущего адреса; - формирование очередного адреса путем опроса адресной зоны информационного слова операции;

Z - признак завершения микропрограммы.

Генератор 3 предназначен для формирования случайных чисел, имитирующих длительность операций моделируемого алгоритма. Каждое случайное число формируется под воздействием сигнала на тактовом входе генератора 3. Случайное число подчинено нормальному закону распределения с математическим ожиданием и дисперсией (либо среднеквадратическим отклонением) , коды которых присутствуют на соответствующих информационных пходах генератора 3 (выходах 30 и 31 блока 1) .

Коммутатор 7 кода длительности служит для подключения к информационным выходам 61 либо группы входов 59 (при моделировании операций с детер- мированной длительностью), либо группы входов 60 коммутатора 7 (при случайной длительности операций). Выбор требуемой группы входов коммутатора 7 осуществляется с помощью управляющего сигнала на входе 53. При единичном состоянии данного входа (т.е. выхода 29 блока 1) открываются элементы И 82 и, таким образом, к выходам 61 подключаются входы 59. При нулевом состоянии входа 58 оказываются открытыми элементы И 83, которые подключают к выходам 61 вторую группу входов 60.

Коммутатор 8 кода вероятности пред назначен для передачи на выходы 68

0

кодов с одной из групп информационных входов 62, 63 или 64 при наличии сигнала на соответствующем управляющем входе 65, 66 или 67. Например, если управляющий сигнал поступает на управляющий вход 66, то трш- гер 89 соответствующего канала коммутатора 8 переключается в единичное

состояние, а триггеры 86 и 92 остальных каналов сбрасываются в нулевое состояние. Сигналом с единичного выхода триггера 89 открыты элементы И 90, выбранного канала. Таким

r образом, к выходам 68 через элементы НЛП 94 и элементы И 90 оказывается подключенной группа информационных входов 63. Аналогичным образом осуществляется коммутация кода вероятности по другим каналам коммута- топа 8.

При подготовке устройства к работе в оперативную память (блок 71 памяти) блока 1 вводят исходные дан5 ные tr° каждой операции ноделируемо- го алгоритма, в счетчик 12 записывают требуемое чиспо цикгюв моделирования, обнуляют счетчики 13, 70 и 78, сумматоры 10, 11 и триггеры 14 и 15.

о Устройство функционирует следующим образом.

В момент подачи сигнала на вход запуска триггер 14 установлен в единичное состояние, что разрешает поступление в схему устройства тактовых импульсов с лыхода генератора 5. Первым тактовым импульсом в блоке 1 по нулевому адресу из блока 71 памяти в регистр операций 72 считывает.. ся информационное слово первой операции моделируемого алгоритма деятельности оператора. Этим же тактовым импульсом на выходе генератора 3 формируется случайный код дли, телыюсти, подчиненный нормальному закону распределения с математическим ожиданием и дисперсией, задаваемыми выходными сигналами 30 (Q2) и 31 (ОЗ). в соответствии с состоянием ныходного бита 29 (О1) через коммутатор 7 на информационный вход сумматора 10 поступает либо случайный (с выходов генератора 3), либо детермированный (с выходов 30 непосредственно) код длительности операции. Одновременно первый тактовый импульс переводит в единичное состояние триггер 15, запуская блок 2 на отработку микропрограммы соответству5

O

ющей типу моделируемой операции алгоритма. При зтом тип моделируемой операции задается состоянием входов X i и Х блока 2. Кроме того, первый тактовый импульс, установит в единичное состояние триггер 16, что означает отсутствие неустраненных ошибок.

Для имитации возможных ошибок, допускаемых оператором при выполнении той или иной операции алгоритма,блок 2 формирует сигналы, управляющие коммутатором 8 и генератором 4. Напри25

30

мер, чтобы разыграть случайное собы- зоны Q11 регистра адреса 72. тие, .заключающееся в совершении (не совершении) оператором ошибки с вероятностью, заданной значением кода на выходах 33 (05) блока 1, блок 2 формирует сигналы на выходах 48 (Za) 20 и 50 (Z,}.),, а затем опрашивает состояние входа 43 (), что реализуется выработкой микрокоманды у и проверкой первого логического условия в микропрограмме рабочей операции (фиг.7). В соответствии с положениями метода Монте-Карло случайное событие считается наступившим, если случайное число из интервала (0,1) меньше числового значения вероятности появления данного события. Поскольку с выходов 33, 34 (Q5, 06) блока 1 снимаются коды вероятностей правильных действий оператора, появление единичного сигнала на выходе схемы 9 сравнения, а также на входе 43 (Xj-T блока 2, означает отсутствие ошибки в действиях оператора. В случае успешных действий оператора блок 2 формирует сигнал на выходе 51 (), поступающий на тактовый вход накапливающего сумматора 10. Тем самым время работы оператора в текущем цикле моделирования наращивается на величину, равную под продолжительности смоделированной операции.

При совершении ошибки (ноль на входе 43) блок 2 анализирует состояние входа 41 (Ха) - при ошибке первого рода, или входа 42 (Х.) - при ошибке второго рода. В случае совершения оператором компенсируемой ошибки (при единичном состоянии соответствующего входа) блок 2 формирует сигналы на выходах 51 (Zg-) , 53 (Z) и. 57 (2ц) . Сигнал на выходе 51 увеличивает содержимое сумматора 10, а сигнал с выхода 53 переключает триг35

40

45

50

55

Сигнал с выхода 57 (ZM) дит триггер 15 в нулевое сос Тем самым в блок 2 прекращае поступление синхроимпульсов генератора 6 и обнуляется сч адреса 78. Таким образом, за ся моделирование текущей опе блок 2 готовится к работе по ной микропрограмме. Моделиро очередной операции алгоритма нается в момент появления на де элемента И 17 очередного го импульса. При этом повто весь описанный цикл работы у ва.

В процессе моделирования ной операции алгоритма блок веряет состояние входа 44 (Х оценивает состояние триггера при нулевом состоянии тригге имитируется успешное обнаруж ратором допущенной ранее ош на выходе 54 блока 2 формиру сигнал Zg, возвращающий три в единичное состояние. Если вается пропуск ранее допущен ки, т.е. имитируется компенс ошибка второго рода, то это что моделируемая контрольная ция охвачена внешним контуро роля, где у оператора еще бу можность обнаружить и устран тавшуюся незамеченной ошибку

Если моделируется соверше компенсируемой ошибки, то б формирует сигналы на выходах и 57 (Z ц ). По сигналу Z . п дится в исходное состояние б сигнал Z изменяет на единиц яние счетчиков 12 и 13, обну матор 10 и устанавливает в и состояние блок 1. Таким обра роство подготавливается к н ЦИКЛУ моделирования, который

гер 16 в нулевое состояние, свидетельствующее о наличии в алгоритме неустраненной компенсирующей ошибки.

Кроме того, блок 2 дополнительно формирует на выходе 55 (zq) либо на выходе 56 (2) сигнал для выбора адреса очередной операции алгоритма. Так при появлении сигнала на выходе 55 (Z«) адрес очередной операции формируется путем наращивания текущего адреса. При появлении сигнала на выходе 56 () адрес очередной операции считывается из адресной

5

0

зоны Q11 регистра адреса 72. 0

5

0

5

0

5

Сигнал с выхода 57 (ZM) переводит триггер 15 в нулевое состояние. Тем самым в блок 2 прекращается поступление синхроимпульсов с выхода генератора 6 и обнуляется счетчик адреса 78. Таким образом, завершается моделирование текущей операции, а блок 2 готовится к работе по очередной микропрограмме. Моделирование очередной операции алгоритма начинается в момент появления на выходе элемента И 17 очередного тактового импульса. При этом повторяется весь описанный цикл работы устройства.

В процессе моделирования контрольной операции алгоритма блок 2 проверяет состояние входа 44 (Х), т.е. оценивает состояние триггера 16, Если при нулевом состоянии триггера 16 имитируется успешное обнаружение оператором допущенной ранее ошибки, то на выходе 54 блока 2 формируется сигнал Zg, возвращающий триггер 16 в единичное состояние. Если разыгрывается пропуск ранее допущенной ошибки, т.е. имитируется компенсируемая ошибка второго рода, то это означает, что моделируемая контрольная опера- ция охвачена внешним контуром контроля, где у оператора еще будет возможность обнаружить и устранить оставшуюся незамеченной ошибку.

Если моделируется совершение некомпенсируемой ошибки, то блок 2 формирует сигналы на выходах 52 (Zg) и 57 (Z ц ). По сигналу Z . переводится в исходное состояние блок 2, а сигнал Z изменяет на единицу состояние счетчиков 12 и 13, обнуляет сумматор 10 и устанавливает в исходное состояние блок 1. Таким образом, уст- роство подготавливается к новому ЦИКЛУ моделирования, который начина13

ется с появлением очередного тактового импульса генератора 5.

, При отсутствии некомпенсируемых ошибок цикл моделирования алгоритма продолжается до исчерпания списка операций, т.е. до одновременного появления сигналов на выходах 35, 36 (07, Q8) блока 1. Это приведет к фор мированию на выходе элемента И 19 сигнала, свидетельствующего об окончании алгоритма. Данный сигнал, прой дя элемент 23 задержки, уменьшает на единицу состояние счетчика 12, прибавляет к содержимому сумматора 11 содержимое сумматора 10 и обнуляет его спустя время задержки 24 элемента.

По отработке заданного количестт ва циклов моделирования на выходе об нуления счетчика 12 формируется сигнал, который переключает триггер 14 в нулевое состояние и прекращает поступление тактовых импульсов в схему устройства. Процесс моделирова ния на этом заканчивается. При этом в счетчике 13 и в сумматоре 11 соответственно зафиксированы число оши бочных реализаций алгоритма и суммарное время безошибочной работы one ратора, вычисленное с учетом устране ния оператором совершаемых ошибок.

Таким образом, устройство позволяет моделировать алгоритмы деятельности оператора сложной логической структуры с учетом возможных ошибок, их последствий и действий оператора по устранению допущенных ошибок.

Формула изобретения

Устройство для моделирования алго ритма деятельности человека-оператора, содержащее блок программного управления, состоящий из блока памяти и регистра операций, информационные входы регистра операций соединены с информационными выходами блока памяти, генератор длительности операций алгоритма, генератор равномерно распределенных случайных чисел, схему сравнения, сумматор длительности цикла моделирования, сумматор времени работы оператора,счетчик циклов моделирования, счетчик ошибочных реяли заций, первый триггер управления, первый элемент И, три элемента ИЛИ, два элемента задержки, первая и вторая группы разрядных выходов регист

10

15

20

25

21042

ра операций блока программного управления соединены соответственно с информационными входами первой и второй групп генератора длительности опера- ций алгоритма, выход первого элемента задержки соединен с входом второго элемента задержки, выходы генератора равномерно распределенных случайных чисел соединены соответственно с информационными входами первой группы схемы сравнения, информационные выходы сумматора длительности цикла моделирования соединены соответственно с информационными входами сумматора времени работы оператора, выход первого элемента Ш1И соединен с вычитающим входом счетчика циклов моделирования, входом запуска устройства является единичный вход первого триггера управления, выход первого элемента И соединен с первым входом третьего элемента ИЛИ, отличающееся тем, что, с целью расширения области применения за счет моделирования операций алгоритма, допускающих устранение совершаемых оператором ошибок, оно дополнительно содержит блок микропрограммного управления, коммутатор кода длительности, коммутатор кода вероятности, генератор микротактов, второй триггер управления, триггер фиксации ошибки, генератор тактовых импульсов, второй и третий элементы И. блок программного управления дополнительно содержит счетчик адреса и группу элементов И, выходы которых соединены соответственно с информацоинными входами счетчика адреса, разрядные выходы которого подключены соответственно к адресным входам блока памяти, блока программного управления, блок микропрограммного управления содержит три группы элементов И, группу элементов НЕ, два элемента ИЛИ, счетчик адреса микрокоманд, блок памяти микрокоманд и регистр микрокоманд,разрядные входы которого соединены, соответственно с выходами блока памяти микрокоманд, адресные входы которого подключены соответственно к раз- рядным выходам счетчика адреса, информационные входы которого соединены соответственно с выходами элементов II первой группы, первые входы которых подключены соответственно к разрядным выходам первой группы регистра микрокоманд, разрядные выхо30

35

40

45

50

55

15162

ды второй группы которого соединены соответственно с первыми входами одноименных элементов И второй и третьей групп, выходы элементов 1Ш группы подключены соответственно к вторым входам элементов И второй группы, выходы которых соединены соответственно с входами первого элемента ИЛИ, выход которого подключен к вторым входам элементов И первой группы, выходы элементов И третьей группы подключены соответственно к входам второго элемента ИЛИ, выход которого соединен со счетным входом счетчика адреса микрокоманд, информационные выходы первой группы регистра операций блока программного управления подключены соответственно к информационным входам первой группы коммутатора кода длительности, информационные входы второй группы которого подключены соответственно к выходам генератора длительности операций алгоритма, выход первого разряда регистра операций блока программного управления соединен с управляющим входом коммутатора кода длительности, выходы которого подключены соответственно к информационным входам сумматора длительности цикла моделирования, выходы второго разряда регистра операций блока программного управления соединены с входом второго элемента НЕ группы и вторым входом первого элемента И третьей группы блока микропрограммного управления и первым входом первого элемента И устройства, второй вход которого, вход второго элемента НЕ группы и второй вход второго элемента И третьей группы блока микропрограммного управления подключены к выходу третьего разряда регистра операций блока программного управления, выход второго элемента И устройства подключен к входу первого элемента задержки, выход второго элемента задержки подключен к первому входу второго элемента ИЛИ, выход которого соединен с входами сброса сумматора длительности цикла моделирования и счетчика адреса блока программного управления, выход обнуления счетчика циклов моделирования подключен к нулевому входу перво- го триггера управления, прямой выход которого соединен с первым вхо- дом первого элемента И, второй вход

16

3

5

5

которого1 подключен к выходу генератора тактовых импульсов, а выход соединен с тактовым входом генератора длительности операций алгоритма и входом считывания блока памяти, блока программного управления, вход третьего элемента НЕ группы и второй вход третьего элемента И третьей группы объединены и подключены к выходу четвертого разряда регистра операций блохг программного управления, выход пятого разряда регистра операций которого подключен к входу четвертого элемента НЕ группы и второму входу четвертого элемента И третьей группы блока микропрограммного управления, вход пятого элемента НЕ группы и второй вход пятого элемента И которого Q подключены к выходу Меньше схемы сравнения, информационные входы второй группы которой соединены соответственно с выходами коммутатора кода вероятности, вход шестого элемента НЕ группы и второй вход шестого элемента И третьей группы блока микропрограммного управления подключены к прямому выходу триггера фиксации ошибки, единичный вход которого соецинен с выходом третьего элемента ИЛИ, вход считывания блока памяти микрокоманд блока микропрограммного управления подключен к выходу третьего элемента И, первый вход которого соединен с выходом генератора микротактов, а второй вход - с прямым выходом второго триггера управления, инверсный выход которого соединен с входом сброса счетчика адреса блока микропрограммного управления, разрядные выходы третьей, четвертой и пятой групп в регистре операций блока программного управления подключены соответственно к информационным входам первой, второй и третьей групп коммутатора кода вероятности, первый, второй и третий управляющие входы которого подключены соответственно к выходам первого, второго и третьего разрядов регистра микрокоманд блока микропрограммного управления, выход четвертого разряда регистра микрокоманд которого соединен с тактовым входом генератора равномерно распределенных случайных чисел, тактовый вход сумматора длительности цикла моделирования подключен к выходу пятого разряда регистра микрокоманд блока микропрограммного управления,

0

5

0

5

0

17

выход шестого разряда регистра микрокоманд которого соединен с первым входом первого и с вторым входом второго элементов ИЛИ и со счетным входом счетчика ошибочных реализаций, нулевой вход триггера фиксации ошибки подключен к выходу седьмого разряда регистра микрокоманд бдока микропрограммного управления, выход восьмого разряда регистра микрокоманд которого соединен с вторым входом третьего элемента ИЛИ, счетный вход счетчика адреса блока программного управления подключен к выходу девятого разряда регистра микрокоманд блока микропрограммного управления, выход десятого разряда регистра микрокоманд которого подключен к первым входам

1042t8

г

элементов И группы блока программного управления, а выход одиннадцатого разряда регистра микрокоманд блока микропрограммного управления соединен с нулевым входом второго триггера управления, единичный вход которого подключен к выходу первого элемента И, а выход первого элёменJQ та задержки подключен к второму входу первого элемента ИЛИ и тактовому входу сумматора времени работы оператора,а разрядные выходы шестой группы регистра операций блока проU граммного управления соединены соответственно с вторыми входами элементов И группы блока программного управления.

2 мй

2 01391

(Начало j

О

С Конец)

%..

Фиг. 5

Фиг. 6

f

YS 5t210f f1

Ы is i

I

ZftlrftoJii

Фиг.7

Фиг. 9

| Устройство для моделирования деятельности человека-оператора системы "человек-машина | 1981 |

|

SU966701A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1164726A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-15—Публикация

1989-03-24—Подача