f

Изобретение относится к -1мпульс- ной технике и может быть использовано в измерительных преобразователях например, угла поворота вала в код«

Цель изобретения - повышение статической точности путем обеспечения апериодического закона регулирования

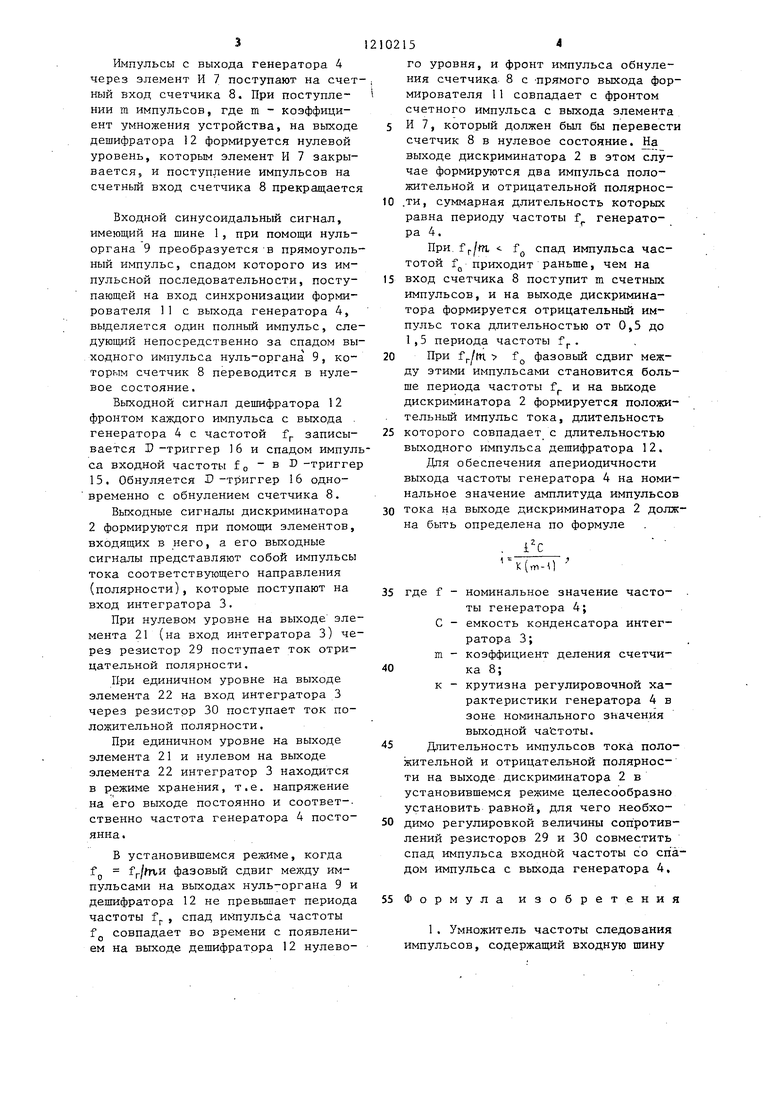

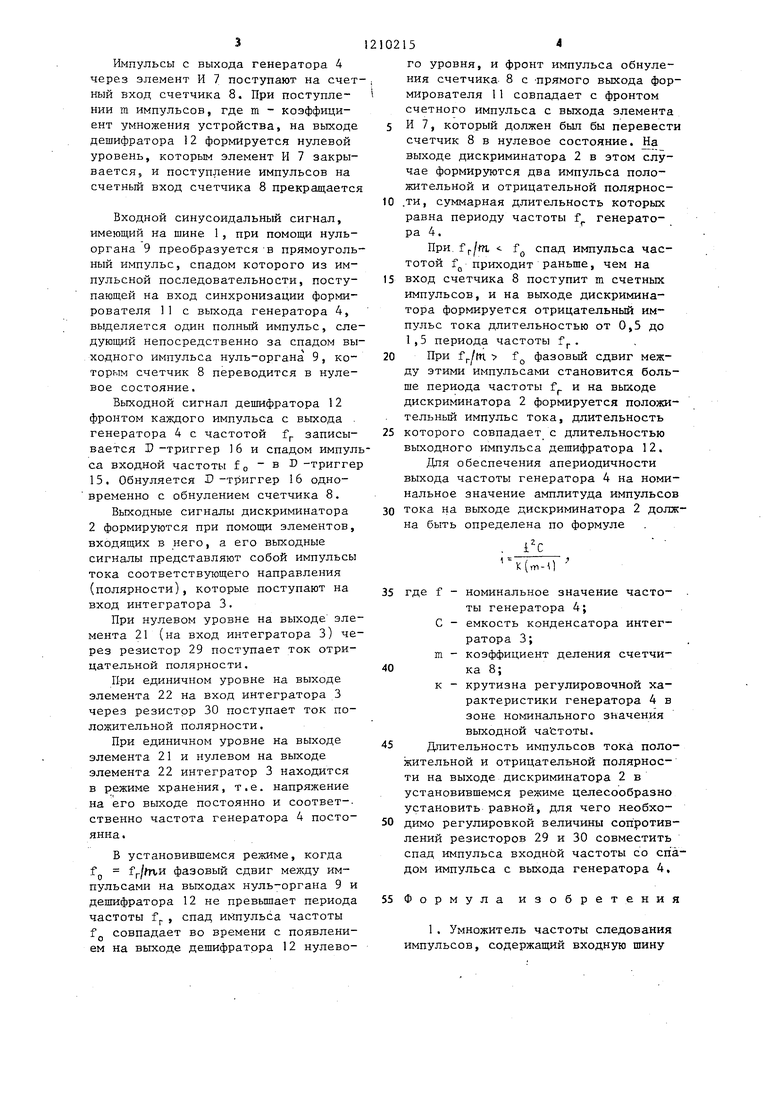

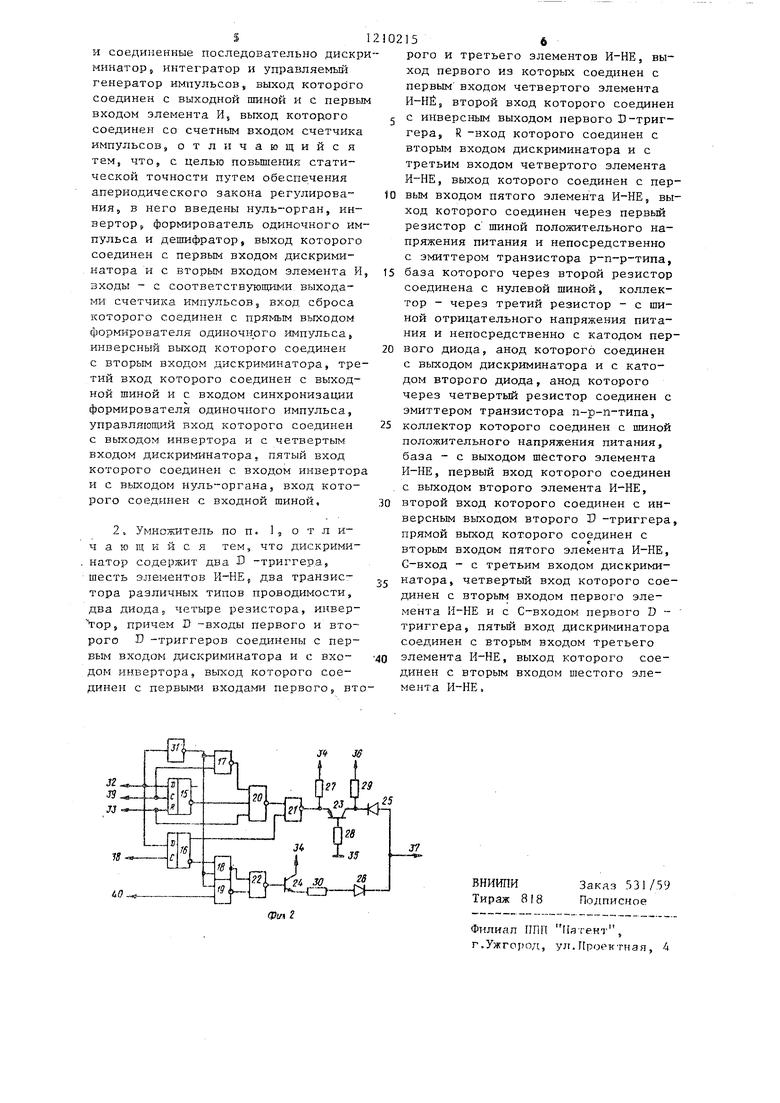

На фиг, 1 приведена электрическая структурная схема умножителя частоты следования импульсов; на фиг« 2 - дискриминатор (фазовый), входящий в умножитель частоты следования импульсов .

Устройство содержит входную пгину 1 и соединенные последовательно дискриминатор 2, интегратор 3, управляемый генератор 4 импульсов, шину 5 логической I, выход генератора 4 соединен с вы ходной шиной бис первым ВХОДОМ- элемента И 7, выход которого соединен с счетным входом счетчика 8 импульсов, нуль-орган 9, инвертор 10 , формирователь 1 1 .одиночного импульса и дешифратор 12, выход которого соединен с первым входом дискриминатора 2 и с вторым входом элемента И 7, входы -- с соответствующими выходами счетчика 8 импульсов 5 вход сброса которого соединен с прямым выходом формирователя 11 одиночного импульса, инверсный выход которого соединен с вторым входом дискриминатора 2,, третий вход которого соединен с вьпсодной шиной бис входом синхронизации формирователя 11 одиночного и гпуль- са, управляющий вход которого соединен с выходом инвертора 10 и с четвертьзм входом дискриминатора 2, пятый вход которого соединен с входом инвертора 10 и с выходом нуль- органа 9, вход которого соединен ;с входной шиной 1j шина 5 логичес- кой 1 соединена с входом логической 1 формирователя 11

Формирователь 11 одиночного импульса может содержать первый 13 и второй 14 В-триггеры, прямой и инверсный выходы первого D-триггера 13 соединены соответственно с прямым и инверсным выходами формирова-. теля I1, вход синхронизации которого соединен с С-входом второго D- триггера 14 и с R-входом первого D-триггера 13, D-вход которого соединен с входом логической I , С- вход - с выходом второго D-тригге102152

ра,, .D -вход которого соединен с управляющим входом формирователя 11.

Дискриминатор 2 содерхшт два D - триггера 15 и 16, шесть элементов И5 НЕ 17-22, два транзистора 23 и 24 различного типа проводимости два диода 25 и 26, четыре резистора 27- 30 и инвертор 31, причем D -входы первого 15 и второго 16 D -триггеlO ров соединены с первым входом 32 дискриминатора 2 и с входом инвертора 31, выход которого соединен с первьми вxoдa ш первого 17 второго 18 и третьего 19 элементов И-НЕ,

15 выход первого из которых - с первым входом четвертого элемента И-НЕ 20, вто5рой вход которого соединен с инверсным выходом первого D -триггера 15, R -вход которого соединен с вто20 рым входом 33 дискриминатора 2 и с третьим входом четвертого элемента И-НЕ 20, выход которого соединен с первым входом пятого элемента И-НЕ 21, выход которого через первый ре25 зистор 27 - с шиной 34 положительного питания и непосредственно с эмиттером транзистора 23 р-п-р-типа база которого через второй резистор

28соединена с нулевой шиной 35, 30 коллектор - через третий резистор

29с шиной 36 отрицательного питания и непосредственно с катодом первого диода 25, анод которого соединен с выходом 37 дискриминатора 2

35 и катодом второго диода 26, анод которого через четвертый резистор 30 с эмиттером транзистора 24 п-р-п-ти па, коллектор которого соединен с шиной 34 положительного питания, ба40 за - с выходом шестого элемента И- НЕ 22J первый вход которого соедине с выходом второго элемента 18, второй вход которого соединен с инверсным выходом второго 1 -тригге45 ра 16, прямой выход которого соединен с вторым входом пятого элемента И-НЕ, С-вход - с третьим входом 38 дискри:минатора 2, четвертый вход 39 которого соединен с вторым входом

50 первого элемента И-НЕ 17 и с С-входом первого Г -триггера 155 пятый вход 40 дискриминатора 2 соединен с вторым входом третьего элемента И-НЕ 19. которого соединен с

55 вторым входом шестого элемента И- НЕ 22,

Устройство работает следующим образом.

31210215

с выхода генератора 4

го ни ми сч

через элемент И 7 поступают на счет ный вход счетчика 8. При поступле- НИИ m импульсов, где m - коэффициент умножения устройства, на выходе дешифратора 12 формируется нулевой уровень, которым элемент И 7 закрывается, и поступление импульсов на счетный вход счетчика 8 прекращаетс

Входной синусоидальный сигнал, имеющий на шине 1, при помощи нуль- органа 9 преобразуется -в прямоугольный импульс, спадом которого из импульсной последовательности, поступающей на вход синхронизации формирователя 11 с выхода генератора 4, выделяется один полный импульс, следующий непосредственно за спадом выходного импульса нуль-органа 9, которым счетчик 8 переводится в нулевое состояние.

Выходной сигнал дешифратора 12 фронтом каждого импульса с выхода . генератора 4 с частотой f записывается Г -триггер 16 и спадом импулса входной частоты f о в D -тригге 15, Обнуляется I -триггер 16 одновременно с обнулением счетчика 8.

Выходные сигналы дискриминатора 2 формируются при помощи элементов, входящих в него, а его выходные сигналы представляют собой импульсы тока соответствующего направления (полярности), которые поступают на вход интегратора 3,

При нулевом уровне на выходе элемента 21 (на вход интегратора 3) через резистор 29 поступает ток отрицательной полярности.

При единичном уровне на выходе элемента 22 на вход интегратора 3 через резистор 30 поступает ток положительной полярности.

При единичном уровне на выходе элемента 21 и нулевом на выходе элемента 22 интегратор 3 находится в режиме хранения, т.е. напряжение на iero выходе постоянно и соответ-- ственно частота генератора 4 постоянна.

В установившемся режиме, когда fp f|-/fT /H фазовый сдвиг между импульсами на выходах нуль-органа 9 и дешифратора 12 не превышает периода частоты fj. , спад импульса частоты f совпадает во времени с появлением на выходе дешифратора 12 нулевого уровня, и фронт импульса обнуления счетчика 8 с -прямого выхода формирователя 11 совпадает с фронтом счетного импульса с выхода элемента

И 7, который должен был бы перевести счетчик 8 в нулевое состояние. На выходе дискриминатора 2 в этом случае формируются два импульса положительной и отрицательной полярнос.ти, суммарная длительность которых равна периоду частоты f генератора 4 .

При. f f спад импульса частотой Гд приходит раньше, чем на

вход счетчика 8 поступит m счетньк импульсов, и на выходе дискриминатора формируется отрицательный импульс тока длительностью от 0,5 до 1,5 периода частоты f.

При fp/fn TQ фазовый сдвиг между этими импульсами становится больше периода частоты f. и на выходе дискриминатора 2 формируется положительный импульс тока, длительность

которого совпадает с длительностью выходного импульса дешифратора 12. Для обеспечения апериодичности выхода частоты генератора 4 на номинальное значение амплитуда импульсов

тока на выходе дискриминатора 2 должна быть определена по формуле

,

)с(,п-0

где f - номинальное значение частоты генератора 4; С - емкость конденсатора интегратора 3;

m - коэффициент деления счетчи- ка 8;

к - крутизна регулировочной характеристики генератора 4 в зоне номинального значения выходной ча стоты.

Длительность импульсов тока положительной и отрицательной полярности на выходе дискриминатора 2 в установившемся режиме целесообразно установить равной, для чего необхо- димо регулировкой величины сопротивлений резисторов 29 и 30 совместить спад импульса входной частоты со спадом импульса с выхода генератора 4.

Формула изобретения

1. Умножитель частоты следования импульсов, содержащий входную шину

S

и соединенные последовательно дискриминатор, интегратор и управляемый генератор импульсов, выход которого соединен с выходной шиной и с первым входом элемента И, выход которого соединен со счетным входом счетчика импульсов, отличающийся тем, что, с целью повьпяеьшя статической точности путем обеспечения апериодического закона регулирования, в него введены нуль-орган, инвертор формирователь одиночного импульса и депшфратор, выход которого соединен с первым входом дискриминатора и с вторым входом элемента И входы - с соответствующи И выходами счетчика импульсов, вход сброса которого соединен с прямым выходом формирователя одиночнрго им:пульса, инверсный выход которого соединен с вторым входом дискриминатора, третий вход которого соединен с выходной шиной и с входом синхронизации формирователя одиночного импульса, управляющий вход которого соединен с выходом инвертора и с четвертым входом дискриминатора, пятый вход которого соединен с входом инвертора и с выходом нуль-органа, вход которого соединен с входной шиной.

2v Умножитель по п. 1 ,, о т л и.- чающийся тем, что дискрими- натор содержит два D -триггера, шесть элементов И-НЕ два транзистора различных типов проводимости, два диода5 четыре резистора, инвер- ор J причем D -входы первого и второго I -триггеров соединены с первым входом дискриминатора и с входом инвертора, выход которого соединен с первыми входами первого, вто10

02

с

15

20

5

0

5

0

156

рого и третьего элементов И-НЕ, выход первого из которых соединен с первым входом четвертого элемента И-НЁЭ второй вход которого соединен с инверс1й1м выходом первого Л-триггера, R -вход которого соединен с вторым входом дискриминатора и с третьим входам четвертого элемента И-НЕ, выход которого соединен с первым входом пятого элемента И-НЕ, выход которого соединен через первый резистор с шиной положительного напряжения питания и непосредственно с эмиттером транзистора р-п-р-типа, база которого через второй резистор соединена с нулевой шиной, коллектор - через третий резистор - с шиной отрицательного напряжения питания и непосредственно с катодом первого диода, анод которого соединен с выходом дискриминатора и с катодом второго диода, анод которого через четвертый резистор соединен с эмиттером транзистора п-р-п-типа, коллектор которого соединен с шиной положительного напряжения питания, база - с выходом шестого элемента И-НЕ, первый вход которого соединен с выходом второго элемента И-НЕ, второй вход которого соединен с инверсным выходом второго И -триггера, прямой выход которого соединен с вторым входом пятого элемента И-НЕ, G-вход - с третьим входом дискриминатора, четвертый вход которого соединен с вторым входом первого элемента И-НЕ и с С-входом первого D - триггера, пятый вход дискриминатора соединен с вторым входом третьего элемента И-НЕ, выход которого соединен с вторым входом шестого элемента И-НЕ,

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Тактовый генератор с контролем | 1986 |

|

SU1378021A1 |

| Дешифратор команд телеуправления | 1989 |

|

SU1709365A1 |

| Устройство для измерения параметров дыхания | 1990 |

|

SU1803037A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО КОНТРОЛЯ ТЕМПЕРАТУРЫ | 2015 |

|

RU2631018C2 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство управления фазоимпульснымСчЕТчиКОМ | 1979 |

|

SU851780A1 |

| Частотно-импульсное устройство преобразования сигнала с мостового датчика | 1986 |

|

SU1383474A1 |

Изобретение относится к импульсной технике и может быть использовано в измерительных преобразователях, например, угла поворота вала в код. Целью изобретения является повышение статической точности. Умножитель содержит входную шину 1 и соединенные последовательно дискриминатор (D) 2, интегратор 3, управляемый генератор 4 импульсов, шину 5 логической 1,инвертор 10, формирователь 11 одиночного импульса и дешифратор 12. Выход генератора 4 соединен с выходной шиной 6 и первым входом элемента И 7. Выход этого элемента соединен со счетным входом счетчика 8 импульсов. Формирователь 11 может содержать первый и второй D-триггеры. D 2 содержит D-тригге- ры, элементы И-НЕ, транзисторы, диоды и инвгртор. Дпя нормальной работы умножителя длительность импульсов тока положительной и отрицательной полярности на выходе D 2 в установившемся режиме целесообразно устанавливать равной. Введение нуль- органа 9, инвертора 10, формирователя 11 одиночного импульса, дешифратора 12 и образование новых связей между элементами устройства позволяет обеспечить апериодический закон регулирования. 1 3 п. ф-лы. 2 ил. (О С .Ю О 1C ел

J Jff

4(7

ВИНИЛИ Тираж 8 18

Заказ 531/59 Подписное

Ф(/« 2

Филиал ППП Пятент, г.Ужгоро/т, ул. Проектная, 4

| Умножитель частоты повторения импульсов | 1981 |

|

SU1056372A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Широкополосный умножитель частоты следования импульсов | 1978 |

|

SU712971A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-07—Публикация

1984-08-13—Подача