Изобретение относится к вычислительной технике и автоматике и может найти применение в системах передачи, приема и обработки информации, в частности в системах дистанционного управления различными объектами в электромагнитном диапазоне.

Целью изобретения является повышение помехозащищенности.

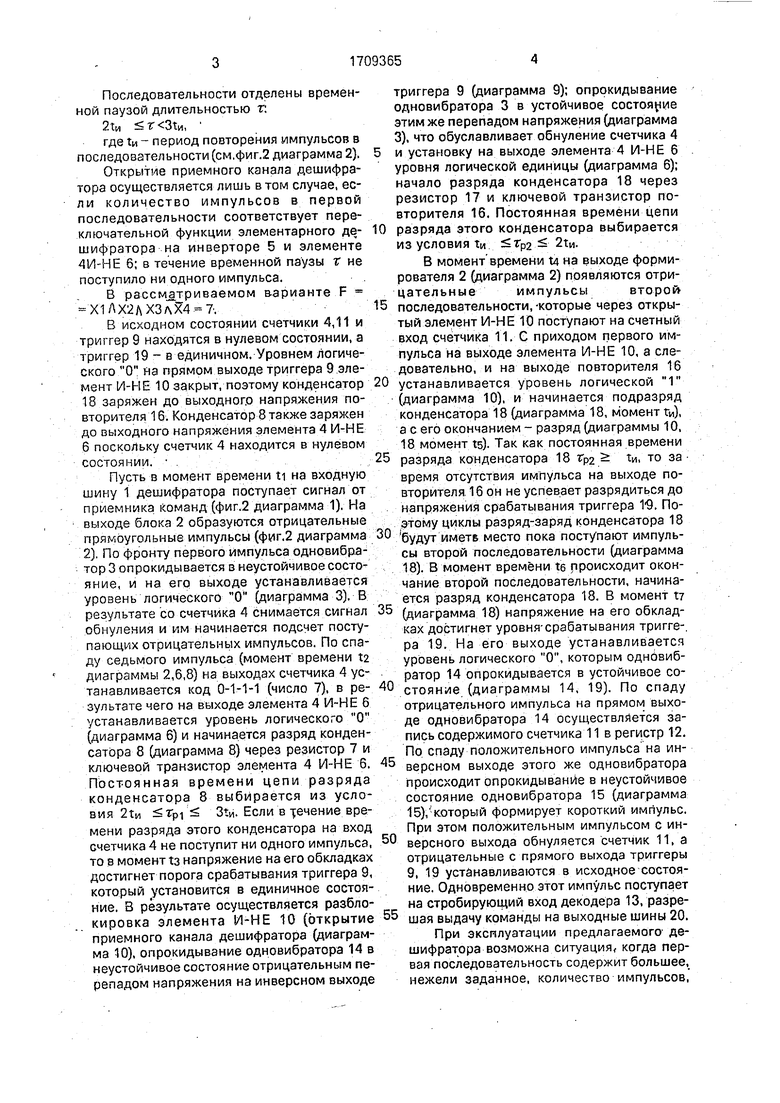

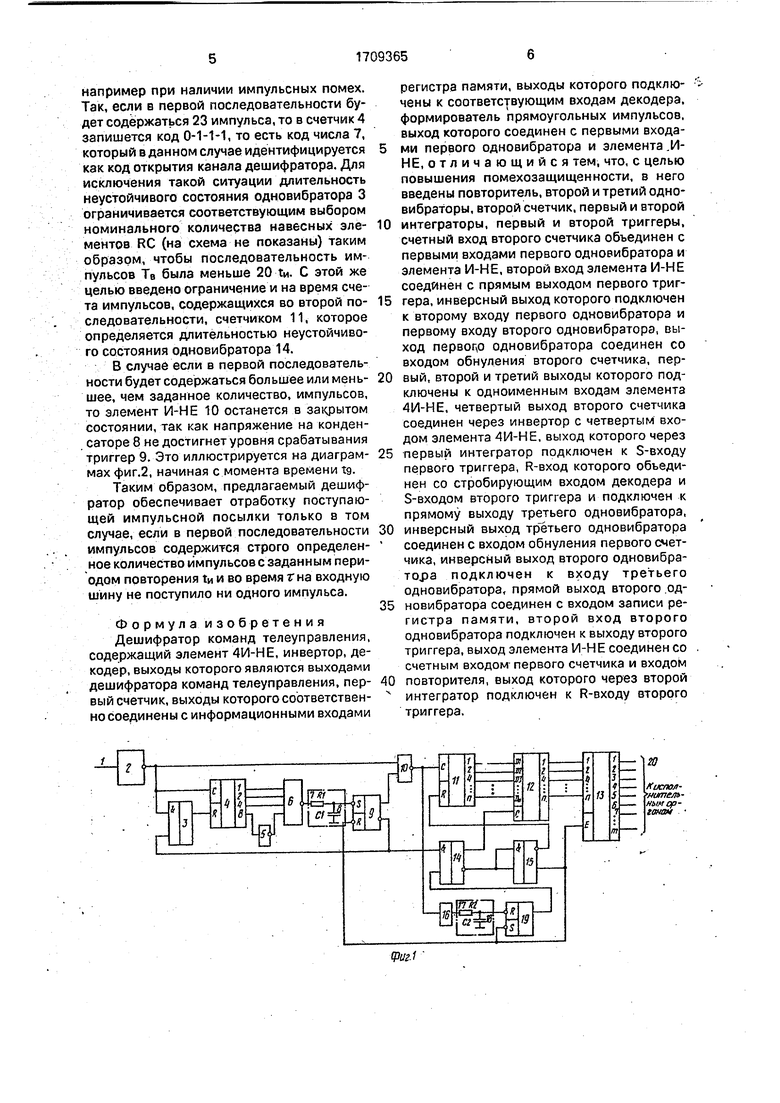

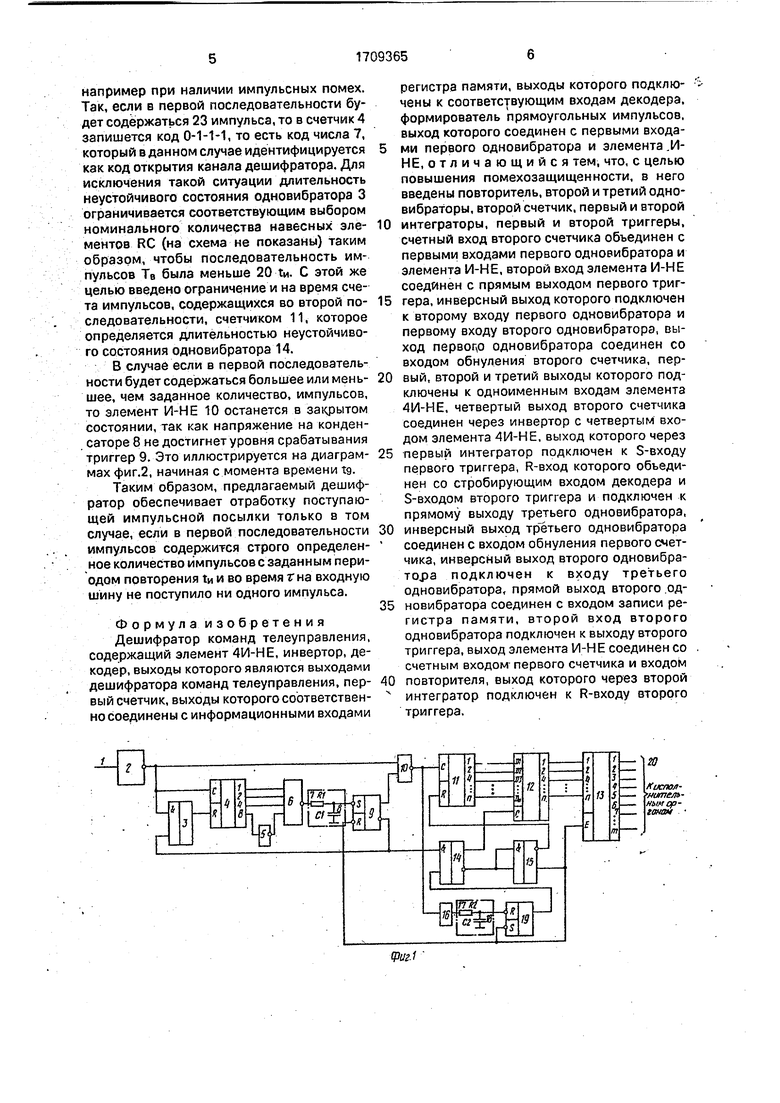

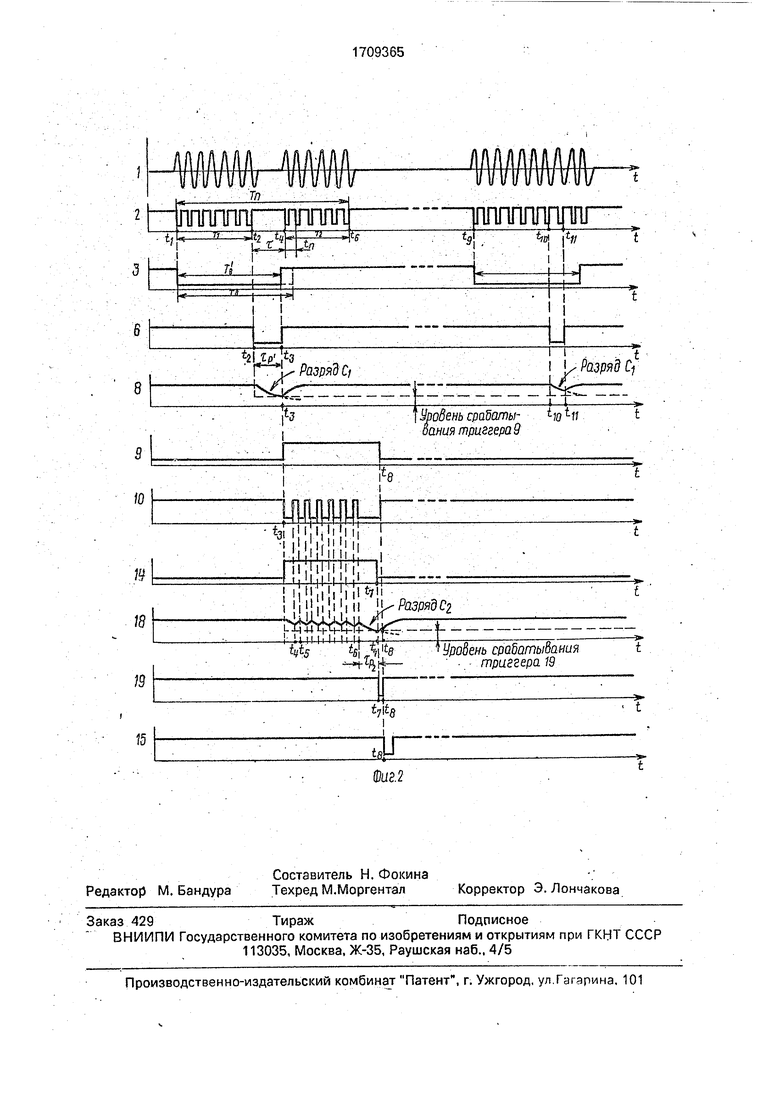

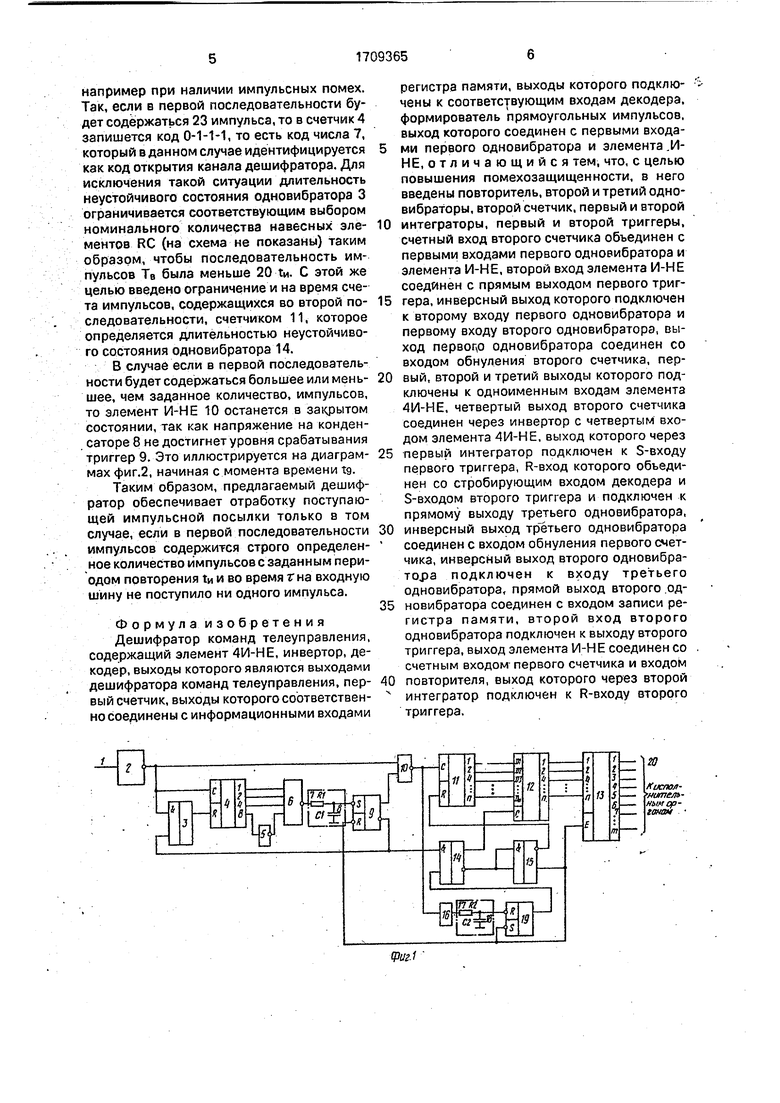

На фиг.1 представлена схема устройства; на фиг,2 - временные диаграммы.

Устройство содержит входную шину 1, формирователь прямоугольных импульсов 2, первый одновибратор 3, второй счетчик 4, инвертор 5, элемент 4И-НЕ 6, первую интегрирующую цепь, содержащую резистор 7 и

конденсатор 8, первый триггер 9. элемент И-НЕ 10, первый счетчик 11, регистр 12, декодер 13, второй 14 и третий 15 одновибраторы, повторитель 16, вторую .интегрирующую цепь, содержащую резистор 17 и конденсатор 18, второй триггер 19, выходные шины 20.

Принцип работы данного дешифратора основан на следующем. Импульсная посылка длительностью Тп от передатчика команд содержит две последовательности импульсов; пербая последовательность импульсов представляет собой код открытия приемного канала дешифратора и имеет длительность Ti; вторая - код команды и имеет длительность Та.

Последовательности отделены временной паузой длительностью т.

2Ти ,

где 1и - период повторения импульсов в последовательности (см,фиг.2 диаграмма 2).

Открытие приемного канала дешифратора осуществляется лишь в том случае, если количество импульсов в первой последовательности соответствует переключательной функции элементарного дешифратора на инверторе 5 и элементе 41/1-НЕ 6; в течение временной паузы т не поступило ни одного импульса,

В рассм триваемом варианте F Х1ЛХ2ЛХЗлХ4 Т.

В исходном состоянии счетчики 4,11 и триггер 9 находятся в нулевом состоянии, а триггер 19 - в единичном. Уровнем логического О на прямом выходе триггера 9.элемент И-ЫЕ 10 закрыт, поэтому конденсатор 18 заряжен до выходного напряжения повторителя 16. Конденсатор 8 также заряжен до выходного напряжения элемента 4 И-НЕ 6 поскольку счетчик 4 находится в нулевом состоянии. .

Пусть в момент времени ti на входную шину 1 дешифратора поступает сигнал от приемника команд (фиг.2 диаграмма 1), На выходе блока 2 образуются отрицательные прямоугольные импульсы (фиг.2 диаграмма 2). По фронту первого импульса однрвибратор 3 опрокидывается в неустойчивое состояние, и на erq выходе устанавливается уровень логического О (диаграмма 3). В результате со счетчика 4 снимается сигнал обнуления и им начинается подсчет поступающих отрицательных импульсов. По спаду седьмого импульса (момент времени t2 диаграммы 2,6,8) на выходах счетчика 4 устанавливается код 0-1-1-1 (число 7), в результате чего на выходе элемента 4 И-НЕ 6 устанавливается уровень логического О (диаграмма 6) и начинается разряд конденсатора 8 (диаграмма 8) через резистор 7 и ключевой транзистор элемента 4 И-НЕ 6. Постоянная времени цепи разряда конденсатора 8 выбирается из условия 2Ти 3tH. Если в-речение времени разряда этого конденсатора на вход счетчика 4 не поступит ни одного импульса, то 8 момент t3 напряжение на его обкладках достигнет порога срабатывания триггера 9, который установится в единичное состояние. В результате осуществляется разблокировка элемента И-НЕ 10 (открытие приемного канала дешифратора (диаграмма 10), опрокидывание однрвибратора 14 в неустойчивое состояние отрицательным перепадом напряжения на инверсном выходе

триггера 9 (диаграмма 9); опрокидывание одновибратора 3 в устойчивое состоя 1ие этим же перепадом напряжения (диаграмма 3), что обуславливает обнуление счетчика 4

и установку на выходе элемента 4 И-НЕ 6 уровня логической единицы (диаграмма 6); начало разряда конденсатора 18 через резистор 17 и ключевой транзистор повторителя 16. Постоянная времени цепи

разряда этого конденсатора выбирается из условия tw :STp2 S 2ги.

В момент времени t4 на выходе формирователя 2 (диаграмма 2) появляются отрицательныеимпульсывторой

последовательности, -которые через открытый элемент И-НЕ 10 поступают на счетный вход счетчика 11. G приходом первого импульса на выходе элемента И-НЕ 10, а следовательно, и на выходе повторителя 16

устанавливается уровень логической 1 (диаграмма 10), и начинается подразряд конденсатора 18 (диаграмма 18, момент Ги), ас его окончанием - разряд (диаграммы 10, 18 момент ts). Так как постоянная времени

разряда конденсатора 18 fpz tn, то за время отсутствия импульса на выходе повторителя, 16 он не успевает разрядиться до напряжения срабатывания триггера 19. По;этому циклы разряд-заряд конденсатора 18

будут иметь место пока поступают импульсы второй последовательности (диаграмма 18). В момент времени te происходит окончание второй последовательности, начинается разряд конденсатора 18. В момент t

(диаграмма 18) напряжение на его обкладках достигнет уровня-срабатывания тригге-. ра 19. На его выходе устанавливается уровень логического О, которым однбвибратор 14 опрокидывается в устойчивое состояние (диаграммы 14, 19). По спаду отрицательного импульса на прямом выходе одновибратора 14 осуществляется запись содержимого счетчика 11 в регистр 12. По. спаду положительного импульса на инверсном выходе этого же одновибратора происходит опрокидыван1 е а неустойчивое состояние одновибратора 15 (диаграмма 15),который формирует короткий импульс. При этом положительным импульсом с инверсного выхода обнуляется счетчик 11, а отрицательные с прямого выхода триггеры 9, 19 устанавливаются в исходное состояние. Одновременно этот импульс поступает на стробируюцдий вход декодера 13, разрешая выдачу команды на выходные шины 20. При эксплуатации предлагаемого дешифратора возможна ситуация, когда первая последовательность содержит большее, нежели заданное, количество импульсов. например при наличии импульсных помех. Так, если в первой последовательности будет содержаться 23 импульса, то в счетчик 4 запишется код 0-1-1-1, то есть код числа 7, который в данном случае идентифицируется как код открытия канала дешифратора. Для исключения такой ситуации длительность неустойчивого состояния одновибратора 3 ограничивается соответствующим выбором номинального количества навесных элементов RC (на схема не показаны) таким образом, чтобы последовательность импульсов Тв была меньше 20 Ти. С этой же целью введено ограничение и на время счета импульсов, содержащихся во второй последовательности, счетчиком 11, которое определяется длительностью неустойчивого состояния одновибратора 14. В случае если в первой последовательности будет содержаться большее или меньшее, чем заданное количество, импульсов, то элемент И-НЕ 10 останется в забытом состоянии, так как напряжение на конденсаторе 8 не достигнет уровня срабатывания триггер 9. Это иллюстрируется на диаграммах фиг.2, начиная с момента времени tg. Таким образом, предлагаемый дешифратор обеспечивает отработку поступающей импульсной посылки только в том случае, если в первой последовательности импульсов содержится строго определенное количество импульсов с заданным периодом повторения Ги и во время г на входную шину не поступило ни одного импульса. Формул аи зоб ретения Дешифратор команд телеуправления, содержащий элемент 4И-НЕ, инвертор, декодер, выходы которого являются выходами дешифратора команд телеуправления, первый счетчик, выходы которого соответственно соединены с информационными входами 5 10 15 20 25 30 35 40

Киспол Humejitнын оргонамрегистра памяти, выходы которого подключены к соответствующим входам декодера, формирователь прямоугольных импульсов, выход которого соединен с первыми входами первого одновибратора и элемента .ИНЕ, отличающийся тем, что, с целью повышения помехозащищенности, в него введены повторитель, второй и третий одновибраторы, второй счетчик, первый и второй интеграторы, первый и второй триггеры, счетный вход второго счетчика объединен с первыми входами первого одновибратора и элемента И-НЕ, второй вход элемента И-НЕ соединен с прямым выходом первого триггера, инверсный выход которого подключен к второму входу первого одновибратора и первому входу второго одновибратора, выход первого одновибратора соединен со входом обнуления второго счетчика, первый, второй и третий выходы которого подключены к одноименным входам элемента 4И-НЕ, четвертый выход второго счетчика соединен через инвертор с четвертым входом элемента 4И-НЕ, выход которого через первый интегратор подключен к S-входу первого триггера, R-вход которого объединен со стробирующим входом декодера и S-входом второго триггера и подключен к прямому выходу третьего одновибратора, инверсный выход третьего одновибратора соединен с входом обнуления первого с етчика, инверсный выход второго одновибратора подключен к входу третьего одиовибратора, прямой выход второго .одновибратора соединен с входом записи регистра памяти, второй вход второго одновибратора подключен к выходу второго триггера, выход элемента И-НЕ соединен со счетным входом первого счетчика и входом повторителя, выход которого через второй интегратор подключен к R-входу второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ЧЕТЫРЕХФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1998 |

|

RU2133550C1 |

| Устройство для контроля знаний обучаемых | 1990 |

|

SU1758658A1 |

| Устройство автоматического управления диапроекторами | 1987 |

|

SU1453361A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Устройство автоматического управления диапроекторами | 1987 |

|

SU1515136A1 |

| Устройство для цифрового управления тиристорным регулятором | 1990 |

|

SU1744774A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| СИСТЕМА ОХРАННОЙ СИГНАЛИЗАЦИИ | 1993 |

|

RU2092903C1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

Изобретение относится к вычислительной технике и обеспечивает отработку командтелеуправления, импульсная посылка которых состоит из двух последовательностей, разделенных временной паузой. Первая последовательность импульсов содержит код открытия приемного канала дешифратора, вторая - код номера крман- ды. Цель изобретения - повышение помехозащищенности устройства. Предлагаемый дешифратор содержит три одновибратора, два счетчика, регистр, инвертор, повторитель, два элемента И-НЕ, два RS-триггера, две интегрирующие RC-цепи, декодер. Цель достигается, во-первых, за счет закрытого состояния приемного канала дешифрации. Его открытие осуществляется в том случае, если количество импульсов в первой последовательности соответствует переключательной функции элементарного дешифратора на счетчике импульсов и логическом элементе 4И-НЕ, и во время паузы, разделяющей импульснь1е последовательности, не поступило ни одного импульса; во-вторых, за счет установления функциональной зависимости между длиной передаваемой команды (второй и_мпульсной последовательностью) и временем открытого состояния приемного канала дешифратора: Тсч = N'tn + Тр2, где N - количество импульсов в последовательности. 2 ил.! С;i \оС/)

| Журнал "Радио" | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Механический грохот | 1922 |

|

SU41A1 |

Авторы

Даты

1992-01-30—Публикация

1989-11-21—Подача