1

Изобретение относится к вычислительной технике и может быть использовано в измерительно-информационных системах для вьтолнения операций умножения и деления кодов.

Цель изобретения - упрощение устройства.

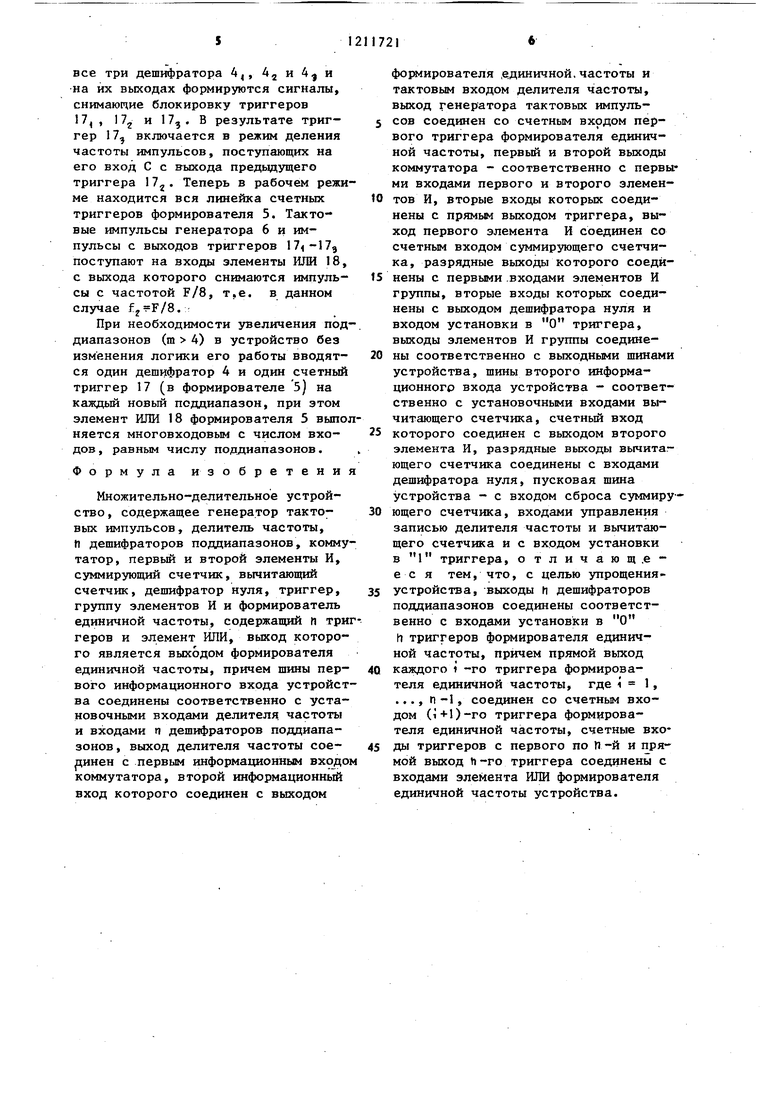

На чертеже представлена функциональная схема множительно-делитель- ного устройства.

Устройство содержит делитель 1 частоты, установочные входы которого соединены соответственно с шина- ми 2 первого информационного входа устройства, коммутатор 3, п дешифраторов 4 поддиапазонов, формирователь 5 единичной частоты, генератор 6 тактовых импульсов, первый и второй элементы И 7, 8, суммирующий счетчик 9, группу элементов И 10, выходы которых соединены соотв тствен- но с выходными шинами 11 устройства, вычитающий счетчик 12, установочные входы которого соединены соответственно с шинами 13 второго информационного входа устройства, дешифратор 14 нуля, триггер 15 и пусковую шину 16, причем формирователь 5 единичной частоты содержит п триггеров 17 и элемент ИЛИ 18, шины 2 первого информационного входа устройства соединены с входами д дешифраторов 4 поддиапазонов, выход делителя 1 частоты соединен с первым информационным входом коммутатора 3, второй информационный вход которого соединен с выходом формирователя 5 единичной частоты и тактовым входом делителя 1 частоты, выход генератора 6 тактовых импульсов соединен со счетным входом первого триггера 17 формирователя 5 единичной частоты, первый и второй выходы коммутатора 3 соединены соответственно с первыми вхо дами элементов И 7, 8, вторые входы которых соединены с прямым выходом триггера 15, выход элемента И 7 соединен со счетным входом суммирующего счетчика 9, разрядные выходы которого соединены с первьми входами элементов И 10 группы, вторые входы которых соединены с выходом дешифратора 14 нуля и входом установки в триггера 15, выход элемента ИЗ соединен со счетным входом вычитающего счетчика 12, разрядные выходы которого соединены с входами дешифратора 14 нуля, пусковая шина 16

212

устройства - с входом сброса сумми рующего счетчика 9, входами управления записью делителя 1 частоты и вычитающего счетчика 12, и с входом установки в 1 триггера 15, выходы п дешифраторов 4 поддиапазонов соединены соответственно с входами установки в О п триггеров 17 формирователя 5 единичной частоты,

причем прямой выход каждого предыдущего триггера I7 соединен со счетным входом последующего триггера 17, счетные входы триггеров 17 с первого по п-ый и прямой выход п-го триггера 17 - с входами элемента ИЛИ 18, выход которого является выходом формирователя 5 единичной частоты.

Устройство работает следующим образом.

В исходном состоянии схемы триггер 15 находится в положении О, элементы И 7 и 8, управляемые этим триггером, закрыты и не пропускают импульсы.на счетные входы соответствующих счетчиков 9 и 12. В момент появления запускающего импульса на пусковой шине 16 устройства триггер 15 устанавливается в положение 1, при этом одновременно данный

импульс сбрасывает в нулевое положение суммирующий счетчик 9 и разрешает запись в вычитающий счетчик 12 кода Б с второго информационного входа 13 устройства, этот же импульс сбрасьшает в нулевое положение делитель 1 частоты и разрешает запись кода А с первого информационного входа 2 устройства, элементы И 7 и 8 начинают пропускать импульсы

на счетные входы счетчиков 9 и 12, так как на их управляющие входы подается разрешаюш 1й потенциал с выхода триггера 15.

Делитель I частоты формирует импульсы с частотой f,, прямопропорциональ- ной коду А, причем если передаточный коэффициент делителя равен 1, то i,, А. Формирователь 5, подключенный к генератору 6 тактовых

импульсов, формирует счетные импульсы с частотой f. В зависимости от положения переключателей коммутатора 3 импульсы с выходов делителя 1 частоты и формирователя 5 поступают

через элементы И 7 и 8 на счетные входы счетчиков 9 и 12.

Если переключатели коммутатора 3 находятся в положении Умножеиие,

31

то импульсы с частотой f, , проходя через открытый элемент И 7, начинают заполнять суммирующий счетчик 9, а импульсы с частотой f, проходя через открытый элемент И 8, вычитают код Б, находящийся в счетчике 12. Через интервал времени ut, равньй

At

содержимое счетчика 12 достигает нуля,что фиксирует дешифратор 14,ииг- пульс с выхода которого возвращает триггер 15 в нулевое состояние (при этом элементы И 7 и 8 вновь закрываются и прекращается поступление импульсов на счетчики 9 и 12) и разрешает считьшание содержимого счет- .чика .9 через группу элементов И 10 на выходную шину П устройства. При этом код счетчика 9 N f, at, атак как f, А, At пропорционально Б, то при f2 1 получаем N А -Б.

Если переключатели коммутатора 3 находятся в положении Деление, то импульсы с частотой f, через элемент И 8 поступают на счетный вход счетчика 12, вычитая содержащийся в нем код Б, а импульсы с частотой f через элемент И 7 поступают на счетный вход счетчика 9. Дальнейшая последовательность операций аналогична рассмотренной, т.е. в момент обнуления счетчика 12 (через интервал времени

-г- с момента появления А

импульса на пусковой шине 16} сраба- тьгоает дешифратор 14, импульс с выхода которого возвращает триггер 15 в нулевое состояние, разрешает считывание содержимого счетчика 9 через группу элементов И 10 на выходную ши ну 11 устройства и т.д. Код в счетчике 9 в момент срабатывания дегаиф- ратора 14 равен результату выполняем мой в данном режиме операции, т.е.

N it - f, ..

Значение числа А может находиться в одном из следующих поддиапазонов:

1-й О А 0,125 А,,,; 2-й 0,125 ,, сА 0,25 ,; 3-й 0,25 ,, .А 0,5. 4-й 0,5 А,А ,,

В зависимости от значения А сраба- тьшают те или иные дешифраторы 4, 42 ... 4„ поддиапазонов (,, где п - число поддиапазонов, в рас-

11721

сматриваемом случае , ). Эти дешифраторы управляк1т формирователем 5 таким образом, чтобы обеспечить требуемый коэффициент деления часто5 ты тактовых импульсов.

Если значение А находится в первом поддиапазоне, то ни один из дешифраторов поддиапазонов не cpa6ai тьюает. Запрещающий потенциал с вы10 хода дешифратора (,.... р-1) блокирует триггер 17 формирователя 5 по входу установки в О. Таким образом, счетные триггеры 17, соединенные последовательно, в данном

t5 поддиапазоне блокируются. На их выходах, связанных с соответствующими входами элемента ИЛИ 18, формируется потенциал уровнем логического нуля. Тактовые импульсы генератора 6 че20 рез элемент ИЛИ 18 поступают на выход формирователя 5, т.е. частота F этих импульсов не изменяется (fe F)

Если значение А находится во вто25 ром поддиапазоне, то срабатывает дешифратор 4 J и на его выходе формируется сигнал, снимающий блокировку триггера I7 . В результате триггер 17, включается в режим деле30 ния частоты импульсов, поступающих на его вход С, с коэффициентом деления, равным двум. Остальные триггеры по-преннему блокированы дешифраторами 4 и 4q. Тактовые импульсы генератора 6 и импульсы с выхода тригге- ра 17, поступают на входы элемента ИЛИ 18, с выхода которого снимаются импульсы с частотой F/2, т.е. в данном случае

35

40

f, F/2.

Если значение А находится в третьем поддиапазоне, то срабатывают дешифраторы 4I и 42 и на их выходах формируются сигналы, снимающие блокировку триггеров 17 и 17. В результате триггер 17,включается в режим деления частоты импульсов, поступающих на его вход С с выхода предьщу- щего триггера 17. Триггер 17 попрежнему блокирован дешифратором 4,. Тактовые импульсы генератора 6, им- пульСы с выходов триггеров 17, и 17j поступают на входы элемента ИЛИ 18, с выхода которого снимаются импульсы с частотой F/4, т.е. в данном случае выполняется .

Если значение А находится в четвертом поддиапазоне, то срабатывают

все три дешифратора 4,, Ад и i на их выходах формируются сигналы, снимающие блокировку триггеров 17, , 17g и 17,. В результате триг- гер 17, включается в режим деления частоты импульсов, поступающих на его вход С с ныхода предьщущего триггера 17. Теперь в рабочем режиме находится вся линейка счетных триггеров формирователя 5. Тактовые импульсы генератора 6 и импульсы с выходов триггеров поступают на входы элементы ИЛИ 18, с выхода которого снимаются импуль- сы с частотой F/8, т.е. в данном случае .При необходимости увеличения поддиапазонов (т 4) в устройство без изменения логики его работы вводят- ся один дешифратор 4 и один счетный триггер 17 (в формирователе 5) на каждый новый поддиапазон, при этом элемент ИЛИ 18 формирователя 5 выполняется многовходовым с числом вхо- ДОН, равным числу поддиапазонов.

Формула изобретения

Множительно-делительное устройство , содержащее генератор такто- вых импульсов, делитель частоты, ti дешифраторов поддиапазонов, коммутатор, первый и второй элементы И, суммирующий счетчик, вычитающий счетчик, дешифратор нуля, триггер, группу элементов И и формирователь единичной частоты, содержащий п триггеров и элемент ИЛИ, выход которого является выходом формирователя единичной частоты, причем шины пер- вого информационного входа устройства соединены соответственно с установочными входами делителя, частоты и входами п дешифраторов поддиапазонов , выход делителя частоты сое- динен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом

фо ; 1ирователя .единичной, частоты и тактовым входом делителя частоты, выход генератора тактовых импульсов соединен со счетным входом первого триггера формирователя единичной частоты, первый и второй выходы коммутатора - соответственно с первы ми входами первого и второго элементов И, вторые входы которых соединены с прямым выходом триггера, выход первого элемента И соединен со счетным входом суммирующего счетчика, разрядные выходы которого соединены с первыми .входами элементов И группы, вторые входы которых соединены с выходом дешифратора нуля и входом установки в О триггера, выходы элементов И группы соединены соответственно с выходными шинами устройства, шины второго информационного входа устройства - соответственно с установочными входами вычитающего счетчика, счетньй вход которого соединен с выходом второго элемента И, разрядные выходы вычитающего счетчика соединены с входами дешифратора нуля, пусковая шина устройства - с входом сброса сз ммиру ющего счетчика, входами управления записью делителя частоты и вычитающего счетчика и с входом установки в 1 триггера, о тличающ.е- е с я тем, что, с целью упрощения- устройства, выходы И дешифраторов поддиапазонов соединены соответственно с входами установки в О

h триггеров формирователя единичной частоты, причем прямой выход каждого i -го триггера формирователя единичной частоты, где i 1,

..., л-1, соединен со счетным входом (i+l)-ro триггера формирователя единичной частоты, счетные входы триггеров с первого по П-и и прямой выход h-го триггера соединены с входами элемента ИЛИ формирователя единичной частоты устройства.

JL &

Оэ

н

VN

Csj

Составитель В.Гусев Редактор НЛИвьщкая Техред 3.Палий Корректор Л. Пилипенко

Заказ 641/53 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная,4

9

N

c

4-e

гз

V«v

J

33

«

Tl

«kc tj

J .

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое множительно-делительное устройство | 1981 |

|

SU1012246A2 |

| Цифровой измеритель отношения временных интервалов | 1986 |

|

SU1322223A1 |

| АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1991 |

|

RU2043648C1 |

| Измеритель переходных характеристик частотных прецизионных устройств | 1987 |

|

SU1620992A1 |

| Цифровое фазосдвигающее устройство | 1984 |

|

SU1241148A1 |

| Устройство для измерения искажений дискретных сигналов | 1986 |

|

SU1327309A1 |

| Преобразователь временных параметров импульсных последовательностей | 1980 |

|

SU900445A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1367036A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Трехальтернативный частотный компаратор | 1989 |

|

SU1780161A1 |

Изобретение относится к области вычислительной техники и может быть использовано в измерительно-информационных системах для выполнения операции умножения и деления кодов. Цель изобретения - упрощение устройства. Устройство содержит делитель частоты, коммутатор, п дешифраторов поддиапазонов, формирователь единичной частоты, генератор тактовых импульсов, суммирующий счетчик, группу элементов И, вычитающий счетчик, дешифратор нуля, (n+f) триггеров и элемент ИЛИ. Делитель частоты формирует импульсы с частотой ,,, прямопропорхщональной коду А.Причем если передаточный коэффициент делителя равен .единице, -то 1, А. Формирователь, подключенный к генератору тактовых импульсов, формирует счетные импульсы с частотой i . В зависимости от положения переключателей коммутатора импульсы с выходов делителя частоты и формирователя поступают через два элемента И на счетные входы счетчиков. 1 шт. § (О

| ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 0 |

|

SU271115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровое множительно-делительное устройство | 1981 |

|

SU1012246A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-15—Публикация

1984-08-10—Подача