(54) УСТРОЙСТВО ТАКТОВОЙ CVlHXPOHK3AlIHH

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство поэлементного фазирования | 1980 |

|

SU928665A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU965005A2 |

| Устройство для синхронизации приемника телеграфных сигналов | 1980 |

|

SU970715A1 |

| Усредняющее устройство с блокировкой для фазирования дискретной информации | 1980 |

|

SU896785A2 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

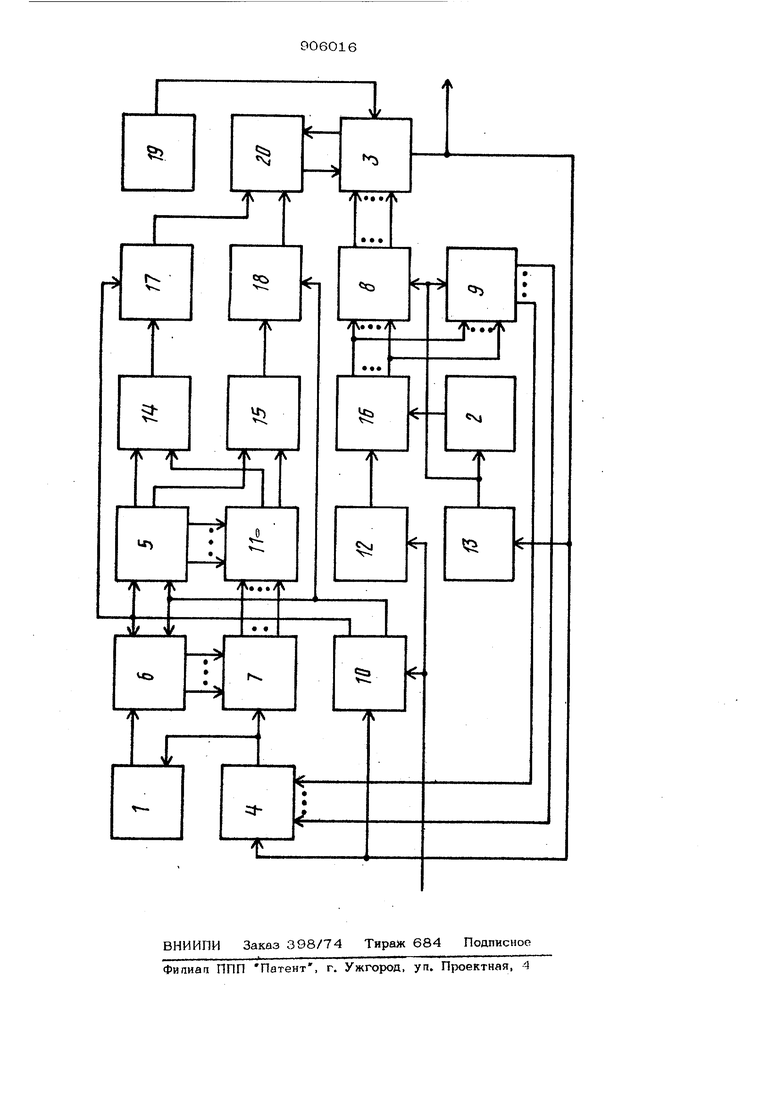

Изобретение относится к передаче дискретных сообщений и может быть использовано для обеспечения тактовой синх ронизации приемной части аппаратуры. Известно устройство тактовой синхронизации, содержащее последовательно соединенные блок управления, первый управляемый делитель и фазовый дискриминатор выходы которого подключены к суммирующему и вычитающему входам первого реверсивного счетчика, а также задающий генератор , интегратор и последовательно соединенные первый триггер и первый элемент И, при этом выход задающего генератора подключен к второму входу первого управляемого делителя 1 . Однако известное устройство обладает низкой точностью и малым быстродействием фазирования. Цель изобретения - повышение точности и быстродействия фазирования. Цель достигается тем, что в устройство тактовой синхронизации, содержащее последовательно соединенные блок управления, первый управляемый делитель и фазовый дискриминатор, выходы которого подключены к суммирующему и вычитающему входам первого реверсивного счетчика, а также задающий генератор, интегратор и последовательно соединенные первый триггер и первый элемент И, при этом вход задающего генератора подключен к второму входу первого управляемого делителя, введены последовательно соединенные второй управляемый делитель, первый элемент задержки, второй реверсивный счетчик, первый дешифратор и коммутатор, а также формирователь переднего фронта импульса, делитель, второй элемент задержки, второй и третий дешифраторы и последовательно соединенные второй триггер и второй элемент И, к второму входу которого, а также второму входу первого И, вычитающему и суммирующему входам второго реверсивного счетчика подключены соответствующие выходы фазового аискриминатора, авыходы первого и второго эле(ментов И подключены соответственно к суммирующему и вычитающему входам блока управления, к тактовому входу кото рого подключен второй выход первого управляемого делителя, к управляющим входам которого подключены выходы второго дешифратора, ко входам которого и входам третьего деши4ратора подключены выходы интегратора, ко. входу которого подключен выход формирователя передне- го фронта импульса, вход которого объединен с информационным входом фазового дискриминатора, а к сбросовому входу интегратора через второй элемент задержки и тс управляющим входам второго и третьего дешифраторов .непосредственн подключен выход делителя, к счетному входу которого и счетному входу второго управляемого делителя подключен первый выход первого управляемого делителя, при этом выходы третьего дешифратора подключены ко входам установки начальных состояний второго управляемого делителя, выход которого подключен к упра ляющему входу первого дешифратора, а выходы первого реверсивного счетчика подключены к установочным входам первого и второго триггеров, к сбросовым (Входам которых подключены выходы коммутатора, к вторым входам которого подключены вторые выходы первого реверсивного счетчика. На чертеже представлена структурная электрическая схема устройства. Устройство тактовой синхронизации со держит первый и второй элементы задерж ки 1 и 2, первый и второй управляемые делители 3 и 4, первый и второй реверсивные счетчики 5 и 6, первый, второй и третий дешифраторы 7-9, фазовый дискриминатор Ю, коммутатор 11, форм рователь 12 переднего фронта импульса, делитель 13, первый и второй триггеры 14 и 15, интегратор 16, первый и второй элементы И 17 и 18, задающий генератор 19, блок 20 управления. Устройство работает следующим образом. Последовательность импульсов высокой частоты поступает с выхода задаклцего генератора 19 на вход первого управляемого делителя 3, на выходе которого фор мируется последовательность тактовых импульсов, следуемых с частотой, близкой к скорости .аискретной модуляции (скорости телеграфирования) принимаемы сообщений, поступающих на информационные входы фазового дискриминатора 10 и формирователя 12 переднего фронта импульса. Фазовый дискриминатор 1О осуществляет сравнение фазы принимаемых элементов сообщения с фазой тактовых нмпуль сов и прв их несовпадении на одном из его выходов формируется корректирующий импульс (добавления или вычитания), поступающий на соответствующие входы (суммирующие или вычитающие) реверсивных счетчиков 5 и 6. Первый реверсивный счетчик 5, осуществляя защиту от ложной подстройки частоты при случайных искажениях принимаемых элементов сообщения, производит усреднение входных величин. ЕС; и число импульсов, поступак на один из входов (например, суммирующий) первого реверсивного счетчика 5, превышает число импульсов, поступивших на его второй вход (вычитающий), на величину, равную коэффициенту пересчета первого реверсивного счетчика 5, на одном из выходов его последних разрядов ( в данном случае выходе разряда добавления) формируется импульс, устанавливающий соответствующий триггер (в данном случае первый триггер 14) в единичное состояние. Вследствие этого импульсы добавления проходят через первый элемент И 17 на суммирующий вход блока 20 управления без усреднения. Сброс первого триггера 14 в нулевое состояние для защиты от случайных искажений принимаемых элементов сообщения производится через коммутатор 11 сигналом с выхода промежуточного разряда вычитания первого реверсивного счетчика 5, т е. частично усредненным сигналом. Работа второго триггера 15 и второго элемента И 18 полностью аналогична работе первого триггера 14 и первого элемента И 17. При этом установка второго триг гера 15 в единичное состояниепроизводится максимально усредненным импульсом с выхода последнего разряда вычитания первого реверсивного счетчика 5, а его перевод в нулевое состояние осущестгпяется через коммутатор 11 частично усредненным сигналом с выхода промежуточного разряда добавления первого реверсивного счетчика 5. Для повышения быстродействия и точности фазирования в условиях сильных помех коэффициент частичного усреднения сбросовых сигналов сделан переменным, т. е. коммутатор 11 осуществляет коммутацию сбро совых входов первого и второго тригге ров 14 в 15 с выходами определенных разрядов добавления и вычитания первого реверсивного счетчика 5 в зависимости от ТОГО; на каком из выходов коммутато ра 11 сформирован уровень напряжения логической единицы. Сигнал на определен ном выходе первого дешифратора 7 форми руемся в зависимости от кода числа, заюгасанного во второй реверсивный счетчик 6, т. е. в зависимости от соотношения числа импульсов добавления и вычитания, поступивших с выхода фазового дискриминатора 10 за промежуток времени между двумя импульсами на выходе второго управляемого делителя 4. Сброс второго реверсивного счетчика 6 осуществляется импульсом с выхода второго управляемого делителя 4, задержанным первым элементом задержки 1 на время, приблизительно равное длительности импульса, емкость второго ревернсивного счетчика 6 выбирается достаточной для того, чтобы за время между дву- мя сбросовыми импульсами не происходи ло его переполнение. Сигналы с выходов первого и второго элемента И 17 и 18 поступают на. суммирующий и вычитающий входы блока 20 управления, вследствие чего изменяется коли ество импульсов высокой частоты, подвергаемых делению в первом управляемом делителе 3. И таким образо осуществляется подстройка фазы и час- тоты следования тактовых импульсов на выходе устройства. Шаг подстройки (дискретизации) часто ты, т. е. величина смешения тактового импульса на выходе устройства от его основного положения, приходящаяся на один добавленный или исключенный импульс, подвергаемый делению в первом управляемом делителе 3, устанавливается в зависимости от того, на каком из выходов второго дешифратора 8 имеется ур вень напряжения логической единицы. Уровень напряжения логической единицы на определенном выходе второго дешифра тора 8 устанавливается в зависимости от показаний интегратора 16, на вход которого с выхода формирователя 12 переднего импульса поступают импульсы, соответствующие моменту перехода группы принимаемых элементов сообщения из состояния логического нуля в состояние логической единицы. Ввод показаний интегратора 16 во второй и третий дешифраторы 8 и 9 производится через промежуток времени, равный перио ду следования импульсов на выходе делителя 13 и определяющий число элементов принимаемого сообщения, анализ которог характеризует среднюю частоту чередоваКИЯ единичных и нулевых посылок в принимаемом сообщении, т, е. их статичеокую характеристику. Емкость интегратора 16 выбирается достаточной для того, чтобы за время между двумя сбросовыми импульсами, поступающими с выхода делителя 13 через второй элемент задержки 2 не происходило его переполнение. Чем чаще чередуются единичные и нулевые зл деить} нпи их группы в составе принимаемых сообщений, тем выше показания интегратора 16 и тем меньше шаг подстройки частоты первого управляемого делителя 3, устанавливаемый вторым дешифратором 8. Аналогичным образом интегратор 16 управляет третьим деши(}фатором 9, код сигнала на вьисоде которого поступает на группу установочных входов управляемого делителя 4, изменяя коэффициент его деления, а следовательно и время, в продолжении которого вторым реверстюным счетчиком 6 определяются соотношения числа импульсов добавления и вычитания, формируемых фазовым дискриминатором 1О, Таким образом данное устройство обеспечивает повышение точности и быстродействия фазирования за счет введения автоматического изменения шага дискретизации подстройки частоты, а также введением блокировки усреднения корректирующих импульсов добавления и автоматическим изменением коэффициента усреднения импульсов сброса блокировочных триггеров. Формула изобретения Устройство тактовой синхронизации, содержащее последовательно соединенные блок управления, первый управляемый де- итель и фазовый дискриминатор, выходы которого подключены к суммирующему и вычитающему входам первого реверси&ного счетчика, а также задающий генератор, интегратор и последовательно соединенные первый триггер и первый элемент И, при этом выход задающего генератора подключен к второму входу nej вого управляемого, делителя, отличающееся тем, что, с целью повышения точности и быстродействия фазирования в него, введены последовательно соединенные второй управляемый делитель, первый элемент задержки, второй реверсивный счетчик, первый дешифратор и коммутатор, а также формирователь переднего

фронта импульса, делитель, второй 9ле мент задержки, иторой и третий аешифраторы и послецовптельно соединенные второй триггер и второй элемент И, к второму Бхоцу которого, а таюке второму входу первого элемента И, вычитающему и суммирующему вхопам второго реверсивного счетчика подключены соответствующие выходы фазового пискриминатора, а выходы первого и второго эле- ментов И подключены соответственно к суммирукглиему и вычитающему входам блока управления, к тактовому входу которого подключен второй выход первого управляемого целителя, к управляющим входам которого подключены выходы второго дешифратора, к входам которого и входам третьего дешифратора подключены выходы интегратора, к входу которого подключен выход формирователя переднег фронта импульса, вход которого объединен с информационным входом фазового дискриминатора, а к сбросовому входу интегратора через второй элемент задержки и к управляющим входам второго и трютьего дешифраторов непосредственно подключен выход делителя, к счетному входу которого и счетному входу второго управляемого делителя подключен первый выход первого управляемого делителя, при этом выходы третьего дещифра- тора подключены к входам установки начальных состояний второго управляемого делителя, выход которого подключен к управляющему входу первого дешифратора а выходы первого реверсивного счетчика подключены к установочным входам первого и второго триггеров, к сбросовым входам которых подключены выходы коммутатора, к вторым входам которого подключены вторые выходы первого реверсивного счетчика.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 25О2О5, кл. Н 03 К 5/00, 1968 (прототип).

Авторы

Даты

1982-02-15—Публикация

1980-05-06—Подача