Х 00

О

OK

Изобретение относится к импульсной технике и может быть использовано в автоматике и измерительной технике.

Цель мзобретеиия - повышение помехоустойчивости за счет статической обработки и анализа нескольких периодов входной частоты.

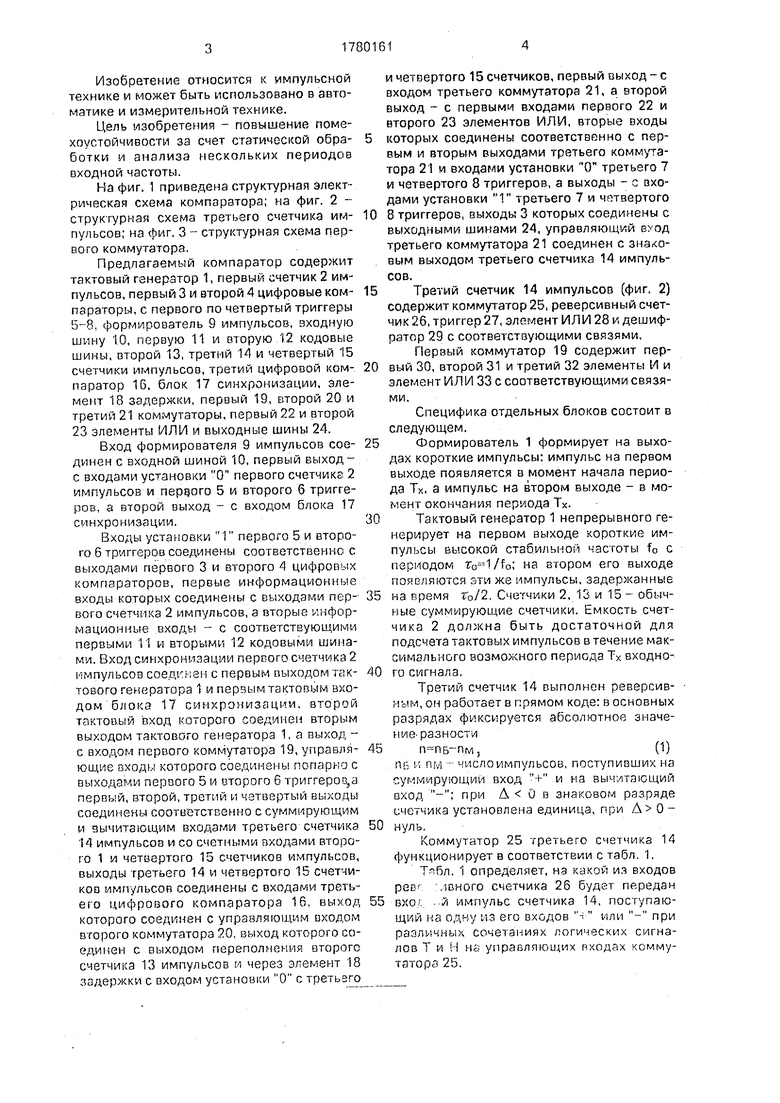

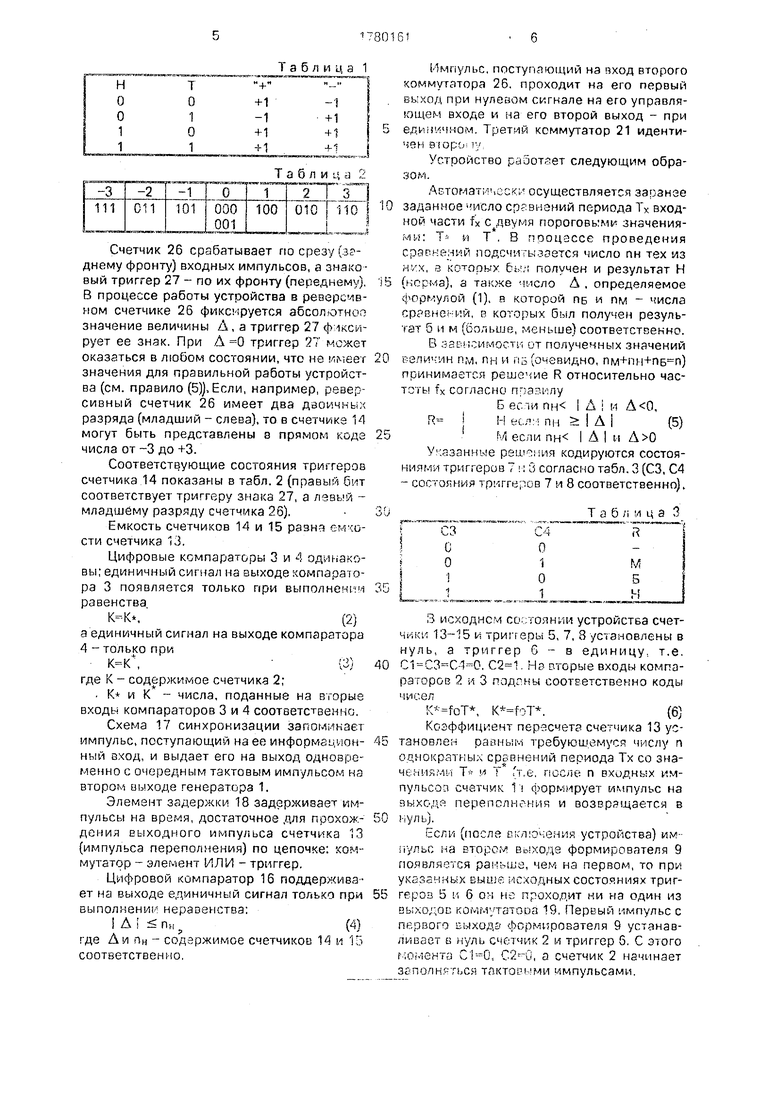

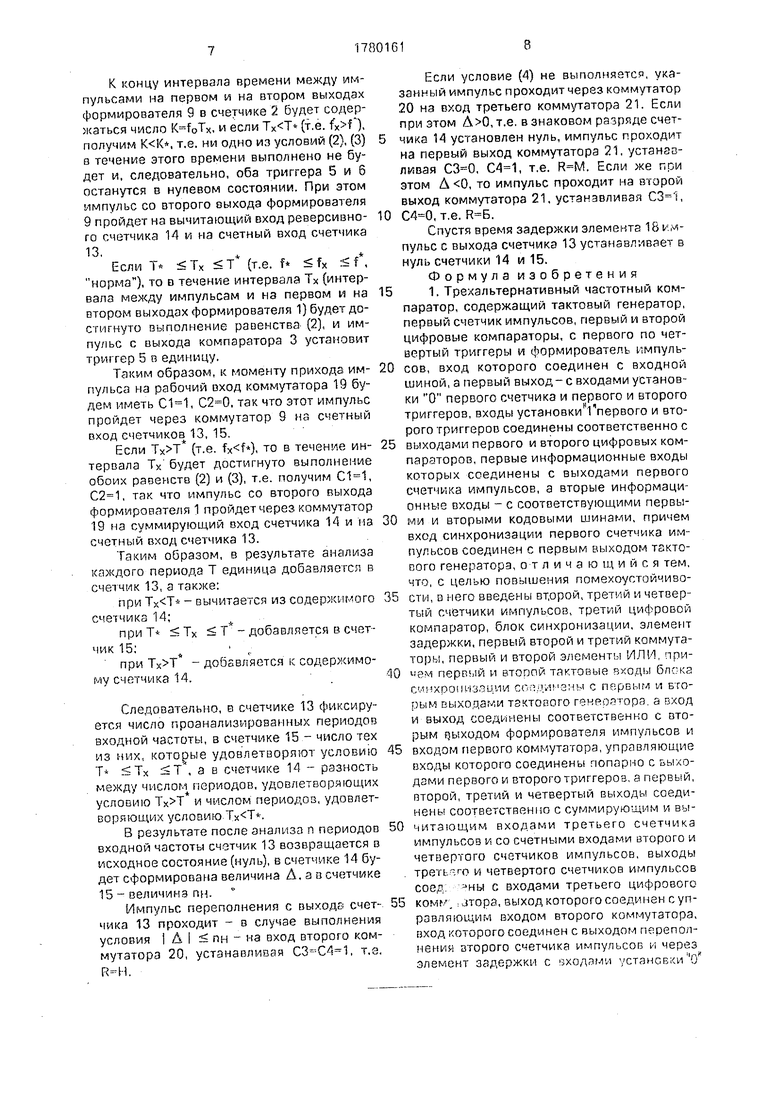

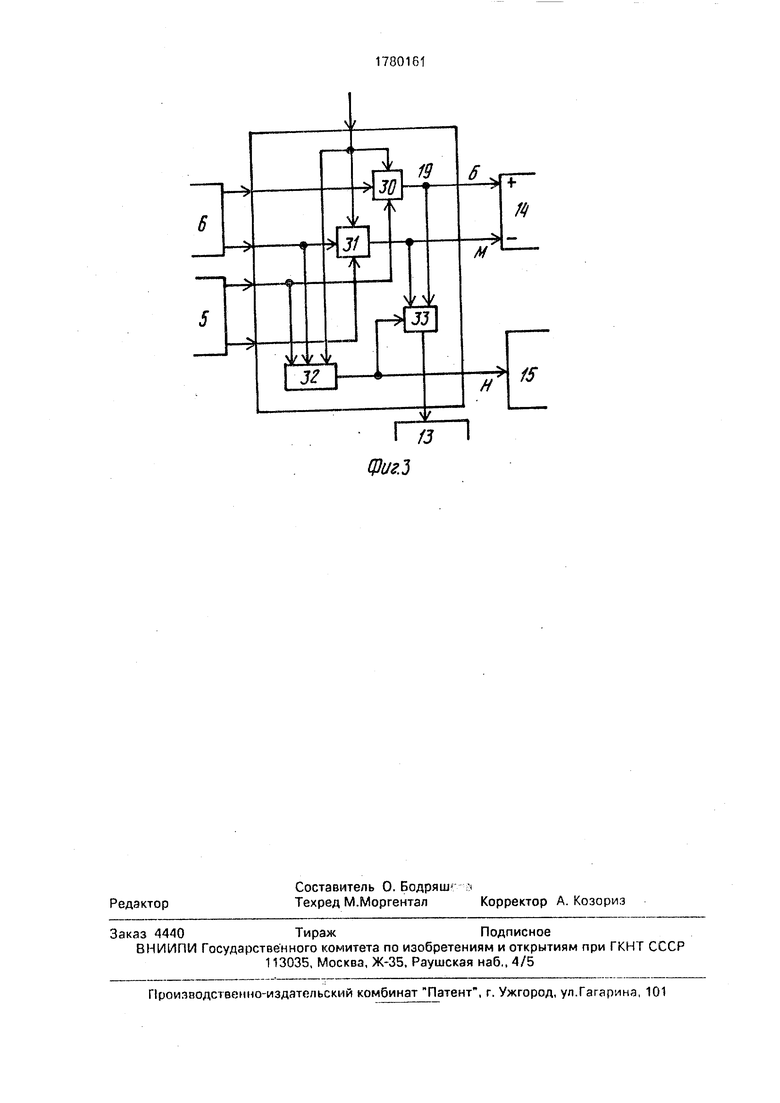

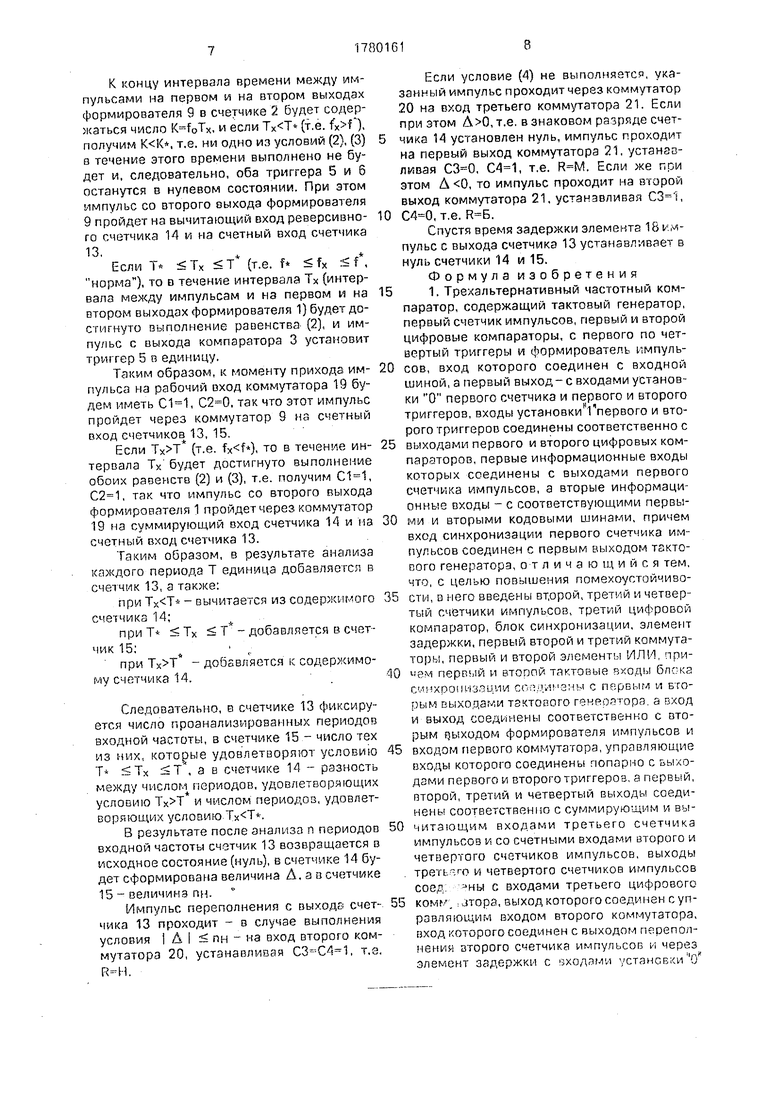

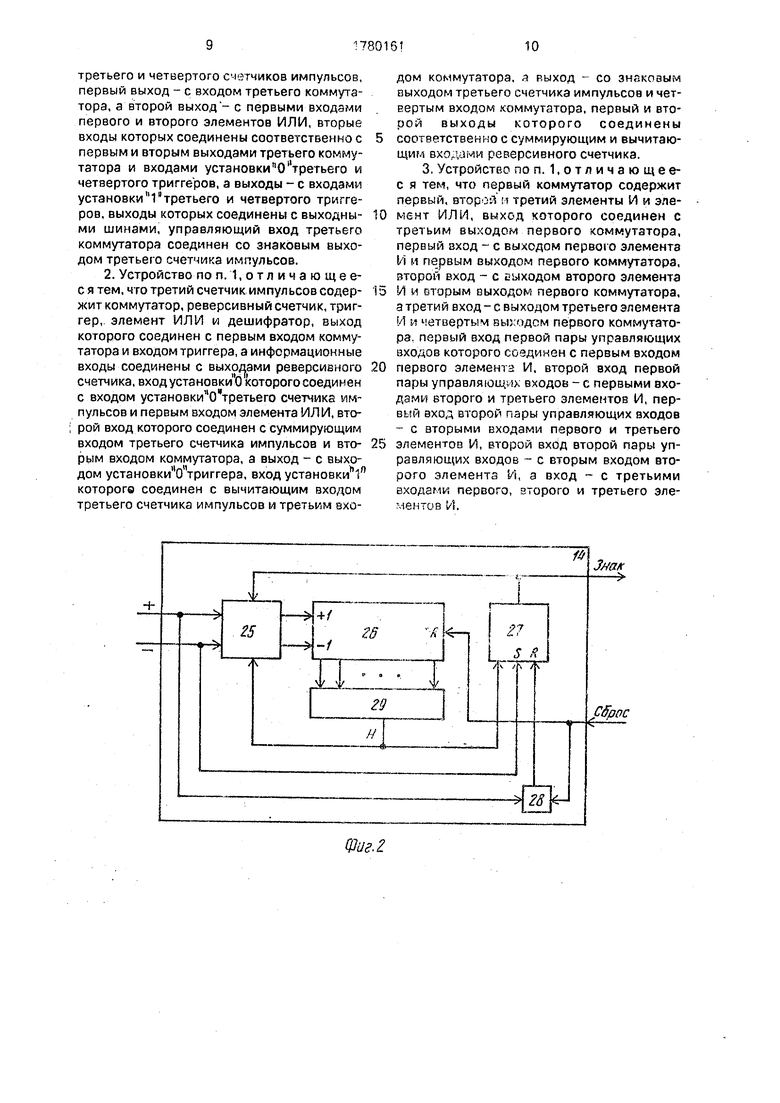

На фиг. 1 приведена структурная электрическая схема компаратора; на фиг, 2 структурная схема третьего счетчика импульсов; на фиг, 3 - структурная схема первого коммутатора.

Предлагаемый компаратор содержит тактовый генератор 1, первый счетчик 2 импульсов, первый 3 и второй 4 цифровые компараторы, с первого по четвертый триггеры 5-8, формирователь 9 импульсов, входную шину 10, первую 11 и вторую,12 кодовые шины, второй 13, третий 14 и четвертый 15 счетчики импульсов, третий цифровой компаратор 16. блок 17 синхронизации, элемент 18 задержки, первый 19, второй 20 и третий 21 коммутаторы, первый 22 и второй 23 элементы ЛЛИ и выходные шины 24.

Вход формирователя 9 импульсов соединен с входной шиной 10, первый выходс входами установки О первого счетчике. 2 импульсов и первого 5 и второго 6 триггеров, а второй выход - с входом блока 17 синхронизации.

Входы установки 1 первого 5 и второго 6 триггеров соединены соответственно с выходами первого 3 и второго 4 цифровых компараторов, первые информационные входы которых соединены с выходами первого счетчика 2 импульсов, а вторые информационные входы - с соответствуюш,ими первыми 11 и вторыми 12 кодовыми шинами. Вход синхронизации первого счетчика 2 импульсов соедккеи с первым выходом тактового генератора 1 и первым тактовым входом блока 17 синхронизации, второй тактов.ый вход которого соединен вторым выходом тактового генератора 1, а выход с входом первого коммутатора 19, управляющие входы которого соединены попарно с выходами первого 5 и второго 6 триггеров,,а первый, второй, третий и четвертый выходы соединены соответственно с суммирующим и зычитающим входами третьего счетчика 14 импульсов и со счетными входами второго 1 м четвертого 15 счетчиков импульсов, выходы третьего 14 и четвертого 15 счетчиков импульсов соединены с входами третьего цифрового компаратора 16, выход которого соединен с управляющим входом второго коммутатора 20, выход которого соединен с выходом переполнения второго счетчика 13 импульсов м через элемент 18 задержки с входом установки О с третьего

и четвертого 15 счетчиков, первый выход с входом третьего коммутатора 21, а второй выход - с первыми входами первого 22 и второго 23 элементов ИЛИ, вторые входы которых соединены соответственно с первым и вторым выходами третьего коммутатора 21 и входами установки О третьего 7 и четвертого 8 триггеров, а выходы - с ЕЗХОдами установки 1 третьего 7 и четвертого 8 триггеров, выходы 3 которых соединены с выходными шинами 24, управляющий вход третьего коммутатора 21 соединен с зналоаым выходом третьего счетчика 14 импульсов.

Третий счетчик 14 импульсов {фиг. 2) содержит коммутатор 25, реверсивный счетчик 26, триггер 27, элемент ИЛИ 28 и дешифратор 29 с соответствующими связями.

Первый коммутатор 19 содержит первый 30, второй 31 и третий 32 элементы И и элемент ИЛ 14 33 с соответствующими связями.

Специфика отдельных блоков состоит в следующем.

Формирователь 1 формирует на выходах короткие импульсы; импульс на первом выходе появляется в момент начала периода Тх, а импульс на втором выходе - в момент окончания периода Тх.

Тактовый генератор 1 непрерывного генерирует на первом выходе короткие импульсы высокой стабильной частоты fo с периодом To 1/fo; на втором его выходе появляются эти же импульсы, задержанные на время toll. Счетчики 2, 13 и 15 - обычные суммирующие счетчики. Емкость счетчика 2 должна быть достаточной для подсчета тактовых импульсов в течение максимального возможного периода Тх входного сигнала.

Третий счетчик 14 выполнен реверсивным, он работает в прямом коде: в основных разрядах фиксируется абсолютное значение разности

П-ПБ-ПМ,(1)

ПБ и пм число импульсов, поступивших на суммирующий вход + и на вычитающий вход при Д О 13 знаковом разряде счетчика установлена единица, при А О нуль.

Коммутатор 25 третьего счетчика 14 функционирует в соответствии с табл. 1.

. 1 определяет, нз KaKovi из входов рев. мвного счетчика 26 будет передан вхо/; ..и импульс счетчика 14, поступающий на одну из его входов ч или - при различных сочетаниях логических сигналов Т и И на управляющих входах коммутатора 25.

Таблица 1

Счетчик 26 срабатывает по срезу(з днему фронту ) входных импульсов, а знаковый триггер 27 - по их фронту (переднему), В процессе работы устройства в реверсивном счетчике 26 фикс Фуется абсолютноезначение величины А, а триггер 27 фмксирует ее знак. При А 0 триггер 27 может оказаться в любом состоянии, что не ммеет значения для правильной работы устройства (см. правило (5)), Если, например, реверсивный счетчик 26 имеет два даоичных разряда (младший - слева), то в счетчике 14 могут быть представлены а прямом коде числа от -3 до -t-3.

Соответствующие состояния триггеров счетчика 14 показаны в табл. 2 (правый бит соответствует триггеру знака 27, а левый младшему разряду счетчика 26).

Емкость счетчиков 14 и 15 равна емкости счетчика 13.

Цифровые компараторы 3 и 4 од1-и;аковы; единичный сигнал на выходе компаратора 3 появляется только при выполнен равенства

.(2)

а единичный сигнал на выходе компаратора

4 - только при

.

1ч-1ч ,k,

где К - содержимое счетчика 2;

. К и К - числа, поданные на вторые входы компараторов 3 и 4 соответственно.

Схема 17 синхронизации запом лнаег импульс, поступающий на ее информационный вход, и выдает его на выход одновременно с очередным тактовым импульсом на втором выходе генератора 1.

Элемент задержки 18 задерживает импульсы на время, достаточное .для прохождения выходного импульса счетчика 13 (импульса переполнения) по цепочке: коммутатор - элемент ИЛИ - триггер.

Цифровой компаратор 16 по,вдерживает на выходе единичный сигнал только npii выполнении неравенства:

А ; Пи (4)

где Аи Пн - содержимое счетчиков 1 и 15 соответственно,

Импульс, поступающий на вход второго коммутатора 26. проходит на его первый выход при нулевом сигнале на его управляющем входе и на его второй выход - при единичном. Третий коммутатор 21 идентичен BiOpO; Г-/,

Устройство раЭотает следующим образом.

АЕтомати.ески осуществляется заданное число сравнений периода Тх входной части fx с двумя пороговь:м1л значениями: T;- и Т . В процассе проведения срагнений подсчмтыззется число пн тех мз HVx, гз 1 оторых был получен и результат Н (норма), а таюке --п-юло А , определяемое формулой (1). а которой ПБ и пм - числа сравнений, в которых был получен результат 5 и м (больше, меньше) соответственно.

В .зависимости от полученных значений величин пм, пн и пз (очевидно, ПМ+ПН+ПБ П) принимается решение R относительно частоты fx согласно ппазклу

Б еспи пн I А I и ,

R I Н еслм пн I А i(5)

М если пн I А I и

У;;азанные решо1 ия кодируются состояниями триггеров 7 : 3 согласно табл. 3 (СЗ, С4 - состояния тр;5ггеров 7 и 8 соответственно).

О 1 О

м

Б

1

3 исходном со:.;тоянии устройства счетчики 13-15 и триггеры 5, 7, 3 установлены в нуль, а триггер б - в единицу, т.е. . . Нэ вторые входы компараторов 2 i-1 3 поданы соответственно коды чисел

, .(6)

Коэффициент пересчета счетчика 13 установлен равным требуюшемуся числу п однократных сравнений периода Тх со значениями Т .W Т т,е, riccjie п входных импульсоп счетчик 1 i сформирует импульс на аыходя переполне-ния и возвращается в нуль).

Если (гюсле включения устройства) импульс на второ.м выходе формирователя 9 появляется раньше, чем на первом, то при указанных выше исходных состояниях триггеров 5 и б он не проходит ни на один из зыходос коммутатооа 19, Первый импульс с первого Еыхода форм1фователя 9 устанавливает в нуль счетчик 2 м триггер 6. С этого гломента , , а счетчик 2 начинает заполняться такторыми импульсами.

К концу интервала времени между импульсами на первом и на втором выходах формирователя 9 в счетчике 2 будет содержаться число K --foTx, и если (т.е. ), получим . т.е. ни одно из условий (2), (3) в течение этого времени выполнено не будет и, следовательно, оба триггера 5 и 6 останутся в нупевом состоянии. При этом импульс со второго выхода формирователя 9 пройдет на вычитающий вход реверсивного счетчика 14 и на счетный вход счетчика

Если Т Тх Т (т.е. f fx f норма), то в течение интервала Тх (интервала между импульсам и на первом и на втором выходах формирователя 1) будет достигнуто выполнение равенства- (2), и импульс с выхода компаратора 3 установит триггер 5 п единицу.

Таким образом, к моменту прихода импульса на рабочий вход коммутатора 19 будем иметь , , так что этот импульс пройдет через коммутатор 9 на счетный вход счетчиков 13, 15.

Если (т.е. ), то в течение интервала Тх будет достигнуто выполнение обоих равенств (2) и (3), т.е. получим , , так что импульс со второго выхода формирователя 1 пройдет через коммутатор 19 на суммирующий вход счетчика 14 и isa счетный вход счетчика 13.

Таким образом, в результате анализа каждого периода Т единица добавляется в счетчик 13, а также:

при - вычитается из содержимого счетчика 14;

при Т Тх Т - добавляется в счетчик 15:

при - добавляется к содержимому счетчика 14.

Следовательно, в счетчике 13 фиксируется число проанализированных периодоп входной частоты, в счетчике 15 - число тех из них, которые удовлетворяют условию Т Тх Т , а в счетчике 14 -- разность между числом периодов, удовлетворяющих условию и числом периодов, удовлетворяющих условию .

В результате после анализа п периодов входной частоты счетчик 13 возвращается в исходное состояние (нуль), в счетчике 14 будет сформирована величина А, а в счетчике 15 - величина пц.

Импульс переполнения с выходв счетчика 13 проходит - в случае выполнения условия I А I пн - на вход второго коммутатора 20, устанавливая , т.е. .

Если условие (4) не выполняатср, указанный импульс проходит через коммутатор 20 на вход третьего коммутатора 21. Если при этом , т.е. в знаковом разряде счетчика 14 установлен нуль, импульс проходит на первый выход коммутатора 21, устанавливая , , т.е. . Если же при этом А 0, то импульс проходит на второй выход коммутатора 21. устанавливая ,

, т.е. .

Спустя время задержки элемента tiv.l пульс с выхода счетчика 13 устанавливает в нуль счетчики 14 и 15.

Формула изобретения

1. Трехальтернативиый частотный компаратор, содержащий тактовый генератор, первый счетчик импульсов, первый и второй цифровые компараторы, с первого по четвертый триггеры и формирователь импульсов, вход которого соединен с входной шиной, а первый выход- с входами установки О первого счетчика и первого и второго триггеров, входы установки Тпервого и второго триггеров соединены соответственно с

выходами первого и второго цифровых компараторов, первые информационные входы которых соединены с выходами первого счетчика импульсов, а вторые информационные входы - с соответствующими первыми и вторыми кодовыми шинами, причем вход синхронизации первого счетчика импульсов соединен с первым выходом тактоRoro генератора, отличаю щ и и с я тем. что, с целью повышения помехоустойчивости, в него введены вт.орой, третий и четвертый сч1этчики импульсов, третий цифровой компаратор, блок синхронизации, элемент задержки, первый второй и третий коммутаторы, первый и второй элементы ИЛИ, при«ем первый и втопой тактовые входы блока С1лнхрО 1изЗоЛ1 Л со;-;ди эны с первым и вторым выходами тзктойого генератора, а вход и выход соединены соответственно с вторым выходом формирователя импульсов и

входом первого коммутатора, управляющие вхо,аы которого соединены попарно с выходами первого и второго триггеров, а первьт, второй, третий и четвертый выходы соединены соответственно с суммирующим и вычитающим входами третьего счетчика

импульсов и со счетными входами второго и

четвертого счетчиков импульсов, выходы

третьего и четвертого счетчиков импульсов

соед: ны с входами третьего цифрового

KOMh..; атора, выход которого соединен с упрзвляющим входом второго коммутатора, вход которого соединен с выходом переполнений второго счетчика импульсов и через злемент задержки с входами устансвки,}

третьего и четвертого счетчиков импульсов, первый выход - с входом третьего коммутатора, а второй выход- с первыми входами первого и второго элементов ИЛИ. вторые входы которых соединены соответственно с первым и вторым выходами третьего коммутатора и входами установки0 третьего и четвертого триггеров, а выходы - с входами установки третьего и четвертого триггеров, выходы которых соединены с выходными шинами, управляющий вход третьего коммутатора соединен со знаковым выходом третьего счетчика импульсов.

2. Устройство по п. 1,отличающееся тем. что третий счетчик импульсов содержит коммутатор, реверсивный счетчик, триггер., элемент ИЛИ и дешифратор, выход которого соединен с первым входом коммутатора и входом триггера, а информационные входы соединены с выходами реверсивного счетчика. входустановки 0 которого соединен с входом установки 0третьего счетчика VIMпульсов и первым входом элемента ИЛИ. вто; рой вход которого соединен с суммирующим входом третьего счетчика импульсов и вторым входом коммутатора, а выход - с выходом установки о триггера. вход установки 1 которого соединен с вычитающим входом третьего счетчика импульсов и третьим входом коммутатора, а выход - со знаковым выходом третьего счетчика импульсов и четвертым входом коммутатора, первый и второй выходы которого соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика.

3. Устройство поп. 1.отличающеес я тем. что первый коммутатор содержит первый, второй и третий элементы И и элемент ИЛИ. выход которого соединен с третьим выходом первого коммутатора, первый вход - с выходом первого элемента И и первым выходом первого коммутатора, второй вход - с Еыходом второго элемента И и вторым выходом первого коммутатора. а третий вход- с выходом третьего элемента И 1-1 четвертым вы);одсм первого коммутатора, первый вход первой пары управляющих входов которого соединен с первым входом первого элемента И. второй вход первой пары управляющих входов - с первыми входами второго и третьего элементов И. первый вход второй пары управляющих входов - с вторыми входами первого и третьего элементов И. второй вход второй пары управляющих входов с вторым входом второго элемента И. а вход - с третьими входами первого, второго и третьего элементов И.

l/j I

teJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Времяимпульсный компаратор | 1986 |

|

SU1403361A1 |

| Цифровой дифференциальный широтно-импульсный модулятор | 1986 |

|

SU1406759A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Цифровая сейсмическая станция | 1984 |

|

SU1188686A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Устройство измерения времени ограничения тока транзисторными коммутаторами систем зажигания | 1989 |

|

SU1758279A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Устройство для регулирования расхода | 1986 |

|

SU1377832A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

Устройство содержит тактовый генератор 1, первый счетчик 2 импульсов, первый 3 и второй 4 цифровые компараторы, с первого по четвертый триггеры 5-8. формирователь 9 импульсов, входную шину 10. первую 11 и вторую 12 кодовые шины, второй 13. третий 14 и четвертый 15 счетчики импульсов, третий цифровой компаратор 16. блок 17 синхронизации, элемент 18 задержки, первый 19. второй 20 и третий 21 коммутаторы, первый 22 и второй 23 элементы ИЛИ и выходные шины 24. Третий счетчик 14 импульсов содержит коммутатор, реверсивный счетчик, триггер, элемент ИЛИ и дешифратор. Первый коммутатор 19 содержит первый, второй и третий элементы И и элемент ИЛИ. 2 з.п. ф-лы. 3 ил.. 3 табл. Зшо^г^(Яс

| Переключатель диапазонов частоты | 1979 |

|

SU783989A2 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| С | |||

| и др | |||

| Электроизмерительные устройства для диагностики машин и механизмов | |||

| Л.: Энергия, 1979 | |||

| с | |||

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-07—Публикация

1989-09-19—Подача