«

Изобретение относится к автоматике и вычислительной технике и может быть использовано при создании высоконадежных систем для управления технологическими процессами.

Целью изобретения является повышение надежности работы устройства за счет исключения ошибок оператора при эксплуатации устройства путем автоматизации учета временной эксплуатации устройства погрешности.

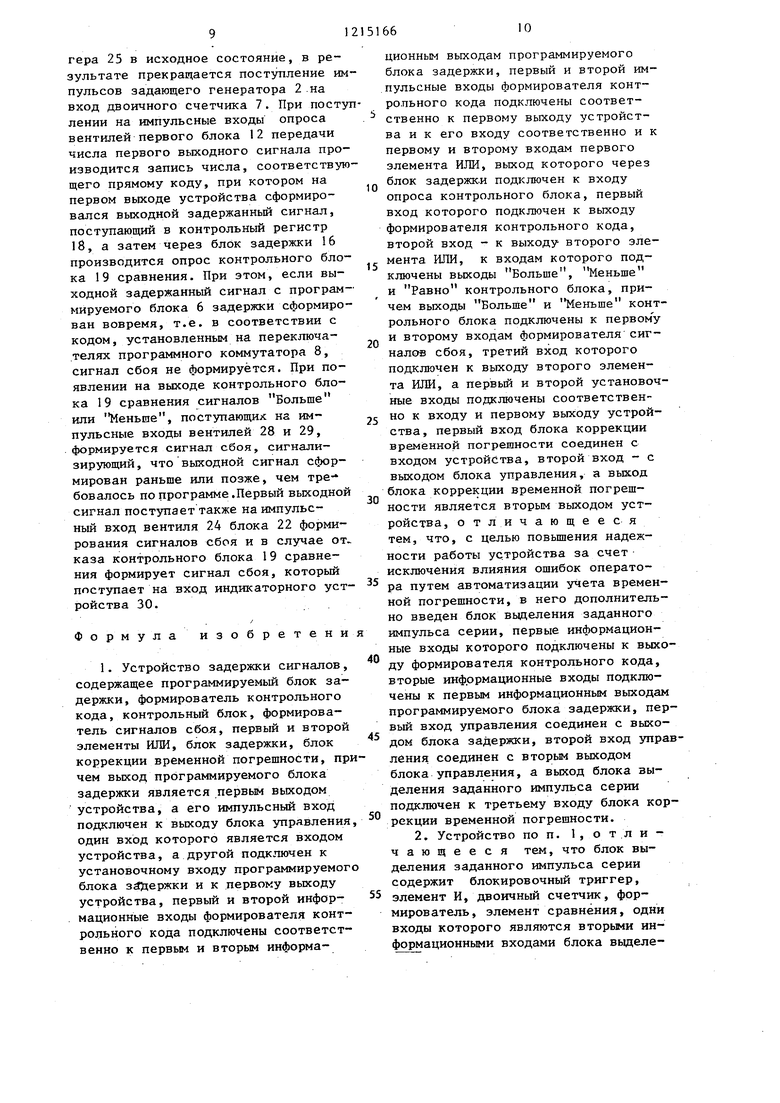

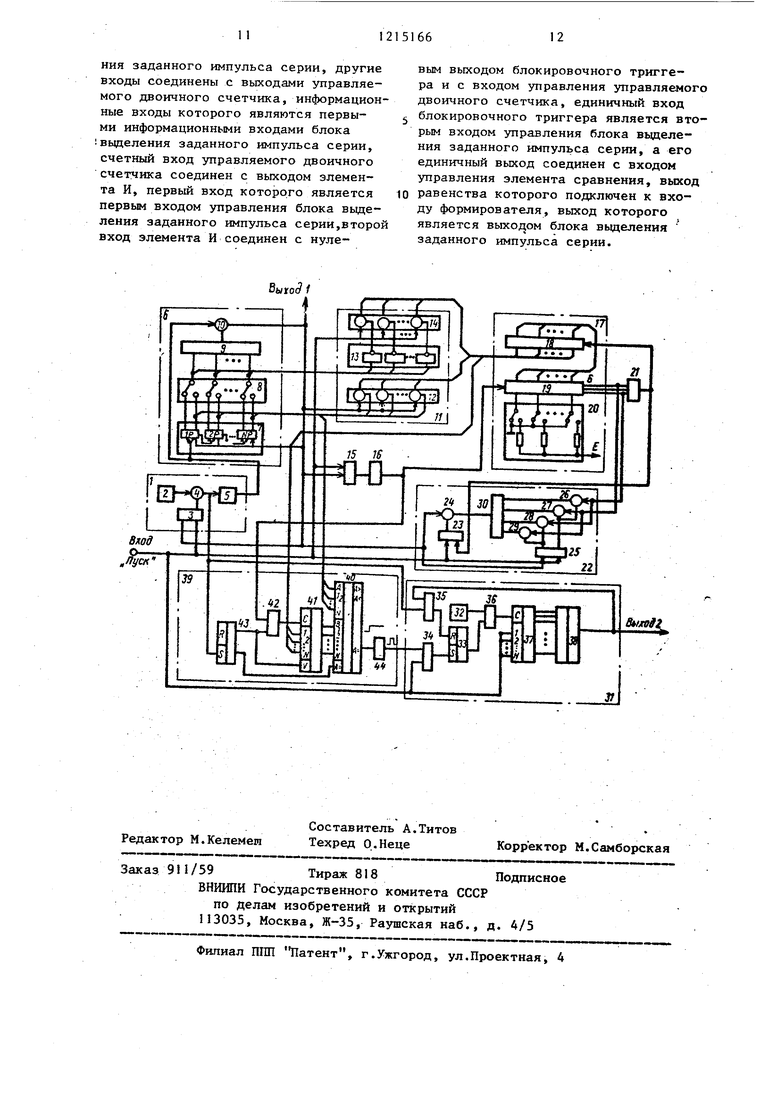

На чертеже представлена схема предпоженного устройства.

Устройство содержит блок 1 управ- ления, в который входит задающий генератор 2, триггер 3 управления, управляемый вентиль 4 и делитель 5 частоты, причем единичный вход триггера 3 управления подключен к вход- ной клемме устройства, а, единичный выход - к входу управления управляемого вентиля 4, импульсный вход которого подключен к выходу задающего генератора 2, а выход соединен с вхо дом делителя 5 частоты.

В состав устройства входит про- граммируемьм блок 6 задержки, содержащий двоичный счетчик 7 на N разрядов, прогр;аммный коммутатор 8,мно- говходовый элемент И 9, входы которого подключены к выходным клеммам программного коммутатора 8, а выход соединен с управляющим входом вентиля 10, импульсный вход которо- го соединен со счетным выходом первого разряда двоичного счетчика 7, а также выходом делителя 5 частоты, выход вентиля 10 соединен с выходом задержанного сигнала программи- руемого блока 6 задержки. Выходы двоичного счетчика 7 являются первым информационным выходом программируемог блока 6 задержки, а выходы программного коммутатора 8 являются вторым информационным выходом. Формирователь iI контрольного кода содержит первый блок 12 передачи числа, блок 13 инвертирования контрольного кода, второй блок 14;передачи числа. Пер- вый и второй импульсные входы формирователя 11 контрольного кода подключены соответственно к выходу задержанного сигнала программируемого блока 6 задержки и первому выходу устройства и к входной клемме, а также к первому и второму входам первого элемента ИЛИ 15 и через блок задерж

5

О

15 20 25

зо 40 5 Q

5

662

ки 16 к контрольному блоку 17, кото-1 рьй содержит контрольный регистр 18, выходные концы которого поразрядно подключены на первые потенциальные входы контрольного блока 19 сравнения. На вторые потенциальные входы i последнего подключены выходные клеммы контрольного коммутатора 20, подключенного к минусу источника постоянного напряжения.

Выходы Больше, Меньше и Равно контрольного блока 19 сравнения подключены к входам второго элемента ИЛИ 21, причем выходы Больше и Меньше подключены также соответственно к первому и второму входам формирователя 22 сигналов сбоя, на третий вход которого подключен выход второго элемента ИЛИ 21, соединенный с установочньми входами триггеров контрольного регистра 18. Формирователь 22 сбоя содержит первый триггер 23, управляемьй вентиль 24, второй триггер 25, управляемые вентили 26 - 29, к выходам которых подключено индикаторное устройство 30. К единичному входу первого контрольного триггера 23 подключен выход второго элемента ИЛИ 21, нулевой вход первого контрольного триггера 23 подключен к входной клемме устройства, единичный и нулевой входы второго контрольного триггера 25 подключены к установочным входам формирователя .22 сигналов сбоя, соединенным соот- в,е-тственно с входной и первой выходной клеммами устройства.

Устройство содержит блок 31 коррекции временной погрешности, состоящий из генератора 32 импульсов высокой частоты (частота которого в 1 раз больше частоты задающего генератора 2) , триггера 33 первого и второго элементов ИЛИ 34 и 35, элемента И 36, счетчика 37 и дешифратора 38, причем первый вход первого элемента ИЛИ 34, являющийся первым входом блоки 31 коррекции временной погрешности, подключен к входной клемме устройства, второй вход первого элемента ИЛИ 34, являющийся третьим входом блока 31, подключен к первой выходной клемме устройства, перйый вход второго элемента ИЛИ 35. являющийся вторым входом блока 31 коррекции временной погрешности, подключен к выкоду управляемого вентиля 4 блока 1 управления, выходы первого и второго элементов ИЛИ 34 и 35 подключены соответственно к единичному и нулевому входам следящего триггера 33, единичный выход которого подключен к од- 5 ному входу элемента И 36, на другой вход которого подключен генератор 32 импульсов ВЫС9КОЙ частоты, выход элемента И 36 подключен на счетный вход счетчика 37, на установочный вход 0 которого подключен вход первого элемента ИЛИ 34, выходы счетчика 37 под. ключены к дешифратору 38, выход которого подключен к второму входу второго элемента ШШ 35 и является выхо- 5 дом блока 31 коррекции временной погрешности и вторым выходом устройст-. ва.

Емкость счетчика 38 выбрана несколько большей максимального числа 20 импульсов генератора 32 импульсов высокой частоты, поступающих на его счетный вход за период выбранной частоты задающего генератора 2.

Устройство содержит также блок 39 25 вьщеления заданного импульса серии, содержащий элемент 40 сравнения, число входов сравнения которого равно числу разрядов двоичного счетчика 7 программируемого блока 6 задерж- 30 ки, управляемый двоичный счетчик 41, работающий в режиме вычитания и с возможностью записи модуля при разрешающем потенциале на входе управления, причем число разрядов этого jj счетчика равно числу разрядов двоичного счетчика 7, элемент И 42, блокировочный триггер 43 и формирователь 44, предназначенный для формирования короткого положительного 0 импульса, причем одни входы А элемента 40 сравнения подключен к первым информационным выходам программируемого блока 6 задержки и являются вторыми информационными входами блока 39 вьоделения заданного импульса ерии, а другие входы В элемента 40 равнения соединены с выходами упавляемого двоичного счетчика 41, нформационные входы которого под- слючены к выходу формирователя 11 контрольного кода и являются первыми информационными входами блока 39 выделения заданного импульса серии, счетный вход управляемого дво- ично.го счетчика 41 соединен с выхо- 55 дом элемента И 42, первый вход которого подключен к выходу блока 16 задержки и является первым входом уп-

45

50

5

0

5 0 j 0 5

5

0

равления блока 39 выделения заданного импульса серии, второй вход элемента И 42 соединен с нулевым выходом блокировочного триггера 43 и входом управления управляемого двоичного счетчика 41, единичный вход упомянутого триггера 43 соединен с, выходом управляемого вентиля 4 блока I управления и является вторым входом управления блока 39 выделения заданного импульса серии, еди- ничньш выход блокировочного триггера 43 соединен с входом управления схемы 40 сравнения, выход равенства которой через формирователь 44 соединен с вторым входом первого элемента ИЛИ 34, являющимся третьим входом блока 31 контроля временной погрешности, при этом выход формирователя 44 является выходом блока 39 вьщеления заданного импульса серии.

Устройство работает следующим образом.

Перед началом работы производится установка исходного состояния триггера 3 управление, разрядов двоичного счетчика 7, контрольного регистра 18, первого и второго контрольных триггеров 23 и 25, следящего триггера 33, счетчиков 37, 41 и триггера 43 блокировки (цепь установки О на чертеже не показана).

Сигнала равенства элемента 40 сравнения на единичный вход следящего триггера 33 не поступает ввиду формирования на управляющем входе элемента 40 сравнения запрещающего потенциала с единичного плеча триггера 43 блокировки. На переключателях программного коммутатора 8 и контрольного коммутатора 20 проводится набор кодовой комбинации для получения задержки необходимой длительности.

По сигналу Пуск, поступающему на вход управления устройства, производится установка триггера 3 управления в единичное состояние, в результате на вход управления-вентиля 4 подается разрешающий потенциал низкого уровня.

Для устранения временного рассогласования между сигналом Пуск и первым импульсом серии задающего генератора 2, с приходом которого на вход делителя 5 частоты начинается отсчет истинного времени задержки по установленному коду, сигнал Пуск поступает Также на первый вход блока 31 коррекции временной погрешности, где производится обнуление счетчика 37 и через первый элемент ИЛИ 34 производится установка триггера 33 в единичное состояние, в результате с генератора 32 импульсов высокой частоты через элемент И 36 начинают поступать импульсы на счетньй вход счетчика 37. С приходом первого импульса с задающего генератора 2 на вход делителя 5 частоты на второй вход блока 31 коррекции временной погрешности работы счетчика прекращается, так как этим сигналом через элемент ИЛИ 35 производится установка триггера 33 в исходное положение. Таким образом, временной интервал А между сигналом Пуск и первым импульсом с задающего генера тора 2 в каждом конкретном случае фиксируется путем включения счетчика 37, который по сигналу Пуск отрабатывает часть периода Т задающего генератора 2.

Сигналом Пуск производится установка в исходное состояние первого контрольного триггера 23, второго контрольного триггера 25 - в единичное состояние, этда же сигналом производится опрос второго блока 14 передачи числа, в результате контрольная кодовая комбинация, соответствующая выбранной временной задержке, подается на входы контрольного регистра 18 и далее на первые потенциа. тьные входы контрольного блока 19 сравнения. Одновременно эта же контрольная кодовая комбинация подается на информационные входы управляемого двоичного счетчика 41 блока 39 выделения заданного импульса серии. Производится запись контрольного модуля, так как триггер 43 блокировки находится в исходном состоянии и с его нулевого выхода поступает разрешающий потенциал на вход управления управляемого двоичного счетчика 41, а также на второй вход элемента И А2, что разрешает прохождение импульса на счетный вход управляемого двоичного счетчика 41.

Задержанный сигнал Пуск с выхода блока 16 задержки поступает на первый вход элемента И 42 блока 39 вьзделения заданного импульса серии и с его выхода - на счетный вход управляемого двоичного счетчика 41,

1

0

5

0

5

0.

5

0

5

0

5

в результате из модуля, записанного в счетчик в соответствии с установленной кодовой комбинацией п по формированию заданной временной задержки, производится вычитание единицы. С приходом первого импульса с задающего генератора 2 на вход делителя 5 частоты на второй вход управления блока 39 выделения заданного импульса серии и даже на единичный вход триггера 43 блокировки происходит переключение этого триггера, в результате на втором входе элемента И 42 и входе управления управляемого двоичного счетчика 41 устанавливается запрещающий потенциал, а на входе управления элемента 40 сравнения - разрешающий потенциал, который разрешает формирование выходного сигнала при равенстве двоичных чисел А и В на входах этого элемента, при этом на все время работы устройства .(до установления новой кодовой комбинации на переключателях коммутатора и установки О) в управляемом двоичном счетчике 41 хранится двоичное число h-1, которое присутствует на входах В элемента 40 сравнения блока 39 вы- деления заданного импульса серии. Прсле установления потенциалов сигналом с выхода блока 16 задержки производится опрос контрольного блока 19 сравнения и в зависимости от результатов сравнения контрольного кода с контрольного регистра 18 с кодом задержки, установленным на коммутаторе 20, формируется один из трех возможных сигналов на выходе контрольного блока 19 сравнения, а именно Больше, Равно, Меньше, причем по сигналам Больше или Меньше, поступающим на импульсные входы вентилей 27 и 26, производится контроль исправности контрольного коммутатора 20, программного коммутатора 8 и двоичного счетчика 7. Любой из выходных сигналов контрольного блока 19 сравнения с выхода элемента ИЛИ 21 переключает первый контрольный триггер 23, который при отсутствии сигнала с выхода контрольного блока 19 сравнения сохраняет свое исходное состояние, сигналом с выхода элемента ИЛИ 21 производится также установка исходного состояния разрядов контрольного регистра 18.

С приходом входного сигнала двоичный счетчик 7 начинает счет и при достижении в нем кода на единицу мен , чем код, установленный на переключателях программного коммутатора 8, на выходе элемента 40 сравнения блока 39 выделения заданного импульса серии формируется сигнал равенства (широкий положительный импульс, длительность которого равняется И, который формирователем 44 преобразуется в узкий положительный импульс длительностью I мкс, что обеспечивает нормальную работу следящего триггера 33 блока 31 коррекции временной погрешности. При кодовой комбинации И 1 с приходом первого импульса, задающего генератора 2 с входа управляемого вентиля 4 на нулевой вход бледящего триггера 33 переключение триггера не происходит, так как на единичном входе этого триггера под воздействием сигнала равенства элемента 40 сравнения присутствует сформированный импульс с выхода формирователя 44 несколько большей длительности 1 мкс. Наличие формирователя 44 обеспечивает также установку следящего триггера 33 после окончания второго цикла работы блока 31 коррекции временной погрешности.

Сигнал с выхода формирователя 44 поступает на третий вход блока 31 коррекции временной погрешности и через первый элемент ИЛИ 34 производит второе за цикл работы устройства задержки сигналов переключение триггера 33 в единичное состояние, в результате через элемент И 36 разрешается поступление импульсов с генератора 32 импульсов высокой частоты на счетньй вход счетчика 37, который продолжает работать до тех пор пока на его выходах не установится двоичная кодовая комбинация, которая соответствует числу импульсов генератора 32 импульсов высокой частоты за период между импульсами задающего генератора 2, после чего на выходе дешифратора 38 формируется сигнал, по которому через второй элемент ИЛИ 35 производится установка триггера 33 в вьжодное положение в результате прекращается поступление импульсов с генератора 32 импульсов высокой частоты на счетный вход счетчика 37.

Сигнал с выхода дешифратора 38, поступающий на выход блока 31 коррекции временной погрешности,является вторым ( точным) выходом устройства задержки сигналов, причем время задержки на этом выходе равно

- Bbu-i

.А + Т (п-1) + (Т-Л) пТ,

0

5

0

5

0

5

0

5

0

где Д - временная погрешно.сть ,обусловленная рассогласованием между пусковым импульсом и первым импульсом задающего генератора (первый цикл работы блока коррекции временной погрешности); Т - период серии импульсов

с выхода блока управленияj

п - требуемая кодовая комбинация для установки времени задержки;

Т(п-1) - время до формирования выходного импульса с блока выделения заданного импульса серии; (Т-Д) - второй цикл работы блока

коррекции временной погрешности

Таким образом, при установке реальной кодовой комбинации п на переключателях коммутатор за счет выделения (п-1)-го импульса серии блоком 39 выделения заданного импульса серии, который используется для вторичного за цикл работы устройства включения блока 31 коррекции временной погрешности, на втором (точном) выходе устройства формируется сигнал с ликвидацией погрешности Д , который равен установленному времени на задержку сигнала, т.е.

л.

бых 7

При достижении в счетчике 7 кода, равного установленному на переключателях программного коммутатора 8, на выходе элемента И 9 формируется низкий потенциал разрешающего уровня, который поступает на управляющий вход вентиля 10. На выходе вентиля 10 формируется сигнал, который подается на первую -выходную клемму и является первьм выходньм сигналом устройства, причем величина задержки.на этом выходе равна

Г, + Д

быт

По этому сигналу производится установка второго контрольного триггера 25 в исходное состояние, в результате прекращается поступление импульсов задающего генератора 2.на вход двоичного счетчика 7. При посту пении на импульсные входы опроса вентилей первого блока 12 передачи числа первого выходного сигнала производится запись числа, соответствующего прямому коду, при котором на первом выходе устройства сформировался выходной задержанный сигнал, поступающий в контрольный регистр 18, а затем через блок задержки 16 производится опрос контрольного блока 19 сравнения. При этом, если выходной задержанный сигнал с программируемого блока 6 задержки сформирован вовремя, т.е. в соответствии с кодом, установленным на переключателях программного коммутатора 8, сигнал сбоя не формируется. При появлении на выходе контрольного блока 19 сравнения сигналов Больше или Меньше, поступающих на импульсные входы вентилей 28 и 29, формируется сигнал сбоя, сигнализирующий, что выходной сигнал сформирован раньше или позже, чем тре- бовалось по программе.Первый выходной сигнал поступает также на импульсный вход вентиля 24 блока 22 формирования сигналов сбоя и в случае от каза контрольного блока 19 сравнения формирует сигнал сбоя, который поступает на вход индикаторного устройства 30.

/

Формула изобретени

1. Устройство задержки сигналов, содержащее программируемый блок задержки, формирователь контрольного кода, контрольный блок, формирователь сигнашов сбоя, первый и второй элементы ИЛИ, блок задержки, блок коррекции временной погрешности, причем выход программируемого блока задержки является первым выходом устройства, а его импульсный вход подключен к выходу блока управления, один вход которого является входом устройства, а другой подключен к установочному входу программируемого блока зг(Держки и к первому выходу устройства, первый и второй информационные входы формирователя контрольного кода подключены соответственно к первым и вторым информа5

10

15

0

5

0

5

0

5

ционным выходам программируемого блока задержки, первый и второй импульсные входы формирователя контрольного кода подключены соответственно к первому выходу устройства и к его входу соответственно и к первому и второму входам первого элемента ИЛИ, выход которого через блок задержк.и подключен к входу опроса контрольного блока, первый вход которого подключен к выходу формирователя контрольного кода, второй вход - к выходу второго элемента ИЛИ, к входам которого подключены выходы Больше, Меньше и Равно контрольного блока, причем выходы Больше и Меньше контрольного блока подключены к первом у и второму входам формирователя сигнале сбоя, третий вход которого подключен к выходу второго элемента ИЛИ, а первый и второй установочные входы подключены соответственно к входу и первому выходу устройства, первый вход блока коррекции временной погрешности соединен с входом устройства, второй вход - с выходом блока управления, а выход блока коррекции временной погрешности является вторым выходом устройства, отличающееся тем, что, с целью повьш1ения надежности работы устройства за счет исключения влияния ошибок оператора путем автоматизации учета временной погрешности, в него дополнительно введен блок вьщеления заданного импульса серии, первые информационные входы которого подключены к выходу формирователя контрольного кода, вторые информационные входы подключены к первым информационным выходам программируемого блока задержки, первый вход управления соединен с выходом блока задержки, второй вход управления соединен с вторым выходом блока управления, а выход блока выделения заданного импульса серии подключен к третьему входу блока коррекции временной погрешности.

2. Устройство по п. 1, о т .л и - чающееся тем, что блок выделения заданного импульса серии содержит блокировочный триггер, элемент И, двоичный счетчик, формирователь, элемент сравнения, одни входы которого являются вторыми информационными входами блока вьщеления заданного импульса серии, другие входы соединены с выходами управляемого двоичного счетчика, информационные входы которого являются первыми информационными входами блока 1вцделения заданного импульса серии, счетный вход управляемого двоичного счетчика соединен с выходом элемента И, первый вход которого является первым входом управления блока выделения заданного импульса серии,второй вход элемента И соединен с нуле0

вым выходом блокировочного триггера и с входом управления управляемого двоичного счетчика, единичный вход блокировочного триггера является вторым входом управления блока вьщеле- ния заданного импульса серии, а его единичный выход соединен с входом управления элемента сравнения, выход равенства которого подключен к входу формирователя, выход которого является выхо; ом блока выделения заданного импульса серии.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки сигналов | 1982 |

|

SU1104655A2 |

| Устройство задержки сигналов | 1982 |

|

SU1015491A1 |

| Устройство задержки сигналов | 1983 |

|

SU1091306A2 |

| Устройство для сбора,обработки и отражения информации | 1972 |

|

SU451997A1 |

| Генератор псевдослучайной последовательности импульсов | 1979 |

|

SU866716A1 |

| Устройство контроля линейных размеров движущихся изделий | 1982 |

|

SU1146550A1 |

| Устройство для моделирования дискретного радиоканала | 1983 |

|

SU1103256A2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2019 |

|

RU2713624C1 |

| Формирователь страниц для голографического запоминающего устройства | 1986 |

|

SU1388948A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться при создании высоконадежных систем для управления технологическими процессами. Цель изобретения - повьшение надеж -. ности работы устройства путем исклк - чения ошибок оператора - достигается автоматизацией учета временной эксплуатации устройства погрешности. Для этого в устройство задержки сигналов дополнительно введен блок выделения заданного импульса серии, содержащий блокировочный триггер, логический элемент И, двоичный счетчик , формирователь и элемент сравнения. Функциональная схема устройства задержки, состав блоков и описание работы приводятся в описании изобретения. I з.п. ф-лы, 1 ил. (Л С :л а 0)

Редактор М.Келенеш

Составитель А.Титов Техред О,Неде

Заказ 911/59 Тираж 818Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Филиал ППП Патент, г.Ужгород, ул.Проектная, 4

Корректор М.Самборская

| Устройство задержки сигналов | 1982 |

|

SU1015491A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство задержки сигналов | 1982 |

|

SU1104655A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-28—Публикация

1984-07-10—Подача