со

00 СХ)

со

4

00

Изобретение относится к вычислительной технике и предназначено для записи объемов информации.

Целью изобретения является повышение надежности формироЕ.ателя за счет увеличения контраста сформированного на управляемом транспаранте изображения, увеличение отношения сигнал/шум, а следоварого подключен к единичному входу триггера 13 и первому входу элемента ИЛИ 14. Второй вход элемента ИЛИ 14 связан с первым выходом пускового узла 15, нулевым входом триггера 13, первым входом элемента ИЛИ 16 и является седьмым выходом блока 7. Выход элемента ИЛИ 14 подключен к нулевому входу триггера 17, единичный вход которого связан с вхотельно, повышение достоверности записы- , ° генератора 18 импульсов и вторым

ваемой на голограмму информации.1° пускового узла 15. Прямой выход

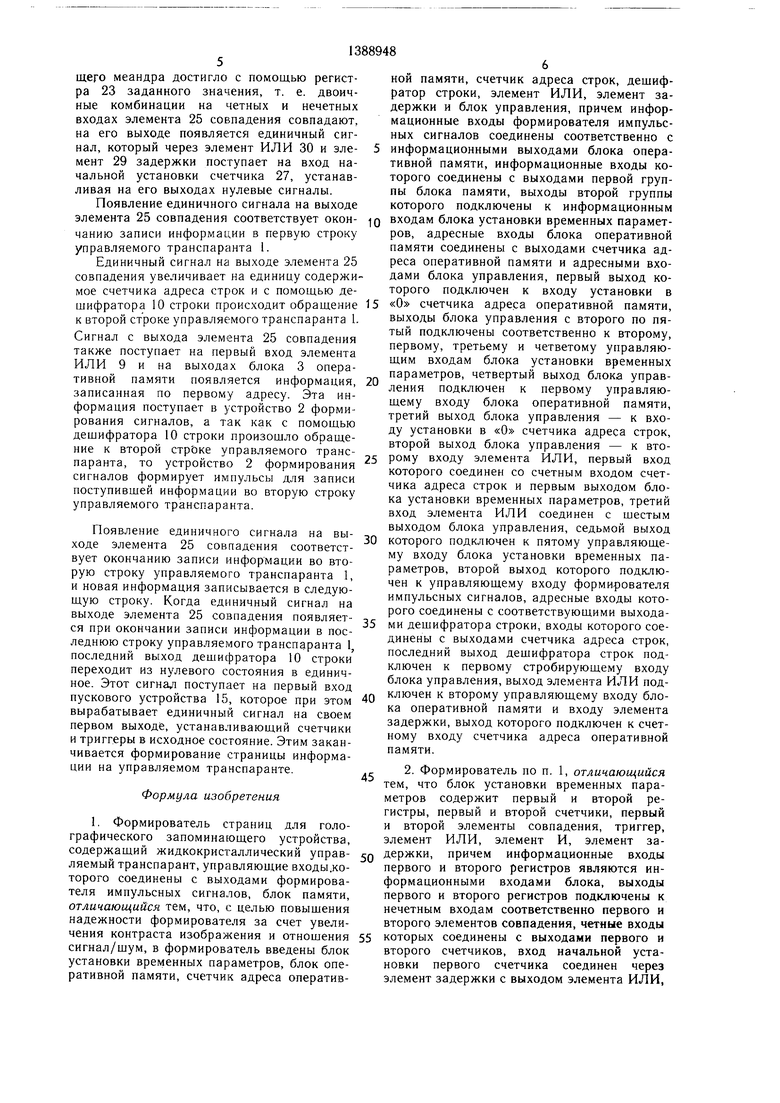

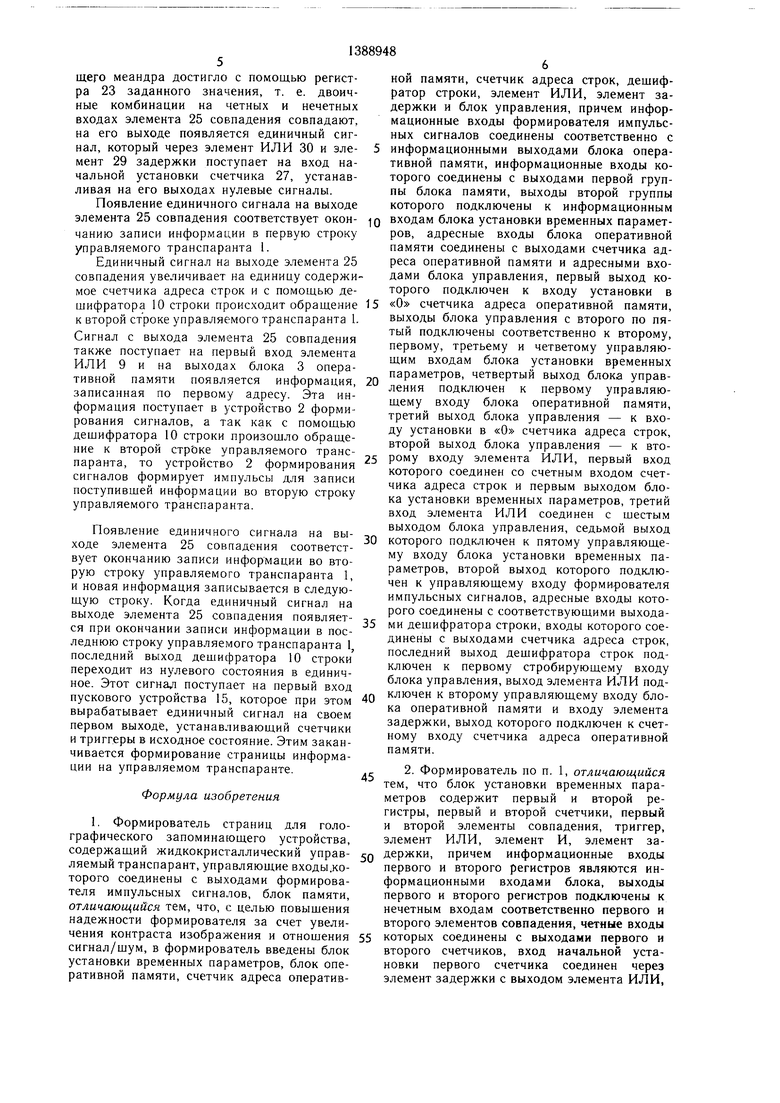

На чертеже Представлена функциональ- 17 подключен к первому входу

ная схема предлагаемого формирователя. элемента И 19, второй вход которого Формирователь страниц для голографического запоминаюш,его устройства (ГЗУ)

связан с выходом генератора 18 и является пятым выходом блока 7. Второй и третий выходы блока 7 являются соответстсвязан с выходом генератора 18 и является пятым выходом блока 7. Второй и третий выходы блока 7 являются соответстгг.а ;с„ТрГЛ, - - од-о.„ар„ор„, 2 „ 2,.

рователю 2 импульсных сигналов, информа- «днов братора 2 связан с вторым

ВХОДОМ элемента ИЛИ 16, выход которого является первым выходом блока 7, и входом элемента 22 задержки, выход которователю 2 импульсных сигналов, инфор ционные входы которого подключены к информационным выходам блока 3 оперативной памяти . Информационные входы бло-,„п ка 3 оперативной памяти подключены к 20 Р подключен к входу одновибратора 20. Вход одновибратора 21 связан с прямым

выходом триггера 13 и является четвертым выходом блока 7, первый вход которого подключен к первому входу пускодами счетчика 6 адреса оперативной памяти и адресными входами блока 7 управления, первый выход которого подключен к входу начальной установки счетчика 6 адреса оперативной памяти, а его третий, второй, четвертый и пятый выходы зо связаны соответственно с первым, вторым, третьим и четвертым входами блока 5 установки временных параметров. К четвертому выходу блока 7 управления подключен первый управляющий вход «Выбор ревыходам блока 4 памяти, к первым восьми выходам которого подключены информационные входы блока 5 установки вреу

менных параметров. Адресные входы блокаic о -ic

3 оперативной памяти связаны с выхо- „ У Второй вход узла 15 яв- с„25 ляется вторым входом блока 7.

гчютпыь а hi Q п гл,(л/ о ппогчоты D urMjf

Информационные входы регистров 23 и 24 являются информационными входами блока 5. Выходы регистров 23 и 24 подключены к нечетным входам элементов 25 и 26 совпадения, четные входы которых связаны с выходами счетчиков 27 и 28, причем вход начальной установки счетчика 27 подключен через элемент 29 задержки к выходу элемента ИЛИ 30, первый вход которого подключен к нулевому вхожима чтение/запись блока 3 оперативной 35 2 Р. 31 и является пятым входом памяти. К третьему выходу блока 7 уп- лока 5. Второй вход элемента ИЛИ 30 равления подключен вход начальной уста- является первым выходом блока 5 и сое- Еовки счетчика 8 адреса строк. Второй « „ элемента 25 совпадения, выход блока 7 связан с вторым входом Счетные вход счетчика 27 связан с выхо- элемента ИЛИ 9, третий вход которого ом элемента 26 совпадения, си нхровходом соединен с шестым выходом блока 7 уп- 0 триггера 31 и входом начальной установки

счетчика 28, счетный вход которого подключен к выходу элемента И 32, первый и второй входы которого являются соответственно третьим и четвертым входами

у 1апиолп орс1У1 ппо1л пп i CLTDCIJUJD, iinijoin DAUA с- nс-, лn

которого связан С седьмым ВЫХОДОМ блока 7, 45 регистров 24 и 23

а второй выход блока 5 подключен к уп- являютс первым и вторым входами бло- равляюшему входу формирователя 2 импульсных сигналов, строчные входы которого через дешифратор 10 строки подключены к выходам счетчика 8 адреса строк, причем последний выход дешифратора 10 50 строки связан с первым входом блок 7 управления, выход элемента ИЛИ 9 подключен к второму управляющему входу блока 3 оперативной памяти и входу элемента 11 задержки, выход которого связан со счетным входом счетчика 6 адреса оператив- 55 тупающий на входы начальной установки ной памяти.счетчика 27 и счетчика 6 адреса oneАдресными входами узла 7 являются вы-ративной памяти. Этот единичный импульс

ходы узла 12 фиксации адреса, выход кото-поступает также на нулевые входы тригравления. Первый вход элемента ИЛИ 9 подключен к счетному входу счетчика 8 адреса строк и первому выходу блока 5 установки временных интервалов, пятый вход

ка 5. Прямой выход триггера 31 является вторым выходом блока 5, инверсный выход и информационный вход триггера 31 объединены между собой.

Формирователь страниц для ГЗУ работает следующим образом.

Сигнал «Пуск поступает через второй вход блока 7 управления на второй вход пускового узла 15, на первом выходе которого появляется единичный импульс, посэлемента И 19, второй вход которого

связан с выходом генератора 18 и является пятым выходом блока 7. Второй и третий выходы блока 7 являются соответст- - од-о.„ар„ор„, 2 „ 2,.

«днов братора 2 связан с вторым

ВХОДОМ элемента ИЛИ 16, выход которого является первым выходом блока 7, и входом элемента 22 задержки, выход кото,„п Р подключен к входу одновибратора 20. Вход одновибратора 21 связан с прямым

являютс первым и вторым входами бло- тупающий на входы начальной установки счетчика 27 и счетчика 6 адреса oneка 5. Прямой выход триггера 31 является вторым выходом блока 5, инверсный выход и информационный вход триггера 31 объединены между собой.

Формирователь страниц для ГЗУ работает следующим образом.

Сигнал «Пуск поступает через второй вход блока 7 управления на второй вход пускового узла 15, на первом выходе которого появляется единичный импульс, посгеров 31, 13 и 17, устанавливая на выходах счетчиков и на прямых выходах триггеров нулевые сигналы, а на инверсных выходах триггеров 31, 13 и 17 - единичные. Затем пусковой узел 15 форми- , рует единичный импульс на своем втором выходе, который запускает генератор 18 импульсов и устанавливает на прямом выходе триггера 17 единичный сигнал. Работа блока 3 оперативной памяти в режиме забатывается одиночный импульс, по которому информация на восьми младших разрядах блока 4 памяти, соответствующая заданной частоте наполнения управляющего сигнала, запоминается в регистре 24. Сигнал с выхода одновибратора 21 обнуляет счетчик 6 адреса оперативной памяти и, пройдя через элемент 22 задержки, поступает на вход одновибратора 20. ГТо единичному импульсу на его выходе инфорписи информации определяется нулевым сиг- 10 мация на восьми младших разрядах блока налом на втором входе блока 3 опера- 4 памяти, соответствующая времени записи

на строку управляющего сигнала, записывается в регистр 23. Единичный импульс

на выходе одновибратора 20 вызывает появра 17 разрешает прохождение импульсов от генератора 18 через элемент И 19 на третий вход элемента ИЛИ 9.

При появлении первого единичного сигтивнои памяти, поступающим с прямого выхода триггера 13. Этот сигнал запрещает прохождение последовательности импульсов от генератора через элемент И 32. Еди- 4 ление информации, записанной по нулевому ничный сигнал на прямом выходе тригге- адресу на выходах блока 3 оперативной памяти. Эта информация поступает в формирователь 2 импульсных сигналов.

Единичный сигнал с выхода элемента ИЛИ 9 поступает через элемент 11 занала на выходе элемента ИЛИ 9, пос- 20 держки на счетный вход счетчика 6 адреса тупающего на второй вход блока 3 one- оперативной памяти, увеличивая на единицу ративной памяти, в него происходит запись его содержимое.

информации по нулевому адресу, так какЕдиничный сигнал на выходе триггера

на выходах счетчика 6 адреса оператив- 13 разрешает прохождение импульсов от ге- ной памяти - нулевые сигналы. Сигнал нератора 18 импульсов на счетный вход

1ЛТТ1Л п - - /J счетчика 28, который считывает количество

импульсов, пришедших от генератора 18 импульсов.

При поразрядном совпадении комбинаций сигналов на выходах регистра 24 и счет- импул ьсу, пришедшему от генератора 18 на зо чика 28 на выходе элемента 26 совпа- третий вход элемента ИЛИ 9, в блок 3 one- дения появляется единичный сигнал, перево- ративной памяти записывается новая инфор- дящий прямой выход триггера 31 в единич- мация и через время, определяемое эле- „де состояние, так как на его инверсном ментом 11 задержки, на адресные входы выходе первоначально был установлен блока 3 оперативной памяти поступит но- сигнал логической единицы. Сигнал с выхо- вый адрес, по которому будет записана 35 да элемента 26 совпадения поступает так- следующая информация..е „а счетный вход счетчика 27, увеличивая его содержимое на единицу, и обнуляет счетчик 28, который считает количество импульсов, пришедших от генератора.

мая на управляемый транспарант, полностью ,, Вновь сигнал на выходе элемента 26 перепишется из блока 4 памяти в блок 3 совпадения появится при совпадении комбинаций на выходах регистра 24 и счетчика 28, и на прямом выходе триггера 31 единичный сигнал сменится нулевым. При появлении следующего единичного сигнала

с выхода элемента ИЛИ 9 также поступает через элемент 11 задержки на счетный вход счетчика 6 адреса оперативной памяти, происходит увеличение содержимого счетчика на единицу. По следующему

После записи информации в блок 3 оперативной памяти по тридцать первому адресу, т. е. страница информации, выводиоперативной памяти, содержимое счетчика 6 адреса оперативной памяти станет равным тридцати двум. Соответствующая этому числу двоичная комбинация на выходах счетчика 6 адреса оперативной памяти посту- 45 ча выходе элемента 26 совпадения на выпает на входы узла 12 фиксации адреса, который формирует на своем выходе единичный сигнал, поступающий на единичный вход триггера 13 и через элемент ИЛИ 14 на нулевой вход триггера 17, переводя

ходе триггера 31 опять появляется единичный сигнал. Таким образом, на прямом выходе триггера 31 образуется меандр, частота которого определяется содержимым регистра 24. Записывая в него различего прямой выход из единичного в нуле- 50 ные двоичные коды, можно менять частоту вое состояние, что запрещает прохождениемеандра, поступающего на управляющий сигналов от генератора 18 через элементвход формирователя 2 сигналов. И 19. Выходной сигнал узла 12 фиксацииСчетчик 27 фиксирует количество полуадреса также устанавливает на прямомпериодов управляющего меандра, получае- выходе триггера 13 единичный сигнал, чтомого на прямом выходе триггера 31. С соответствует переходу блока 3 оперативнойприходом на его вход единичного сигнала

с выхода элемента 26 совпадения счетчик 27 увеличивает свое содержимое на единицу. Когда число полупериодов управляюпамяти из режима записи в режим чтения. По единичному сигналу, поступающему на вход одновибратора 21, им вырабатывается одиночный импульс, по которому информация на восьми младших разрядах блока 4 памяти, соответствующая заданной частоте наполнения управляющего сигнала, запоминается в регистре 24. Сигнал с выхода одновибратора 21 обнуляет счетчик 6 адреса оперативной памяти и, пройдя через элемент 22 задержки, поступает на вход одновибратора 20. ГТо единичному импульсу на его выходе инфор мация на восьми младших разрядах блока 4 памяти, соответствующая времени записи

на строку управляющего сигнала, записывается в регистр 23. Единичный импульс

на выходе одновибратора 20 вызывает появление информации, записанной по нулевому адресу на выходах блока 3 оперативной памяти. Эта информация поступает в формирователь 2 импульсных сигналов.

ча выходе элемента 26 совпадения на выходе триггера 31 опять появляется единичный сигнал. Таким образом, на прямом выходе триггера 31 образуется меандр, частота которого определяется содержимым регистра 24. Записывая в него различные двоичные коды, можно менять частоту меандра, поступающего на управляющий вход формирователя 2 сигналов. Счетчик 27 фиксирует количество полупериодов управляющего меандра, получае- мого на прямом выходе триггера 31. С приходом на его вход единичного сигнала

с выхода элемента 26 совпадения счетчик 27 увеличивает свое содержимое на единицу. Когда число полупериодов управляюной памяти, счетчик адреса строк, дешифратор строки, элемент ИЛИ, элемент задержки и блок управления, причем информационные входы формирователя импульсных сигналов соединены соответственно с информационными выходами блока оперативной памяти, информационные входы которого соединены с выходами первой группы блока памяти, выходы второй группы которого подключены к информационным

щего меандра достигло с помощью регистра 23 заданного значения, т. е. двоичные комбинации на четных и нечетных входах элемента 25 соЕ;падения совпадают, на его выходе появляется единичный сигнал, который через элемент ИЛИ 30 и эле- 5 мент 29 задержки поступает на вход начальной установки счетчика 27, устанавливая на его выходах нулевые сигналы.

Появление единичного сигнала на выходе элемента 25 совпадения соответствует окон- ю входам блока установки временных парамет- чанию записи инфорклации в первую строку ров, адресные входы блока оперативной управляемого транспаранта 1.памяти соединены с выходами счетчика адЕдиничный сигнал на выходе элемента 25 реса оперативной памяти и адресными вхо- совпадения увеличивает на единицу содержи- дами блока управления, первый выход ко- мое счетчика адреса строк и с помощью де- торого подключен к входу установки в шифратора 10 строки происходит обращение 15 «О счетчика адреса оперативной памяти, к второй строке управляемого транспаранта 1. выходы блока управления с второго по пяСигнал с выхода элемента 25 совпадения также поступает на первый вход элемента ИЛИ 9 и на выходах блока 3 оперативной памяти появляется информация, 20 записанная по первому адресу. Эта информация поступает в устройство 2 формирования сигналов, а так как с помощью дещифратора 10 строки произошло обращение к второй строке управляемого транс-ро;7 вход7 эл ем ен та Ил Й7 первый паранта, то устройство 2 формирования j oTOporo соединен со счетным входом счет- сигналов формирует импульсы для записи поступившей информации во вторую строку

тыи подключены соответственно к второму, первому, третьему и четветому управляющим входам блока установки временных параметров, четвертый выход блока управления подключен к первому управляющему входу блока оперативной памяти, третий выход блока управления - к входу установки в «О счетчика адреса строк, второй выход блока управления - к вточика адреса строк и первым выходом бло ка установки временных параметров, третий вход элемента ИЛИ соединен с шестым выходом блока управления, седьмой выход

li iJJb J -JT V-. /д,г111Г1 1гил. w 4 riincj(JlO nci D Dl -4

ходе элемента 25 совпадения соответст- ° «оторого подключен к пятому управляюще- вует окончанию записи информации во вто- У ° установки временных па-г к - раметров, второй выход которого подключен к управляющему входу формирователя импульсных сигналов, адресные входы которого соединены с соответствующими выходас7ГрТок он;;;;и и з7пи;7иГф;7ма - дешифратора строки, входы которого сое- леднюю строку управляемого транспаранта 1, ™ « ходами счетчика адреса строк, последний выход дешифратора 10 строки переходит из нулевого состояния в единичное. Этот сигнал поступает на первый вход

управляемого транспаранта.

Появление единичного сигнала на вырую строку управляемого транспаранта 1, и новая информация записывается в следующую строку. Когда единичный сигнал на выходе элемента 25 совпадения появляетпоследний выход дешифратора строк подключен к первому стробирующему входу блока управления, выход элемента ИЛИ v - iiin liuv, yilKAVI IlCl Dl fl: O/.J JjLff

пускового устройства 15, которое при этом 40 ключей к второму управляющему входу бловьфабатывает единичный сигнал на своем оперативной памяти и входу элемента

первом выходе, устанавливающий счетчикизадержки, выход которого подключен к счети триггеры вислое состояние Этим закан- « У Р оперативной чивается формирование страницы информации на управляемом транспаранте.

45

памяти.

2. Формирователь по п. 1, отличающийся тем, что блок установки временных параметров содержит первый и второй регистры, первый и второй счетчики, первый и второй элементы совпадения, триггер, элемент ИЛИ, элемент И, элемент заФормула изобретения

2. Формирователь по п. 1, отличающийся тем, что блок установки временных параметров содержит первый и второй регистры, первый и второй счетчики, первый и второй элементы совпадения, триггер, элемент ИЛИ, элемент И, элемент за1. Формирователь страниц для голо- графического запоминающего устройства, содержащий жидкокристаллический управ- п , причем информационные входы ляемый транспарант, управляющие ВХОДЫ.КО-первого и второго регистров являются ин- торого соединены с выходами формирова-формационными входами блока, выходы теля импульсных сигналов, блок памяти,первого и второго регистров подключены к отличающийся тем, что, с целью повышениянечетным входам соответственно первого и надежности формирователя за счет увели-второго элементов совпадения, четные входы чения контраста изображения и отношения55 которых соединены с выходами первого и сигнал/шум, в формирователь введены блоквторого счетчиков, вход начальной уста- установки временных параметров, блок one-новки первого счетчика соединен через ративной памяти, счетчик адреса оператив-элемент задержки с выходом элемента ИЛИ,

ной памяти, счетчик адреса строк, дешифратор строки, элемент ИЛИ, элемент задержки и блок управления, причем информационные входы формирователя импульсных сигналов соединены соответственно с информационными выходами блока оперативной памяти, информационные входы которого соединены с выходами первой группы блока памяти, выходы второй группы которого подключены к информационным

входам блока установки временных парамет- ров, адресные входы блока оперативной памяти соединены с выходами счетчика адреса оперативной памяти и адресными вхо- дами блока управления, первый выход ко- торого подключен к входу установки в «О счетчика адреса оперативной памяти, выходы блока управления с второго по пяро;7 вход7 эл ем ен та Ил Й7 первый j oTOporo соединен со счетным входом счет-

тыи подключены соответственно к второму, первому, третьему и четветому управляющим входам блока установки временных параметров, четвертый выход блока управления подключен к первому управляющему входу блока оперативной памяти, третий выход блока управления - к входу установки в «О счетчика адреса строк, второй выход блока управления - к вто - дешифратора строки, входы которого сое- ™ « ходами счетчика адреса строк,

последний выход дешифратора строк подключен к первому стробирующему входу блока управления, выход элемента ИЛИ подff

Р оперативной

памяти.

2. Формирователь по п. 1, отличающийся тем, что блок установки временных параметров содержит первый и второй регистры, первый и второй счетчики, первый и второй элементы совпадения, триггер, элемент ИЛИ, элемент И, элемент , причем информационные входы первого и второго регистров являются ин- формационными входами блока, выходы первого и второго регистров подключены к нечетным входам соответственно первого и второго элементов совпадения, четные входы которых соединены с выходами первого и второго счетчиков, вход начальной уста- новки первого счетчика соединен через элемент задержки с выходом элемента ИЛИ,

ключей к единичному входу первого триггера и первому входу первого элемента ИЛИ, второй вход которого соединен с первым выходом пускового узла, нулевым входом первого триггера, первым входом второго элемента ИЛИ и является седьмым выходом блока, выход первого элемента ИЛИ подключен к нулевому входу второго триггера, единичный вход которого соединен с входом генератора импульсов и втопервый вход которого подключен к нулевому входу триггера и является пятым управляющим входом блока, второй вход элемента ИЛИ соединен с выходом первого элемента совпадения, который является первым выходом блока, счетный вход первого счетчика соединен с выходом второго элемента совпадения, синхровходом триггера и входом начальной установки второго счетчика счетньж вход ,оторо- ------,,,., выход

ГГемГа-И ТоТоГ

соответственно лока входГ з ап иси со еди ен с выходом ге нератора импульсов

выходом блока.. ляется первым выходом блока, и входом

° :гпЬ:;: г„ т™7гг™

вой узел, узел Фихс,, ,„, второго одновибратора соединен с прямым

выходом первого триггера и является четвертым выходом блока, первый вход которого соединен с п ервым входом пускоЬиИ OV-l l,J .- -| И второй триггеры, первый и второй элементы ИЛИ, первый и второй одновибра- торы, элемент И, элемент задержки и генератор импульсов, причем входы узла фиксации адреса являются адресными входами блока, выход узла фиксации адреса под25

вого узла, второй вход которого является вторым входом блока.

ключей к единичному входу первого триггера и первому входу первого элемента ИЛИ, второй вход которого соединен с первым выходом пускового узла, нулевым входом первого триггера, первым входом второго элемента ИЛИ и является седьмым выходом блока, выход первого элемента ИЛИ подключен к нулевому входу второго триггера, единичный вход которого соединен с входом генератора импульсов и вто ------,,,., выход

выходом первого триггера и является четвертым выходом блока, первый вход которого соединен с п ервым входом пуско25

вого узла, второй вход которого является вторым входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оценки работы оператора | 1990 |

|

SU1748165A1 |

| Устройство для психологических исследований | 1989 |

|

SU1708302A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| УСТРОЙСТВО ДЛЯ ТРЕНИРОВКИ ПАМЯТИ ОПЕРАТОРА | 1991 |

|

RU2020606C1 |

| Логическое запоминающее устройство | 1983 |

|

SU1140172A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Обнаружитель комбинаций двоичных сигналов | 1986 |

|

SU1325724A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1654852A1 |

| Устройство для ввода информации | 1981 |

|

SU1005019A1 |

| Устройство для отображения информации | 1987 |

|

SU1437909A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение надежности работы и достоверности считывания. Голографическое постоянное запоминающее устройство содержит оптически связанные блок излучателей, выполненный в виде решетки инжекционных лазеров и подключенный через блок накачки к блоку управления, носитель голограмм и фотоприемную матрицу, работающую в режиме накопления заряда и подключенную через формирователь импульсов стирания к блоку управления, коммутатор адресных шин подключенный к первой группе выходов счетчика элементов матрицы, а через коммутаторы нечетных разрядных шин - к первому и второму входам дифференциального усилителя, причем вторая группа выходов счетчика элементов матрицы подключена к входам управления коммутаторов нечетных и четных разрядных шин, а третья группа выходов счетчика элементов матрицы связана с адресными входами блока оперативной памяти, вход управления которого подключен к одновибратору, четвертый выход счетчика элементов матрицы подключен к первому входу блока управления, третий выход которого связан с первым входом счетчика элем-ентов матрицы, блок компараторов, блок одновибраторов, распределитель импульсов, первый и второй регистры, узел вычитания, первый и второй счетчики, дешифраторы «О и «1, триггер, счетчик времени, дешифратор, два инвертора, элемент И, четыре элемента ИЛИ и элемент задержки. 2 з.п. ф-лы, 1 ил. 5S (Л

ilLJ

п

| Автометрия, 1982, № 1, с | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

Авторы

Даты

1988-04-15—Публикация

1986-09-29—Подача