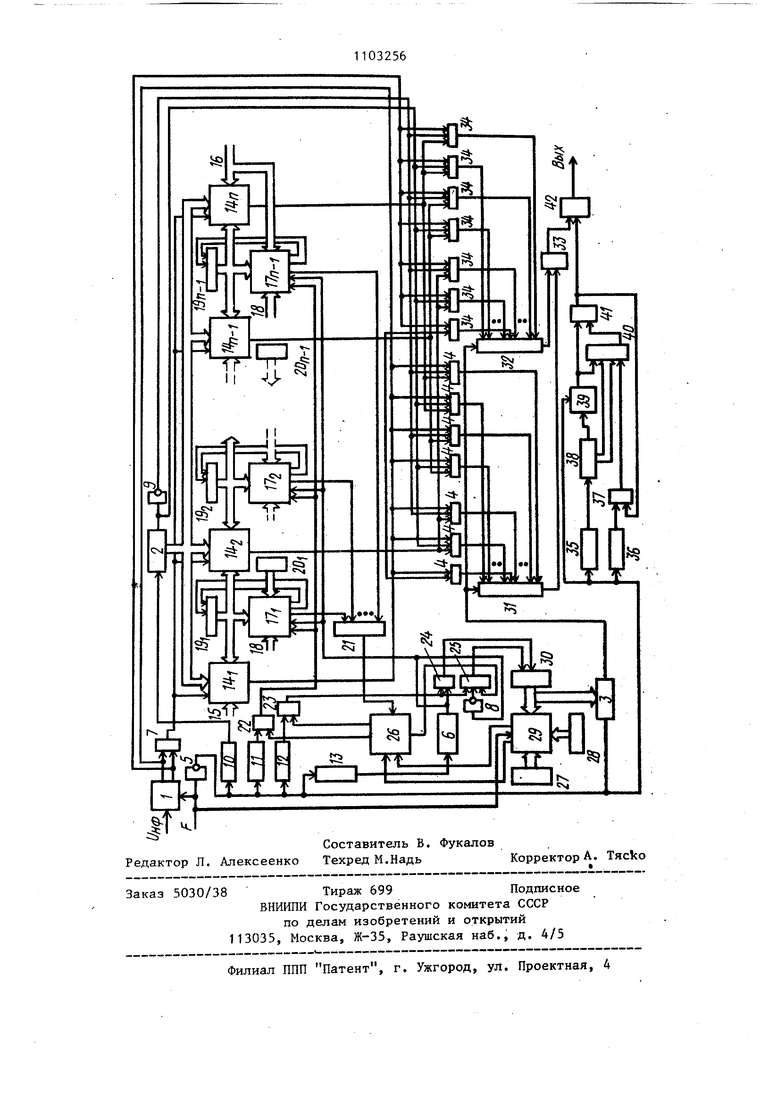

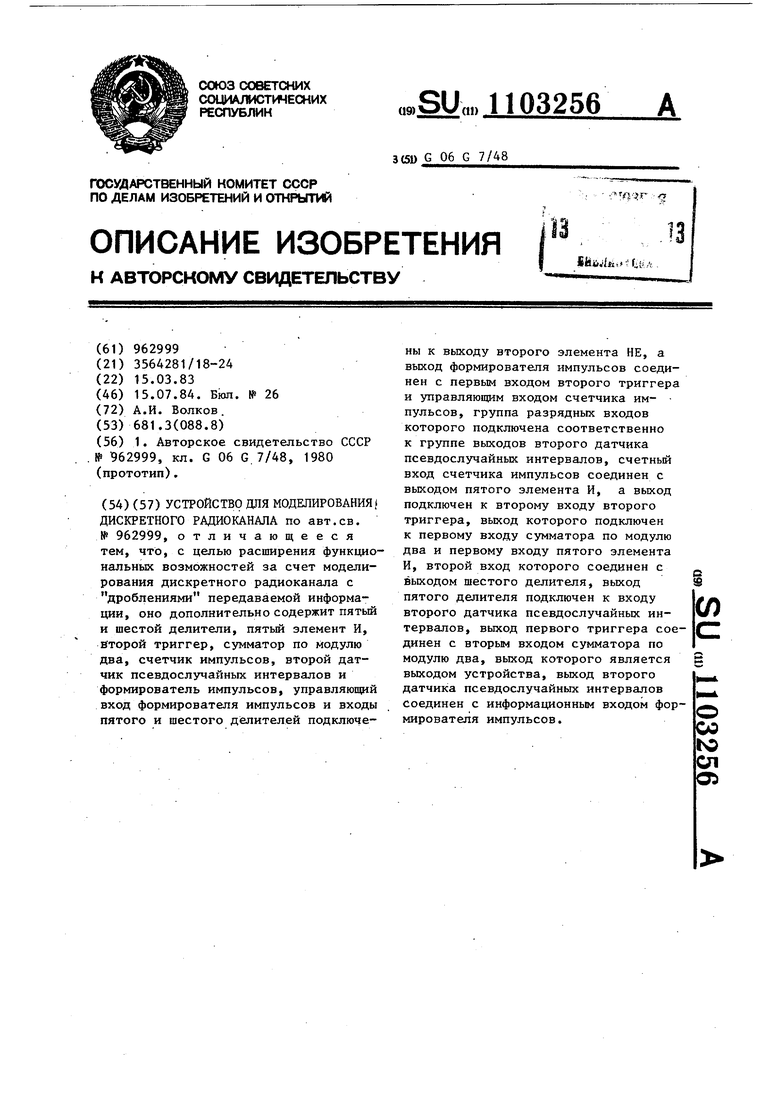

« Изобретение относится к аппаратур ным средствам электронного моделирования дискретных радиоканалов связи и может быть использовано при исследовании помехоустойчивости при приеме дискретной информации. По основному авт.св. 962999 известно устройство для моделирования дискретного радиоканала, содержащее входной каскад, вход которого являет ся входом устройства, элемент ИЛИ, две группы элементов И, группу блоков, сравнения, элемент НЕ, генератор псевдослучайной последовательности, два дискретных элемента задержки, первый триггер, группу логических коммутаторов, группу регистров хране ния, блок выбора перехода, датчик псевдослучайных интервалов, второй элемент НЕ, группу реверсивных счетчиков, общий элемент И, блок управления, четьфе делителя частоты, уп. равляемьй делитель частоты, третий элемент НЕ, четыре элемента И, первы выход входного каскада соединен с первым входом элемента ИЛИ и с первыми входами элементов И первой груп пы, вторые входы первых элементов И первой и второй группы подключены к выходу первого блока сравнения группы, выходы К-го блока сравнения группы (К 2,п) соединены с вторыми входами 2(К-1)-го и (2К-1)-го элементов И первой и второй группы, вто рой выход входного каскада подключен к первым входам элементов И второй группы и к второму входу элемента ИЛИ, третьи входы Р х(Р 2,2п-1) элементов И первой группы непосредственно, а третьи входы К-х элементов И второй группы через первый элемент НЕ соединены с выходом генератора псевдослучайной последователь ности, вход которого подключен к выходу первого делителя частоты, выходы первых элементов И первой и второй группы подключены к п-м входа первог.о и второго дискретных элементов задержки соответственно, выходы (2М+1)-х элементов И (,) первой и второй группы соединены соответственно с (г1+М)-м входом первого и второго дискретных элементов заДержки, выходы 2о6-х элементов (, п+1) первой и второй группы подключены соответственно к (п-о1)-м входам первого и второго дискретных элементов задержки, тактовые входы которых 56 соединены с выходом управляемого делителя частоты, выходы первого и второго дискретных элементов задержки подключены к нулевому и единичному входам первого триггера, выход элемента ИЛИ соединен с входами считывания блоков сравнения группы, входы первой группы входов которых подключены к разрядным выходам генератора псевдослучайной последовательности, входы второй группы входов первого и последнего блоков сравнения группы соединены с входами минимального и максимального числа первого и последнего логических коммутаторов группы соответственно, группа выходов J-ro реверсивного счЦтчика группы (j 1,) подключена к входам второй группы -го блока сравнения группы, к входам первой группы вхоДов (j+1)-ro блока сравнения и к входам первой группы логических коммутаторов группы, входы второй группы -X логических коммутаторов группы (1,п-2) соединены с выходами соответствующего регистра хранения группы, входы третьей группы логических коммутаторов группы подключены соответственно к входам констант устрой ства, тактовые входы логических коммутаторов группы соединены с выходом первого элемента И, первый вход которого подключен к выходу второго делителя частоты, а. второй вход к первому выходу блока выбора перехода, управляющие входы логических коммутаторов группы соединены с выходом датчика псевдослучайных интервалов, первым входом второго элемента И, входом второго элемента НЕ, первый выход логических коммутаторов группы соединен с суммирующим входом соответствующего реверсивного счетчика группы, а второй выход - с его вычитаюидам входом, третьи выходы логических коммутаторов группы подключены. соответственно к входам общего элемента И, вькод которого соединен с первым входом блока выбора перехода, второй и третий входы которого подключены соответственно к первому и второму выходам блока управления, тактовьй вход которого соединен с тяктовым входом устройства непосредственно, а через второй элемент НЕ с входами четырех делителей частоты и входам управляемого делителя частоты, группы управляющих входов которого подключены к разрядным выходам реверсивного счетчика и к входам первой группы блока управления, входы второй группы которого соединены с разрядными выходами первого дополнительного регистра хранения, а входы третьей группы блока управле ния подключены соответственно к разрядным выходам второго дополнительного регистра хранения, выход первог делителя частоты соединен с входом генератора псевдослучайной последовательности, выход третьего делите ля частоты подключен к первому входу третьего элемента И, второй вход которого соединен с вторым выходом бло ка выбора перехода, а выход - с вторым входом второго элемента И и с первым входом четвертого элемента И, второй вход которого подключен к выходу третьего элемента НЕ, третий вход четвертого элемента И соединен с третьим выходом блока выбора перехода, суммирующий вход дополнительно го реверсивного счетчика подключен к выходу второго элемента И, а вычитающий вход - к выходу четвертого элемента И, выход четвертого делителя частоты соединен с входом датчика псевдослучайных интервалов. Это устройство позволяет смоделировать дискретный радиоканал с замираниями за счет возможности непосредственно задавать закон распределения плотности вероятности временных искажени фронтов посьшок tl . Недостатком данного устройства яв ляется то, что оно не позволяет моделировать дискретный радиоканал свя зи с дроблениями, которые могут. присутствовать в реальном канале. Цель изобретения - расширение функциональных возможностей устройст ва за счет моделирования дискретного канала с дроблениями передаваемой .информации. Поставленная цель достигается тем, что в устройство для моделирования дискретного радиоканала введен пятый и шестой делители, пятый элемент И, второй триггер, сумматор по модулю два, счетчик импульсов, второ да:тчик псевдослучайных интервалов и формирователь импульсов, управляющий вход формирователя импульсов и входы пятого и шестого делителей подключены к выходу второго элемен. та НЕ, а выход формирователя импульсов соединен с первым входом второго триггера и управляющим входом счетчика импульсов, группа разрядных входов которого подключена соответственно к группе выходов второго датчика псевдослучайных интервалов, счетный вход счетчика импульсов соединен с выходом пятого элемента И, а выход подключен к второму входу второго триггера, выход которого подключен к первому входу сумматора по модулю два и первому входу пятого элемента И, второй вход которого соединен с выходом шестого делителя, вьрсод пятого делителя подключен к входу второго датчика псевдослучайных интервалов, выход первого триггера соединен с вторым входом сумматора по модулю два, выход которого является вьгходом устройства, выход второго датчика псевдослучайных интервалов соединен с информационным входом формирователя импульсов. На чертеже приведена схема предлагаемого устройства. Устройство содержит входной каскад 1, генератор 2 псевдослучайной последовательности, управляемый делитель 3, первую группу элементов И 4, первый элемент НЕ 5, первый датчик 6 псевдослучайных интервалов, элемент ИЛИ 7, второй и третий элементы НЕ 8 и 9, первый - четвертый делители 10-13, группу блоков 14 сравнения, первый и последний их которых имеют соответственно входы минимального 15 и максимального 16 чисел, группу логических коммутаторов 17 с входами констант 18, группу реверсивных счетчиков 19, группу регистров 20 хранения, общий элемент и 21, четыре элемента И 22-25, блок 26 выбора перехода, первый и второй дополнительные регистры 27 и 28 хранения, блок 29 управления, реверсивньй счетчик 30, дискретные элементы 31 и 32 задержки, первый триггер 33, вторую группу элементов И 34, пятый и шестой делители 35 и 36, пятый элемент И 37, второй датчик 38 псевдослучайных интервалов, формирователь 39 импульсов, счетчик 40 импульсов, второй триггер 41 и сумматор 42 по модулю два. Первый выход входного каскада 1 соединен с первым входом элемента ИЛИ 7 и с первыми входами соответствующих элементов И 4 первой группы, вторые входы элементов И 4 и 34 соединены с выходами соответствующих блоков 14 сравнения, а выходы - с соответствующими входами дискретного элемента 31 задержки, подключенного выходом к нулевому входу триггера 33, второй выход входного каскада 1 соединен с вторым входом элемента ИЛИ 7, подключенного вьшодом к входа считывания блоков 14 сравнения группы и к первым входам элементов И 34 второй группы, выходы которых соединены с соответствующими входами диск ретного элемента 32 задержки, подклю ченного к единичному входу триггера 33. Тактовый вход входного каскада 1 соединен с тактовым входом блока 29 управления непосредственно и через элемент НЕ 5 с входами делителей 10-13. Выход делителя 10 подключен к тактовому входу генератора 2 псевдослучайной последовательности, выходы соответствующих разрядов которого соединены с первыми входами блоков 14 сравнения. Выходы делителе 11 и 12 подключены к первым входам соответственно элементов И 22 и 23, вторые входы которых соединены соответственно с первым и вторым выходам блока 26 выбора перехода, а выходы соответственно с тактовыми входами логических коммутаторов 17 и первыми входами элементов И 24 и 25, подключенных выходами к вычитающему и суммирующему входам реверсивного счетчика 30 соответственно. Выход делите ля 13 соединен с тактовым входом дат чика 6 псевдослучайных интервалов, выход которого через элемент НЕ 8 подключен к второму входу элемента И 25 и непосредственно к второму входу элемента И 24 и к управляющему входу логических коммутаторов 17 первый и второй выходы которых соеди нены соответственно с суммирующими и вычитающими входами соответствующих реверсивных счетчиков 19, а третьи выходы - с соответствующими входами общего элемента И 21, выход I которого соединен с первым входом блока 26 выбора перехода, второй и третий входы которого соединены соответственно с первым и вторым вы ходами блока 29 управления, подклюНенного первыми, вторыми, третьими входами соответственно к выходам разрядов регистров 27 и 28 хранения и реверсивного счетчика 30, выходы разрядов которого соединены также с управляющими входами управляемого делителя 3, подключенного выходом к тактовым входам дискретных элементов 31 .и 32 задержки, а входом - к выходу элемента НЕ 5. Выходы разрядов реверсивных счетчиков 19 соединены с первыми входами соответствующих логических коммутаторов 17, а также с вторыми и третьими входами соответствующих блоков 14 сравнения. Вторые входы всех логических коммутаторов 17, кроме последнего, соединены с выходами разрядов соответствующих регистров 20 хранения, а вторые входы последнего логического коммутатора 17 соединены с входами 16 максимального числа последне: о блока 14 сравнения. Выход генератЪра 2 псевдослучайной последовательности непосредственно и через элемент НЕ 9 соединен с третьими входами соответствующих элементов И 4. Третий выход блока 26 выбора перехода соединен с третьим входом элемента И 25. Входы делителей 35 и 36 соединены между собой, с управляющим входом формирователя 39 импульсов и с выходом элемента НЕ 5, выход делителя35.соединен с входом датчика 38 псевдослучайных интервалов, выходы соответствующих разрядов которого соединены с входами разрядов счетчика 40, а выход последнего разряда - с-входом формирователя 39 импульсов, выход которого соединен с входом записи четчика 40 и первым входом триггера 41, подключенного вторым входом к выходу счетчика 40, а выходом - к первому входу сумматора 42 по модулю два и первому входу элемента И 37, второй вход которого соединен с выходом делителя 36, а выход - со счетным входом счетчика 40, при этом второй вход сумматора 42 подключен к выходу триггера 33, а его выход является выходом устройства. Устройство работает следующим образом. На входах i-го логического коммутатора 17 устанавливают в параллельном коде двоичное число К; t(2-n)i, где М- разрядность двоичного числа, подаваемого в параллельном коде на первые входы блоков 14 сравнения с выходом разрядов генератора 2; (h-1) - число логических коммутаторов г17. Перед началом работы устройства в реверсивные счетчики 19 и соответс; 71вующие им регистры 20 хранения записывают N-разрядные числа, , с помощью которых задается закон распределения средней во времени плотности вероятности временных искажений фронтов посылок, при этом на 1входах 15 и 16 устанавливают сооти ,,аГ2 ве1гственно числа М Число отводов элементов 31 и 32 задержки равно 2п-1. Частота импуль-. сов., подаваемых на тактовые входы входного каскада 1 и блока 29 управления непосредственно и на входы делителей 10-13 и управляемого делителя 3 должна удовлетворять условию р7,, где В - скорость передачи информации. Воды. Входной каскад 1 формирует импульсы, совпадающие во времени с фронтами посылок дискретной информации, поступающей на его вход, пропус кая на первьй вход импульс из последовательности F , следующий непосред ственно за положительным фронтом, а на второй выход - за отрицательным фронтом. Импульсы фронтов с выхода элемента ИЛИ 7 поступают на считывающий вход блоков 14 сравнения. Импульс фронта проходит на выход блока 14 в случае, если текущее значение N -раз рядного числа М; на выходах разрядов генератора 2 псевдослучайных последовательностей лежит в пределах М- :М.М. При использовании в качестве генератора 2 регистра сдвига с сумматором по модулю два в цепи обратной связи частость появления импульса фронта на выходе i-ro блока 14 сравнения равна а - м -1-LU-i Импульс на выходе входного каскад 1 открывает по первому входу элемент И первой группы, выходы которых подключены к входам элемента 31 задержки. Импульс с выхода блока 14 сравнения поступает на второй вход элемента И 4 первой группы или элемента И 34 второй группы, выход которого подключен к п-му входу элементов 31 и 32 задержки, импульс с выхода блок 14 сравнения поступает на вторые вхо ды элементов И 4 и 34, выходы которы соединены с (п-1 +1)-м и (n+v-1)-M входами элементов 31 и 32 задержки. На третьи входы элементов И4, выходы 6 которых соединены с входами элементов задержки от (п-1)-го до первого, поступает сигнал с выхода датчика 6 непосредственно, а на входы элементов И 4, выходы которых соединены C входами с (п+1)-го до (2п-1)-го через элемент НЕ 9. Так как появление единичного и нулевого сигнала на выходе генератора 2 равновероятно, импульсы отрицательных фронтов посылок равновероятно могут поступить на (п-1 + 1)-й и ()-й входы элемента 31 задержки, а-импульсы положительных фронтов - на входы элемента 32 задержки. Таким образом, частости задержек импульсов фронта на величины T| 1/f h+i-l , Т- равны между собой, т.е. задержки фронта симметричны относительно величины Тр п/, а сама частость задержек Т, Т равна Так как импульсы с элемента 31 задержки поступают на нулевой вход триггера 33, а импульсы с выхода элемента 32 задержки на единичный вход, с прямого выхода триггера снимается двоичный сигнал, отличаюрийс я тем, что фронты посылок искажены во времени псевдослучайным образом по заданному закону распределения плотности вероятности этих искажений через числа М.. Работа устройства обеспечивает моделирование по вторичным характеристикам гауссовского канала связи, пр.гчем если М,/ О, а М 2 , некоторые импульсы фронтов не поступают на линии 31 и 32 задержки, что соответствует в реальном канале связи ощибочному приему посыпки из-за ее полной инверсии. Изменение среднего закона распределения временных искажений фронтов, т.е. имитация замираний сигнала в коротковолновом радиоканале, реализуется путем изменения двоичных чисел М, находящихся в соответствующих реверсивных счетчиках 19. Осуществляется это следующим образом. Импульсы с выхода делителя 11 через элемент И 22 поступают на тактовые входы логических коммутаторов 17. Если текущее значение числа М , находящегося в реверсивном счетчике 19, удовлетворяет условию К, (MJ - число в регистре 20-хранения), то импульсы, присутствующие на тактовом входе логического коммутатора 17, проходят на его перкъш или второй вход, т.е. на суммирующий или вычитающий вход реверсивного счетчика, в зависимости от этого единичный или нулевой сигнал присутствует на управляющих входах логических коммутаторов 17, куда он поступает с выхода генератора 2. В случае К М. и при нулевом сигнале на выходе датчика 6 импульсы с тактового входа логического коммутатора на входы реверсивного счетчика не проходят, т.е. число Mt имеет возможность изме jf няться только в пределах К М.М.. В случае К- М появление импульсов считывания на выходах всех блоков сравнения равновероятно, что соответ ствует присутствию в канале только шума. В случае М на третьем выходе логического коммутатора 17 формируется единичный сигнал, которы поступает на соответствующий вход общего элемента И 21. При единичных потенциалах на всех входах элемента И 21 сигнал с его выхода поступает на первьй вход блока 26 выбора перехода. второй вход блока 26 поступает единичный сигнал с первого выхода блока 29 управления в случае равенства числа в реверсивном счетчи ке 30, численно равного текущему коэффициенту деления управляемого де лителя 3,числу в регистре 27, равному максимально возможному коэффициенту делителя 3. На третий вход бло.ка 26 поступает единичный сигнал с второго выхода блока 29 управления в случае равенства, числа в реверсивном счетчике 30 числу в регистре 28, равному минимально возможному коэффициенту деления блока 3. На третьем выходе блока 26 выбора перехода присутствует единичный сигнал при нулевом сигнале на его втором входе (коэффициент деления делителя 3 максимален). Таким образом, сигнал с выхода элемента И 21 устанавливает на перво выходе блока 26 нулевой потенциал, а на втором - единичный. При этом элемент И 22 закрывается по второму 1 610 входу, а элемент И 23 открывается и импульсы с выхода делителя 12 начинают поступать на первые входы элементов И 24 и 25. При единичном сигнале на выходе датчика 6 псевдослучайных интервалов эти импульсы-проходят на вычитающий вход реверсивного счетчика 30, а при нулевом - на суммирующий. Таким образом, при единичном сигнале на выходе датчика 6 частота на выходе делителя 3 увеличивается, а при отрицательном - уменьшается. При увеличении частоты на тактовых входах линий 31 и 32 задержки абсолютные временные интервалы между моментом идеального положения фронта и моментом реального положения этого фронта уменьшаются, так как величина -j nt(ii) обратно пропорциональнА частоте f , т.е. в этом случае уменьшается дисперсия временных искажений фронтов, что соответствует увеличение отношения сигнал/шум в канале связи. По достижении коэффициентом деления делителя 3, зафиксированным а реверсивном счетчике 30, минимального значения элемент И 25 закрывается По третьему входу, что предотвращает дальнейшее уменьшение этого коэффициента. По достижении коэффициентом деления максимального значения и появлении единичного сигнала на первом входе блока 26 выбора перехода элемент И 22 открывается, а элемент И 23 закрывается по второму входу. Таким образом, при единичном сигнале на выходе датчика 6, т.е. при увеличении отношения сигнал/шум, сначала увеличиваются числа М в реверсивных счетчиках 19 (, ), а у при М j М начинает увеличиваться частота f на тактовых входах элементов 31 и 32 задержки, что приводит к уменьшению дисперсии временных искажений. При нулевом сигнале на . вькоде датчика 6 сначала уменьшается частота , а затем М() образом осуществляются замирания Коэффициент деления целителя 3 устанавливается таким образом, чтобы частота на его выходе быпа меньше скорости передачи информации. Так как частота импульсов на выходе делителя 11 определяет значение глубины замираний, а частота импульсов на выходе делителя 12 - значение глубины

амираний при изменении частоты, о коэффициенты деления этих делитеей подбираются таким образом, чтобы эти значения были равны. Коэффициент еления делителя 13 выбирается таким 5 образом, чтобы средний период смены полярности сигнала на выходе датчика 6, определяемьш частотой импульсов на выходе делителя 13, равнялся выбранному периоду замираний в ка- 10 нале связи. Элемент НЕ 5 необходим ля того, чтобы импульсы с выхода входного каскада 1 и делителей 10-13 не совпадали во времени, чем обеспечивается устойчивость работы устрой- is ства.

Импульсы дробления дискретного сигнала моделируются следующим образом.

На выходах делителей 35 и 36 фор- 20 мируются импульсы с частотами F и р2 соответственно. Импульсы частоты F, поступающие на вход датчика 38 псевдослучайных интервалов, определяют среднюю частоту появления им- 25 пульсов дроблений, так как начало импульса дробления определяется формированием на выходе датчика 38 перепада из нулевого состояния в единичное. Формирователь 39 импульсовзо пропускает на свой выход импульс из

исходной последовательности, следующий непосредственно за перепадом 0-1 на выходе датчика 38, т.е. реализуется аналогично каскаду 1. Импульс с выхода формирователя 39 устанавливает триггер 41 в единичное состояние и записьшает в разряды счетчика 40 псевдослучайное число. После установки триггера 41 в единичное состояние открывается по первому входу элемент И 37 и на его выход поступают импульсы, которые подаются на вход счетчика 40 с частотой Импульс с выхода переполнения счетчика 40 устанавливает триггер 41 в нулевое состояние. Таким образом,на единичном выходе триггера 41 формируются положительные перепады импульсов дроблений, длительность которых обратно пропорциональна частоте FI и имеет равномерное распределение. Импульсы дроблений накладываются на дискретный сигнал с помощью сумматора 42 по модулю два.

Таким образом, предлагаемое устройство позволяет с достаточной степенью адекватности моделировать дискретный радиоканал связи с замираниями и дроблениями передаваемой информации .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования дискретного радиоканала | 1980 |

|

SU962999A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Генератор квазирегулярных последовательностей импульсов | 1981 |

|

SU991589A2 |

| Генератор квазирегулярных последовательностей импульсов | 1979 |

|

SU866717A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Генератор псевдослучайной последовательности импульсов | 1979 |

|

SU866716A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ) ДИСКРЕТНОГО РАДИОКАНАЛА по авт.св. № 962999, отличающееся тем, что, с целью расширения функциональных возможностей за счет моделирования дискретного радиоканала с дроблениями передаваемой информации, оно дополнительно содержит пятый и шестой делители, пятый элемент И, второй триггер, сумматор по Модулю два, счетчик импульсов, второй датчик псевдослучайных интервалов и формирователь импульсов, управляюп51й вход формирователя импульсов и входы пятого и шестого делителей подключены к выходу второго элемента НЕ, а выход формирователя импульсов соединен с первьм входом второго триггера и управляющим входом счетчика им- пульсов, группа разрядных входов которого подключена соответственно к группе выходов второго датчика псевдослучайных интервалов, счетный вход счетчика импульсов соединен с выходом пятого элемента И, а выход подключен к второму входу второго триггера, выход которого подключен к первому входу сумматора по модулю два и первому входу пятого элемента И, второй вход которого соединен с § выходом шестого делителя, выход пятого делителя подключен к входу (Л второго датчика псевдослучайных интервалов, выход первого триггера соединен с вторым входом сумматора по модулю два, выход которого является выходом устройства, выход второго датчика псевдослучайных интервалов соединен с информационным входом формирователя импульсов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для моделирования дискретного радиоканала | 1980 |

|

SU962999A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-15—Публикация

1983-03-15—Подача