1

Изобретение относится к цифровой

обработке сигналов, в частности к устройствам задержки информации в дискретной технике.

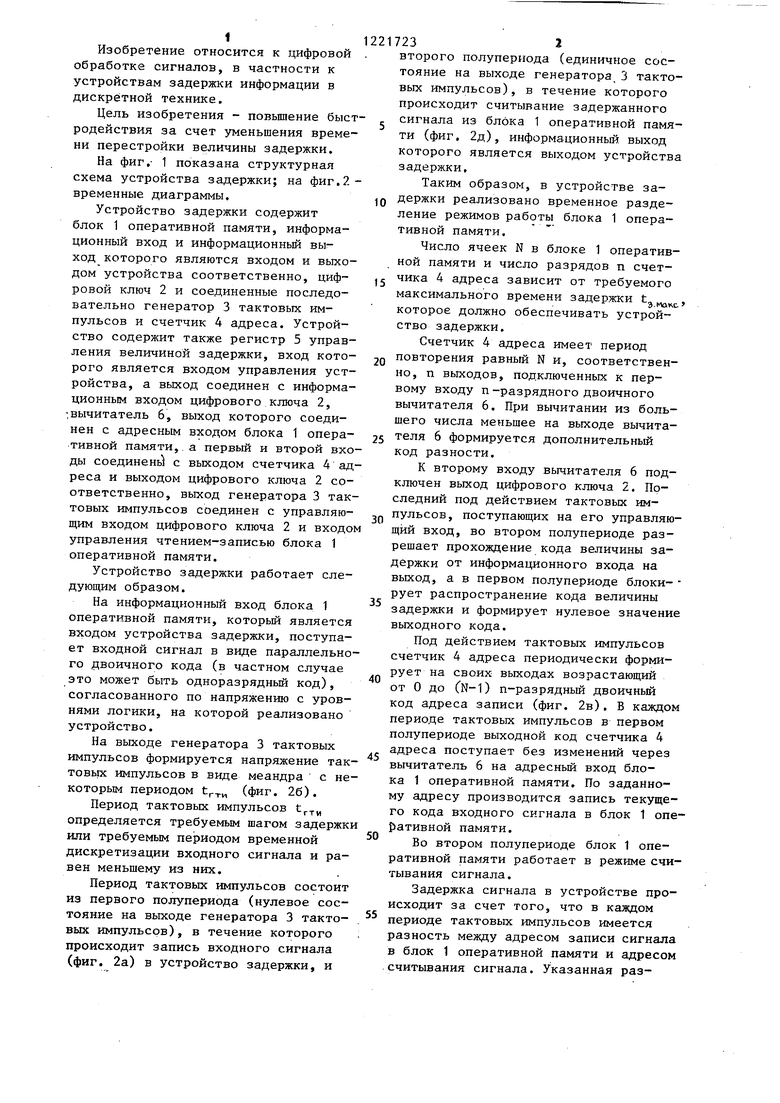

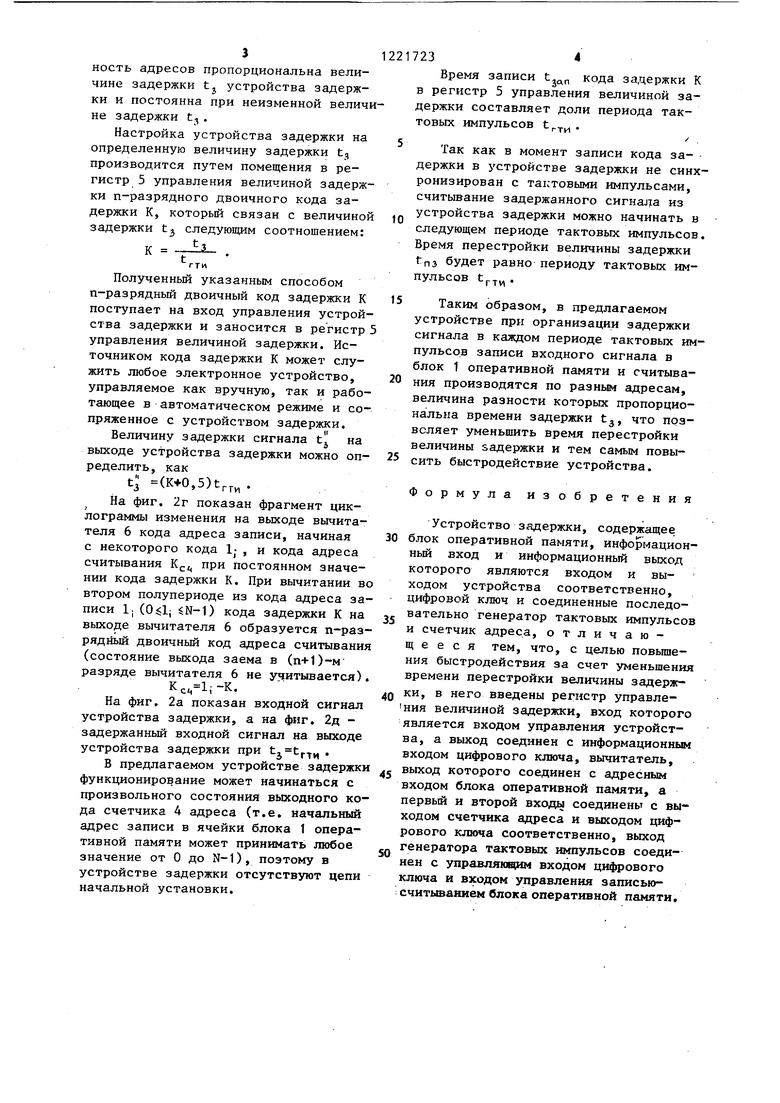

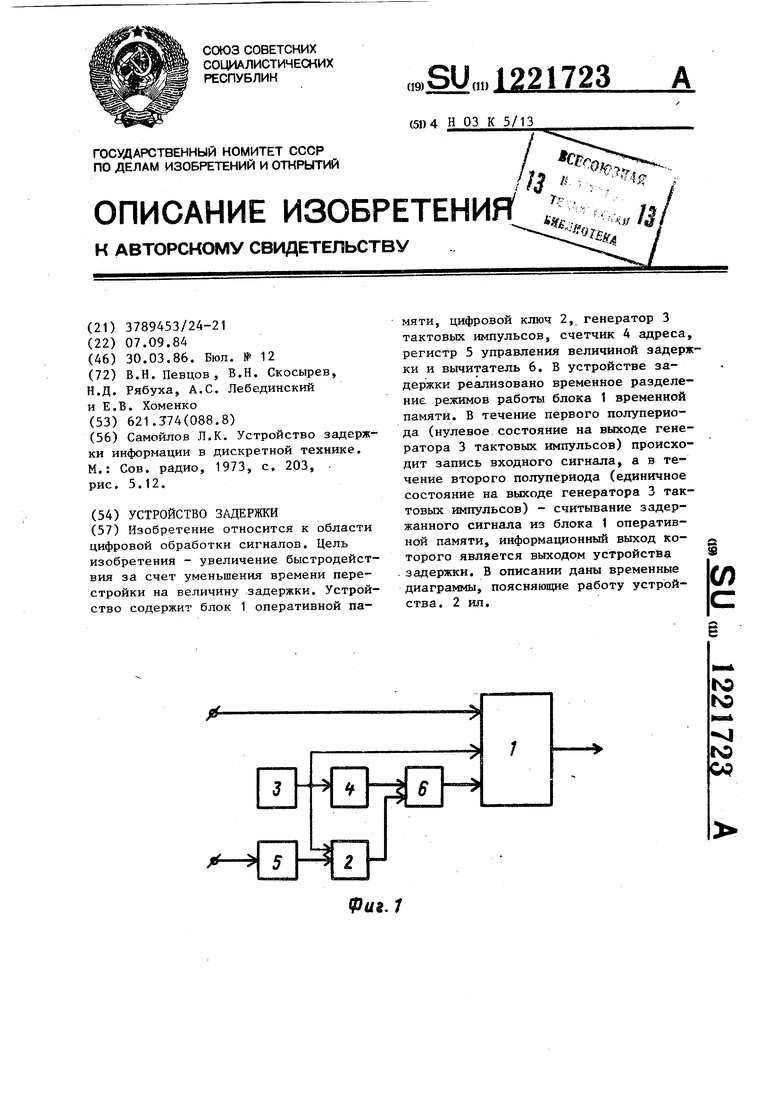

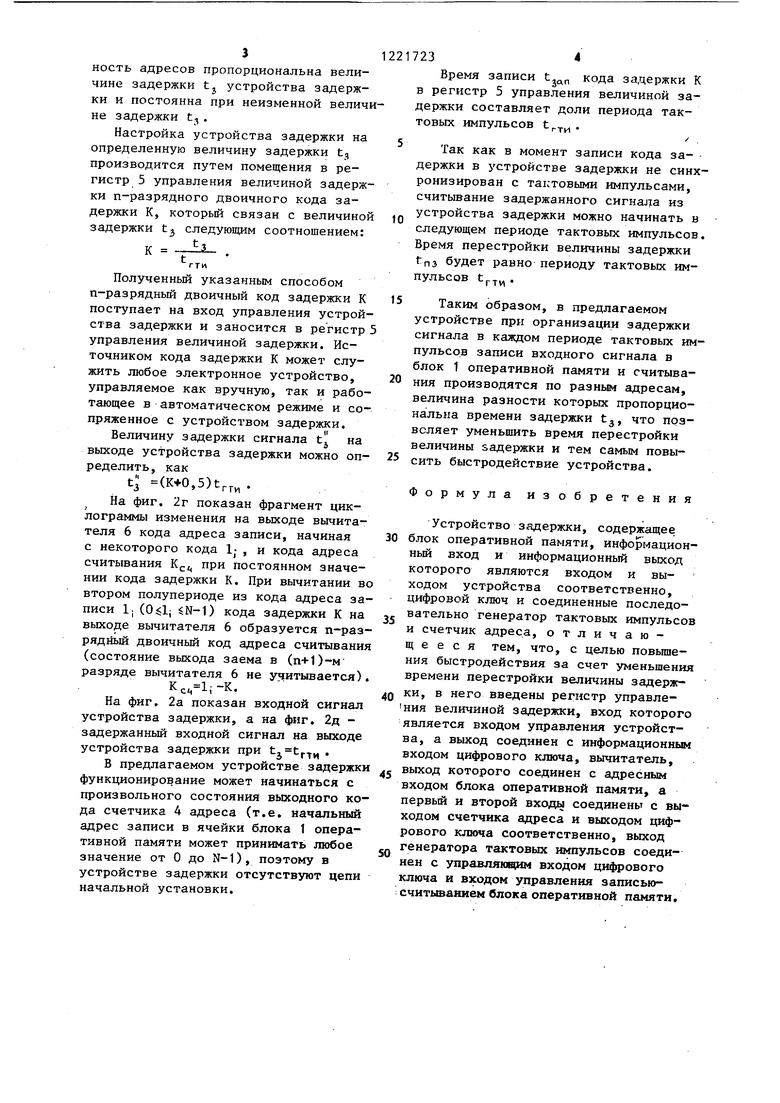

Цель изобретения - повышение быстродействия за счет уменьшения времени перестройки величины задержки. На фиг,- 1 показана структурная схема устройства задержки; на фиг.2- временные диаграммы.

Устройство задержки содержит блок 1 оперативной памяти, информационный вход и информационньш выход которого являются входом и выходом устройства соответственно, циф- ровой ключ 2 и соединенные последовательно генератор 3 тактовых импульсов и счетчик 4 адреса. Устройство содержит также регистр 5 управления величиной задержки, вход кото- рого является входом управления устройства, а выход соединен с информационным входом цифрового ключа 2, вычитатель 6, выход которого соединен с адресным входом блока 1 опера- тивной памяти, а первый и второй входы соединень с выходом счетчика 4 адреса и выходом цифрового ключа 2 соответственно, выход генератора 3 тактовых импульсов соединен с управляю- щим входом цифрового ключа 2 и входо управления чтением-записью блока 1 оперативной памяти.

Устройство задержки работает следующим образом.

На информационный вход блока 1 оперативной памяти, которьм является входом устройства задержки, поступает входной сигнал в виде параллельного двоичного кода (в частном случае это может быть одноразрядный код), согласованного по напряжению с уровнями логики, на которой реализовано устройство.

На выходе генератора 3 тактовых импульсов формируется напряжение так товьгх импульсов в виде меандра с некоторым периодом tpTM (фиг. 26).

Период тактовых импульсов t, определяется требуемым шагом задержк или требуемым периодом временной дискретизации входного сигнала и равен меньшему из них.

Период тактовых импульсов состоит из первого полупериода (нулевое состояние на выходе генератора 3 такто- вых импульсов), в течение которого происходит запись входного сигнала (фиг. 2а) в устройство задержки, и

7232

второго полупериода (единичное состояние на выходе генератора 3 тактовых импульсов), в течение которого происходит считывание задержанного сигнала из блока 1 оперативной памяти (фиг, 2д), информационньш выход которого является выходом устройства задержки.

Таким образом, в устройстве задержки реализовано временное разделение режимов работы блока 1 оперативной памяти.

Число ячеек N в блоке 1 оперативной памяти и число разрядов п счетчика 4 адреса зависит от требуемого максимального времени задержки t, „

у. МйКС

которое должно обеспечивать устройство задержки.

Счетчик 4 адреса имеет период повторения равный N и, соответственно, п вьпсодов, подключенных к первому входу п -разрядного двоичного вычитателя 6. При вычитании из большего числа меньшее на выходе вычитателя 6 формируется дополнительный код разности.

К второму входу вычитателя 6 подключен выход цифрового ключа 2. Последний под действием тактовых импульсов, поступающих на его управляющий вход, во втором полупериоде разрешает прохождение кода величины задержки от информационного входа на выход, а в первом полупериоде блоки- рует распространение кода величины задержки и формирует нулевое значени выходного кода.

Под действием тактовых импульсов счетчик 4 адреса периодически формирует на своих выходах возрастающий от О до (N-1) п-разрядный двоичньй код адреса записи (фиг. 2в). В каждо периоде тактовых импульсов в первом полупериоде выходной код счетчика 4 адреса поступает без изменений через вычитатель 6 на адресньй вход блока 1 оперативной памяти. По заданному адресу производится запись текущего кода входного сигнала в блок 1 опративной памяти.

Во втором полупериоде блок 1 оперативной памяти работает в режиме считывания сигнала.

Задержка сигнала в устройстве происходит за счет того, что в каждом периоде тактовых импульсов имеется разность между адресом записи сигнал в блок 1 оперативной памяти и адресо считывания сигнала. Указанная раз

3

ность адресов пропорциональна величине задержки tj устройства задержки и постоянна при неизменной величине задержки t.,.

Настройка устройства задержки на определенную величину задержки t, производится путем помещения в регистр 5 управления величиной задержки п-разрядного двоичного кода задержки К, которьй связан с величиной задержки t следующим соотношением:

.

гти

Полученный указанным способом п-разрядный двоичный код задержки К поступает на вход управления устройства задержки и заносится в регистр управления величиной задержки. Источником кода задержки К может служить любое электронное устройство, управляемое как вручную, так и работающее в автоматическом режиме и сопряженное с устройством задержки.

Величину задержки сигнала tj на выходе устройства задержки можно определить, как

t (K+0,5)t

гги

На фиг. 2г показан фрагмент циклограммы изменения на выходе вычита- теля 6 кода адреса записи, начиная с некоторого кода 1; , и кода адреса считывания Kj., при постоянном значении кода задержки К. При вычитании во втором полупериоде из кода адреса записи 1| ( $N-1) кода задержки К на выходе вычитателя 6 образуется п-раз- рядйый двоичный код адреса считывания (состояние выхода заема в (п+1)-м разряде вычитателя 6 не учитывается). Kt;t,li-K,

На фиг, 2а показан входной сигнал устройства задержки, а на фиг. 2д - задержанный входной сигнал на выходе устройства задержки при ,, .

В предлагаемом устройстве задержки функционирование может начинаться с произвольного состояния выходного кода счетчика А адреса (т.е. начальный адрес записи в ячейки блока 1 оперативной памяти может принимать любое значение от О до N-1), поэтому в устройстве задержки отсутствуют цепи начальной установки.

723

Время записи tj кода задержки К в регистр 5 управления величиной задержки составляет доли периода тактовых импульсов t.

/

Так как в момент записи кода задержки в устройстве задержки не синхронизирован с тактовыми импульсами, считывание задержанного сигнала из устройства задержки можно начинать в следующем периоде тактовых импульсов. Время перестройки величины задержки tn3 будет равно периоду тактовых импульсов tp .

Таким образом, в предлагаемом устройстве при организации задержки сигнала в каждом периоде тактовых импульсов записи входного сигнала в блок 1 оперативной памяти и считывания производятся по разным адресам, величина разности которых пропорцио- времени задержки t, что позволяет уменьшить время перестройки величины задержки и тем самым повысить быстродействие устройства.

Формула изобретения

Устройство задержки, содержащее блок оперативной памяти, информационный вход и информационный выход которого являются входом и выходом устройства соответственно, цифровой ключ и соединенные последовательно генератор тактовых импульсов и счетчик адреса, отличающееся тем, что, с целью повьппе- ния быстродействия за счет уменьшения времени перестройки величины задержки, в него введены регистр управле- ния величиной задержки, вход которого является входом управления устройства, а выход соединен с информационным входом цифрового ключа, вычитатель, выход которого соединен с адресным входом блока оперативной памяти, а первый и второй входы соединены с выходом счетчика адреса и выходом цифрового ключа соответственно, вьссод генератора тактовых импульсов соединен с управляющим входом цифрового ключа и входом управления записью- считыванием блока оперативной памяти.

Kl

KL-Fq

(puB.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый генератор импульсов | 1984 |

|

SU1248029A1 |

| Программируемая линия задержки | 1982 |

|

SU1193789A1 |

| Программируемый генератор импульсов | 1985 |

|

SU1298869A2 |

| Устройство автоматической подстройки частоты генератора | 1980 |

|

SU982203A1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Программируемый генератор импульсов | 1980 |

|

SU949785A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ЖИДКОСТИ | 1991 |

|

RU2012848C1 |

| УПРАВЛЯЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 2011 |

|

RU2450432C1 |

| Устройство групповой тактовой синхронизации | 1980 |

|

SU932641A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

Изобретение относится к области цифровой обработки сигналов. Цель изобретения - увеличение быстродействия за счет уменьшения времени перестройки на величину задержки. Устройство содержит блок 1 оперативной памяти, цифровой ключ 2, генератор 3 тактовых импульсов, счетчик 4 адреса, регистр 5 управления величиной задержки и вычитатель 6. В устройстве задержки реализовано временное разделение режимов работы блока 1 временной памяти. В течение первого полупериода (нулевое состояние на вЕаходе генератора 3 тактовых импульсов) происходит запись входного сигнала, а в течение второго полупериода (единичное состояние на выходе генератора 3 тактовых импульсов) - считывание задержанного сигнала из блока 1 оперативной памяти, информационный выход которого является выходом устройства задержки. В описании даны временные диаграммы, пояснякицие работу устройства. 2 ил. 9 1C ГС tsS OQ Фиг, 1

| Самойлов Л.К | |||

| Устройство задержки информации в дискретной технике | |||

| М.: Сов | |||

| радио, 1973, с | |||

| Эксцентричный фильтр-пресс для отжатия торфяной массы, подвергшейся коагулированию и т.п. работ | 1924 |

|

SU203A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-03-30—Публикация

1984-09-07—Подача