Изобретение относится к импульс-ной технике, а именно к устройствам временнойзадержки цифровых сигналов, например, в аппаратуре формирования и сканирования характеристики направленности MHoroaneMeHTHbik антенных решеток.

Целью изобретения является расширение функциональных возможностей за счет возможности одновременного формирования N выходных сигналов, сдвинутых на заданные промежутки времени.

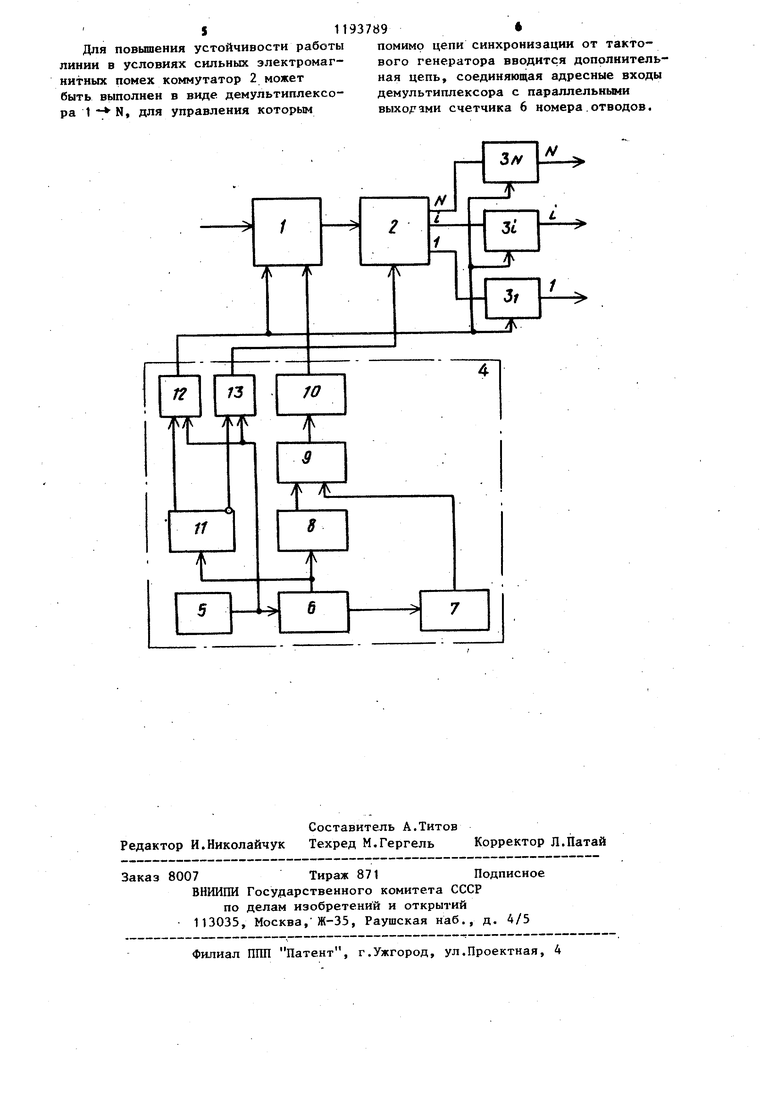

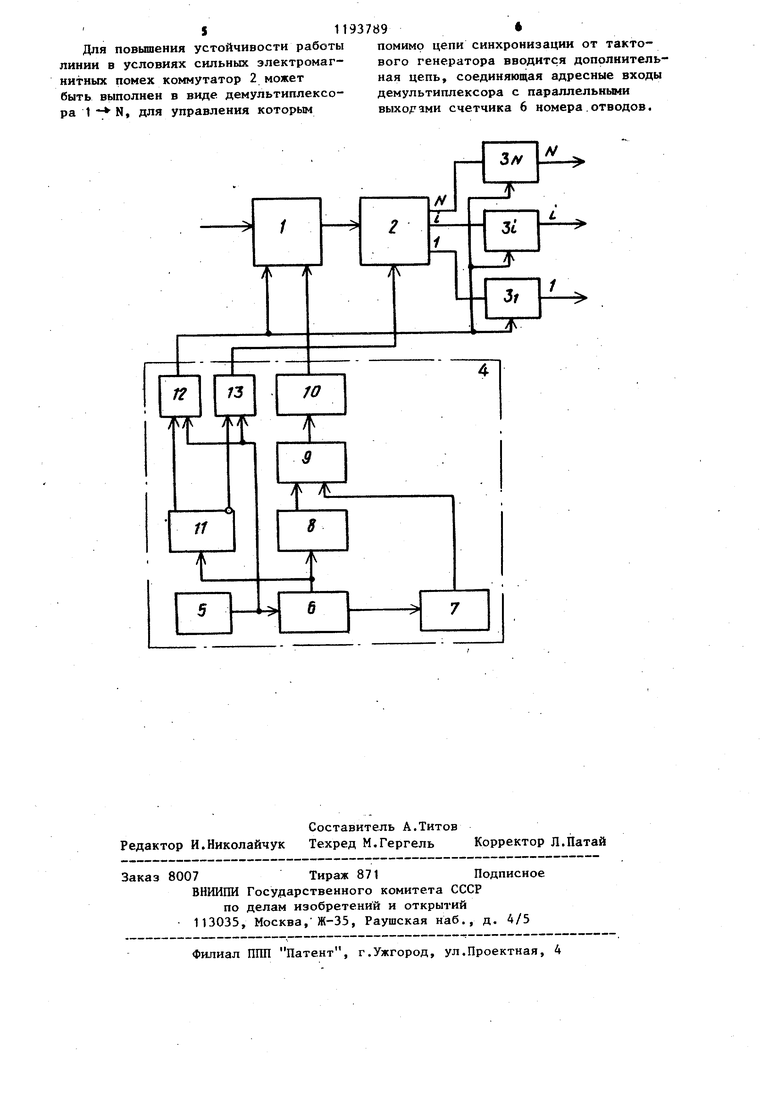

На чертеже: представлена структурная схема программируемой линии задержки.

Программируемая линия задержки содержит оперативное запоминающее устройство 1 с произвольной выборкой например с организацией М-ячеек по 1-разрядных двоичных слов в каждой, коммутатор 2, обеспечивающий переключение 1-разрядных двоичных слов с одного на N направлений и выполненный, например, на J регистрах сдвига с N выходами, N буферных -разрядных параллельных регистров (д и. блок 4 управления.

Адресные входы и вход управления оперативного запоминающего устройства 1 подключены соответственно к адресным И к первому управляющему выходу блока А управления, к второму управляющему выходу которого подключен управляющий вход коммутатора 2, информационный вход которого подключен к .выходу оперативного запоминающего устройства 1, а выходы - к входам буферных регистров 3ц,

Блок 4 управления содержит генератор 5 тактовых импульсов, подключенный выходом к счетчику 6 номера отвода, выход которого соединен с входом счетчика 7 текущего адреса записи, выход счетчика 6 номера отвода соединен с входом запоминающего устройства 8, подключенного выходом к первому входу вычитателя 9, выход которого соединен через регист 10 с адресными выходами блока 4 управления, Выход счетчика 6 номера отвода соединен также через дешифратор 1.1 нулевого состояния с первыми входами первого второго 13 элементов И соответственно, выходы которого являются соответственно первым и вторым управляющими выходами блока 4 управления, а вторые объединенные входы элементов И 12 и 13 подключены к выходу генератора 5 тактовых импульсов. Выход счетчика 7 текущего адреса записи соединен с вторым входом вычитателя 9,

Программируемая линия задержки работает следующим образом,,

Импульсы генератора 5 тактовых импульсов, поступая на счетный вход счетчика 6 номера отвода, переводят его последовательно в положения от О до. N, Информация с выходов счетчика 6 номера отвода в виде параллельного кода поступает на адресные входы запоминающего устройства 8 знчений задержек, определяя адрес ячейки памяти, в которой хранится двоичное число (коэффициент задержки) , пропорциональное времени задержки на i-M отводе линии, Импульсы переполнения счетчика 6 номера отвода поступают на счетный вход счетчика 7 текущего адреса записи, переводя его последовательно в положения от О до М, Информация с выходов запоминающего устройства 8 значений задержек и счетчика 7 текущего адреса записи поступают на входы вычитателя 9, где вычитанием коэффици- ента задержки из параллельного кода состояния счетчика 7 текущего адреса записи определяется адрес ячейки оперативного запоминающего устройства 1, из которой производится считы вание информации для формирования выходного сигнала для i-ro отвода линии. Эта информация сказывается задержанной по отношению к текущему времени, которое, определяется состоянием счетчика 7 текущего адреса записи, на число тактов, равное десятичному эквиваленту коэффициента задержки, Вычисленный адрес ячейки поступает на адр-эсныё входы оперативного запоминающего устройства 1 , через регистр 10, Считывание и запись в оперативное запоминающее устройство 1 происходит в зависимости от состояния счетчика 6 номера отвода. При поступлении информации на входы дешифратора 11 нулевого состояния с выходов счетчика 6 номера отвода для его состояний с .1 до N с прямого вькода дешифратора 11 нулевого состояния снимается сигнал, запрещающий прохождение импульсов тактовой частоты от генератора 5 тактовых импульсов через элемент И 12, в результате последний вырабаты3

вает,сигнал, устанавливающий оперативное запоминающее устройство 1 в режим считывания.

При нулевом состоянии счетчика 6 номера отвода с прямого выхода дешифратора 11 нулевого состояния поступает сигнал на элемент И 12, разрешающий прохождение через него одиночного импульса тактовой частоты, на время присутствия которого оперативное запоминающее устройство 1 установлено в режим записи и происходит запись входного сигнала в оперативное запоминающее устройство 1. При состояниях счетчика немера отвода 6 от 1 до N вычитатель 9 последовательно во времени формирует N адресов считывания из оперативного запоминающего устройства 1 сигнала, записанного в него. Оперативное запоминающее устройство в соответствии с вычисленными адресами вырабатывает N сигналов, соответствующих сигналам на отводах на текущем такте работы линии задержки. Двоичное слово с выхода оперативного запоминающего устройства 1 поступает на коммута- тор 2, осуществляющий преобразование последовательной информации на его входе в параллельнзто N-разрядную на выходах путем установки коммутатора в положения с 1 до N тактовыми импульсами управления с выхода Генератора 5 тактовых импульсов, проходящими через зЛемент И 13 при наличии сигнала разрешения, поступающего с инверсного выхода дешифратора Г1 нулевого состояния для состояний счетчика 6 номера отвода с 1 до N.

Для нулевого состояния счетчика 6 номера отвода дешифратор 1 1 нулевого состояния запрещает прохождение тактовых импульсов на управляющий вход коммутатора 2 и его переключения не происходит. Параллельный Nразрядный код с выходов коммутатора 2 поступает на информационные, входы буферных регистров 3 -Л , запись в которые происходит при поступлении на их управляющие входы одиночного импульса тактовой частоты с выхода элемента И 12 при нулевом состоянии счетчика номера отвода 6 одновременно с записью в оперативное запоминающее устройство 1 следующего значения входного сигнала. При состоянии счетчика 6 номера с 1 до N буферные регистры 3 J -3ц, находятся в режиме

93789

хранения информации. Выходы буферных регистров 3, -3fi представляют собой отводы линии задержки, с которых снимают выходные сигналы.

с Операция по определению адреса считывания и само считывание из оперативного запоминающего устройства 1 в буферные регистры 3 -3 jjj повторяется N раз за один такт работы ли10 НИИ. Длительность одного такта равна N периодам импульсов генератора 5 тактовых импульсов. N-й тактовый импульс, поступая на счетчик 6 отвода, переводит его из N-ro состояния

15 в нулевое, при зтом формируется импульс переполнения, поступающий на счетный вход счетчика 7 текущего адреса записи и переводящий его в следующее положение (т + 1). При новом положении счетчика 6 номера отводов в вычитателе 9 из кода, поступающего из счетчика 7, вычитается нулевой код, считанный, из запоминающего устройства 8 требуемого значения задержки. Результат вычитания является адресом записи входного сигнала для данного такта.

Далее работа линии циклически повторяется М раз, т.е. до момента заполнения счетчика 7 текущего адреса записи, после чего М + 1 импульс на входе счетчика 7 текущего адреса записи переходит в нулевое состояние и запись входного сигнала опять идет с О до М ячейки памяти.

Емкость оперативного запоминающего устройства с произвольной выборкой выбирается из следующих соображений:

jOKc

М

Т - N

М - количество ячеек памяти}

где макс требуемая максимальная

задержка;

Т - период тактовых импульсов;

N - количество требуемых отводов .

Таким образом, диапазон изменения задержек на отводах линии лежит в пределах от Т. N до Т.- N-M с шагом дискретности Т.- N. Закон измения задержки в указанном диапазоне определяется значениями коэффициентов, хранящихся в запоминающем устройстве требуемых значений задержек, и может быть выбран любым с точностью Т-гг N.

Для повьшения устойчивости работы линии в условиях сильных электромагнитных помех коммутатор 2 может быть выполнен в виде демультиплексора 1 - N, для управления которым

помимо цепи синхронизации от тактового генератора вводится дополнительная цепь, соединяющая адресные входы демультиплексора с параллельными выходами счетчика 6 номера.отводов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Таймер | 1985 |

|

SU1357939A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

| Устройство для регистрации сигналов, представленных в цифровой форме | 1976 |

|

SU659904A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Вычислительное устройство для формирования маршрута сообщения | 1982 |

|

SU1049917A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1539825A1 |

1. ПРОГРАММИРУЕМАЯ ЛИНИЯ ЗАДЕРЖКИ, содержащая оперативное запоминающее устройство, информационный вход KOTopjOro является входом устройства, а адресные входы и входу управления;которого подключены соответственно к адресным -и к первому управляющему выходам блока управления, отличающаяся тем, что, с целью расширения функциональных возможностей за счет возможности одновременного формирования N выходных сигналов, сдвинутых на заданные промежутки времени, в него введены буферные регистры, коммутатор, информационный вход которого подключен к выходу оперативного запоминающего устройства, управляюпщйк второму, управляющему выходу блока управления, а выходы соединены с входами соответствующих буферных регистров, выходы которых являются выходами устройства, а управляющие входы подключены к первому управляющему выходу блока управления. 2. Линия по п. 1, о т л и ч а ю щ а я с я тем, что блок управления содержит генератор тактовых импульгсов, подключенный выходом к счетчику номера отвода и к одним входам первого и второго элементов И, выходы которых являются соответственно первым и вторым управляющими выходами блока управления, а другие (Л объединенные их входы подключены соответственно к прямому и инверсному выходам дешифратора нулевого состояния, входы которого соединены с выходами счетчика номера отвода и с входами запоминающего устройства значений задержек, выходы которого соединены с входами.вычитателя, со другие входы которого через счетчик 00 текущего адреса записи соединены с выходом переполнения счетчика 00 номера отвода, и регистр, входы косо торого подключены к выходам вычитателя, а выходы являются адресными выходами блока управления.

Авторы

Даты

1985-11-23—Публикация

1982-10-15—Подача