(5j) УСТРОЙСТВО ГРУППОВОЙ ТАКТОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

| Устройство для выделения посылок сигналов | 1984 |

|

SU1338090A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Устройство для выбора частотных диапазонов передачи группового радиосигнала | 1982 |

|

SU1072277A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ТАКТОВОЙ И НЕСУЩЕЙ ЧАСТОТ | 1991 |

|

RU2096917C1 |

| Адаптивное дуплексное устройство для передачи и приема фазоманипулированных сигналов | 1985 |

|

SU1256238A2 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1129641A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Устройство групповой тактовой синхронизации | 1982 |

|

SU1022325A2 |

I

Изобретение относится к технике электросвязи и может быть использовано в аппаратуре цифровых систем передачи информации при приеме и обработке большого числа цифровых сйгналов.

Известно устройство групповой тактовой синхронизации, содержащее опорный генератор, коммутатор входных сигналов, коммутатор тактовых импульсов и фазовый дискриминатор Cvl.

Однако известное устройство обладает низкой помехоустойчивостью за счет того, что любые случайные фазовые рассогласования принимаемого сигнала вызывают немедленно изменение фазы тактовых импульсов.

Цель изобретения - повышение помехоустойчивости.

Указанная цель достигается тем, что в устройство групповой тактовой синхронизации, содержащее опорный генератор, коммутатор входных сигма лов, коммутатор тактовых импульсов

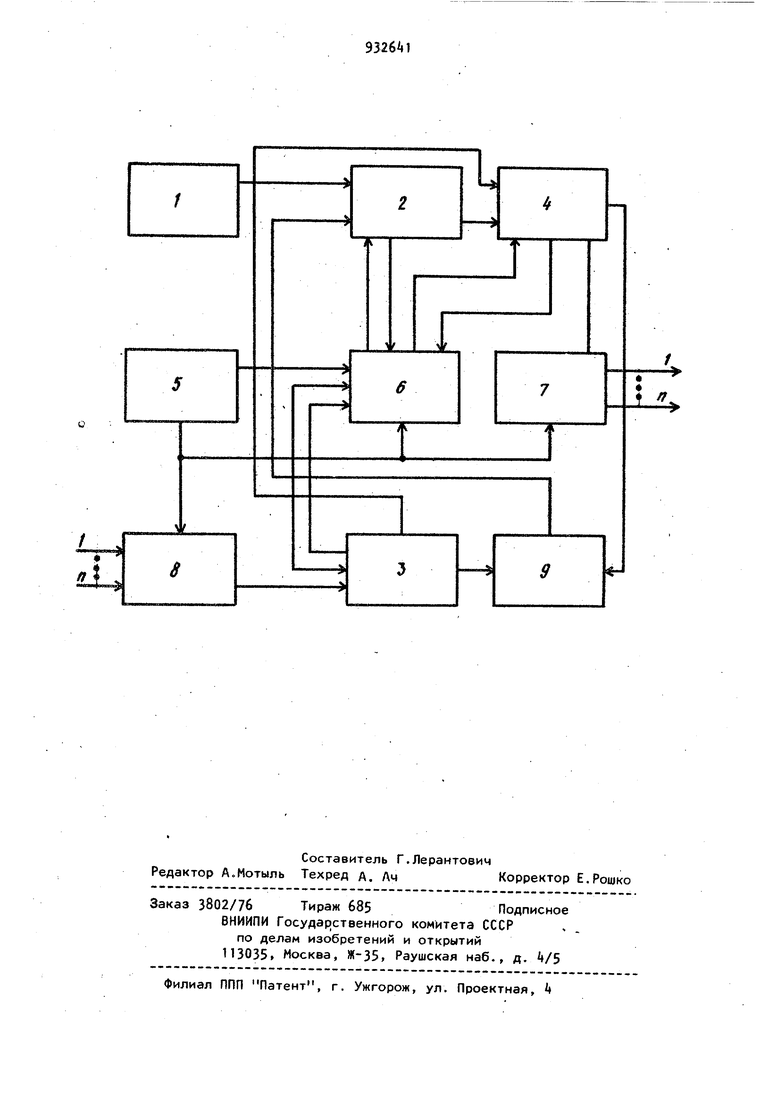

и фазовый дискриминатор, введены последовательно соединенные сумматорвычитатель, сумматор, блок оперативной памяти и блок определения знакоперемен сигналов, а также счетчик импульсов, выход которого подключен к адресным входам коммутатора входных сигналов, блока оперативной памяти и коммутатора тактовых импульсов, к входу которого подключен второй выход сумматора, третий выход которого подключен к первому входу фазового дискриминатора, к второму входу которого подключен первый выход блока определения згдакоперемен сигналов, а выход фазового дискриминатора подключен к первому входу сумматора-вычитателя, к второму входу которого, а также к входу счетчика импульсов, входу записи и считывания блока опе- ративной памяти и вторым входам сумматора и блока определения знакоперемен сигналов подключен выход опор ного генератора, при этом вторые выходы блока определения знакоперемен сигналов и cyMMaTopa-BbmntaTejifl подключены к информационным входам блока оперативной памяти, второй и третий выходы которого подключены соответственно к третьим входам сумматора-вычитателя и сумматора, а к третьему входу блока определения знакоперемен сигналов подключен выход коммутатора входных сигналов. На чертеже представлена структурная электрическая схема устройства. Устройство групповой тактовой синхронизации содержит опорный гене ратор 1, сумматор-вычитатель 2, блок 3 определения знакоперемен си|- налов, сумматор Ц, счетчик 5 импульров, блок 6 оперативной памяти, коммутатор 7 тактовых импульсов, коммутатор 8 входных сигналов, фазовый дискриминатор 9Устройство работает следующим образом. Сигнал с выхода опорного генерато ра 1 с частотой f поступает на вход счетчика 5 импульсов, который обеспе чивае-г пересчет поступающих импульсов с коэффициентом п и формирование на выходе параллельного кода, являющегося кодом номера обрабатываемого канала. Формируемый код номера канала с выхода счетчика 5 импульсов поступает на адресные входы коммутатора 8 входных сигналов, коммутатора 7 тактовых импульсов и блок 6 оператив ной памяти. При этом коммутатор 8 входных сигналов обеспечивает подачу на третий вход блока 3 определения знакоперемен сигналов i-ro канала,а коммутатор 7 тактовых импульсов выдачу синхронизирующего сигнала на выход тактовых импульсов -го канала. В блоке 6 оперативной памяти осу ществляется считывание и запись информации, относящейся к i-иу каналу. Весь процесс обработки сигнала Г-го канала в устройстве осуществляется за период частоты fp, а за интервал времени Тн j- обеспечиваетс р о поочередная обработка сигналов всех каналов. Поэтому дальнейшая работа устройства будет рассмотрена для одного канала. 3 первой половине периода частоты fe, задаваемой высоким уровнем сигна ла опорного генератора 1, поступающе го на вход записи и считывания блока оперативной памяти, осуществляется считывание с этого блока информации, относящейся к i-му каналу. При этом блок 3 определения знакоперемен сигналов, сравнивая значение входного сигнала i-ro канала, поступающего на третий вход его, со значением этого же сигнала в предыдущем цикле опроса, поступающим на первый вход с первого выхода блока оперативной памяти, определяет наличие и вид знакового перехода в канале в течение инг :тервала Тц. Если соответствующий переход имел место, то сигнал знакового перехода с первого выхода блока 3 определения знакоперемен сигналов поступает на второй вход фазового дискриминатора 9,где сравнивается с фазой сигнала тактовой частоты, поступающего на первый вход с третьего выхода сумматора k. Фазовый дискриминатор 9 имеет прямоугольную характеристику и при наличии сигнала знакового перехода формирует сигнал Опережение или 1Отставание который с выхода егопоступает на первый вход сумматора-вычитателя 2, на третий вход которого с блока 6 оперативной памяти поступает код сое- тояния сумматора-вычитателя 2 в предыдущем цикле, Сумматор-вычитатель 2 в зависимоети от значения сигнала фазового дискриминатора 9 осуществляет наращивание или уменьшение на единицу значения кода, поступающего на его третий вход, и выдачу результата на второй выход. При достижении сумматором-вычитателем 2 заданного значения L (L)y характеризующего заданный коэффициент усреднения, на первом выходе его формируется кодовый сигнал Добавления или Вычитания фазы тактового импульса i-ro канала, который поступает на первый вход сумматора, где он суммируется с кодом фазы тактовых импульсов i-ro канала в предыдущем цикле, поступающим на третий вход сумматора 4 с третьего выхода блока 6 оперативной памяти. При сигнале Добавления к предыдущему значению фазы тактовых импульсов прибавляется число 2, что соответствует сдвигу фазы на в сторону опережения, а при сигнале Вычитания предыдущее .значение кода фазы «Q изменяется, что соответствует сдвигу фазы на -тг в сторону отставания. При отсутствии указанных сигналов к значению 59 фазы тактовых импульсов прибавляется число 1, что соответствует линейному изменению фазы тактовых импульсов. Результат суммирования выдается , на первый выход сумматора k. При достижении сумматором f заданного значения К, равного коэффициенту деления частоты в устройствах с промежуточным делением частоты, на втором выхо де его формируется тактовый импульс, который через коммутатор 7 тактовых импульсов поступает на выход тактовых импульсов 1-го канала. На третьем выходе сумматора Ц формируется сигнал тактовой частоты вида меандр, который поступает на первый вход фазового дискриминатора 9. Во втором полупериоде сигнала частоты fp осуществляется запись значения входного сигнала i-ro канала с второго выхода блока 3 определения знакоперемен сигналов и обновленной информации с второго выхода сумматора- вычитателя 2 и первого выхода сумматора k в блок 6 оперативной па,мяти по тому же i-му адресу. В следующем периоде сигнала частоты fo осуществляется наращивание содержимого счетчика 5 импульсов на 1, формирование на выходе его кодовой комбинации, соответствующей (+1)-му каналу, и обработка сигнала этого канала. Для обеспечения нормальной работ ы устройства частота опорного генератора должна выбираться, исходя из соотношенияf - тактовая частота обрабатываемых сигналов. Таким образом, сумматор-вычитатель и блок оперативной памяти, образующие групповое устройство усреднения, обеспечивают усреднение сигналов фазового дискриминатора и за счет этого повышение помехоустойчивости предлагаемого устройства групг повой тактовой синхронизации. 1 Формула изобретения Устройство групповой тактовой синхронизации, содержащее опорный генератор, коммутатор входных сигналов, коммутатор тактовых импульсов и фазовый дискриминатор, отличающееся тем, что, с целью повыше;ния помехоустойчивости,.8 него введены последовательно соединенные сумма|тор-вычитатель, сумматор, блок оперативной памяти и блок определения знакоперемен сигналов, а также счетчик импульсов, выход которого подключён к адресным входам коммутатора входных сигналов, блока оперативной памяти и коммутатора тактовых импульсов.к входу которого подключен второй йыход сумматора, третий выход которого подключен к первому входу фазового дискриминатора, к второму входу которого подключен первый выход блока определения знакоперемен сигналов, а выход фазового дискриминатора подключен к первому входу сумматора-вычитателя, к второму входу которого, а также к входу счетчика импульсов, входу записи и считывания блока оперативной памяти и вторым входам сумматора и блока определения знакоперемен сигналов подключен выход опорного генератора, пр.и этом вторые выходы блока определения знакоперемен сигналов и сумматора-вычитателя под- . ключены к информационным входам блока оперативной памяти второй и третий выходы которого подключены соответственно к третьим входам сумматора-вычитателя и сумматора, а к третьему входу блока определения знакоперемен сигналов подключен выход коммутатора входных . сигналов. Источники информации, принятые во внимание при экспертизе I . 1, Авторское свидетельство СССР № , кл. Н L 7/02, 1977 (прототип).

Авторы

Даты

1982-05-30—Публикация

1980-12-31—Подача