Изобретение относится к импульсной технике и может быть использовано при построении БИС обработки и хранения информации.

Цель изобретения - повышение точ- 5 ности аналого-цифрового преобразователя.

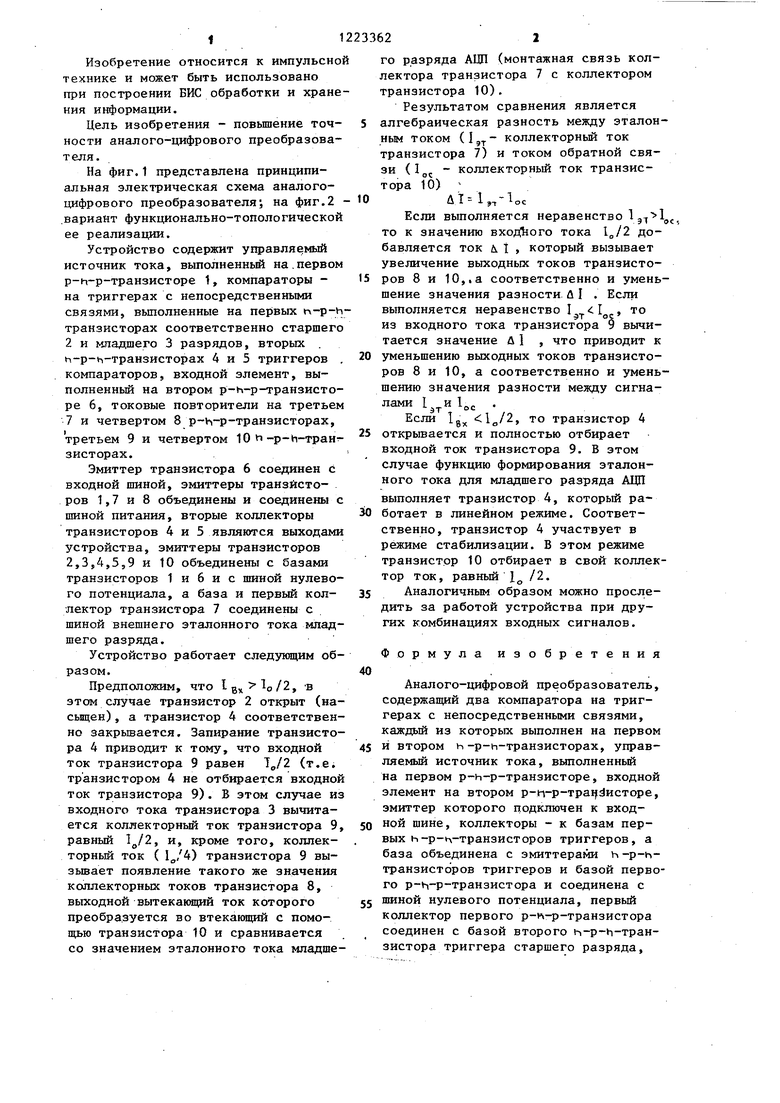

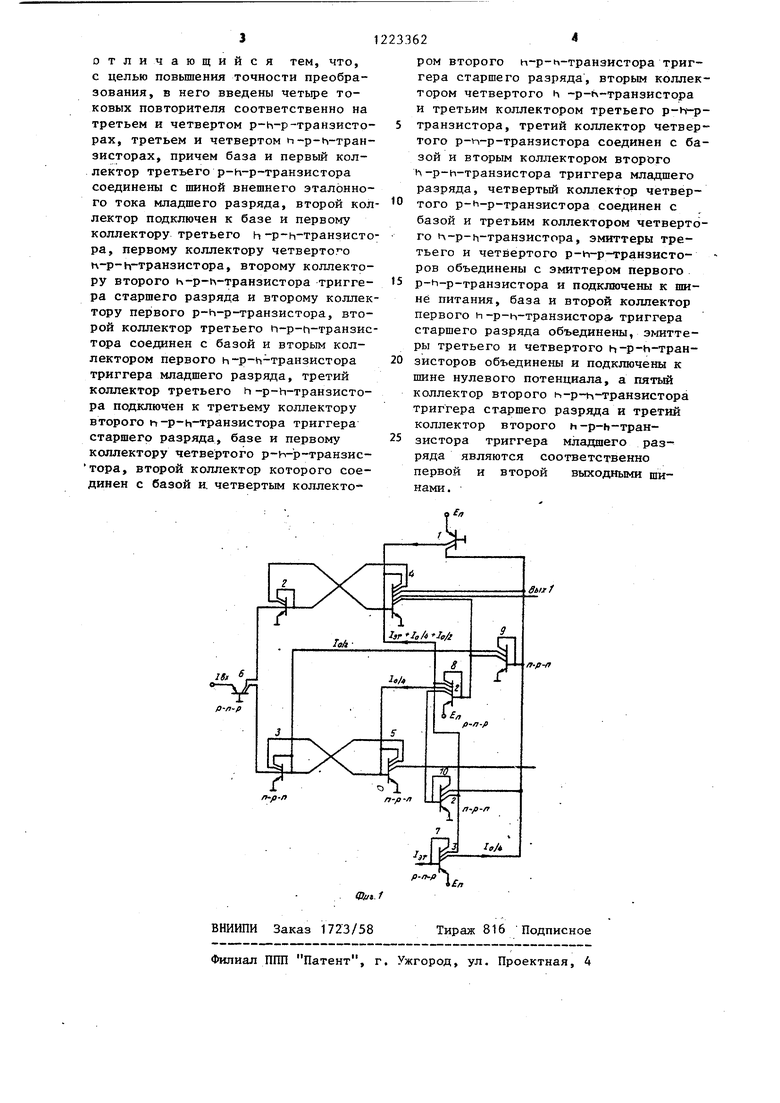

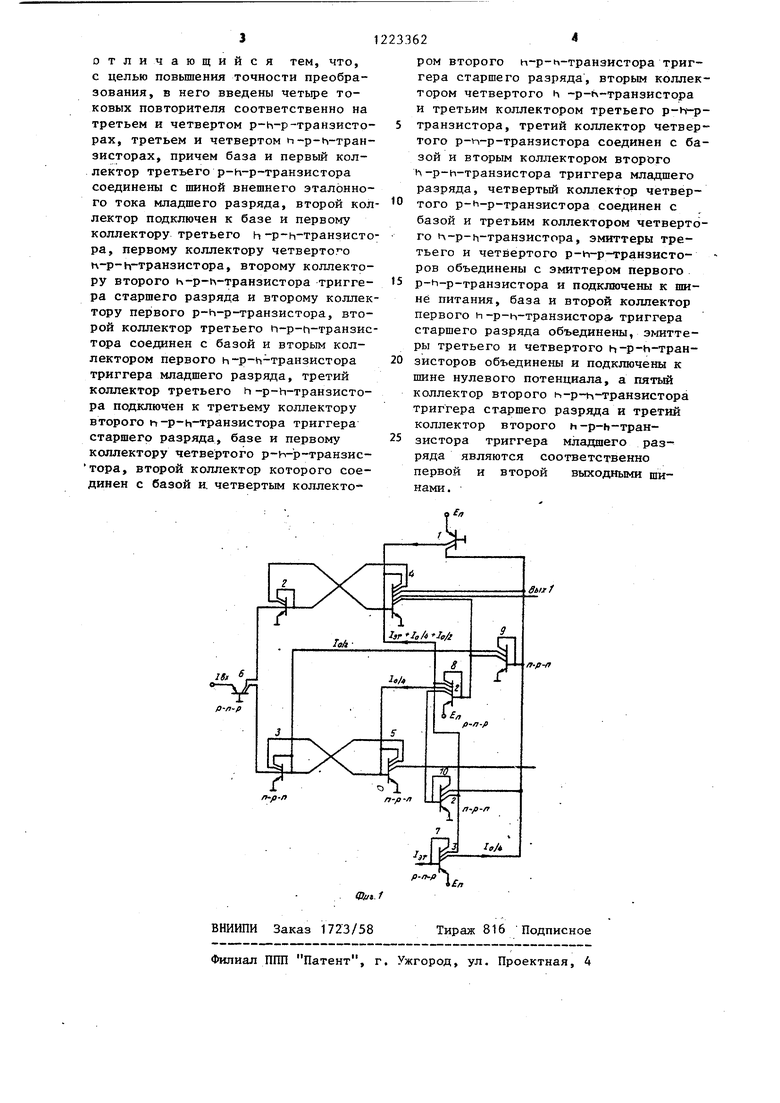

На фиг,1 представлена принципиальная электрическая схема аналого- цифрового преобразователя; на фиг.2 - О .вариант функционально-топологической ее реализации.

Устройство содержит управляемый источник тока, выполненный на.первом р-и-р-транзисторе 1, компараторы - на триггерах с непосредственными связями, вьшолненные на первых л-р-ь- транзисторах соответственно старшего 2 и младшего 3 разрядов, вторых . h-p-h-транзисторах 4 и 5 триггеров , компараторов, входной элемент, вы- полненньй на втором р-н-р-транзисторе 6, токовые повторители на третьем 7 и четвертом 8 p-h-p-транзисторах,

третьем 9 и четвертом 10 i-p-h-тран- зисторах.

Эмиттер транзистора 6 соединен с входной шиной, эмиттеры транзисторов 1,7 и 8 объединены и соединены с

12233622

го разряда АЦП (монтажная связь коллектора транзистора 7 с коллектором транзистора 10).

Результатом сравнения является алгебраическая разность между эталонным током (1эт коллекторный ток транзистора 7) и током обратной связи (Ig - коллекторный ток транзистора 10)

йЬ 1,-1ос

Если выполняется неравенство 1 l, то к значению Bxorfboro тока добавляется ток г I , который вызывает увеличение выходных токов транзисторов 8 и 10,.а соответственно и уменьшение значения разности и I . Если выполняется неравенство I 1 , то из входного тока транзистора 9 вычитается значение Д 1 , что приводит к уменьшению выходных токов транзисторов 8 и 10, а соответственно и уменьшению значения разности между сигна15

20

лами 1.,.и 1ос

Если Ig 1д/2, то транзистор 4

25 открьшается и полностью отбирает входной ток транзистора 9. В этом случае функцию формирования эталонного тока для младшего разряда АЦП

выполняет транзистор 4, который ра- 310 ботает в линейном режиме. Соответственно, транзистор 4 участвует в режиме стабилизации. В этом режиме транзистор 10 отбирает в свой коллектор ток, равный 1 /2.

шиной питания, вторые коллекторы транзисторов 4 и 5 являются выходами устройства, эмиттеры транзисторов 2,3,4,5,9 и 10 объединены с базами транзисторов 1 и 6 и с шиной нулевого потенциала, а база и первый коллектор транзистора 7 соединены с шиной внешнего эталонного тока младшего разряда.

Устройство работает следунщим образом.

Предположим, что , в этом случае транзистор 2 открыт (насыщен) , а транзистор 4 соответственно закрьшается. Запирание транзистора 4 приводит к тому, что входной ток транзистора 9 равен Т„/2 (т.е; транзистором 4 не отбирается входной ток транзистора 9). В этом случае из входного тока транзистсч)а 3 вычитается коллекторный ток транзистора 9, равный I(j/2, и, кроме того, коллекторный ток ( 1о/4) транзистора 9 вы- зьюает появление такого же значения коллекторных токов транзистора 8, выходной вытекакщий ток которого преобразуется во втекающий с помощью транзистора 10 и сравнивается со значением эталонного тока младшелами 1.,.и 1ос

Если Ig 1д/2, то транзистор 4

открьшается и полностью отбирает входной ток транзистора 9. В этом случае функцию формирования эталонного тока для младшего разряда АЦП

выполняет транзистор 4, который ра- ботает в линейном режиме. Соответственно, транзистор 4 участвует в режиме стабилизации. В этом режиме транзистор 10 отбирает в свой коллектор ток, равный 1 /2.

Аналогичным образом можно проследить за работой устройства при других комбинациях входных сигналов.

Формула изобретения

Аналого-цифровой преобразователь, содержащий два компаратора на триггерах с непосредственными связями, каждый из которых выполнен на первом

и втором h-p-h-транзисторах, управляемый источник тока, выполненный на первом р-ь-р-транзисторе, входной элемент на втором p-и-p-тpa fdиcтope, эмиттер которого подключен к входной шине, коллекторы - к базам первых ь-р-ц-транзисторов триггеров, а база объединена с эмиттерами ь-p-h- транзисторов триггеров и базой первого p-h-p-транзистора и соединена с

шиной нулевого потенциала, первый коллектор первого р-п-р-транзистора соединен с базой второго bi-p-h-тран- зистора триггера старшего разряда.

отличающийся тем, что, с целью повьшения точности преобразования, в него введены четыре токовых повторителя соответственно на третьем и четвертом р-и-р-транзисторах, третьем и четвертом и-р- -тран- зисторах, причем база и первый коллектор третьего p-h-p-транзистора соединены с шиной внешнего эталонного тока младшего разряда, второй коллектор подключен к базе и первому коллектору третьего н-р-н-транзисто ра, первому коллектору четвертого H-p-h-транзистора, второму коллектору второго h-p-h-транзистора триггера старшего разряда и второму коллектору первого p-h-p-транзистора, второй коллектор третьего h-p-h-транзис тора соединен с базой и вторым коллектором первого h-p-h-транзистора триггера младшего разряда, третий коллектор третьего h-р-н-транзисто- ра подключен к третьему коллектору второго п-р-h-транзистора триггера старшего разряда, базе и первому коллектору четвертого р-ь-р-транзис- тора, второй коллектор которого соединен с базой и. четвертым коллекто

ром второго и-р- 1-транзистора триггера старшего разряда, вторым коллектором четвертого h -р-к-транзистора и третьим коллектором третьего р-к-р- транзистора, третий коллектор четвертого р- л-р-транзистора соединен с базой и вторым коллектором второго h-p-h-транзистора триггера младшего разряда, четвертый коллектор четвертого p-h-p-транзистора соединен с базой и третьим коллектором четвертого л-p-h-транзистора, эмиттеры третьего и четвертого p-h-p-транзисто- ров объединены с эмиттером первого p-h-p-транзистора и подключены к шине питания, база и второй коллектор первого h -p-h-транзистора триггера старшего разряда объединены, эмиттеры третьего и четвертого h-p-h-тран- 0 зисторов объединены и подключены к шине нулевого потенциала, а пятый коллектор второго ь-р-ь-транзистора триггера старшего разряда и третий коллектор второго н-р-н-тран- зистора триггера младшего раз- ряда являются соответственно первой и второй выходными шинами.

5

5

п-р-п

Stiff

n-f-fi

р-п-р

(Pfit. f

ВНИИПЙ Заказ 1723/58 Тираж 816 Подписное Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Инжекционный сумматор | 1988 |

|

SU1539992A1 |

| Двухразрядный двоичный умножитель инжекционного типа | 1986 |

|

SU1335984A1 |

| Входной транслятор И @ Л-типа | 1984 |

|

SU1202049A1 |

| Мостовой триггер | 1980 |

|

SU1012426A1 |

| Интегральный инжекционный логический элемент | 1982 |

|

SU1046933A1 |

| Двухразрядный двоичный умножитель инжекционного типа | 1983 |

|

SU1150626A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

| Параллельный аналого-цифровой преобразователь | 1982 |

|

SU1019623A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU902243A1 |

| Высокочастотный компаратор | 1986 |

|

SU1394423A1 |

Изобретение относится к импульсной технике и может быть использова АйгГ но при построении БИС обработки и хранения информации. Изобретение позволяет повысить точность аналого- цифрового преобразователя за счет введения четырех токовых повторителей на р-и-р-транзисторах 7 и 8 и h-p-h-транзисторах 9 и 10 в устройство, содержащее управляемый источник тока, выполненный на р-и-р-транзисто- ре 1, компараторы на триггерах с непосредственными связями , выполненных на h-p-h-транзисторах соответственно старшего 2 и младшего 3 разрядов, на п-р-к-транзисторах 4 и 5, входной элемент, выполненный на р-ъ-р-транзисторе 6. 2 ил. (Л IND to оо 00 Од N9

| Аналого-цифровой преобразователь | 1976 |

|

SU600729A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Интегральный преобразовательуРОВНЕй TOKA B дВОичНый КОд | 1979 |

|

SU809558A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-07—Публикация

1983-12-27—Подача