Изобретение относится к импульсной технике и может быть ис.пользовано для обеспечения согласования по логическим уровням элементов ТТЛ, ДТЛ с элементами ил-типа.

Цель изобретения - повышение помехозащищенности устройства путем обеспечения подавления помех большой длительности малой амплитуды и кратковременных помех большой амплитуды.

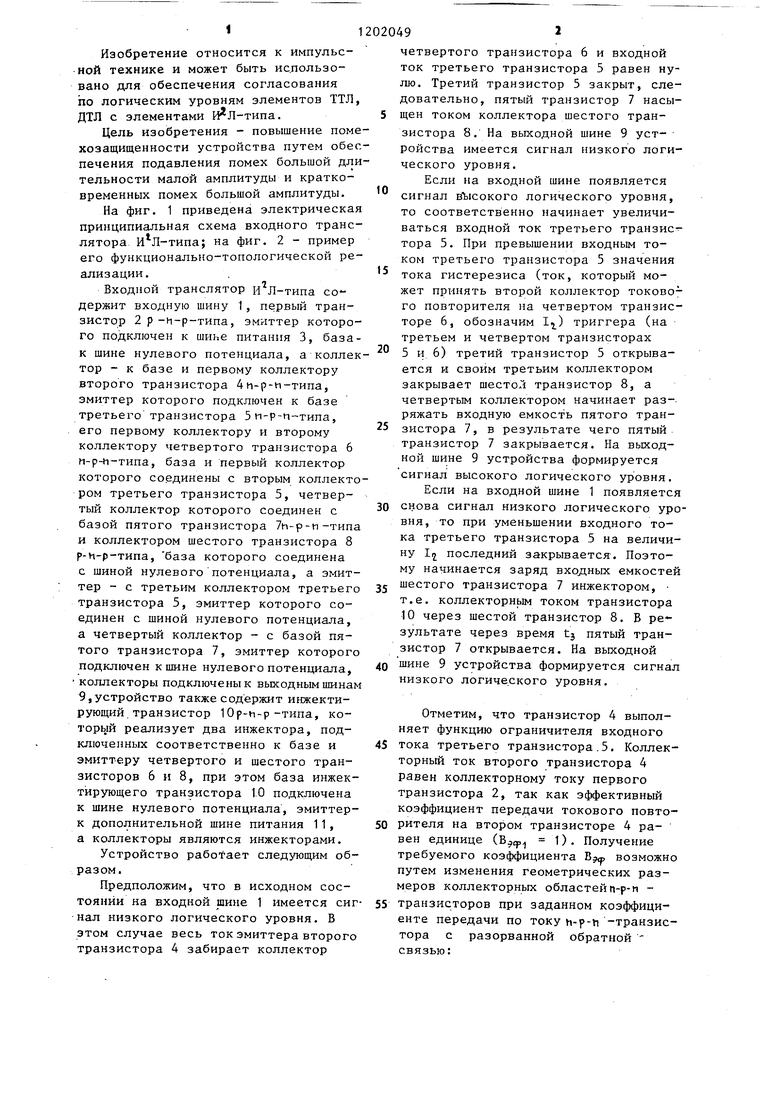

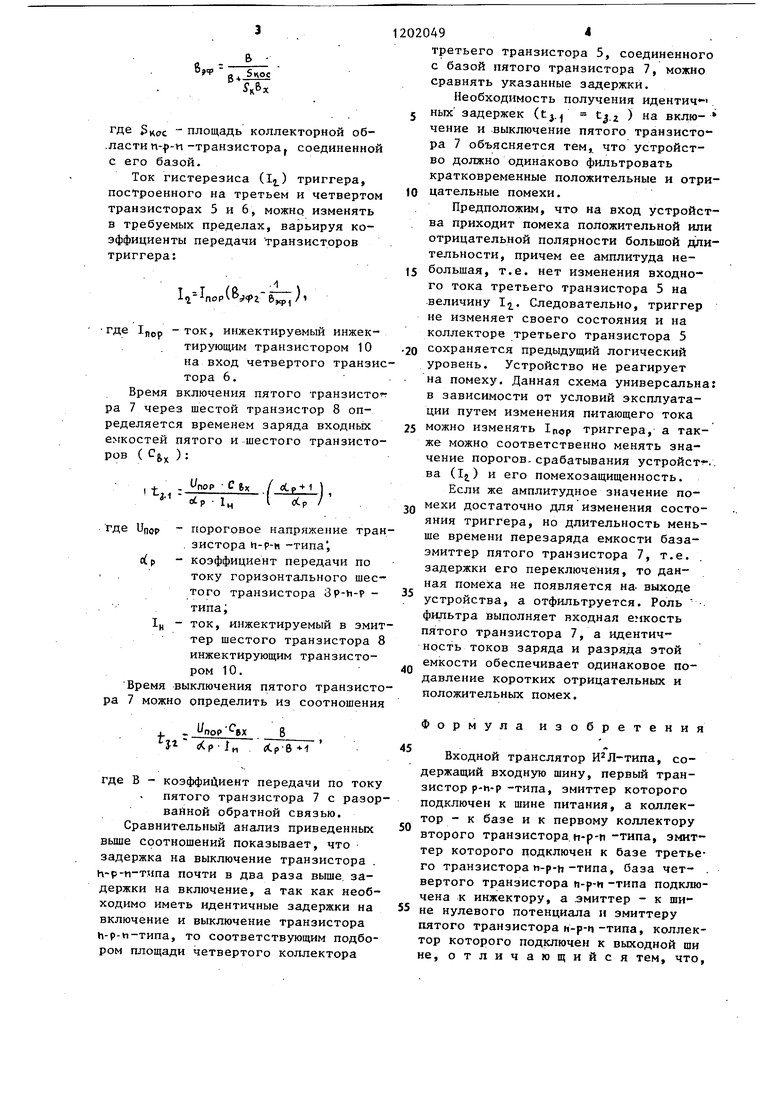

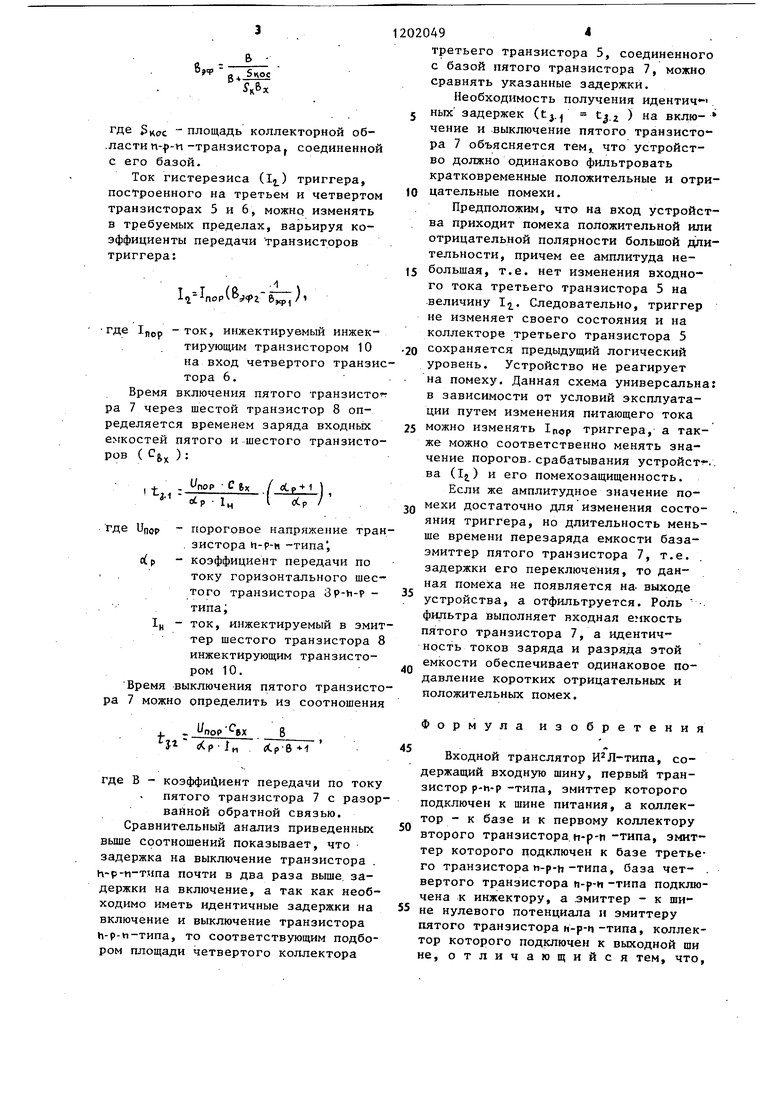

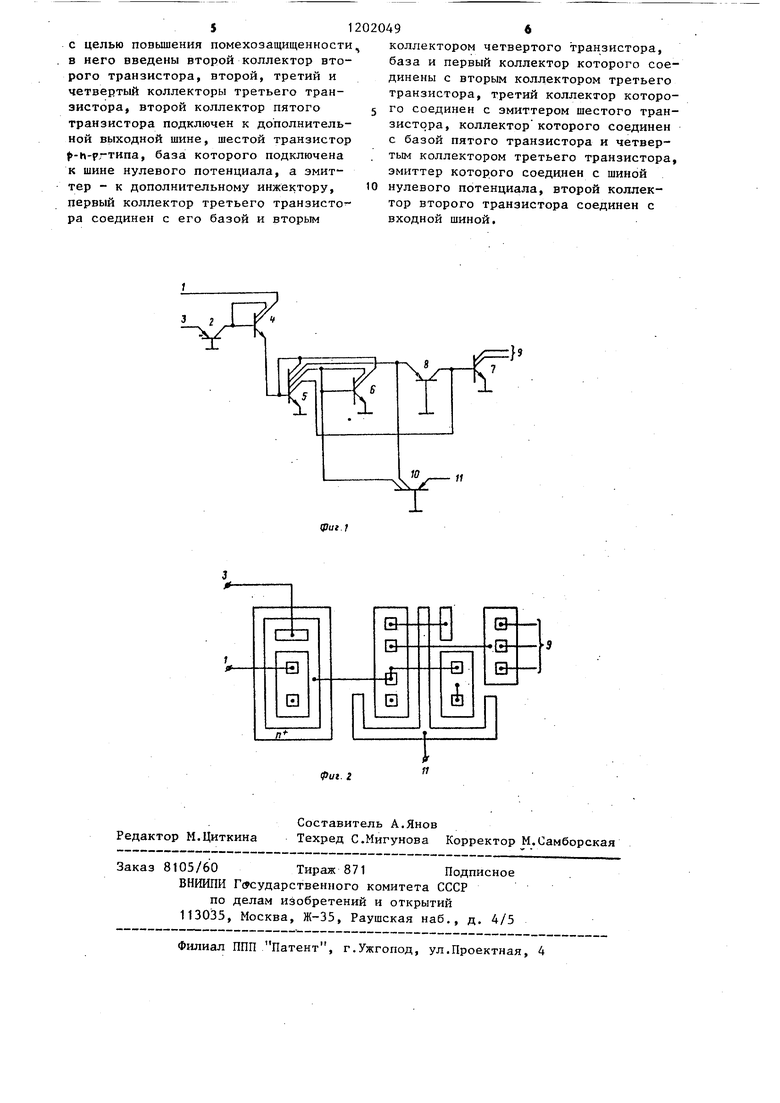

На фиг. 1 приведена электрическая принципиальная схема входного транслятора И Л-типа; на фиг. 2 - пример его функционально-топологической реализации.

Входной транслятор ил-типа содержит входную шину 1, первый транзистор 2 р-и-р-типа, эмиттер которого подключен к шине питания 3, базак шине нулевого потенциала, а коллектор - к базе и первому коллектору второго транзистора 4и-р-и-типа, эмиттер которого подключен к базе третьего транзистора 5 п-р-п-типа, его первому коллектору и второму коллектору четвертого транзистора 6 м-р- 1-типа, база и первый коллектор которого соединены с вторым коллектором третьего транзистора 5, четвертый коллектор которого соединен с базой пятого транзистора 7и-р-п-типа и коллектором шестого транзистора 8 р-н-р-типа, база которого соединена с шиной нулевогопотенциала, а эмиттер - с третьим коллектором третьего транзистора 5, эмиттер которого соединен с шиной нулевого потенциала, а четвертый коллектор - с базой пятого транзистора 7, эмиттер которого подключен к шине нулевого потенциала, коллекторы подключены к выходным шинам 9,устройство также содержит инжектирующий, транзистор 10р-п-р-типа, который реализует два инжектора, подключенных соответственно к базе и эмиттеру четвертого и шестого транзисторов 6 и 8, при этом база инжектирующего транзистора 10 подключена к шине нулевого потенциала, эмиттерк дополнительной шине питания 11 , а коллекторы являются инжекторами.

Устройство работает следующим образом.

Предположим, что в исходном состоянии на входной шине 1 имеется сигнал низкого логического уровня. В этом случае весь ток эмиттера второго транзистора 4 забирает коллектор

четвертого транзистора 6 и входной ток третьего транзистора 5 равен нулю. Третий транзистор 5 закрыт, следовательно, пятый транзистор 7 насыщен током коллектора шестого транзистора 8. На выходной шине 9 устройства имеется сигнал низкого логического уровня.

Если на входной шине появляется сигнал BljicoKoro логического уровня, то соответственно начинает увеличиваться входной ток третьего транзис тора 5. При превышении входным током третьего транзистора 5 значения

тока гистерезиса (ток, который может принять второй коллектор токового повторителя на четвертом транзисторе 6, обозначим 1) триггера (на третьем и четвертом транзисторах

5 и 6) третий транзистор 5 открывается и своим третьим коллектором закрывает шесто- транзистор 8, а четвертым коллектором начинает раз-, ряжать входную емкость пятого транзистора 7, в результате чего пятый транзистор 7 закрывается. На выходной шине 9 устройства формируется сигнал высокого логического уровня. Если на входной шине 1 появляется

снова сигнал низкого логического уровня, то при уменьшении входного тока третьего транзистора 5 на величину Ij последний закрывается. Поэтому начинается заряд входных емкостей

шестого транзистора 7 инжектором, т.е. коллекторнь1м током транзистора 10 через шестой транзистор 8. Б результате через время tj пятый транзистор 7 открывается. На выходной

шине 9 устройства формируется сигнал низкого логического уровня.

Отметим, что транзистор 4 выполняет функцию ограничителя входного

тока третьего транзистора.5. Коллекторный ток второго транзистора 4 равен коллекторному току первого транзистора 2, так как эффективный коэффициент передачи токового повторителя на втором транзисторе 4 равен единице (В, 1). Получение требуемого коэффициента возможно путем изменения геометрических размеров коллекторных областей п-р-п транзисторов при заданном коэффициенте передачи по току h-p-n -транзистора с разорванной обратной связью: где Зксс площадь коллекторной об.ластип-f-n -транзистора f соединенной с его базой. Ток гистерезиса (I,) триггера, построенного на третьем и четвертом транзисторах 5 и 6, можно изменять в требуемых пределах, варьируя коэффициенты передачи транзисторов триггера: () где 1„ор -ток, инжектируемый инжектирующим транзистором 10 на вход четвертого транзи тора 6. Время включения пятого транзисто ра 7 через шестой транзистор 8 определяется временем заряда входных емкостей пятого и шестого транзисто ров ( Cf ) ; , , ,( , dip 1„ ( оСр / где Upop -пороговое напряжение тра . зистора п-р-н -типа, -коэффициент передачи по току горизонтального ше того транзистора типа; ток, инжектируемый в эм тер шестого транзистора инжектирующим транзисто ром 10. Время выключения пятого транзис 7 можно определить из соотношен

t/nrto ex

в

- ПОР

р-1„ . Лр-в+1

где В - коэффициент передачи по току пятого транзистора 7 с разорванной обратной связью. Сравнительный анализ приведенных Bbmie соотношений показывает, что задержка на выключение транзистора . и-р-м-тяпа почти в два раза выше, задержки на включение, а так как необходимо иметь идентичные задержки на включение и выключение транзистора h-p-tt-типа, то соответствующим подбором площади четвертого коллектора

Формула изобретения

Входной транслятор И Л-типа, содержащий входную шину, первый транзистор р-п-р -типа, эмиттер которого подключен к шине питания, а коллектор - к базе и к первому коллектору второго транзистора h-p-ti-типа, эмиттер которого подключен к базе третьего транзистора ti-p-h-типа, база чет- . вертого транзистора п-р-и -типа подключена к инжектору, а .эмиттер - к шине нулевого потенциала и эмиттеру пятого транзистора и-р-п-типа, коллектор которого подключен к выходной ши не, отличающийся тем, что. 49 третьего транзистора 5, соединенного с базой пятого транзистора 7, можно сравнять указанные задержки. Необходимость получения идентич -. ньгх задержек (t. tj.j ) на вклю- чение и выключение пятого транзистора 7 объясняется тем, что устройство должно одинаково фильтровать кратковременные положительные и отридательные помехи. Предположим, что на вход устройства приходит помеха положительной или отрицательной полярности большой длительности, причем ее амплитуда небольшая, т.е. нет изменения входного тока третьего транзистора 5 на величину Ij. Следовательно, триггер не изменяет своего состояния и на коллекторе третьего транзистора 5 сохраняется предыдущий логический уровень. Устройство не реагирует на помеху. Данная схема универсальна: в зависимости от условий эксплуатации путем изменения питающего тока можно изменять 1цор триггера, а также можно соответственно менять значение порогов-срабатывания устройств., ва (Ij) и его помехозащищенность. Если же амплитудное значение помехи достаточно для изменения состояния триггера, но длительность меньше времени перезаряда емкости базаэмиттер пятого транзистора 7, т.е. задержки его переключения, то данная помеха не появляется на- выходе устройства, а отфильтруется. Роль фильтра выполняет входная емкость пятого транзистора 7, а идентичность токов заряда и разряда этой емкости обеспечивает одинаковое подавление коротких отрицательных и положительных помех.

51

с целью повьииения помехозащищенности в него введены второй коллектор второго транзистора, второй, третий и четвертый коллекторы третьего транзистора, второй коллектор пятого транзистора подключен к дополнительной выходной шине, шестой транзистор -h-p-типа, база которого подключена к шине нулевого потенциала, а эмиттер - к дополнительному инжектору, первый коллектор третьего транзисто ра соединен с его базой и вторым

2020496

коллектором четвертого транзистора, база и первый коллектор которого соединены с вторым коллектором третьего транзистора, третий коллектор которого соединен с змиттером шестого транзистора, коллекторкоторого соединен с базой пятого транзистора и четвертьм коллектором третьего транзистора, эмиттер которого соединен с шиной 10 нулевого потенциала, второй коллектор второго транзистора соединен с входной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Тактируемый @ -триггер @ -типа | 1985 |

|

SU1275738A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Тактируемый JK-триггер И @ Л-типа | 1987 |

|

SU1422367A1 |

| Буферный логический элемент и @ л типа | 1981 |

|

SU980289A1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

| Многоуровневая ячейка памяти | 1980 |

|

SU1067534A1 |

| НЕСИММЕТРИЧНЫЙ ТРИГГЕР | 2020 |

|

RU2743452C1 |

| Каскад двоичного деления частоты | 1979 |

|

SU815870A1 |

| Инжекционный динамический элемент | 1980 |

|

SU953731A1 |

| Регистр сдвига | 1982 |

|

SU1136217A1 |

Изобретение относитсяк области импульсной техники и можетиспользоваться для согласования пологическим уровням элементов ТТЛ,ДТЛ с л элементами И Л-типа. Цель изобретения - повышение помехозащищенности устройства путем подавления помех большой длительности малой амплитуды и кратковременных помех больщой амплитуды - достигается введением в устройство двух р-п-р-транзисторов и организацией новых связей. Входной транслятор И Л-типа предназначен для согласования по логическому уровню микросхем ТТЛ, ДТЛ и т.п. с БИС И Л-типа. Устройство имеет гистерезисную входную характеристику и не содержит резисторов. Функцию фильтра выполняет входная емкость пятого транзистора. Идентичность токов заряда и разряда этой емкости с обеспечивает одинаковое подавление (Л коротких отрицательных и положительных помех. Принципиальная схема входного транслятора И Л-типа и пример его функционально-топологической реализации приводятся в описании изобретения. 2 ил. N9 О Ю о и со

| Алексеенко А.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| М.: Радио и связь, 1982, с | |||

| Экономайзер | 0 |

|

SU94A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аваев Н.А | |||

| и др | |||

| большие интегральные схемы с инжекционным питанием | |||

| М.: Сов | |||

| радио, 1977, с | |||

| Индукционная катушка | 1920 |

|

SU187A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-12-30—Публикация

1984-08-20—Подача