Изобретение о гносится к электросвязи и может быть использовано для синхронизации систем передачи данных использующих псевдослучайные последовательности

Целью изобретения является уменьшение времени в.хоядения в синхронизм и повьшение надежности.

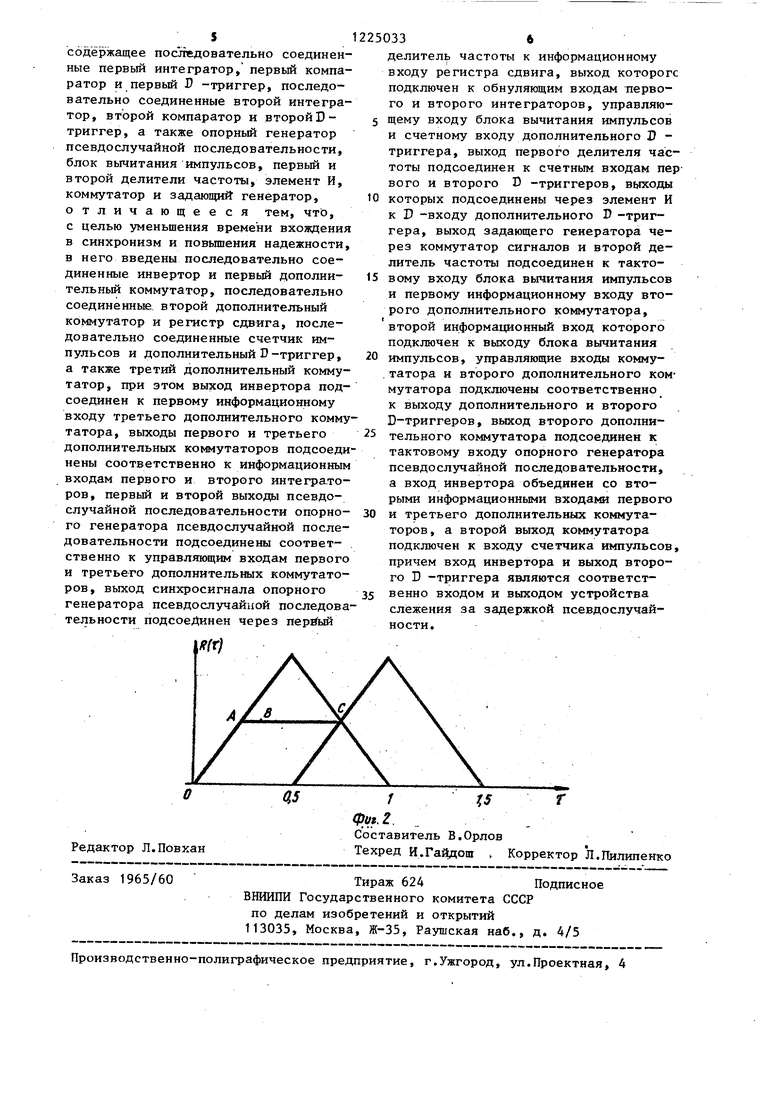

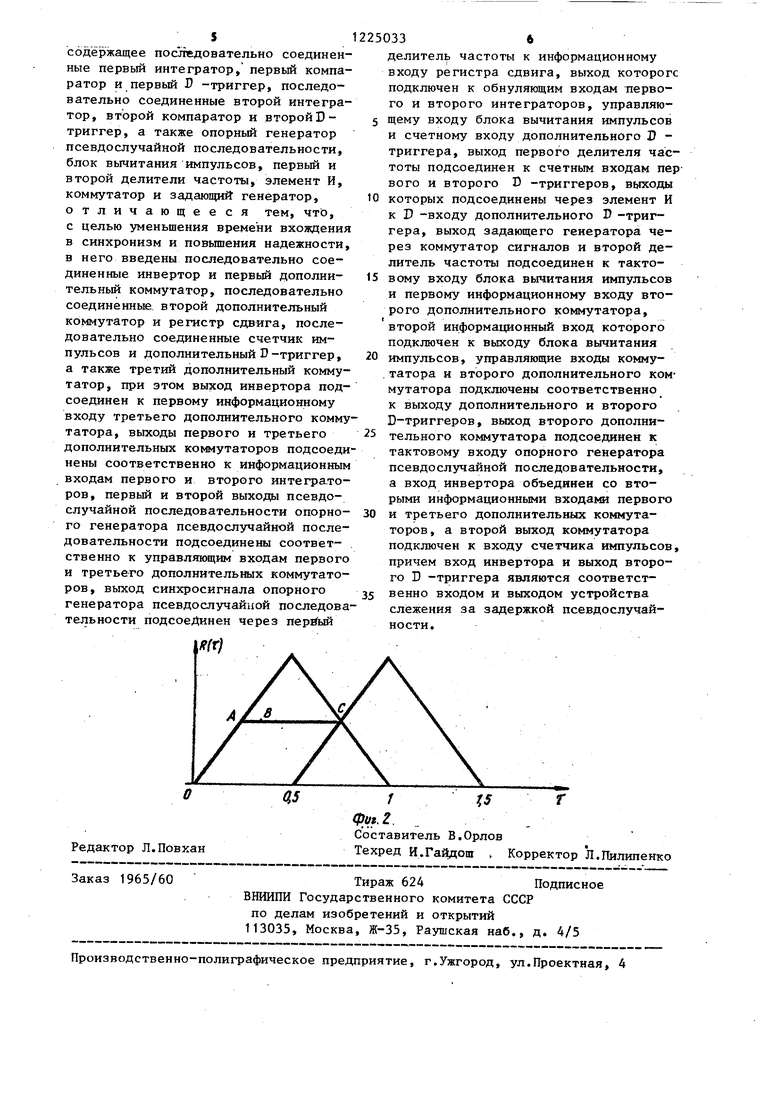

На фиг. 1 представлена структурная электрическая схема устройства слеже- ния за задержкой псевдослучайной послед овательности на фиг. 2 - дискриминационная характеристика устройства слежения за задержкой псевдослучайной последовательности

Устройство слежения за задержкой псевдослучайной последовательности содержит инвертор 1, первый дополнительный коммутатор 2, третий дополнительный коммутатор 3, опорный гене- ратор 4 псевдослучайной последова-. тельности, первый интегратор 5, второй интегратор 6, регистр 7 сдвига, первьй компаратор 8, второй компаратор 9, первьй делитель 10 частоты, первый D -триггер 11, второй D -триггер 12, элемент И 13, дополнительный Б-триггер 14, коммутатор 15, задаю- : щий генератор 16, второй делитель 17 частоты, блок 18 вьиитания импульсов,- второй дополнительный коммутатор 19, счетчик 20 импульсов

Устройство слежения за задержкой псевдослучайной последовательности работает следзпсщим образом.

Входной сигнал, содержащий псевдослучайную последовательность (М- последовательность), поступает () на вход инвертора 1 и на вторые информационные входы первого и третьего дополнительных коммутаторов 2 и Зо На первые информационные входы последних поступает инверсия входного сигнала с выхода инвертора 1„ На управляющий вход первого дополнительного коммутатора 2 с первого выхода псевдослучайной последовательности опорного генератора 4 поступает опорная М-последователь- ность, а на управляющий вход третье- го дополнительного коммутатора 3 со второго выхода псевдослучайной последовательности опбрного генератора 4 подается М-последовательность,

дающего генератора 16 к входу второго делителя 17 Второй делитель 17 с коэффициентом деления не ниже 2 формирует на выходе тактовые импульсы (ТИ) длитеа1ьностью, равной периоду импульсной последовательности, поступающей на его вход, и периодом, меньшим, чем период ТИ входной М-пос ледовательности. Сформирован таким образом ТИ поступают на второй вход блока 18 вычитания импульсов, который в момент присутствия сигнала с выхода регистра 7 на управляющем входе не пропускает на выход ни один импульс ТИ. Модифицированные так

образом ТИ и та с выхода второго делителя 17 поступают соответственно на второй и первый информационный входы второго дополнительного коммутатора 19, на управляющий вход кото40

45

сдвинутая относительно последователь- 55 рого поступает сигнал с выхода втоности на первом выходе псевдослучайной последовательности на один такт. В зависимости от полярности сигнала

на управляющих входах первый и третий дополнительные коммутаторы 2 и 3 подключают к своим выходам прямой или инверсный входной сигнал. Первый и второй интеграторы 5 и 6 накапливают сигнал с выхода первого и третьего дополнительных коммутаторов 2 и 3. .Накопление заканчивается с приходом / на обнуляющий вход первого и второго

интеграторов регистра 7.

5 и 6 сигнала с выхода

В момент, предшествующий обнулению первого и второго интеграторов 5 и 6 по сигналу с выхода первого делителя 10, состояние выхода первого и второго компараторов 8 и 9 записывается соответственно в первый и второй D-триггеры 11 и 12„ Наличие 1 на выходе первого D -триггера 11 (второго 3) -триггера 12) означает, что накопленный в ,первом интеграторе 5 (втором интеграторе 6) сигнал превысил порог, заданный первым компаратором 8 (вторым компаратором 9)(, В случае, когда первый и второй 5-триггеры 11 и 12 находятся в нулевом состоянии, на выходе элемента И 13 формируется О и этот сигнал с выхода элемента И 13 по сигналу с выхода регистра 7 записьшается в дополнительный 3 -триггер 14, а нулевой потенциал с его выхода, поступив на управляющий вход коммутатора 15, обеспечивает подключение выхода задающего генератора 16 к входу второго делителя 17 Второй делитель 17 с коэффициентом деления не ниже 2 формирует на выходе тактовые импульсы (ТИ) длитеа1ьностью, равной периоду импульсной последовательности, поступающей на его вход, и периодом, меньшим, чем период ТИ входной М-пос ледовательности. Сформирован таким образом ТИ поступают на второй вход блока 18 вычитания импульсов, который в момент присутствия сигнала с выхода регистра 7 на управляющем входе не пропускает на выход ни один импульс ТИ. Модифицированные так

образом ТИ и та с выхода второго делителя 17 поступают соответственно на второй и первый информационный входы второго дополнительного коммутатора 19, на управляющий вход кото

рого поступает сигнал с выхода второго и -триггера 12. Если это потенциал О (нет синхронизации), то на тактовый вход опорного генератоpa 4 поступают модифицированные ТЕГ, что заставляет опорные М-последова- тельности сдвигаться относительно входной М-последовательности на оди такт после каяздого периода накопления. Опорный генератор 4 формирует на выходе синхросигнала синхроимпульсы (СИ) длительностью, равной периоду ТИ, и периодом, равным периоду М-последовательности. Импульсная последовательность СИ поступает на первый делитель 10, который и определяет период накопления „ :

т -к Cfc ICM ч

где Т 5ц - период СИ,

К - коэффициент деления перг вого делителя 10.

В простейшем случае К 1, и накопление в первом и втором интеграторах 5 и 6 происходит один период М-последовательности. Импульсы с выхода первого делителя 10 длительностью СИ поступают на информационный вход регистра 7, на вход управления сдвигом которого поступают ТИ, а на выходе регистра 7 формируются импульсы, с длительностью СИ, но сдвинутые на такт относительно импульсов, пос- тупаюпщх на вход регистра 7.

Если в конце накопления срабатывает второй компаратор 9 и второй D-триггер 12 переходит в единичное состояние, это означает, что устройство слежения за задержкой псевдослучайной последовательности засинх- ронизировалось по задержке, а на выходе второго О -триггера 12 формируется сигнал Признак захвата, В случае, когда второй D-триггер 12 перешел в единичное состояние, сигнал с его выхода переключает второй дополнительный коммутатор 19, и на вход опорного генератора 4 начинают поступать ТИ без модификации. Таким образом, опорный генератор 4 продолжает работать синхронно с входной последовательностью, а устройство слежения за задержкой псевдослучайной последовательности переходит в режим слежения. Входу в синхронизм соответствует точка А на дискриминационной характеристике (фиг. 2).

В режиме слежения из-за вышеописанной разницы в тактовых частотах опорная М-последовательность .продолжает медленно сдвигаться по фазе относительно входной М-последовательности: перемещение на дискриминацион

2250334

ной характеристике RCC) (фиг. 2) по прямой от точки А к точке С. В результате этого сдвига в момент, когда разность фаз достигает значения, 5 соответствующего точке С, срабатьгеа- ет второй компаратор 8, в результате чего D -триггер 12 перебрасывается в единичное состояние, сигнал 1 с его выхода поступает на первый

10 вход элемента И 13, на втором входе которого присутствует сигнал 1 с выхода второго Г -триггера 12, что вызывает формирование на выходе элемента И 13 единичного потенциала,

15 который и записывается в дополнительный D -триггер 14о Единичный потенциал с выхода дополнительного С -триг- гера 14 переключает коммутатор 15 так, что импульсы с задающего гене20 ратора 16 поступают на счетчик 20 до тех пор, пока на его выходе не появится сигнал, который возвращает в нулевое состояние дополнительный -триггер 14, что в свою очередь

25 вызывает перекдлочение коммутатора 15 в первоначальное состояние, когда импульсы от генератора 16 поступают на вход второго делителя 17. На дискриминационной характеристике f(tl

3Q (фиг. 2) происходит возврат фазы из точки С в точку В, когда появляется сигнал на выходе счетчика 20. В устано|ив1пемся режиме устройство слежения за задержкой псевдослучайной последовательности работает на

35

40

45

участке ВС дискриминационной характеристики Я{ г)(фиг, 2), величина которого задается коэффш;иентом пересчета счетчика 20. Если в результате сильной помехи или кратковременного отключения питания синхронизация будет утеряна, то устройство слежения за задержкой псевдослучайной последовательности вновь переходит в режим поиска.

Анализ функционирования предложенного устройства слежения за задержкой псевдослучайной последовательности показал, что оно обеспе- чивает уменьшение (до 10 раз) времени вхождения в синхронизм и более высокую надежность работы по сравнению с известным.

Формула изобретения

Устройство слежения за задержкой псевдослучайной последовательности,

содержащее последовательно соединенные первый интегратор, первый компаратор и первьш 1 -триггер, последовательно соединенные второй интегратор, второй компаратор и второй D- триггер, а также опорный генератор псевдослучайной последовательности, блок вычитания импульсов, первьш и второй делители частоты, элемент И, коммутатор и задающий генератор, отличающееся тем, чтЬ, с целью уменьшения времени вхождения в синхронизм и повышения надежности, в него введены последовательно соединенные инвертор и первьш дополнительный коммутатор, последовательно соединенньш второй дополнительный коммутатор и регистр сдвига, последовательно соединенные счетчик импульсов и дополнительный Г-триггер, а также третий дополнительный коммутатор, при этом выход инвертора подсоединен к первому информационному входу третьего дополнительного коммутатора, выходы первого и третьего дополнительных коммутаторов подсоединены соответственно к информационным входам первого и второго интеграторов, первый и второй выходы псевдослучайной последовательности опорного генератора псевдослучайной последовательности подсоединены соответственно к управлякнцим входам первого и третьего дополнителышх коммутаторов, выход синхросигнала опорного генератора псевдослучайной последовательности подсоединен через первый

2250336

делитель частоты к информационному входу регистра сдвига, выход которого подключен к обнуляющим входам первого и второго интеграторов, управляю- 5 щему входу блока вычитания импульсов и счетному входу дополнительного D - триггера, выход первого делителя частоты подсоединен к счетным входам первого и второго D -триггеров, выходы 10 которых подсоединены через элемент И к D -входу дополнительного Г -триггера, выход задающего генератора через коммутатор сигналов и второй делитель частоты подсоединен к такто- 15 вому входу блока вычитания импульсов и первому информационному входу второго дополнительного коммутатора, второй информационный вход которого подключен к выходу блока вычитания 20 импульсов, управляющие входы коммутатора и второго дополнительного коммутатора подключены соответственно к выходу дополнительного и второго D-триггеров, выход второго дополнительного коммутатора подсоединен к тактовому входу опорного генератора псевдослучайной последовательности, а вход инвертора объединен со вторыми информационными входами первого 30 и третьего дополнительных коммутаторов, а второй выход коммутатора подключен к входу счетчика импульсов, причем вход инвертора и выход второго D -триггера являются соответст- 35 венно входом и выходом устройства слежения за задержкой псевдослучайности.

25

5

Редактор Л.Повхан

/ 45 f

Фо.г.

Составитель В.Орлов

Техред И.Гайдош Корректор Л.Пилипенко

Заказ 1965/60

Тираж 624Подписное

ВНШПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство слежения за задержкой псевдослучайной последовательности | 1985 |

|

SU1352664A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1981 |

|

SU1840035A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| ПРИЕМОПЕРЕДАЮЩАЯ АППАРАТУРА ШИРОКОПОЛОСНЫХ ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1979 |

|

SU1840119A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДЛЯ ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ | 1980 |

|

SU1840131A1 |

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1986 |

|

SU1394411A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1976 |

|

SU1840434A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1982 |

|

SU1840503A1 |

Изобретение относится к электросвязи. Цель изобретения - уменьшение времени вхождения в синхронизм и повьшение надежности. Устройство содержит инвертор 1, коммутаторы (К) 2, 3, 15 и 19, опорный генератор 4 псевдослучайной последовательности, интеграторы 5 и 6, регистр 7 сдвига (PC), компараторы 8 и 9, делители 10 и 17 частоты. Л) -триггеры 11, 12 и 14, элемент И 13, задающий генератор 16, блок 18 вычитания импульсов и счетчик 20 импульсов (СИ). Устройство после работы в режиме поиска переходит в режим слежения. Если в результате сильной помехи или кратковременного отключения питания синхронизация теряется, то устройство вновь переходит в режим поиска. Цель достигается введением инвертора 1,К2, Зи19, PC 7, D -триггера 14 и СИ 20о 2 ил. (Л Фт

| Цифровое устройство слежения за задержкой | 1973 |

|

SU467489A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Цифровое устройство слежения за задержкой псевдослучайной последовательности | 1983 |

|

SU1088146A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-04-15—Публикация

1984-12-19—Подача