Изобретение относится к технике электросвязи и может быть использовано для синхронизации радиотехнических систем передачи данных, использующих псевдослучайные последовательности. Известно цифровое устройство слежения за задержкой псевдослучайной последовательности, содержащее после довательно соединенные кварцевый генератор, управляющий элемент, делитель частоты, опорный генератор псев дослучайных последовательностей, оди выход которого подключен к одному из входов перемножителя, выход которого подключен к одному из управляющих входов реверсивного счетчика, выходы сложения и вычитания которого подключены к другим входам управляющего элемента, а также после довательно соединенные сумматор по модулю два и элемент И, к другому входу которого подключен выход кварцевого генератора, а выход элемента И подключен к счетному входу реверсивного счетчика ll . . „ Недостатком известного цифрового устройства слежения за задержкой псевдослучайной последовательности является низкая помехозащищенность. Наиболее близким по технической сущности к изобретению является цифровое устройство слежения за задержкой псевдослучайной последовательности, содержащее последователь но соединенные задающий генератор, блок добавления-вычитания импульсов, делитель частоты и опорный генератор псевдослучайных последовательностей последовательно соединенные сумматор по модулю два и элемент И, последова тельно соединенные перемножитель и реверсивный счетчик, счетный вход которого подключен к выходу элемента И, второй вход которого подсоединен к выходу задающего генератора, первь выход опорного генератора псевдослучайных последовательностей подсоединен к объединенньм входам перемножителя и сумматора по модулю два, второй вход которого подключен к второму выходу опорного генератора псевдо случайных последовательностей, при эт второй вход перемножйтеля является входом цифрового устройства слежения за задержкой псевдослучайной последовательности, выход перемножителя через элемент НЕ подсоединен к второму управляющему входу реверсивного счетчика, выходы сложения и вычитания которого подсоединены к соответствующим входам блока добавления-вычитания импульсов ZJ . Недостатком известного цифров.ого устройства слежения за задержкой псевдослучайной последовательности является низкая помехозащищенность. Цель изобретения - повышение помехозащищенности. Для достижения указанной цели в цифровое устройство слежения за задержкой псевдослучайной последовательности, содержащее последовательно соединенные задающий генератор, блок добавления-вычитания импульсов, делитель частоты и опорный генератор псевдослучайных последовательностей, последовательно соединенные сумматор по модулю два и элемент И, последовательно соединенные перемножитель и реверсивный счетчик, счетный вход которого подключен к выходу элемента. И, второй вход которого подсоединен к выходу задакнцего генератора, первый выход опорного генератора псевдослучайных последовательностей подсоединен к объединенным входам перемножителя и сумматора по модулю два, второй вход которого подключен к второму выходу опорного генератора псевдослучайных последовательностей, при этом второй вход перемножителя является входом цифрового устройства слежения за задержкой псевдослучайной последовательности, введены по следовательно соединенные первьй до-. полнительный реверсивный счетчик, блок памяти и коммутатор коррекционных сигналов, последовательно соединенные дополнительный перемножитель, второй дополнительный реверсивный счетчик и первый цифровой компаратор, последовательно соединенные дополнительный делитель частоты и второй цифровой компаратор, другие входы которого подключены к соответствующим выходам реверсивного счетчика, установочный вход которого, объединенный с установочным входом первого дополнительного реверсивного счетчика и первыми управляющими входами блока памяти и коммутатора коррекционных сигналов, подключен к выходу дополнительного делителя частоты, второй выход которого подсоединен к установочному входу второго дополнитель.ного реверсивного счетчика и управляющему входу первого цифрового компаратора, а вход дополнительного делителя частоты подключен к выходу делителя частоты, выход первого цифрового компаратора подсоединен к управляющему входу первого дополнительного реверсивного счетчика и объединенным вторым управляющим входам блока памяти и коммутатора jcopрекционных сигналов,первый и второй выходы второго цифрового компаратора подсоединены к соответствующим объединенным входам блока памяти и коммутатора коррекционных сигналов, при этом выходы коммутатора коррекционных сигналов подсоединены к управляющим входам блока добавления-вычитания импульсов, а первый и второй входы дополнительного перемножителя подключены соответственно к второму входу перемножителя и третьему выход опорного генератора псевдослучайных последовательностей.

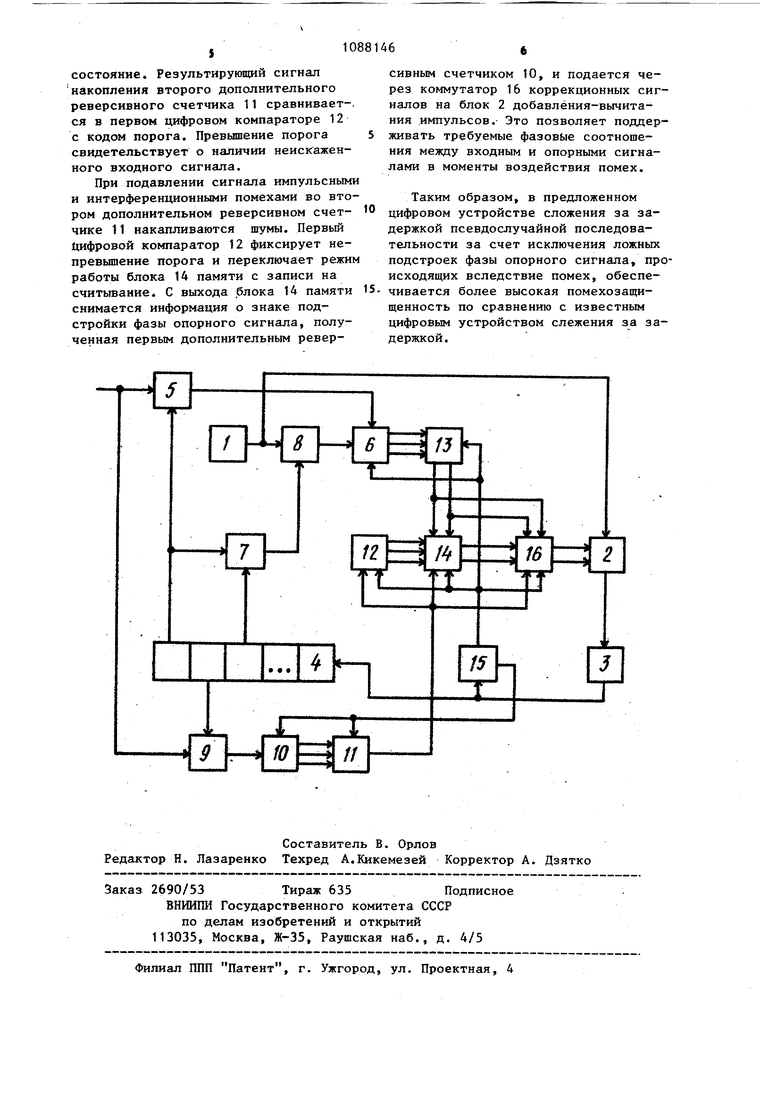

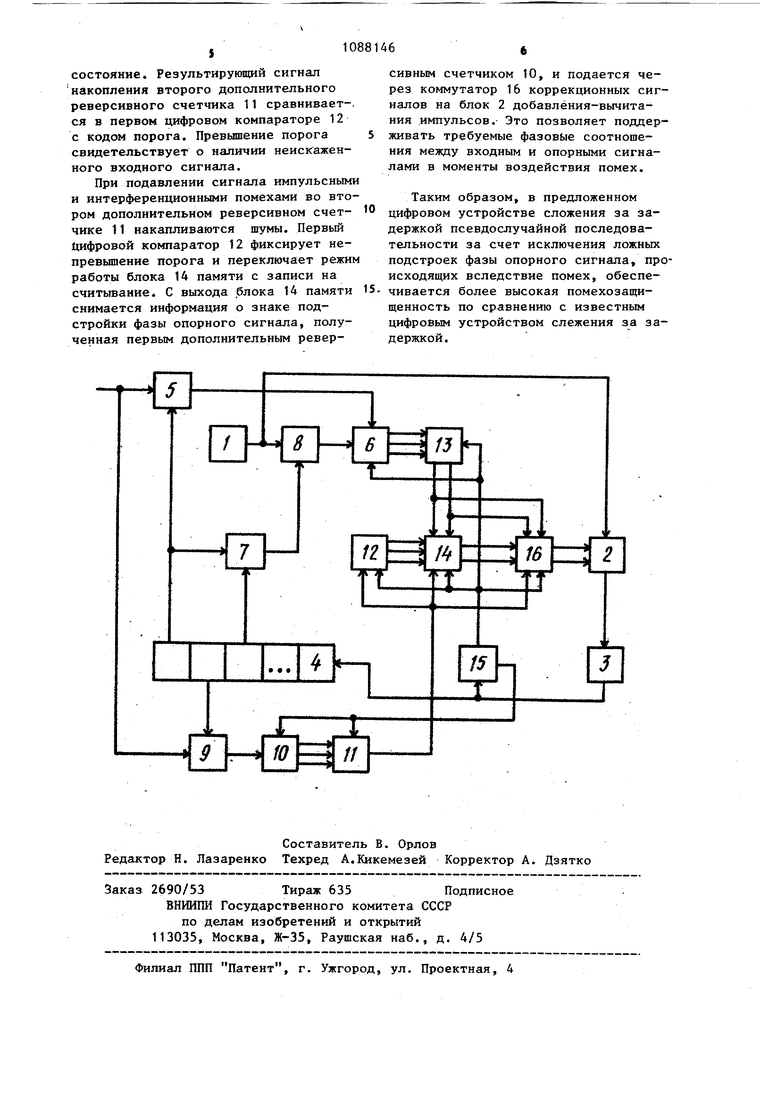

На чертеже приведена структурная электрическая схема цифрового устройства слежения за задержкой псевдослучайной последовательности.

Цифровое устройство слежения за задержкой псевдослучайной последовательности содержит задающий генератор 1, блок 2 добавления-вычитания импуЛьсов, делитель 3 частоты, опорный генератор 4 псевдослучайных последовательностей, перемножитель 5, реверсивный счетчик 6, сумматор 7 по модулю два, элемент И 8, дополнительный перемножитель 9, первьй 10 и второй 11 дополнительные реверсивные счетчики, первый 12 и второй 13 цифровые компараторы, блок 14 памяти дополнительный делитель 15 частоты, коммутатор 16 коррекционных сигналов Устройство работает следующим об- разом. Входной сигнал умножается в перемножителе 5 на опорный сигнал, поступающий с первого выхода опорного генератора 4 псевдослучайных последовательностей. С выхода перемножителя 5 сигнал рассогласования поступает на вход управления реверсивного счетчика 6. На счетный вход реверсивного счетчика v6 через элемент И 8 поступает последовательность импульсов с выхода задающего генератора 1. Временной интервал счета импульсов в реверсивном

счетчике 6 определяется сигналом с сумматора 7 по модулю два, навход ы которого подаются два смещенных во времени опорных сигнала с первого и второго выходов опорного генератора 4 псевдослучайных последовательностей. Выходной сигнал дополнительного делителя 15 частоты, поступаюпщй на установо 1ный вход реверсивного счетчика 6, устанавливает последний в среднее состояние, соответствующее среднему значению максимально возможного числа, записанного в реверсивный счетчик 6.

В зависимости от знака сигнала рассогласования опорного и вх,одного сиг.налов, поступающего с выхода перемножителя 5, реверсивный счетчик 6 будет чаще работать на суммирование или вычитание, в результате чего его код изменится относительно среднего значения. Через временные интервалы, задаваемые сигналом дополнительного делителя 15- частоты, второй цифровой компаратор 13 осуществляет сравнение текущего кода реверсивного счетчика 6 с кодом его среднего состояния. Результирующие сигналы сравнения поступают на входы блока 14 памяти и через коммутатор 16 коррекционных сигналов следуют на входы блока 2 добавления-вычитания импульсов. Блок 2 добавления-вычитания импульсов вводит дополнительные импульсы или стирает часть импульсов в сигнале, поступающем на вход, делителя 3 частоты, При изменении числа импульсов на единицу выходной сигнал делителя 3 частоты сдвигается на величину l/f в сторону уменьшения рассогласования по задержке между опорным сигналом И входным (fo - частота опорного генератора 1). Таким образом происходит подстройка фазы опорного и входного сигналов. На входы дополнительного перемножителя 9 поступают входной сигнал и опорный сигнал с третьего выхода опорного генератора 4 псевдослучайных последовательностей, совпадающий по фазе в режиме синхронизма с входным сигналом. Выходной сигнал дополнительного перемножителя 9 управляет направлением счета второго дополнительного реверсивного счетчика 11. Дополнительный делитель 15 частоты задает время накопления входного сигнала .и сбрасывает второй дополнительный реверсивный счетчик 11 в среднее

состояние. Результирукиций сигнал накопления второго дополнительного реверсивного счетчика 11 сравнивает-, ся в первом цифровом компараторе 12 с кодом порога. Превышение порога свидетельствует о наличии неискаженного входного сигнала.

При подавлении сигнала импульсными и интерференционными помехами во втором дополнительном реверсивном счетчике 11 накапливаются шумы. Первый цифровой компаратор 12 фиксирует непревышение порога и переключает режим работы блока 14 памяти с записи на считывание. С выхода блока 1А памяти снимается информация о знаке подстройки фазы опорного сигнала, полученная первым дополнительным реверсивным счетчиком 10, и подается через коммутатор 16 коррекционных сигналов на блок 2 добавления-вычитания импульсов. Это позволяет поддерживать требуемые фазовые соотношения между входным и опорными сигналами в моменты воздействия помех.

Таким образом, в предложенном цифровом устройстве сложения за задержкой псевдослучайной последовательности за счет исключения ложных подстроек фазы опорного сигнала, происходящих вследствие помех, обеспечивается более высокая помехозащищенность по сравнению с известным цифровым устройством слежения за задержкой.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство слежения за задержкой псевдослучайной последовательности | 1984 |

|

SU1225033A1 |

| Цифровое устройство слежения за задержкой | 1973 |

|

SU467489A1 |

| Устройство поиска шумоподобных сигналов | 1985 |

|

SU1254590A1 |

| Цифровое устройство для слежения за задержкой псевдослучайной последовательности | 1978 |

|

SU999172A1 |

| Цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала | 1983 |

|

SU1131034A2 |

| Цифровое устройство слежения за задержкой псевдослучайных последовательностей | 1975 |

|

SU554630A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство синхронизации корреляционного приемника псевдослучайных сигналов | 1982 |

|

SU1069182A1 |

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1986 |

|

SU1394411A1 |

| Устройство поиска псевдослучайных последовательностей | 1981 |

|

SU1042199A1 |

ЦИФРОВОЕ УСТРОЙСТВО СЛЕШЕНИЯ ЗА ЗАДЕРЖКОЙ ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ, содержащее последовательно соединенные задающий генератор, блок добавления-вычитания импульсов,, делитель частоты и опорньй генератор псевдослучайных последова-. тельностей, последовательно соединенные сумматор по модулю два и элемент И, последовательно соединенные перемножитель и реверсивный счетчик, счетный вход которого подключен к выходу элемента И, второй вход которого подсоединен к выходу задакицего генератора, первый выход опорного генератора псевдослучайных последовательностей подсоединен к объединенным входам перемножителя и сумматора по модулю два, второй вход которого подключен к второму выходу опорного генератора псевдослучайных последовательностей, при этом второй вход перемножителя является входом цифрового устройства слежения за задержкой псевдослучайной последовательности, отличающееся тем, что, с целью повьппения помехозащищенности, в него введены последовательно соединеннее первый дополнительный реверсивный счетчик, блок памяти и коммутатор коррекционных сигналов, последовательно соединенные дополнительный перемножитель, второй дополнительный реверсивный счетчик и первый цифровой компаратор, последовательно соединенные дополнительный делитель частоты и второй цифровой компаратор, другие входы которого подключены к соответствующим выходам реверсивного счетчика, установочный вход которого, объединенный с установочным входом первого дополнительного реверсивного счетчика и первыми управляющими входами блока памяти и коммутатора коррекционных сигналов, подключен к выходу дополнительного делителя частоты, второй выход которого подсоединен к устаноi вочному входу второго дополнительного kn реверсивного счетчика и управляющему входу первого цифрового компаратора, а вход дополнительного делителя частоты подключен к выходу делителя частоты, выход первого цифрового компаратора подсоединен к управляющему входу первого дополнительного реверсивного счетчика и объединенным вторым управляющим входам блока памяти X ЭО и коммутатора коррекционных сигналов, первый и второй выходы второго цифрового компаратора подсоединены к со-« i;; а ответствующим Г объедине ным входам блока памяти и коммутатора коррек- ционных сигналов, при этом выходы коммутатора коррекционных сигналов подсоединены к управляющим входам блока добавления - вычитания импульсов, а первый и второй входы дополнительного перемножителя подключены соответственно к второму входу перемножителя и третьему выходу опорного генератора псевдослучайных последовательностей.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровое устройство слежения за задержкой | 1973 |

|

SU467489A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровое устройство слежения за задержкой | 1978 |

|

SU702536A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-04-23—Публикация

1983-02-15—Подача