Изобретение относится к импульсной технике и может предназначаться для использования в устройствах ав томатики и вычислительной техники.

Цель изобретения - повьшение надежности работы за счет исключения сбойных ситуаций, связанных с поте™ рей информации.

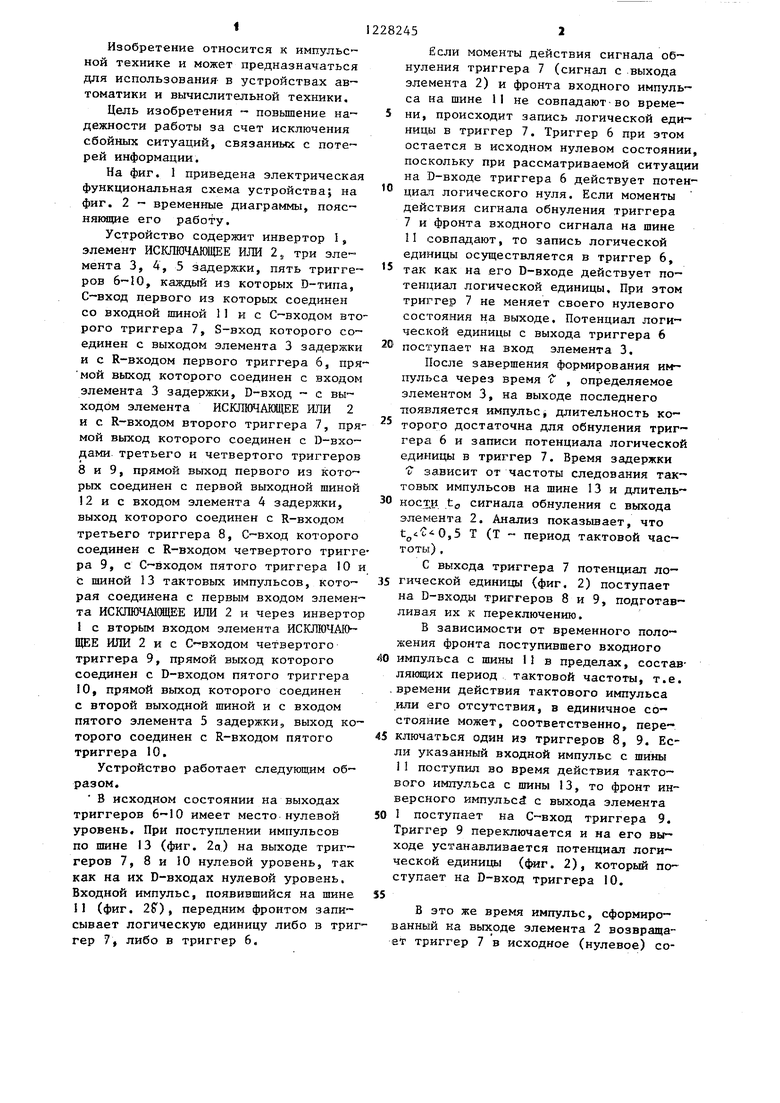

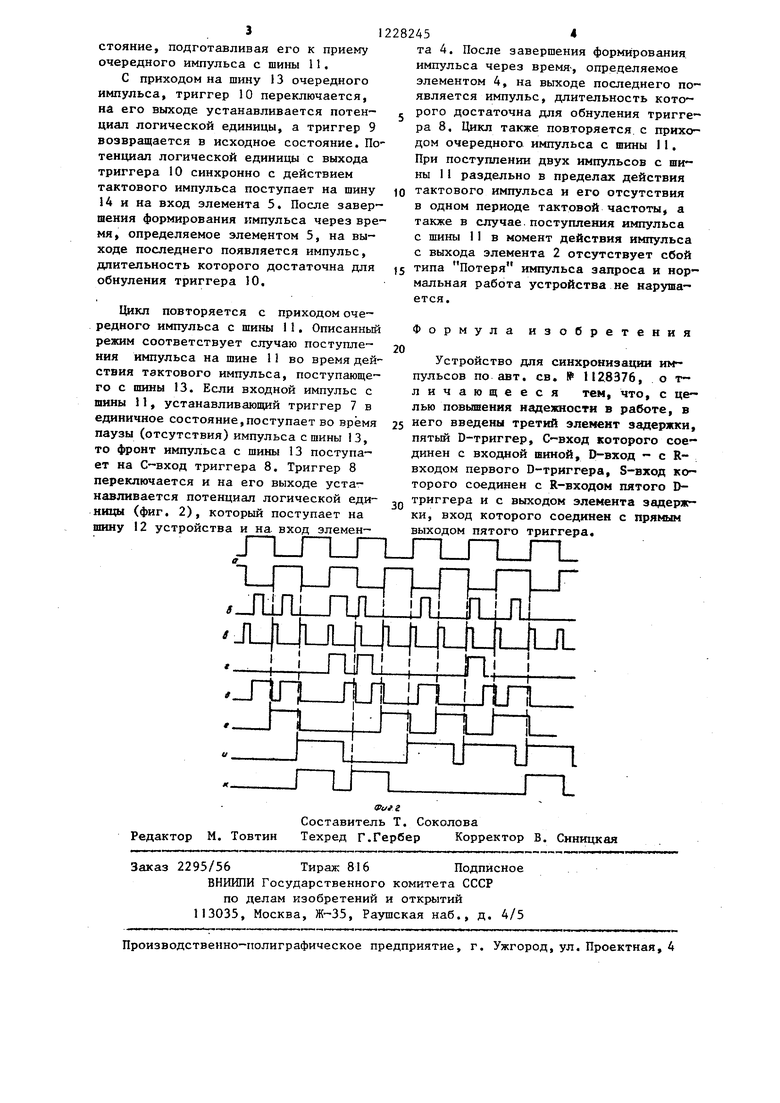

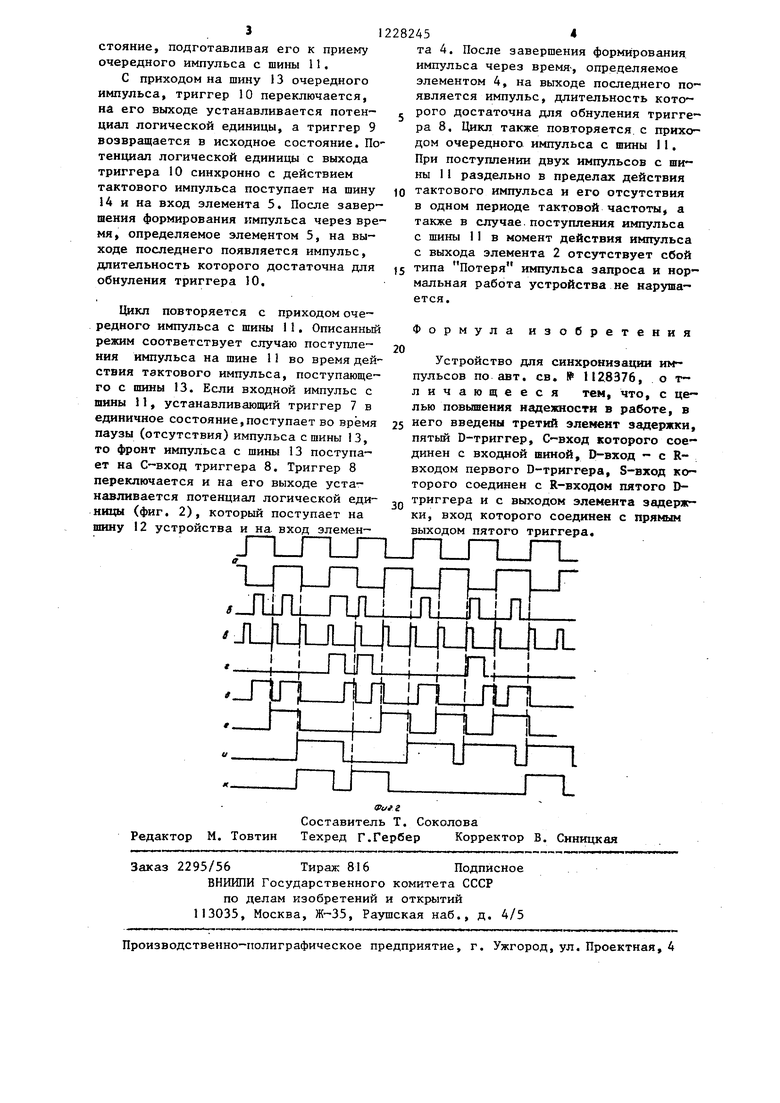

На фиг, 1 приведена электрическая функциональная схема устройства; на фиг. 2 временные диаграммы, пояс™ някмцие его работу,

Устройство содержит инвертор I, элемент ИСКЛННАЮЩЕЕ ИЛИ 2,, три элемента 3, 4, 5 задержки, пять триггеров , каждый из которых D-типа, С-вход первого из которых соединен со входной шиной 11 и с С-входом второго триггера 7, S-вход которого соединен с выходом элемента 3 задержки и с R-входом первого триггера 6, пря мой выход которого соединен с входом элемента 3 задержки, D-вход - с выходом элемента ИСКЛЮЧАЩЕЕ ИЛИ 2

10

Если моменты действия сигнала обнуления триггера 7 (сигнал с выхода элемента 2) и фронта входного импульса на шине II не совпадают-во времени, происходит запись логической единицы в триггер 7, Триггер 6 при этом остается в исходном нулевом состоянии, поскольку при рассматриваемой ситуации на D-входе триггера 6 действует потен- циап логического нуля. Если моменты действия сигнала обнуления триггера 7 и фронта входного сигнала на шине II совпадают, то запись логической единицы осуществляется в триггер 6,

5 так как на его D-входе действует потенциал логической единицы. При этом триггер 7 не меняет своего нулевого состояния на выходе. Потенциал логической единицы с выхода триггера 6

20 поступает на вход элемента 3,

После завершения формирования импульса через время , определяемое элементом 3, на выходе последнего появляется импульс длительность ко-

и с R-входом второго триггера 7, пря- торого достаточна для обнуления тригмой выход которого соединен с D-BXO- дами третьего и четвертого триггеров 8 и 9, прямой выход первого из которых соединен с первой выходной шиной 2 и с входом элемента 4 задержки, выход которого соединен с R-входом третьего триггера 8, С-вход которого соединен с R-входом четвертого триггера 9, с С-входом пятого триггера 10 и с шиной 13 тактовых импульсов, которая соединена с первым входом элемента ИСКЛЮЧАНадНЕ ИЖ 2 и через инвертор 1 с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и с С входом четвертого триггера 9, прямой выход которого соединен с D-входом пятого триггера 10, прямой выход которого соединен с второй выходной шиной и с входом пятого элемента 5 задержки, выход которого соединен с R-входом пятого триггера 10.

Устройство работает следующим образом.

В исходном состоянии на выходах триггеров 6-10 имеет место нулевой уровень. При поступлении импульсов по шине 13 (фиг, 2а) на выходе триггеров 7, 8 и 10 нулевой уровень, так как на их D-входах нулевой уровень. Входной импульс, появившийся на шине И (фиг, 2), передним фронтом записывает логическую единицу либо в триг гер 7, либо в триггер 6,

Если моменты действия сигнала обнуления триггера 7 (сигнал с выхода элемента 2) и фронта входного импульса на шине II не совпадают-во времени, происходит запись логической единицы в триггер 7, Триггер 6 при этом остается в исходном нулевом состоянии, поскольку при рассматриваемой ситуации на D-входе триггера 6 действует потен- циап логического нуля. Если моменты действия сигнала обнуления триггера 7 и фронта входного сигнала на шине II совпадают, то запись логической единицы осуществляется в триггер 6,

так как на его D-входе действует потенциал логической единицы. При этом триггер 7 не меняет своего нулевого состояния на выходе. Потенциал логической единицы с выхода триггера 6

поступает на вход элемента 3,

После завершения формирования импульса через время , определяемое элементом 3, на выходе последнего появляется импульс длительность ко-

торого достаточна для обнуления триггера 6 и записи потенциала логической единицы в триггер 7, Время задержки t зависит от частоты следования тактовых импульсов на шина 13 и длитель-

30 костер tg сигнала обнуления с выхода элемента 2. Анализ показьшает, что t iC 0,5 Т (Т - период тактовой частоты) ,

С выхода триггера 7 потенциал ло35 гической единицы (фиг, 2) поступает на D-входы триггеров 8 и 9, подготавливая их к переключению.

В зависимости от временного положения фронта поступившего входного

40 импульса с шины П в пределах, состав ляквдих период тактовой частоты, т,е, .времени действия тактового импульса или его отсутствия, в единичное со стояние может, соответственно, пере

45 ключаться один из триггеров 8, 9. Если указанный входной импульс с шины 1I поступил во время действия тактового иМ.тульса с шнны 13, то фронт инверсного импульсй с выхода элемента

50 1 поступает на С-вход триггера 9. Триггер 9 переключается и на его выходе устанавливается потенциал логи ческой единищ. ((|иг, 2), который поступает на D-вход триггера 10.

$5

В это же время импульс, сформированный на выходе элемента 2 возвращает триггер 7 в исходное (нулевое) состояние, подготавливая его к приему очередного импульса с шины 11.

С приходом на шину 13 очередного импульса, триггер 10 переключается, на его выходе устанавливается потенциал логической единицы, а триггер 9 возвращается в исходное состояние. Потенциал логической единицы с выхода триггера 10 синхронно с действием тактового импульса поступает на шину 14 и на вход элемента 5. После завер шения формирования импульса через время, определяемое элементом 5, на выходе последнего появляется импульс, длительность которого достаточна для обнуления триггера 10,

Цикл повторяется с приходом очередного импульса с шины 11. Описанный режим соответствует случаю поступления импульса на шине 11 во время действия тактового импульса, поступающего с шины 13. Если входной импульс с шины 11, устанавливающий триггер 7 в единичное состояние,поступает во время паузы (отсутствия) импульса с шины 13, то фронт импульса с шины 13 поступает на С-вход триггера 8. Триггер 8 переключается и на его выходе устанавливается потенциал логической единицы (фиг. 2), который поступает на шину 12 устройства и на вход элемента 4, После завершения формирования импульса через время-, определяемое элементом 4, на выходе последнего появляется импульс, длительность кото

рого достаточна для обнуления триггера 8. Цикл также повторяется с приходом очередного импульса с шины 1I. При поступлении двух импульсов с ши ны 11 раздельно в пределах действия

тактового импульса и его отсутствия в одном периоде тактовой частоты, а также в случае.поступления импульса с шины 1I в момент действия импульса с выхода элемента 2 отсутствует сбой

типа Потеря импульса запроса и нормальная работа устройства не нарушается.

Формула изобретения

Устройство для синхронизации импульсов по авт. св. № 1IZ8376, о т- личающееся тем, что, с целью повышения надежности в работе, в

него введены третий элемент задержки, пятый D-триггер, С-вход которого соединен с входной шиной, D-вход - с R- входом первого D-триггера, S-вход которого соединен с R-входом пятого Dтриггера и с выходом элемента задержки, вход которого соединен с прямым выходом пятого триггера.

-fimi rUU JLJl,JL

JL4JUl -|L fLJULULJL

I I n in II InI

ЛЛ

n

(Put г

Составитель Т. Соколова Редактор М. Товтин Техред Г.Гербер Корректор В. Синицкая

Заказ 2295/56 Тирал: 816 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

In

n

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО С ОБРАТНОЙ СВЯЗЬЮ ДЛЯ КЛИППИРОВАНИЯ ЗНАКОПЕРЕМЕННЫХ СИГНАЛОВ (ВАРИАНТЫ) | 2015 |

|

RU2607934C2 |

| Устройство для задержки и формирования импульсов | 1988 |

|

SU1539979A1 |

| Устройство корректировки фазы для схем синхронизации | 1989 |

|

SU1706037A1 |

| Измеритель временных параметров случайных импульсных потоков | 1988 |

|

SU1575135A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

| Программируемый формирователь управляющих воздействий микропроцессорной системы | 1989 |

|

SU1725210A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1357987A1 |

| Цифровой измеритель длительности одиночных импульсов | 1984 |

|

SU1257600A1 |

| Устройство для формирования импульсных сигналов | 1990 |

|

SU1758858A1 |

Изобретение относится к импульсной технике. Предназначается для использования в устройствах автомати ки и вычислительной техни1яи и является дополнительным изобретением к авт.св. № 1128376. Цель изобретения- повьшеиие надежности работы устройства - достигается путем исключения сбойных ситуаций, связанных с потерей информации. Для этого в устройство введены элемент 5 задержки и триггер D-типа Ш. Устройство также содержит инвертор 1, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, элементы 3 и 4 задержки, триггер D-типа 6, 7, 8 и 9, шины: входную 11, выходную I2, тактовых импульсов 13. 2 ил. с (Л 1СЛ к

Авторы

Даты

1986-04-30—Публикация

1984-12-28—Подача