шину 27. дополнительно введены второй 11 и третий 12 элементы ИЛИ, пятый 6, шестой 7, седьмой 8 и восьмой 9 синхронные D-триг- геры, первый 13, второй 14 и третий 15 элементы И, счетчик 16 импульсов, формирователь 17 импульсных сигналов, элемент 18 ИСКЛЮЧАЮЩЕЕ ИЛИ. первый 19. второй 20, третий 21, четвертый 22 и пятый 23 элементы задержки и дополнительная шина 26 установки устройства в исходное состояние. Эффект от использования

устройства корректировки фазы для схем синхронизации заключается в том, что импульсы, поступающие на входы устройства, не привязываются во времени тактовым импульсам, а с минимальной задержкой подаются на выход устройства. В данном случае задержка составляет суммарное время задержки распространения сигнала в двух логических элементах с простой структурой (элементы И 14 и ИЛИ 11, либо И 15 и ИЛИ 11). 2 ил

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ФАЗЫ | 1992 |

|

RU2028727C1 |

| Устройство для вывода информации | 1989 |

|

SU1656548A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1265789A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1462423A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ЧЕТЫРЕХФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1998 |

|

RU2133550C1 |

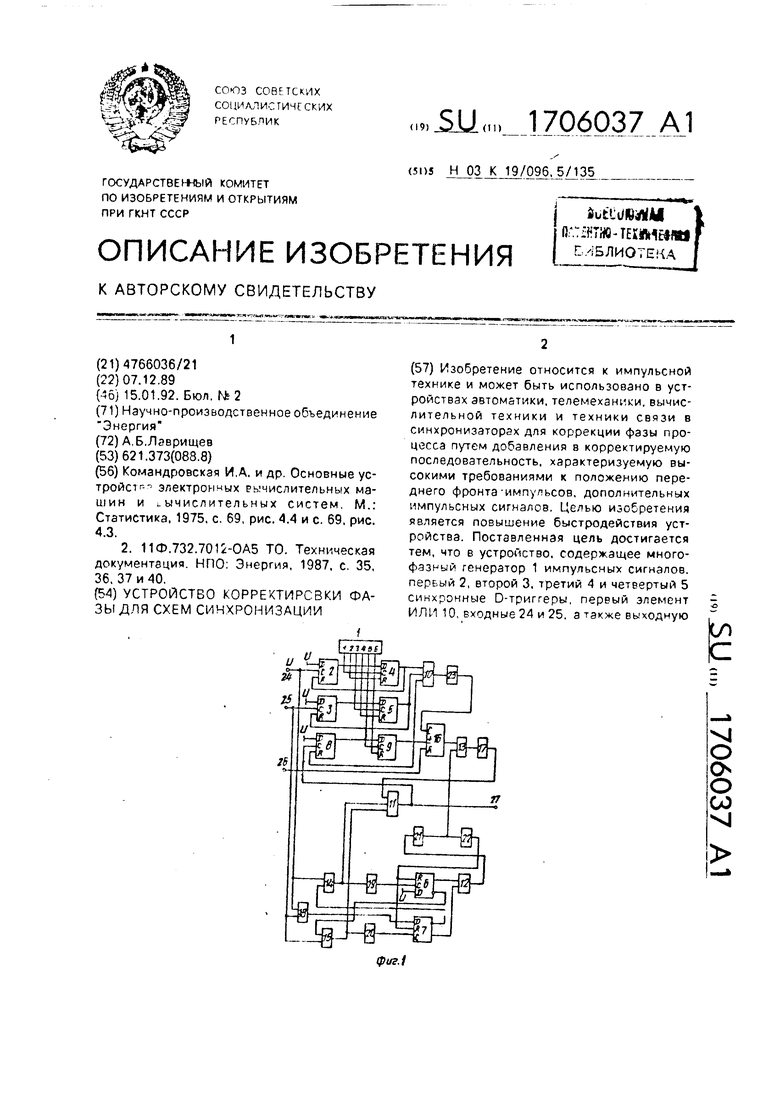

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики,телемеханики, вычислительной техники и техники связи в синхронизаторах для коррекции фазы процесса путем добавления в корректируемую последовательность, характеризуемую высокими требованиями к положению переднего фронта импульсов, дополнительных импульсных сигналов. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее многофазный генератор 1 импульсных сигналов. первый 2, второй 3, третий 4 и четвертый 5 синхронные D-триггеры, первый элемент ИЛИ 10, входные 24 и 25. а также выходную fe VJ О О О CJ vj

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики,телемеханики, вычислительной техники и техники связи в синхронизаторах для коррекции фазы про- цесса путем добавления в корректируемую последовательность, характеризуемую высокими требованиями к положению переднего фронта импульсов, дополнительных импульсных сигналов.

Цель изобретения - повышение быстродействия устройства.

На фиг.1 представлена Функциональная схема устройства; на фиг.2 - временные ди- агрлммы его работы.

Устройство корректировки фазы для схем синхронизации содержит многофазный генератор 1 импульсов, первый 2, второй 3. третий 4, четвертый 5, пятый 6, шестой 7, седьмой 8 и восьмой 9 синхронные D-триггеры. первый 10, второй 11 и третий 12 элементы ИЛИ, первый 13, второй 14 и третий 15 элементы И: реверсивный счетчик 16 импульсов; формирователь 17 импупьсных сигналов; элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18; первый 19. второй 20, третий 21, четвертый 22 и пятый 23 элементы задержки сигнала, первую 24 и вторую 25 входне шины устройства, шину 26 установ- ки его исходного состояния и выходную шину 27.

Прямой выход первого синхронного D- триггера 2 подключен к управляющему входу третьего синхронного D-триггера 4, тактовый вход и вход обнуления которого подключены соответственно к первому и второму выходам мнсгсфазного генератора 1 импульсов, а прямей вь .хзд - к первому входу первого э еме-гя ИЛИ 10 и обнуляю- щему входу nepscro снесенного D-григге- ра 2. Прямой второго синхронного D-триггера З г.лд -и-мен управляющему входу четвертого --.in . - ;. 0-триггера 5,

тактовый вход и вход обнуления которого подключен соответственно к третьему и четвертому выходам многофазного генератора 1 импульсов, а прямой выход - к второму входу первого элемента ИЛИ 10 и к обнуля- входу второго синхронного D-триггера 3. Прямой выхсдседьмогосинхронного D-триггера 8 соединен с управляющим входом восьмого синхронного D-триггера 9, тактовый вход и вход обнуления которого подключены соответственно к пятому и шестому выходам многофазного генератора 1 импульсов, а прямой выход - к третьему входу первого элемента ИЛИ, обнуляющему входу седьмого синхронного D-триггера 8 и управляющему входу реверсивного счетчика 16 импульсов, соединенного тактовым входом через пятый элемент 23 задержки с выходом первого элемента ИЛИ 10, а обнуляющим входом - с шиной 26 исходного состояния устройства. Выход последнего разряда счетчика 16 импупьсов через последовательно соединенные первый элемент И 13 и формирователь 17 импульсных сигналов подключен к первому входу второго элемента ИЛИ 11, объединенного по выходу с тактовым входом седьмого синхронного D- триггера 8 и выходной шиной 27 устройства. Второй вход второго элемента ИЛИ 11 подключен к выходу второго элемента И 14 и через первый элемент задержки 19 - к тактовому входу пятого синхронного D-триггера 6, инверсный выход которого соединен с первым входом третьего элемента И 15. Третий вход второго элемента ИЛИ 11 подклю- чен к выходу третьего элемента И 15 и через второй элемент задержки 20 - к тактовому входу шестого синхронного D-триггерэ 7. инверсный выход которого соединен с первым входом второго элемента И 14. Второй вход второго элемента И 14 обьединен с тактовым входом первого синхронного D- триггера 2, первой входной шиной 24 и первым входом элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 18, второй вход которого подключен к второму входу третьего элемента И 15, тактовому входу второго синхронного D-триг- герэЗ и второй входной шине 25 устройства, а выход - к управляющему входу шестого синхронного D-триггера 7. Прямые выходы пятого б и шестого 7 синхронных D-тригге- ров, обнуляющие входы которых объединены с выходом четвертого элемента 22 задержки, соединены соответствнено с вторым и первым входами третьего элемента ИЛИ 12, подключенного выходом через третий элемент 21 задержки к второму входу первого элемента И 13 и входу четвертого элемента 22 задержки. При этом управляющие входы первого 2, второго 3, пятого 6 и седьмого 8 синхронных D-триггеров объединены с шиной единичного потенциала устройства.

Многофазный генератор 1 должен формировать шесть тактовых последовательностей, поступающих с первого - шестого выходов. Расположение тактов во времени должно соответствовать номерам выходов мног Фазного генератора 1. Так, такт с второго ЕгЫ .ода генератора должен следовать после такта с первого выхода выхода, но песед тактом с третьего выходя и т.д. В устройстве возможно сокращение длительности деформирсвывэемых импульсов на время не больше чем 1.5 период многофазного генератора, г.озтому период тактов должен быть меньше чем, допуск на длительность обрабатываемых устройством импульсов в 1,5 раза.

В качестве формирователя 17 импульсных сигналов может использован любой формирователь импульсов длительностью соответствующем длительности входных сигналов устройства по положительному перепаду управляющего воздействия.

Входящие в устрогство элементы 19-23 передают сигнал (высокий уровень) с входа на выходе с задержками Т1-Т5 соответственно, при снятии высокого уровня с входа на выходе появляется низкий уровень без за,, ки. При этом времена Т1-Т5 определяются k-о выражений

Гвх Ti Г23 4-Г18 +Г7 .

где тВх - длительность входных импульсов устройства:

Г2з - минимально необходимое время опережения сигнала нэ управляющем входе шестого триггера 7 относительно появления рабочего Фронта на его тактовом входе;

Г18 - время задержки распространения сигнала в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 18;

п - время задержки срабатывания шестого триггера 7 по тактовому входу;

Тех Т2 Г23 + Г18 - Г15

где Г15 - время задержки распространения сигнала в элементе И 15 :

, +rn-iiTin; .

где Гл минимально возможная пауза меж- ду входными импульсами на входе устройства;

г{рГ - минимальная задержка распространения сигнала в одной из двух цепей Ц1, где первая цепь: первый элемент 19 зздер- жки, пятый Огтриггер 6, элементы ИЛИ 12, И 13 и формирователь 17; вторая цепь: второй элемент 20 задержки, шестой Dt-триг- гер 7, элементы ИЛИ 12, И 13 и формирователь 17;

rijf - максимальная задержка распространения сигнала в одной из двух цепей Ш;

30

Т4 пз+Г17-Тц 1п:

где - задержка распространения сигнала Е элемент И 13;

Гц- быстродействие формирователя 17 импульсных сигналов;

г5Г минимальная задержка распространения сигнала в одной из двух цепей Ц2, где первая цепь: пятый Di-триггер б, элемент И 15 и вторая цепь: шестой Dt-триггер 7, элемент И 14;

T$fx - максимальное время распространения сигнала в одной из двух цепей Ц2;

tie - гю Ts т 1 - 2 - гю ;

где Tie - минимально необходимое время опережения сигнала на управляющем входе счетчика 16 относительно появления рабочего ф ронта на его тактовом входе;

гю - время задержки распространения сигнала в элементе ИЛИ 10;

71-2 - время разности фаз между нечетным и четным выходами многофазного генератора 1.

Устройство работает следующим образом.

После подачи на устройство питания ьз входную шину 26 установки исходного состояния должен быть подан импульс длительностью не менее, чем 1.4 периода многофазного генератора 1. Этот импульс удерживает счетчик 16 в нулевом состоянии до конца обнуления первого - четвертого и седьмого - восьмого Dt - триггеров, причем в случае, если они после включения оказались в единичном состоянии. По прошествии времени, равного суммарной длительности задержки третьего 21 и четвертого 22 элементов задержки, пятый б и шестой 7 триггеры обнуляются, если при включении устройства они установились в единичное состояние. После этого устройство устанавливается в исходное состояние и готово к работе.

В случае прихода на первый вход 24 устройства входной импульс через второй элемент И 14 и второй элемент ИЛИ 11 поступает нэ выход устройства с минимальной задержкой. С выхода второго элемента И 14 через первый элемент 19 задержки этот импульс поступает на тактовый вход пятого D-триггера б и переводит его в единичное состояние. В результате низкий уро- вень с инверсного выхода триггера 6 поступает на первый вход третьего элемента И 15 и запрещает прохождение импульса, в случае его прихода с второго входа 25 устройства на его выход. Импульс, пришедший на первый вход 24 устройства, также поступает на тактовый вход первого D- триггера 2 и с выхода второго элемента ИЛИ 11 - на тактовый вход седьмого D- триггера 8. в результате чего эти триггеры -переводятся в единичное состояние. С выходов третьего 4 и восьмого 9 D-триггерое на первый и третий входы первого элемента ИЛИ 10 поступает по одному импульсу, которые через первый элемент ИЛИ 10 и пятый элемент задержки 23 последовательно поступают на тактовый вход счетчика 16. Если первым поступает импульс с третьего D-триггера 4, то счетчик 16 переводится в состояние Минус один (нулевой уровень на управляющем входе воспринимается как команда на вычитание). В случае, если первым поступает импульс с прямого выхода восьмого D-триггера 9, то он вначале попадает на управляющий вход счетчика 16 и только затем через первый элемент ИЛИ 10 и пятый элемент задержки 23 на его тактовый вход. При этом состояние счетчика 16 увеличивается на единицу.

Рассмотрим случай, когда первый импульс поступает с прямого выхода восьмого D-триггера 9, т е. вначале счетчик 16 устанавливается в состояние Один, э затем импульсом с выхода третьего D-триггера - вновь в состояние Нуль. Следовательно,

состояние старшего разряда счетчика 16 не изменяется и низкий уровень с выхода счетчика 16 присутствует на первом входе первого элемента И 13. Высокий уровень с

прямого выхода шестого D-триггера 6 поступает через третий элемент ИЛИ 12 и третий элемент задержки 21, задержавшись на последнем на время ТЗ, на второй вход закрытого элемента И 13 и через четвертый

0 элемент задержки 22 - на обнуляющие входы пятого б и шестого 7 синхронных D-триг- геров.

Таким образом, спустя время, равное минимальному периоду для импульсов, по5 ступающих на выход устройства (определяется третьим элементом 21 задержки), пятый D-триггер б обнуляется, третий элемент И 15 открывается, и все устройство в исходном состоянии.

0В случае прихода импульса на второй вход 25 устройства (устройство находится в исходном состоянии) оно срабатывает аналогично тому, как оно срабатывает от импульсов на первом «ходе 24. Импульс через

5 третий элемент И 15 и второй элемент ИЛИ 11 с максимальным быстродействием поступает на выход устройства. С выхода третьего элемента И 15 через второй элемент задержки 20 этот импульсный сигнал

0 поступает на тактовый вход шестого D-триг- . гера 7 (в этот момент на информационном входе триггера 7 присутствует высокий уровень с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18) и переводит шестой D-триггер 7 в

5 единичное состояние. Низкий уровень с инверсного выхода этого триггера поступает на первый вход второго элемента И 14 и запрещает пропускание импульса (в случае его прихода) с первого входа 24 устройства

0 на его выход 27.

Импульс, пришедший на второй вход устройства, также поступает на тактовый вход второго D-триггера З и с выхода второго элемента ИЛИ 11 - на тактовый вход

5 седьмого D-триггера 8, в результате чего эти триггеры оказываются переведенк ,IMH в единичное состояние. С выхода чет «ертого 5 и восьмого 9 триггеров на второй v- третий входы первого элемента ИЛИ 10 поступает

0 по одному импульсу. Высокий уровень с выхода шестого триггера 7 поступает на третий элемент ИЛИ 12, а дальше устройство сработает аналогично тому, как оно срабатывало по приходу импульса на первый

5 вход. После обнуления шестого триггера 7 устройство приходит в исходное состояние.

В случае прихода импульса на закрытый вход устройства, например на второй (т.е. импульс, пришедший до этого на первый

вход устройства, перевел пятый D-триггер 6 в единичное состояние и низкий уровень на первом входе перекрыл третий элемент И 15), этот импульс не проходит через третий элемент И 15, а поступает только на тактовый вход второго D-триггера З. В результате с выхода четвертого триггера 5 на второй вход первого элемента ИЛИ 10 поступает импульс, который, попав на счетный вход счетчика 16, переведет его в состояние минус единица. В результате высокий уровень со старшего разряда счетчика 16 поступает на первый вход первого элемента И 13. После того. как третьим элементом задержки 21 выдержан минимальный перио для импульсов, поступающих на выход ус. ройства, высокий уровень с него поступает на второй вход первого элемента И 13 и с него - на вход формирователя 17 импульсных сигналов. Импульс, сформированной формирователем 17, через второй элемент ИЛИ 11 поступает на выход устройства.

Таким образом, импульс, пришедший на второй вход 25 устройства во время пе- дсЕе с ия импульса через переый его вход 24 или с иг-ерволом между импульсами менее минимально допустимого, задерживается для потребителя на минимально допустимое время и только затем формируется.

Сформированный импульс с выхода второго элемента ИЛИ 11 поступает на тактовый вход седьмого D-триггера 8, с него - на инфорациснный вход восьмого D-триггера 9. Импульс, сформированный на выходе D-триггера 9, поступает через первый элемент ИЛИ 10 и пятый элемент задержки 23 на счетный вход счетчика 16 и увеличивает его состояние на единицу. В результате чего сметчик 16 оказывается в нулезо м состоянии.

Таким образом, в счетчике 16 проходит сравнение количества импульсов, поступивших на входы устройства и вышедших на его выход. уровень с выхода третьего элемента задержки через время задержки четвертого элемента 22 задержки пс ступает на R-входы пятого б и шестого 7 D- ,. .тгеров, в результате пятый D-триггер 6 обнульыся, третий элемент И 15 открывается, и, таким образом, устройство оказывается в исходном состоянии. При этом четвертый элемент задержки 22 необходим для того, чтобы формирователь 17 запускался не позднее, чем откроется второй элемент И 14 или третий элемент И 15. Это обеспечивает запрет прохождения остатка (пачки) импульса, пришедшего на закрытый вход устройства.

В случае прихода импульса на закрытый первый вход устройства оно срабатывает аналогично.

Входные второй 14 и третий 15 элемен- 5 ты И управляются с выходов шестого 7 и пятого 6 D-триггеров соответственно. Эта схема управления выполнена несимметричной за счет введения в нее элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18. чтобы избежать

0 одновременного срабатывания двух D-триггеров б и 7 в случае прихода импульсов на оба входа устройства одновременно (поступают на тактовые входы D-триггеров б и 7 с интервалом меньше времени срабатыва5 ния последних), и, таким образом, избежать сбой в работе всего устройства. В случае прихода импульсов на оба входа устройства одновременно на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 18 формируется низкийуро0 вень напряжения и шестой D-триггер 7 не может перейти в единичное состояние. Первый элемент 19 задержки необходим для того, чтобы сместить во времени момент срабатывания пятого D-триггера б относи5 тельно момента срабатывания шестого D- триггера 7 во время переходного процесса или наличия высокого уровня на 0-аходе последнего (временные диаграммы возможных приходов импульсов на входы ус0 тройства на фиг.2: Г14 - время срабатывания второго элемента И 14; ГБ - время срабатывания пятого D- триггера 5 f - временная граница срабатывания шестого Dt-триггерз 7).

5 Так/ в случае позднего импульса на первый вход 24 устройства по сравнению с вторым входом 25 устройства (случай А, фиг.2) на тактовый вход шестого D-триггера 7 запускающий фронт приходит

0 в момент IA, когда на его информационном входе высокий уровень. Этот триггер переходит в единичное состояние и запрещает прохождение через второй элемент И 14 импульса с первого входа устройства. При

5 этом пятый D-триггер 6 не срабатывает, так как импульс с длительностью меныие времени задержки через элемент задержки не проходит.

В случае Б (фиг.2) запускающий фронт

0 импульса на тактовый вход шестого D-триггера 7 поступает в момент ТБ - момент переходного процесса на информационном входе последнего. Поэтому возможны два ел учат.

51). Шестой D-триггер 7 переходит в единичное состояние и запрещает прохождение через второй элемент И 14 импульса с первого входа 14 устройства. При этом пятый D триггер 6 не срабатывает,

2). Шестой D-триггер 7 не переходит в единичное состояние. При этом второй элемент И 14 остается открытым и пропускает на вход первого элемента задержки 19 импульс, который устанавливается пятый D- триггер б в единичное состояние.

Из случая 2 видно, что при таком совпадении параметров устройства и временном положении импульсов, поступивших на входы устройства, возможно увеличение длительности импульса, поступающего на выход устройства на время, равное

Г15 +Т2 - Г18 -Г23 .

Поэтому Т2 целесообразно выбирать близким к нижней границе допуска.

В случае В (фиг.2) запускающий фронт импульса на тактовый вход шестого триггера 7 поступает в момент, когда на информационном входе триггера 7 - низкий уровень и триггер остается в нулевом состоянии. При этом второй элемент И 14 открыт и импульс с первого входа 24 устройства проходит на тактовый вход пятого триггера 6 и он переходит в единичное состояние.

В случае прихода импульса на закрытый вход устройства за время меньшее, чем период многофазного генератора 1, плюс время задержки на элементах цепочки - первый триггер 2; третий D-триггер 4; первый элемент ИЛИ 10, пятый элемент 23 задержки, счетчик 16; первый элемент И 13 (или цепочки: второй D-триггер З, четвертый D-триггер 5, первый элемент ИЛИ 10, пятый элемент задержки 13, счетчик 16. первый элемент И 13) до открытия этого входа счетчик 16 может не перейти в состояние Минус единица, а в результате этого не срабатывает формирователь 17 импульсных сигналов. Открывшийся вход пропускает остаток импульса, т.е. импульс, прошедший через устройство, может быть укорочен на время, равное периоду тактовэния генератора 1, плюс время, вызванное задержкой на элементах одной из указанных цепочек (в зависимости от входа устройства), т.е. основная составляющая этой погрешности - период тактового генератора 1.

В случае, если импульс, пришедший на закрытый вход устройства, окончится после открытия входного ключа элемента И (14 или 15), его скол может, пройдя через первый 19 или второй 20 элементы задержки, вызвать повторное срабатывание схемы управления (пятый D-триггер 6 или шестой D- триггер 7 будет переведен в единичное состояние). Это приводит к новой попытке запуска формирователя 17 через время, равное минимальному периоду для импульсов, поступающих на выход устройства. Но. поскольку на выходе старшего разряда счетчика 16 низкий уровень, доформирова- ние дополнительного импульса не

происходит.

Эффект от использования изобретения для схем синхронизации заключается в том, что импульсы, поступающие на входы устройства, не привязываются к тактовым им0 пульсам, а это позволяет получить высокое быстродействие. Так, в данном устройстве импульсы от входа до выхода проходят через два логических элемента с простой структурой.

5

Формула изобретения Устройство корректировки фазы для схем синхронизации, содержащее первый и второй синхронные D-триггеры, входы уп0 равления которых объединены с шиной единичного потенциала, а тактовые входы - с первой и второй входными шинами устройства соответственно, прямой выход первого синхронного D-триггера подключен к управ5 ляющему еходу{ третьего синхронного D- триггера, тактовый и обнуляющий в/оды которого объединены соответствнено с первым и вторым выходами многофазного генератора импульсов, а прямой выход - с

0 обнуляющим входом первого синхронного . D-триггера и первым входом элемента ИЛИ. соединенного вторым входом с обнуляющим входом второго и прямым выходом четвертого синхронного D-триггера.

5 управляющий которого подключен к прямому выходу второго синхронного D- триггерэ. а тактовый и обнуляющий входы соответственно к третьему и четвертому выходам многофазного генератора импульсов,

0 отличающееся тем, что, с целью повышения быстродействия, в устройство дополнительно введены пятый, шестой, седьмой и восьмой синхронные D-триггеры, первый, второй, третий, четвертый и пятый

5 элементы задержки, формирователь импульсов, реверсивный счетчик импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй и третий элементы ИЛИ, а также первый, второй и третий элементы И, первый вход пер0 вого из которых подключен к выходу последнего разряда счетчика импульсов, а выход через формирователь импульсов - к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом вто5 рого элемента И и через первый элемент задержки - с тактовым входом пятого синхронного D-триггера, инверсный выход которого подключен к первому входу третьего элемента И. соединенного выход с третьим входом второго элемента ИЛИ и через второй элемент задержки - с тактовым входом шестогосинхронного D-триггерэ, соединенного инверсным выходом с первым входом второго элемента И, второй вход которого объединен с первой входной шиной устройства и первым входом элемента ИСКЛЮЧА- ЮЩЕЕ ИЛИ, подключенного вторым входом к второму входу третьего элемента И и второй входной шине устройства, а выходом - к управляющему входу шестого триггера, прямой выход которого подключен к первому входу третьего элемента ИЛИ. соединенного вторым входом с прямым выходом пятого синхронного D-тригге- ра, а выходом через третий элемент задержки - с вторым входом первого элемента И. подключенным через четвертый элемент задержки к обнуляющим входам пятого и шестого синхронных D-тригтеров,

выход второго элемента ИЛИ соединен с выходной шиной с тактовым входом седьмого синхронного D-триггера. управляющий вход которого объединен с управляющим

входом пятого синхронного D-триггеря и шиной единичного потенциала, а прямой выход - с управляющим входом восьмого синхронного триггера, соединенного своими тактовым и обнуляющим входами с пчтым и шестым выходами многофазного генератора импульсов соответственно, а прямым выходом - с обнуляющим входом седьмого синхронного D-триггера. третьим входом первого элемента ИЛИ и /правляющим входом счетчика импульсов, тактовый вход которого через пятый элемент задержки соединен с выходом первого элемента И Л И, а обнуляющий вход-с шиной установки исходного состояния устройства.

| Командровскэя И,А | |||

| и др | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| ычислительных систем | |||

| М.: Статистика | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Техническая документация | |||

| НПО: Энергия, 1987, с | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Пишущая машина | 1922 |

|

SU37A1 |

Авторы

Даты

1992-01-15—Публикация

1989-12-07—Подача