f12

Изобретение относится к импульсной технике и может быть использовано в синтезаторах частоты.

Цель изобретения повьшение быстродействия.

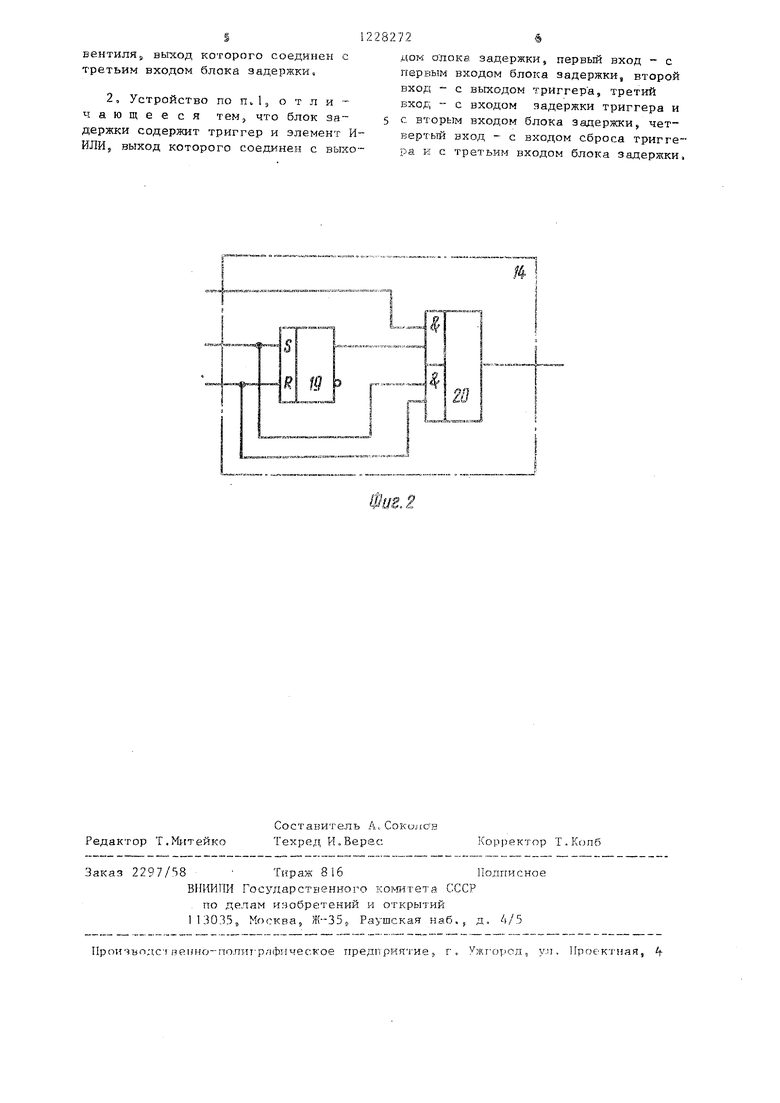

На фиг, приведена электрическая структурная схема делителя частоты с регулируемым коэффициентом делеаия; на фиг,2 - электрическая функциональная схема блока задержки,

Устройство содержит счетчик им- пу.пъсо-в . счетный вход которого соединен с входной шиной 2,, выходы - с первыми входами элементов 3-1, , . .,, 3-1„ 3--(i-i-),.., 3(N-1), 3-N и ,,.,, 4-N ИСКЛЮЧАЮЩЕЕ ИЛИ вторые входь которых соединены с шинами 5- 1,.:;, 5-1, 5-(i+l ),.„., 5--(N-), 5-N сигналов управления частотой и

длительностью выходньп импульсов,

Причем элементы (3-1 - 3-N) и ( - 4-N) объединены соответственно в пер вуро и вторую группы 6 и 7 элементов ИСКЛЮ ЧАЮЩЕЕ ИЛИ, выходы которых соединены с соответствующими входами пйового и второго элементов 8 и 9 И, выход второго элемента 9 соединен с первым входом первого триггера 10 выход которого соединен с выходной шиной 1I5 второй вход через первый и второй инверторы 12 и 13 - с входом сброса счетчика импульсов, блок 14 задержкиJ выход которого соединен с вторым входом первого триг гера 10 и со счетным входом второго триггера 155 выход которого соединен с первым входом вентиля 16s второй В2СОД которого соединен с шиной 17 релмма и с первым входом дополнительного элемента 18 ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с дополнительным входом первого элемента 8 И второй вход с входной шиной 2 и с первым входом блока 14 задержки, второй вход которого соединен с выходом первого элемента 8 И и с третьим входом вентиля 16, выход которого со- един:ен с третьим входом блока 14 задержки ,

Блок 14 задержки содержит триггер 19 и элемент 20 И-ШШ, выход которого соединен с выходом блока 14 за- дгржки, первый вход - с первым входом блока 14 задержки, второй вход - с выходом триггера 19, третий вход - с входам задержки триггера 19 и с вторым входом блока 14 задержки, чет- вертьй вход - с входом сброса триг

722

гера 19 и с третьим входом блока 14 задержки

Делитель частоты с регулируемым коэффициентом деления работает следующим образом.

Коэффициент деления устройства определяется набором логических уровней на шинах 5-1,, . . , 5-i, 5-(i 4- 4- 1),..., 5-(),, и 17. Если дня заданного коэффициента деления уровень на шине 17 соответствует уровню логической единицы, то сигнал с выхода вентиля 16 выключает блок 14 При этом сигналы., поступающие на вход блока 14 с выхода элемента 8,, передаются на выход блока 14 бе .э задержки,

Входные, импульсы с шины 2 поступают на счетный вход счетчика 1. При совпадении состояний соответствующих разрядов счетчика 1 с уровняг-ет, устнрювленными на шинах 5-i, 5-(i +

+ 1),, 5-(N-l), 5-N, триггер 10

выходным сигналом элемента 9 устанавливается в единичное состояние. При последующем счете входных импульсов счетчиком 1 происходит совпадение сигналов соответствующих его разрядов с уровнями, установленными на шинах -l,...j , 5-(1+1)5..., 5(N-1), 5-N, появляются единичные

уровни на выходах группы 6 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, и одновременное совпадение единичного уровня входных импульсов с логической единицей на шине 17, При этом формируется сигнал совп.здения на выходе элемента 8, который проходит без задержки блок 14 и сбрасывает триггер 10 и счетчик 1. Таким образом заканчивается цикл формирования одного периода выходной частоты.

Если для заданного коэффициента деле:ния уровень на шине 7 соответствует уровню логического нуля, то по- .рядок работы отличается от описанного. Предположим, что начальное состояние триггера 15 единичное, т.е. блок 14 задержки в начале работы выключен сигналом с выхода вентиля 16.

Установка триггера 10 в единичное состояние происходит аналогично. В дальнейшем . происходит совпадение сигналов соответствуюш 1Х разрядов счетчика 1 с уровнями, установленными на шинах 5-1 ,..., 5-i, 5-(i+ 1),. .. , 5-()5 5-N, и совпадение нулевого уровня на шине 2 с нулевым уровнем

на шине 17, которое происходит спустя половину периода сигнала на шине 2, в результате чего на дополнительном входе элемента 8 появляется единичный уровень. При этом формируется сигнал совпадения на выходе элемента 8, который проходит без задержки через блок 14, сбрасывает триггер 10, счетчик 1, а также изменяет состояние триггера 15 на нулевое. Нулевое состояние триггера 15 обеспечивает включение блока 14 задержки. Таким образом заканчивается первый цикл формирования периода выходной частоты.

Первое изменение состояния счетчика 1 после его обнуления происходит уже через половину периода частоты на шине 2, а не через период, как это было в первом цикле формирования. Для компенсации более раннего срабатывания счетчика I и используется блок 14

Установка триггера 10 в единичное состояние происходит так как и в первом цикле формирования периода выход- 25 ИСКЛЮЧАЮЩЕЕ ИЛИ, каждая из которых

ной частоты. Сигнал совпадения на выходе элемента 8 формируется как и в первом цикле формирования и поступае на вход блока 14. Последний обеспечивает задержку указанного сигнала на половину периода входной частоты, после чего происходит сброс триггера 10 и счетчика 1 в нулевое состояние, а также изменение состояния триггера 15 на единичное. Таким образом закан чивается второй цикл формирования периода выходной частоты,

Кадый нечетный цикл формирования выходной частоты аналогичен первому, четный - второму, а делитель обеспе- чивает нечетный коэффициент деления при скважности выходного сигнала, близкой к двум,

Работа блока 14 задержки сводится к следующему.

При наличии уровня логической единицы на третьем входе блока 14 (с выхода вентиля 16) триггер 19 находится в нулевом состоянии, и сигналы с второго входа блока 14 (с вы- хода элемента 8) проходят на выход блока 14 через элемент 20, При наличии уровня логического нуля на третьем входе блока 14 запрещается непосредственное прохождение на выход блока 14 с его второго входа, при этом снимается сигнал сброса с триггера 19. При появлении сигнала на

5

0

втором входе блока 14 триггер 19 переключается в единичное состояние. Однако присутствующий в этот момент на первом входе блока 14 уровень логического нуля (с шины 2) не позволяет появиться выходному сигналу на выходе блока 14. Через полпериода входной частоты на первом входе блока 14 появляется уровень логической единицы, что приводит к появлению сигнала на выходе блока 14, Появляющийся после этого сигнал на третьем входе блока 14 возвращает его в исходное состояние.

Формула изобретения.

1. Делитель частоты с регулируемым коэффициентом деления, содержащий счетчик импульсов, счетный вход которого соединен с входной шиной, выходы - с первыми входами соответствующих элементов ИСКПЮЧАКИЦЕЕ ИЛИ, первой и второй групп элементов

объединяет соответственно с первого по N-и и с i-го по N-и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, где , вторые входы которых соединены с соответствующими шинами сигналов управления частотой и длительностью выходных импульсов, выходы - с соответствующими входами соответственно первого элемента И и второго элемента И, выход которого соединен с первым вхо- дом первого триггера, выход которого соединек с выходной шиной, второй вход через соединенные последовательно первый и второй инверторы - с входом сброса счетчика импульсов, отличающийся тем, что, с целью повышения быстродействия, в него введены дополнительный элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй триггер,вентиль, шина режима и блок задержки, выход которого соединен с вторым входом первого триггера и со счетным входом второго триггера, выход которого соединен с первым входом вентиля, второй вход которого соединен с шиной режима и с первым входом дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ выход которого соединен с дополнительным входом первого элемента И, второй вход - с входной шиной и с первым входом блока задержки, второй вход которого соединен с выходом первого элемента И и с третьим входом

вентиляs выход которого соединен с третьим входом блока задержки.

2, Устройство по п.1

о т л и

чающееся тем, что блок задержки содержит триггер и элемент И- ИЛИ5 выход которого соединен с выхо1228272§

дом о лока задержки, первый вход - с первым входом блока задержки, второй вход - с выходом триггера, третий вход - с входом задержки триггера и 5 с вторым входом блока задержки, четвертый вход - с входом сброса триггера и с третьим входом блока задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1070694A1 |

| Устройство для коррекции числа импульсов по параметру | 1984 |

|

SU1228118A1 |

| Многоканальный преобразователь напряжения в код | 1982 |

|

SU1109900A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1981 |

|

SU1001534A1 |

| Устройство для управления тормозами колесного транспортного средства | 1981 |

|

SU1017550A1 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| Устройство для контроля частоты | 1980 |

|

SU995008A1 |

Изобретение может быть использовано в синтезаторах частоты. Цель изобретения - повышение быстродействия. Устройство содержит счетчик I импульсов, входную шину 2, элементы 3, 4 ИСКЛЮЧАЩЕЕ ИЛИ, шины 5 управления, группы 6, 7 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы В, 9 И, триггер 10, выходную шину П, инверторы 12, 13, блок 14 задержки, триггер 15, вентиль 16, шину 17 режима, элемент 18 ИСКЛЮЧАЮЩЕЕ ИЛИ. Повышение быстродействия достигается за счет введения элемента 18 ИСКЛЮЧАЮЩЕЕ ИЛИ, триггера 15, вентиля 16, блока i 4 задержки и новых функциональных связей. В .описании приведено выполнение блока 14 задержки. 1 з,п. ф-лы, 2 ил. с & (Л ю ND 00 vj to

Редактор Т.№гтейко

Составитель А,Соколов Техред И.Верес

Заказ 2297/58 Тираж 816Подггисное

ВННИПИ Государственного xoNMTeTa СССР

по делам изобретений и открытий 113035, Москва, ,. Раушская наб., д. 4/5

Произволе веино-гюлит рлфическое предприятие, г, Ужг-орсд, ул. Проектная,

Корректор Т.Колб

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1978 |

|

SU669487A1 |

| Делитель частоты следования импульсов с регулируемой длительностью импульсов | 1980 |

|

SU924868A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты импульсов с регулируемым коэффициентом деления | 1981 |

|

SU978357A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-30—Публикация

1984-10-24—Подача