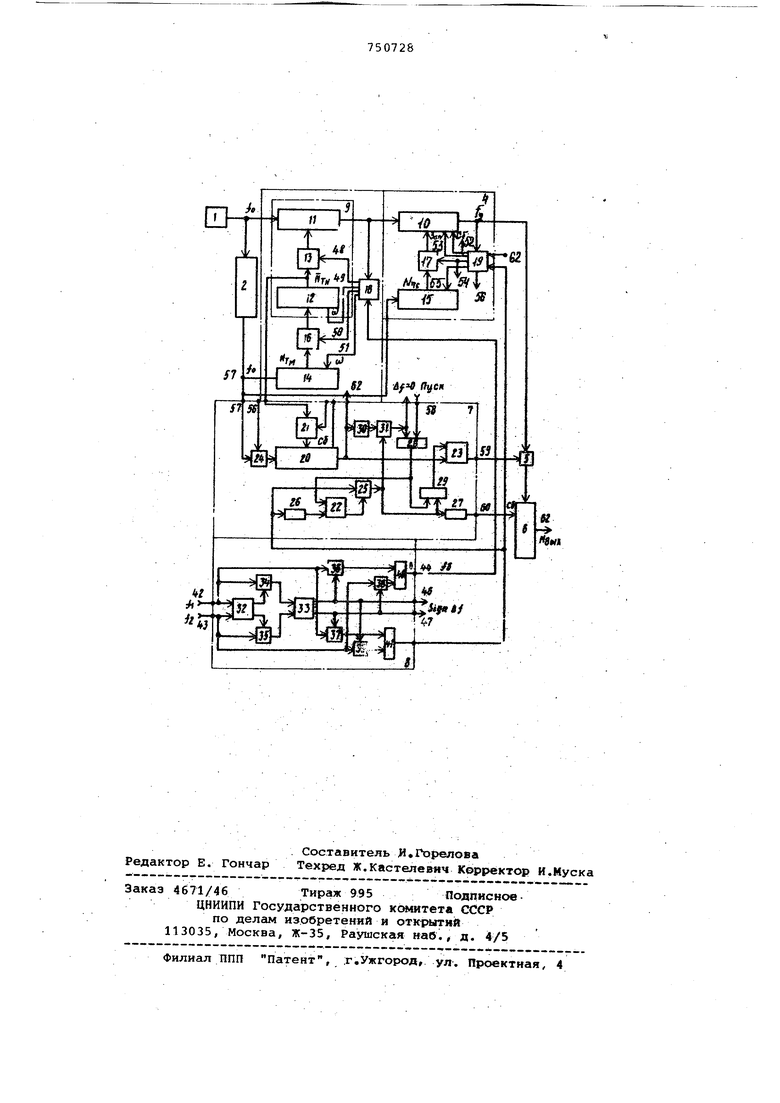

Изобретение относится к технике частотно-импульсного моделирования D авт атике, измерительной и вычис лительной технике и может найти при менение Л.1Я высокоточного измерения разности частот сигналов в быстродействующих цифровых системах управ ления и в информационнс-иэмерительных системах с частотно-импульсной входной информацией. Известны устройства для измерения разности частот входных сигналов с представлением результата в виде параллельного кода, построенные на дискретных элементах и счетных блоках l и 2 . Эти устройства имеют ограниченные точность, фун кциональные возможности и узкий диапазон возможного изменения входных частот. Наиболее близким к изоСретению является устройство для преобразования разности частотно-импульсных сигналов в код, содержащее блок уп равления, вентиль, счетчик результа та и генератор опорной частоты, при чем первый выход блока управления подключен к управляющему входу вентиля, а второй выход подключен к вх ду обнуления счетчика результата; счетный вход которого подключен к вь5ходу вентиля 3 . Это устройство, облсщая высоким быстродействием, имеет ограниченную точность, а также позволяет измерять только абсолютное значение разности сравниваемых частот, тогда как часто требуется также определение знака рассогласования и момента равенства по величине сравнивае лх смгнгиюв. Кроме того, использованные в известном устройстве блоки ограничивают возможный диапазон изменения сравниваемых частот, а также могут давать ложные результаты при совпадении во времени импульсов сравниваемых частот. Цель изобретения - увеличение точности, расширенле области применения, упрощение и уменьшение флуктуации мгновенного значения выходной частоты. Для этого в устройство введены неуправляемый делитель частоты, два множительно-делительных блока с элементами управления и логический блок, входы которого подключены к входным и1г1нам устройства, а выходы к первым входам соответствующих множительно-делительных блоков, вто рые входы которых подключены к выходу неуправляемо1о делителя частоты, вход которого, а та.еже третий вход первого множительно-делительно го блока подключены к выходу генера тора опорной частоты, причем выход первого множительно-делительного блока подключен к третьему входу вт рого множительно-делительного блока , выход которого подключен к импульсному входу вентиля счетчика результата, первый вход блока управле ния устройством подключен к второму выходу логического блока, второй вход блока управления подключен к вы ходу неуправляемого делителя, трети вход блока управления подключен к второму выходу первого множительноделительного блока, четвертый, пяты и шестой входы блока управления под ключены к соответствующим выходам элемента управления вторым множител но-делительным блоком, третий вход которого подключен к третьему выходу блока управления устройством, седьмой вход которого подключен к шине Пуск устройства. С целью упрощения блок управлени устройством содержит вычитающий сче чик, группу вентилей переноса кода. два триггера, два вентиля, два элемента задержки, два элемента ИЛИ, формирователь и элемент И, причем первый вход управления устрой ством подключен к импульсному входу первого вентиля, управляющий вход которого подключен к единичному выходу первого триггера, соответств щий вход которого через первый элем задержки подключен также к первому входу блока, выход первого вентиля подключен к первому входу элемента И, через второй элемент задержки второму выходу блока и через первый элемент ИЛИ - к нулевому входу второ го триггера, единичный выход которого Подключен к первому выходу бло ка, а единичный вход - к выходу вычитающего счетчика, счетный вход которого подключен к второму входу блока через второй вентиль, -управляю щий вход которого подключен к четвер тому входу блока, третий вход которо го подключен к в.ходам разрядов вычит щего счетчика через группу вентилей переноса кода, объединенные управляю щие входы которых подключены к пятому входу блока, шестой вход блока по ключен к входу обнуления вычитающего счетчика, выход которого подключен к третьему выходу блока и через формирователь - к второму входу элемент И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого подключен к седьмо му входу блока, а выход - к нулевом входу первого триггера и через первый элемент ИЛИ - к нулевому второго триггера. С целью уменьшения флуктуации мгновенного значения выходной частоты каждый множительно-делительный блок выполнен из счетчика, группы вентилей переноса кода, элемента управления и управляемого делителя частоты, содержащего, вычитающий счетчик и регистр памяти, соединенные разрядами через группу вентилей переноса кода, причем второй вход множительно-делительного блока подключен к счетному входу счетчика, выходы разрядов которого подключены через группу вентилей к управляющему входу управляемого делителя, счетный вход которого подключен к третьему входу множительно-делительного блока, а выход к первому .выходу множительно-делительного блока и к первому входу элемента управления, второй вход которого подключен к первому входу множительно-делительного блока, а выходы - к входам обнуления счетчика и регистра памяти, а также к объединенным управ-, ляющим входам соответствующих групп вентилей переноса кода, причем второй выход первого множительно-делительного блока является выходом разрядов регистра памяти. На чертеже дана функциональная блок-схема устройства для преобразования разности частотно-импульсных сигналов в код. Устройство содержит генератор 1 опорной частоты, неуправляемый делитель 2 частоты, два множительно(Делительных блока (МДБ) 3 и 4, вентиль 5, счетчик б результата, блок 7 управления устройством и логический блок 8 . Множительно-делительный блок 3(4) выполнен из управляемого делителя 9(10) частоты, содержащего вычитающий счетчик 11, регистр J.2 памяти и группу вентилей 13 переноса кода из счетчика 14(15), групп вентилей 16(17) переноса кода и элемента управления 18(19). Блок 7 управления устройством содержит вычитающий счетчик 20, группу вентилей 21, триггеры 22 и 23, вентили 24 и 25, элементы задержки 26 и 27, элементы ИЛИ 28 и 29, формирователь 30 и элемент И 31 . Логический блок 8 содержит триггеры 32 и 33, вентили 34-39 и элементы ИЛИ 40 и 41. В блоке 7 первый вход подключен к импульсному входу первого вентиля 25, управляющий вход которого подключен к единичному выходу первого триггера 22, соответствующий вход которого ч-ереэ первый элемент 26 задержки подключен также к первому входу блока 7. Выход первого вентиля 25 подключен к первому входу элемента И 31, через второй элемент 27 задержки - к второму выходу блока 7 и через первый элемент ИЛИ 29 - к нулевому входу второго триггера 23, единичный выход которого подключен к первому выходу блока 7, а единичный вход - к вых ду вычитающего счетчика 29. Счетный вход счетчика 29 подключен к второму входу блока 7 через второй вентиль 24, управляющий вход которого подключен к четвертому входу блока .7, Третий вход блока 7 подклю чен к входам разрядов вычитающего счетчика .20 через группу вентилей 21 переноса кода, объединенные упра ляющие входы которых подключены к пятому входу блока, шестой вход блока подключен к входу обнуления вычитающего счетчика, а выход последнего подключен к третьему выходу блока 7 и через формирователь 30 к второму входу элемента И 31, выход которого подключен к первому входу второго элемента ИЛИ 28, второй вход которого подключен к седьмому входу блока 7, а выход - к нулевому входу первого триггера 22, и через первый элемент ИЛИ 29 к нулевому входу второго триггера 2 В управляемом делителе 9 (10) МДБ 3 (4) вычитающий счетчик 11 сое динен разрядами через группу вентилей 13 переноса кода с регистром 12 памяти. Второй вход МДБ 3 (4) подключен к счетному входу счетчика 14 (15), выходы разрядов которого подключены через группу вентилей 16 (1 к,управляющему входу управляемого делителя 9 (10). Счетный вход делителя 9 (10) подключен к третьему входу блока 3 (4), а выход - к перв му выходу блока 3 (4) и к первому входу элемента управления 18 (19), второй вход которого подключен к первому входу блока 3 (4), а выходы - к входам обнуления счетчика 14 (15) и регистра 12 памяти, а так же к объединенным управляющим входа соответствующих групп вентилей 13 и 16 переноса кода, причем второй выход первого множит гльно-делительного блока 3 является выходом разря дов регистра 12 памяти и подключен входам группы вентилей 21 блока 7 Выход счетчика 11 делителя 9 бло ка 3 подключен к входу делителя 10 блока 4. В блоке 8 входные шины подключен к триггеру 32, выходы которого через вентили 34 и 35, вторые входы которых подключены соответственно к входным шинам блока 8, соединены с входами триггера 33, Выходы триггера 33 являются выходами блока 8 и соединены через вентили 36, 37, вто рые входы которых соединены с перво входной шиной,с элементами ИЛИ 40,4 подключенными вторыми входами к второй входной шине.Выходы элементов ИЛИ 40, 41 служат выходами блока 8. Входные шины 42 и 43 подключены к входам логического блока 8, выходы 44-45 которого подключены соответственно к вторым входам элементов 18 и 19 управления множительно-делительного блока, причем выход 45 подключен также к первому входу блока 7 управления устройством На выходах 46 и 47 логического блока 8 формируется сигнал знака измеряемого рассогласования algnuf . Входы 48-51 элемента 18 управления подключены соответственно к входам регистра 12 и вентилей 13 и 16, счетчика 14. Выходы 52-55 элемента 19 управления подключены соответственно к входам делителя 10, вентилей 17 и счетчиков 15. Выходы 52, 54 и 56 управляют также работой блока 7 управления и подключены к его четвертому, пятому и шестому входам. Выход 57 неуправляемого делителя 2 подключен к второму входу блока 7 и к вторым входам множительно-делительных блоков 3 и 4. На вход 58 блока 7 подается сигнал Пуск устройства. На выходе 59 блока 7 формируется сигнал, открывающий вентиль 5 на время, равное разности периодов сравниваемых сигналов. На выходе 60 блока 7 формируется сигнал обнуления счетчика 6 результата. На выходе 61 блока 7 формируется сигнал ui О при равенстве сравниваемых сигналов. Выход Ъ2 счетчика 20 подключен к третьему входу элемента 19 управления множительно-делительного блока. Выход генератора 1 подключен к счетным входам неуправляемого делителя 2 и управляемого делителя 9, выход которого подключен к первому входу элемента 18 управления и к счетному входу управляемого делителя 10, выход которого подключен к первому входу элемента 19 управления и через вентиль 5 - к счетному входу счетчика 6 результата. Выходы разрядов регистра 12 памяти в управляемом делителе 9 подключены через группу вентилей 21 к входам разрядов вычитающего счетчика 20 в блоке 7 управления устройством. стройство работает следующим образом. Входные сигналы f, и f., разность между которыми необходимо измерить, подаются на входы 42 и 43 логического блока 8, служащего для выделения на выходе 44 большего { j- , а на выходе 45 меньшего i из входных сигналов независимо от того, на какой из входов поступает больший сигнал. Триггер 32 и вентили 34 и 35 образуют схему вычитания импульсов. -При поступлении импульса на один :иэ ВХОДОВ 42, 43 триггер 32 переводится в состояние, при котором откр вается один из вентилей 34, 35. Импульсы через один из вентилей 34, 35 пройдет только в том случае, если на один из входов поступит подряд два импульса. Если же импульсы поступающие на разные входы, черенкуются, то через вентили 34, 35 они не проходят. Следовательно, схема реализует вычитатель импульсов двух входных последовательностей. Если fj f-J то разностными импульсами, прсхиедшими через вентиль 34, триггер 33 переводится в нулевое положение. При f;) f триггер переводится в единичное положение. Выходные сигналы с выходов 46 и 47 триггера 33 характеризуют знак разности sign Л BXOAHijix сигналов. В зависимости от наличия сигнала на том или ином выходе триггера 33 открываются либо вентили 36 и 39, либо вентили 37 и 38. Если f f-i - открываются вентили 36 и 39.При этом импульсы, следующие с /более высокой частотой f , прохо/ ят через вентиль 36 и эле мент ИЛИ 40 на выход 44, а импуль сы, следующие с меньшей тастотой f,j , проходят через вентиль 39 и эле мент ИЛИ 41 на выход 45. Если f то открываются вентили 37 И 38. Тогда импульсы большей частоты f проходя через вентиль 38 и элемент ИЛИ 40 на выход 44, а импульсы меньшей частоты f проходят через вентиль 37 и элемент ИЛИ 4 на выход 45. Таким образом, независ мо от того, на какой из входов 42 и 43 поступает большая частота, всегда на выходе 44 будет выделяться большая чаете а, а на выходе 45 меньшая. Использование логического блока позволяет определить знак разности cpaвнивae вг з{ сигналов, упростить блок 7 управлений и повысить надежность его работы. ИМПУЛЬСЫ большей частоты f сГ с вы хода 44 блока 8 поступают на первый вход первого множительно-делительиого блока 3, запуская его элемент управления 18. Шйпульсы Г(Юньшей частоты f с вихояа 45 блока 8 поступают н первый 9ХОД атороро МДБ 4, запуская ег элемент 19 управления. С выхода ге нератора 1 йМпуяьсы высокой опорной частоты fo поступают на счетные вхо ды неуправляемого делителя 2 частот с. постоянным коэффициентом пе:ресчет К и Управляемого делителя 9с переMeHHbfM коэффициентом деления Мт4и« определяемым в счетчике 14 (15). На выходе делителя 2 образуютсяимпульсы, следугаиие с частотой 0 0/ Импульсы, следующие с частотой FQ , поступают на счетные входы счетчиков 14 и 15 и через вентиль 24 - на счетный вход вычитакяцего счетчика 20 в блоке 7 управления. В счетчиках 14 и 15 эти импульсы суг-влируются за временные интервалы, равные соответственно периодам большей f,j- и меньшей f входных частот. Эти временные интервалы измерения формируются подачей на входы обнуления счетчиков 14 и 15 сигналов управления с элементов 18 и 19. В счетчике 14 в конце счетного интервала образуется код, пропорциональный периоду Т большей из входных частот «Г ,4° причем а в счетчике 15 образуется код, пропорциональный периоду Т меньшей из входных частот f M, т Прямые коды чисел в счетчиках 14 и 15 переписываются через открывае№ле сигналами управления с элементов 18 и 19 группы вентилей 16 и 17 и предварительно обнуленные регистры 12 памяти в управляе «лх делителях 9 и 10. Записанные в регистрах 12 памяти числа являются коэффициентами деления управляемах делителей 9 и 10. Каждым импульсом с выхода j-.eлителя, например 9 через элемент 18 открывается группа вентилей 13, через которую в вычитанмдий счетчик 11 пераписывается код Ы числа, хранящегося и регистре 12 памяти. После списывания импульсами генератора 1 числа, записанного в счетчике 11, на его выходе появляется импульс, повторяквдий процесс деления частоты в делителе 9. На выходе делителя 9 образуются импульсы, следующие с частотой т.е. множительно-делительный блок 3 {4) выполняет функцию умножителя большей из входных частот на постоянный йрэффициент К 1. Последовательность формирования С гналов управления элементов 18 управления следующая. При поступлении а первый вход элемента 18 импульСОЕ, следующих с частотой F, в К раз более высокой, чем частота следования импульсов fff, поступающих ка второй вход элемента 18, на его выходе 48 формируется сигнал, откры вающий группу вентилей 13, через ко торую в счетчик 11 записывается код регистра 12. При поступлении же каждого импульса с частотой следования f сГ в элементе 18 на выходах 49-51 формируются сигналы управления, которыми последовательно обнуляется регистр 12 памяти, затем переписывается через группу вентилей 16 код нового числа 4ijf из счетчика 14, и, наконец, обнуляется счетчик 14. Если им пульсы частот fi и f сг на входы элем та 18 приходят одновременно, то сигналы на выходах 49-51 задерживаются относительно сигнала на выходе 48- С выхода множительно-делительного блока 3 импульсы с частотой следования F поступают на счетный вход управляемого делителя 10 множи тельно-делител:,ного блока 4. В дели теле 10 эта частота делится на коэффициент деления ff, пспученный в счетчике 15 и пропорциональный пе оду меньшей из входных частот f. Частота следования импульсов на выходе множительно-делительного бло ка 4 будет равна P,±.Mj5.Li..i N-6 IO.-T . «о R о т.е. на выходе множительно-делитель ного блока 4 образуется частота, пр порциональная произведению входных частот. Импульсы, следукяцие с частотой F,j, поступают через ьантиль 5 на сче ный вход счетчика 6 результата, где они суь««1Ируются ыа, временном ин тервале (дт), равном абсолютному значению разности периодов сравниваемых частот, на котоЕ ай открывает ся вентиль 5 сигналом с выхода 59 блока 7 управления устройством. Множительно-делительные блоки 3 и 4, соединенные последовательно образуют умножитель двух входных частот, позволяющий за один период меньшей из входных частот сформиро вать на выходе частоту пропорциональную произведению двух входных частот., Соответствующим выбором опорной частоты fQ, коэффициента деления К делителя 2 и емкости счетчиков, схема позволяет получать результирующую частоту с высокой точностью без флуктуации мгновенного значени этой частоты при широком диапазоне изменения умножаемых частот. Изменение коэффициента К делителя 2 можно менять коэффициент пропорциональности результирующей частоты. Блок 7 управления устройством работает следующим образом. Сигналом Пуск, поступающим на вход 58 через элемент ИЛИ 28, триггер 22 устанавливается в нулевое положение, а затем через элемент ИЛИ 29 триггер 23 устанавливается в нулевое положениеi При этом с выхода 59 снимается сигнал, открывающий вентиль 5, и в счетчик 6 прекращается поступление импульсов частоты F с выхода множительноделительного блока 4. Цикл измерения начинается с поступления первого импульса меньшей входной частоты f, который пос- упает с выхода 45 блока 8 одновременно на первый вход блока 7 управления и на вход элемента 19 управления множительно-делительного блока 4. Так как триггер 22 установлен в нулевое положение, то первый импульс f, не преходит через вентиль 25, а задержанный элементом задержки 26 переводит триггер 22 в единичное положение. При этом единичным выходным сигналом триггер 22 открывает вентиль 25, через который проходят второй и все последующие импульсы частоты f. Первый импульс частоты f запускает элемент 19 управления, на выходах 52, 54 и 56 которого формируются сигналы, последовательно осуществляющие следующие .операции. Сначала снимается с выхода 56 сигнал, открываьяций вентиль 24, затем сигналом с выхода 52 обнуляется счетчик 20, затем сигналом с выхода 54 открывается группа вентилей 21, которые в счетчик 20 переписывается код , хранящегося в регистре 12 памяти, пропорционального периоду б ОЛЬ ate и входной частоты, ближайшего к первому импульсу частоты М Наконец, на выходе 56 появлягется сигнал, открывающий вентиль 24, через который на вычитающий вход счетчика 20 начинают поступать импульсы, следующие с частотой Гд с выхода неуправляемого делителя 2. Эти импульсы уменьшают записанное в счетчике число, после списывания которого на выходе 62 счетчика 20 появляется импульс,.поступающий на вход элемента 19, по которому снимается сигнал с вентиля 24 и прекра.щается поступление импульсов в счетчик. Так как число в счетчике Ы-, FJ,- уменьшается вычитыванием импульсов, следующих с частотой FQ , то импульс списывания этого числа .на выходе счетчика 20 появляется через временной интервал, равный периоду Тч, большей входной частоты. Импульс с вйхода счетчика 20 поступает на единичный вход тригг ра 23, который своим выходным сигна лом 59 открывает Вентиль 5, через к торый в счетчик 6 начинают поступат импульсы, cлeдv OfI иe с частотой F.J с выхода множительно-делительного блока 4, Второй входной импульс меньшей ч тоты ffj проходит через открытый вен тиль 25 и элемент .ИЛИ 29 на нулевой вход триггера 23. При этом снимаетс сигнал, открывающий вентиль 5, и пр ращается поступление импульсов в сч чик 6 . Так как счетчик 20 запускается п nepsblviy. импульсу меньшей входной ча тоты а выходной импульс счетчик 20 формируется через время -Т,, всег да меньшее, чем период Т меньшей частоты f(, то этот импульс всегда является раньше второго импульса f| Время между импульсом с выхода счет чика 20 и вторым импульсом входной частоты fyj, на которое открывается вентиль 5, равно абсолютной разност периодов (дТ) сравниваемых частот f и f(j независимо от того, на какой из входов устройства поступает большая частота. За это время л Т в счетчике будет записано число %..M-i i: f;f- i пропорциональное разности частот входных сигналов. Код этого числа после окончания счета импульсом, задержанным в элементе 27 задержки, переписывается в регистр памяти (на чертеже не показан), а затем производится обнуление счетчика б. Так как запуск счетчика 20 производится каждым следующим импульсом меньшей частоты f 1 , то запаздывание в определении разности периодов не превышает одного периода меньшей частоты. Если входные частоты f и f приближаются друг к другу, то при fj fi становятся равными и периоды Т Т, следовательно импульс с выхода счетчика 20 и импульс с выхода вентиля 25 поступают одновременно. Для учета скорости относительного изменения входных частот на выходе счетчика 20 устанавливается формирователь 30, расш{1ряющий импул Этот импульс подается на один вход элемента И 31, на другой вход которого подается импульс с выхода вентиля 25. При f f срабатывает эле мент И 31, на выходе 61 которого формируется сигнал Д f О момента совпадения по величине сравниваемых частот, который часто используют в системах управления и измерения. Этот сигнал устанавливает в нулевое положение триггеры 22 и 23, устраняя ложные срабатывания устройства при близких частотах и начиная новый цикл измерения при изменении знака рассогласования. Благодаря этому устройство может работать в режиме, сравнения в системах регулирования, когда рассогласование может менять знак или иметь очень малые значения. Введение последовательно соединенных МДБ, не имеющих флуктуации мгновенного значения частоты, позволяет повысить точность измерения и расширить диапазон изменения входных частот. Блок управления совместно с логическим блоком позволяет расширить функциональные возможности за счет, получения сигналов знака рассогласования и момента совпадения входных сигналов, а также повысить функциональную надежность и расширить область применения, так как устройство можно применять при любых соотношениях частот и фаз входных сигналов, а также при переменном знаке рассогласования. Благодаря возможности изменения коэффициента пропорциональности результирующего сигнала путем изменения коэффициента деления К делителя 2 устройствр можно использовать как пропорциональный цифровой регулятор с выходным сигналом в виде параллельного кода. Устройство можно использовать для измерения разницы частотно-имйульсных сигналов в быстродействующих и высокоточных информациогшоизмерительных системах и в качестве П-регулятора в цифровых системах управления, например, автоматизированным вентильным электроприводом. Формула изобретения 1, Устройство для преобразования разности частотно-импульсных сигналов в код, содержащее блок управления устройством, вентиль, счетчик результата и генератор опорной частоты, причем первый выход блока управления устройством подключен к управляющему входу вентиля, а второй выход подключен к входу обнуления счетчика результата, счетный вход которого подключен к выходу вентиля, отличающееся тем, что, с целью увеличения точности и расширения области применения, в него введены неуправляемый делитель частоты, два множительнй-делительных блока с элементами управления и логический блок, входы которого подключены к входным шинам устройства, а выходы к первым входам соответствующих множительно-делительных блоков, вторые входы которых подключены к выходу неуправля эмого делителя частоты, вход которого, а также третий вход первого множительно-делительного блока, подключены к выходу генератора опорной частоты, причем выход первого множительно-делительного бло ка подключен к третьему входу второго множительно-делительного блока, выход которого подключен к импульсному входу вентиля счетчика результата, первый вход блока управления устройством подключен к второму выхо ду логического блока, второй вход блока управления подключен к выходу неуправляемого делителя, третий вход блока управления подключен к второму выходу первого множительноделительного блока, четвертый, пятый и шестой входы блока управления подключены к соответствующим выходам элемента управления вторым множитель но-г,елительным блоком, третий вход которого подключен к третьему выходу блока управления устройством, седьмой вход которого подключен к шине Пуск устройства. 2. Устройство по п. 1, отлич ют е е с я тем, что, с целью упрощения, блок управления устройством содержит вычитающий счетчик, группу вентилей переноса кода, два триггера, два вентиля, два элемента задерж ки, два элемента ИЛИ, формирователь и элемент И, причем первый вход блока управления устройством подключен к импульсному входу первого вентиля управляющий вход которого подключен к единичному выходу первого триггера, соответствующий вход которого через первый элемент задержки подклю чен также к первому входу блока, выхол первого вентиля подключен к первому входу элемента И, через второй элемент задержки - к второму выходу блока и через первый элемент ИЛИ к нулевому входу второго триггера, единичный вБтход которого подключе к первому выходу блока, а единичны вход - к выходу вычитающего счетчика, счетный вход которого подключен к второму входу блока через второй вентиль, управляющий вход которого подключен к четвертому входу блока, третий вход которого подключен к входам разрял ть вычитающего счетчика через группу вентилей перс-носп кода, объединенные управляющие вхоы которых подключены к пятому входу блока, uiecTov4 вход блока подключе.к входу обнуления вычитающего счетчика, выход которого подключен к третьему выходу блока и через Формирователь - к второму входу элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого подключен к седьмому входу блока, а выход - к нулевому входу первого триггера и через первый элемент ШИ - к нулевому входу второго триггера. 3. Устройство по п. 1, отличающееся тем, что,с целью уменьшения флуктуации мгновенного значения выходной частоты, каждый множительно-делительный блок выполнен из счетчика, группы вентилей переноса кода, элемента управления и управляемого делителя частоты, содержащего вычитающий счетчик и регистр памяти, соединенные разрядами через группу вентилей переноса кода, причем второй вход множительно-делительного блока подключен к счетному входу счетчика, выходы разрядов которого подключены через группу вентилей к управляющему входу управляемого делителя, счетный вход которого подключен к третьему входу множительно-делительного блока, а выход - к первому выходу множительно-делительного блока и к первому входу элемента управления, второй вход которого подключен к первому входу множительно-делительного блока, а выходы - к входам обнуления счетчика и peiистра памяти, а также к объединенным управляющим входам соответствующих групп вентилей переноса кода, причем второй выход первого множительно-делительного блока является выходом разрядов регистра памяти. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 319938, кл. Н 03 К 25/00, 1972. 2.Авторское свидетельство СССР № 335685, кл. G 06 F 7/00, 1972. 3.Авторское свидетельство СССР .№ 364095, кл. Н 03 К 13/20, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1968 |

|

SU217047A1 |

| Устройство для преобразования суммы частотно-импульсных сигналов в код | 1976 |

|

SU657441A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Устройство для дифференцирования частоты повторения импульсов | 1974 |

|

SU525117A1 |

| Множительно-делительное устройство | 1981 |

|

SU982002A1 |

| Устройство для умножения частоты следования импульсов | 1974 |

|

SU517163A1 |

| Частотно-импульсное множительно-делительное устройство | 1975 |

|

SU556437A1 |

| Цифровой частотомер | 1975 |

|

SU783701A1 |

| Частотно-импульсное множительно-делительное устройство | 1983 |

|

SU1112364A1 |

Авторы

Даты

1980-07-23—Публикация

1976-07-12—Подача