f

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем автоматического управления, в частности при проектировании корректируемых компасов и других приборов и систем с минимальными весогабаритными характеристиками, но относительно невысоким быстродействием.

Цель изобретения - повышение точности устройства управления.

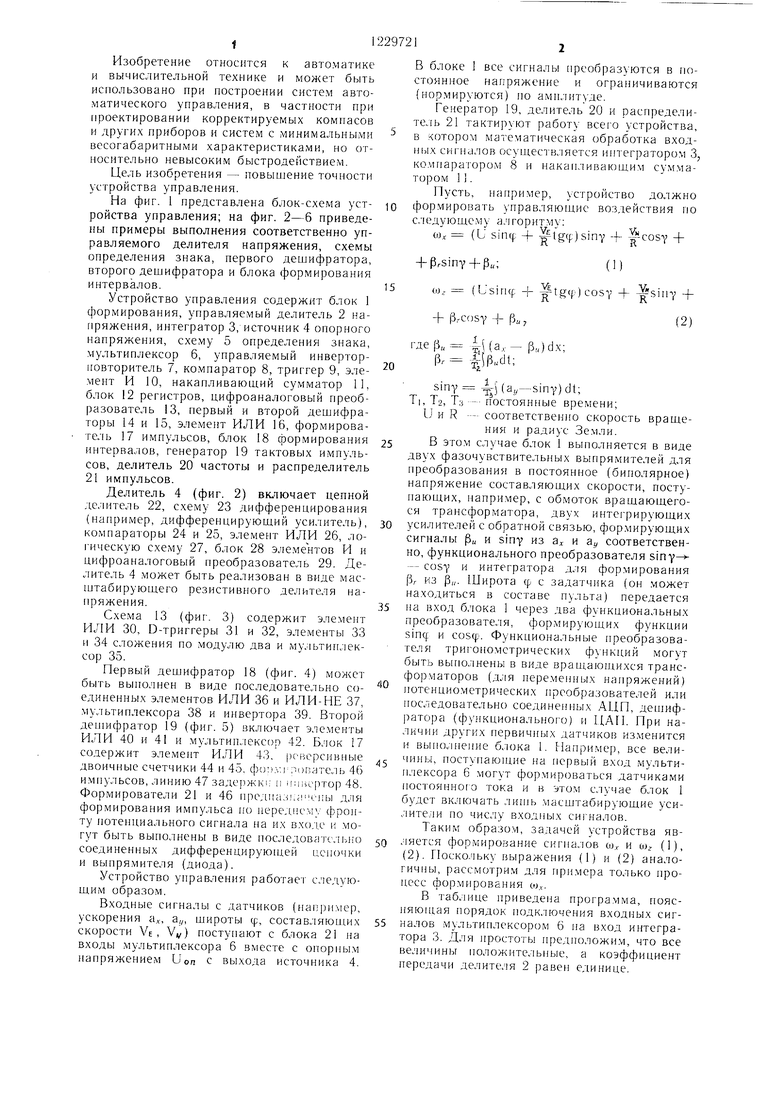

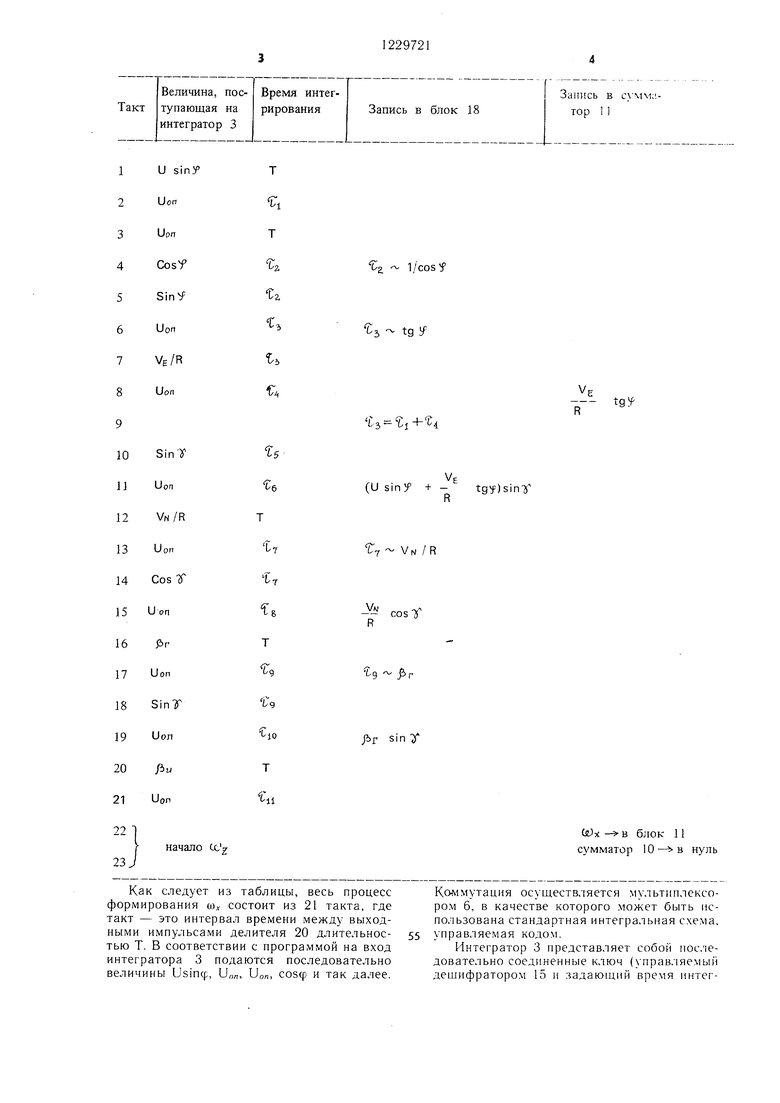

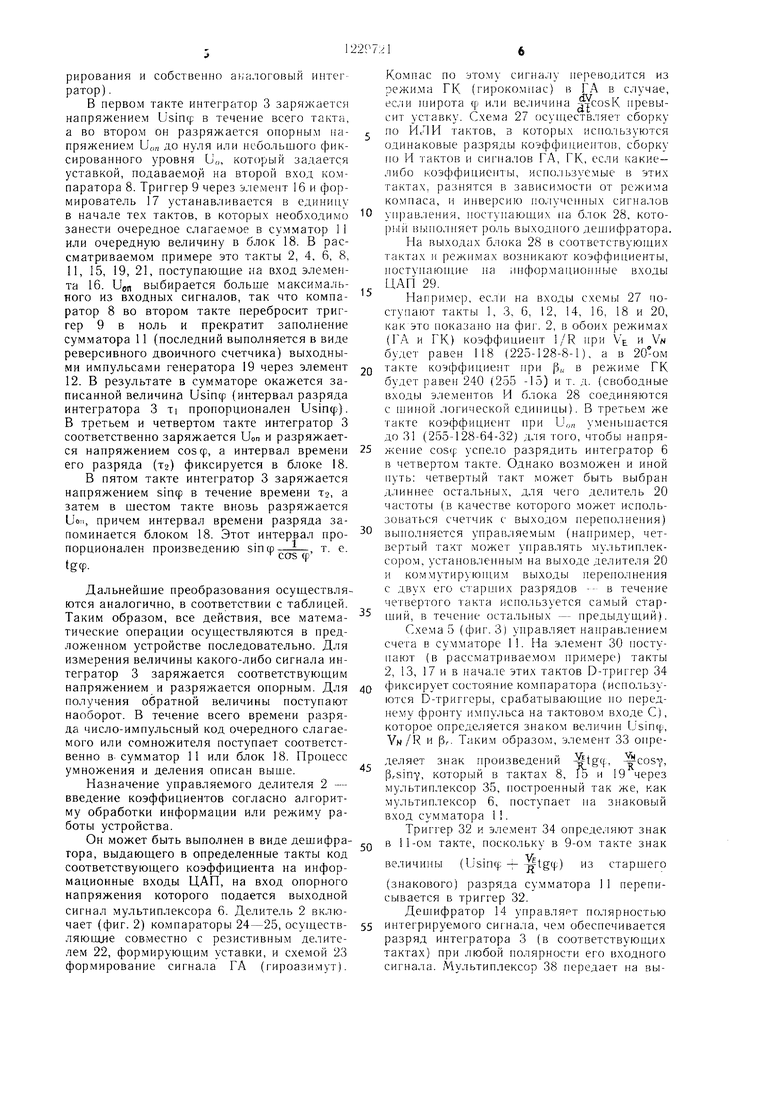

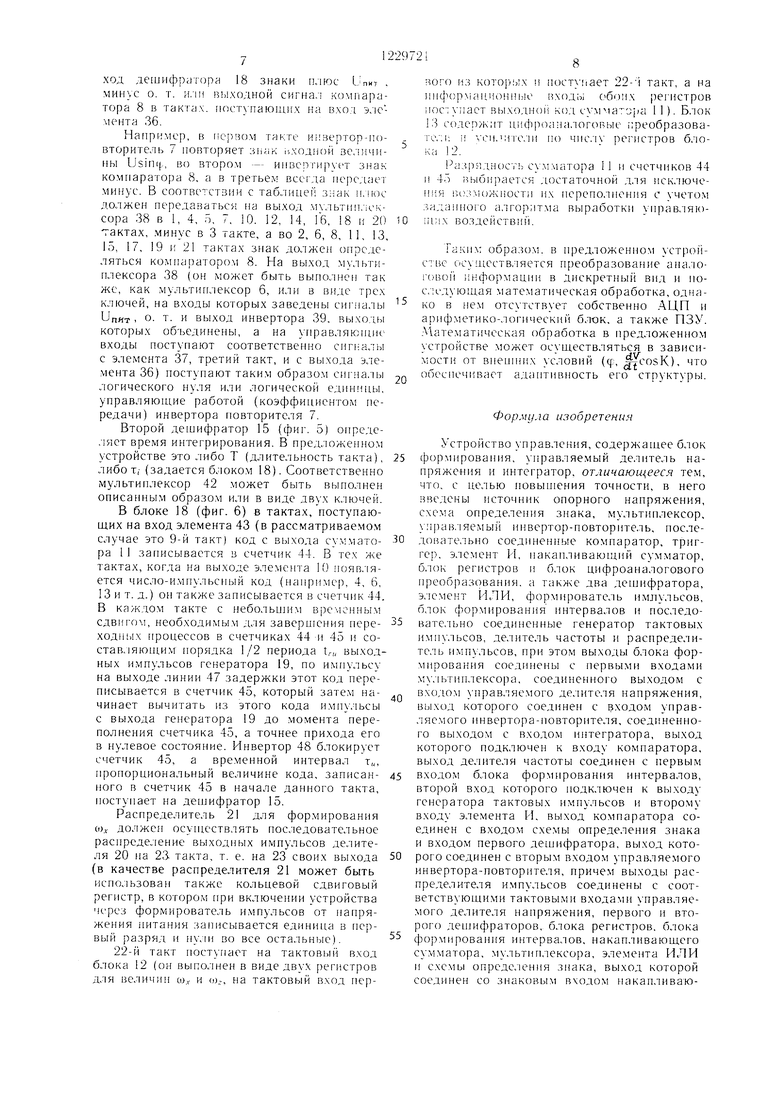

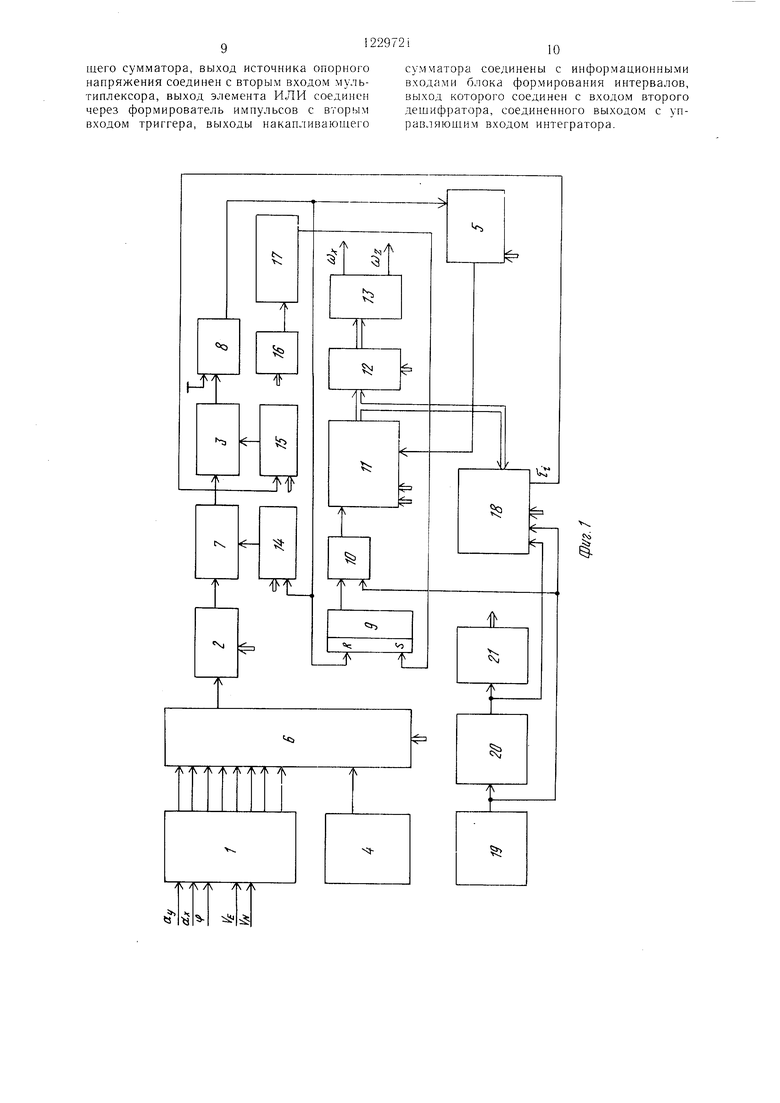

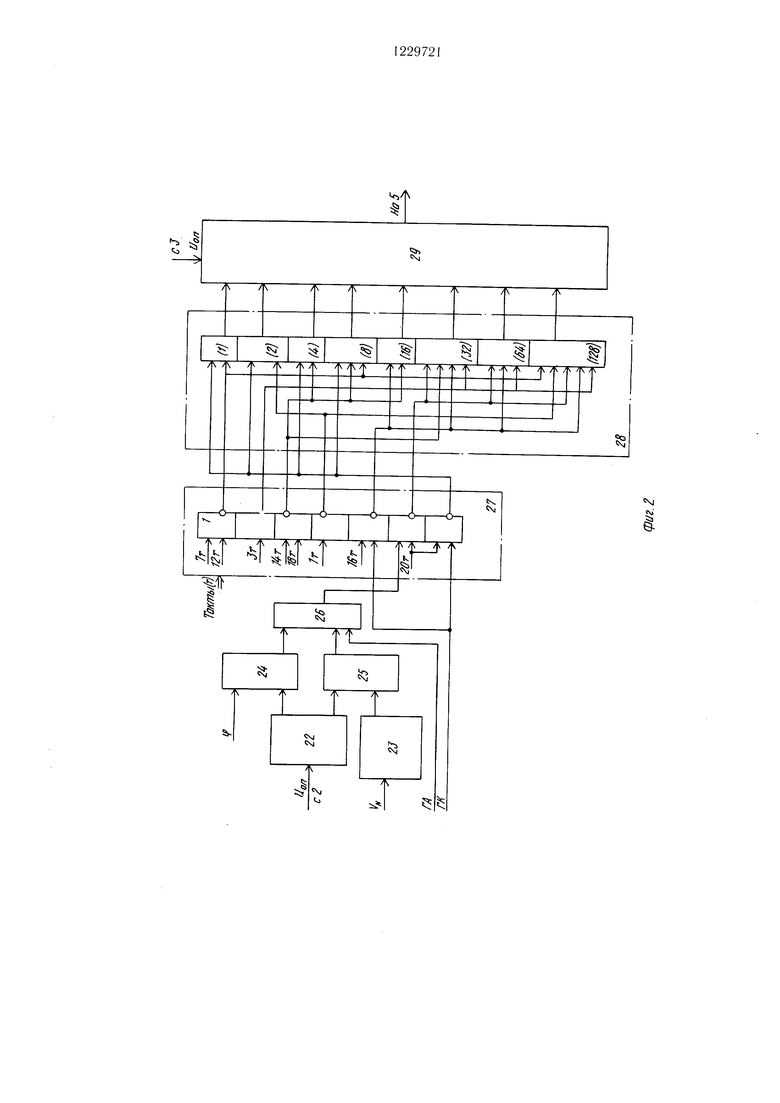

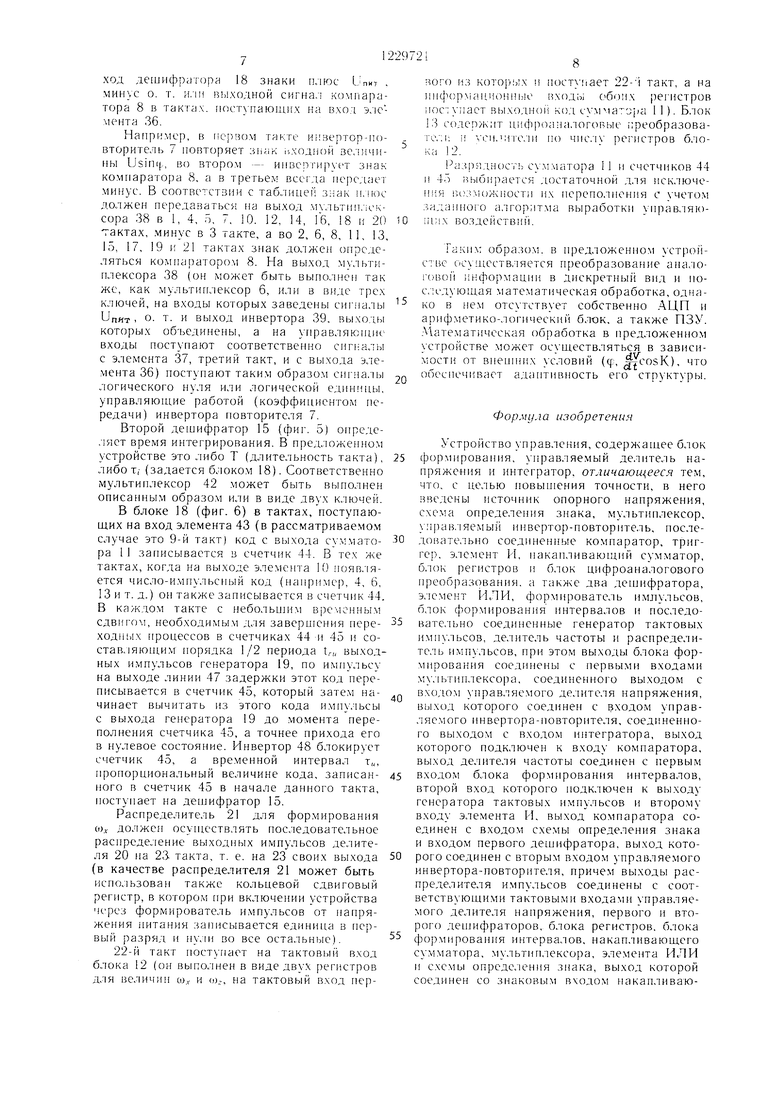

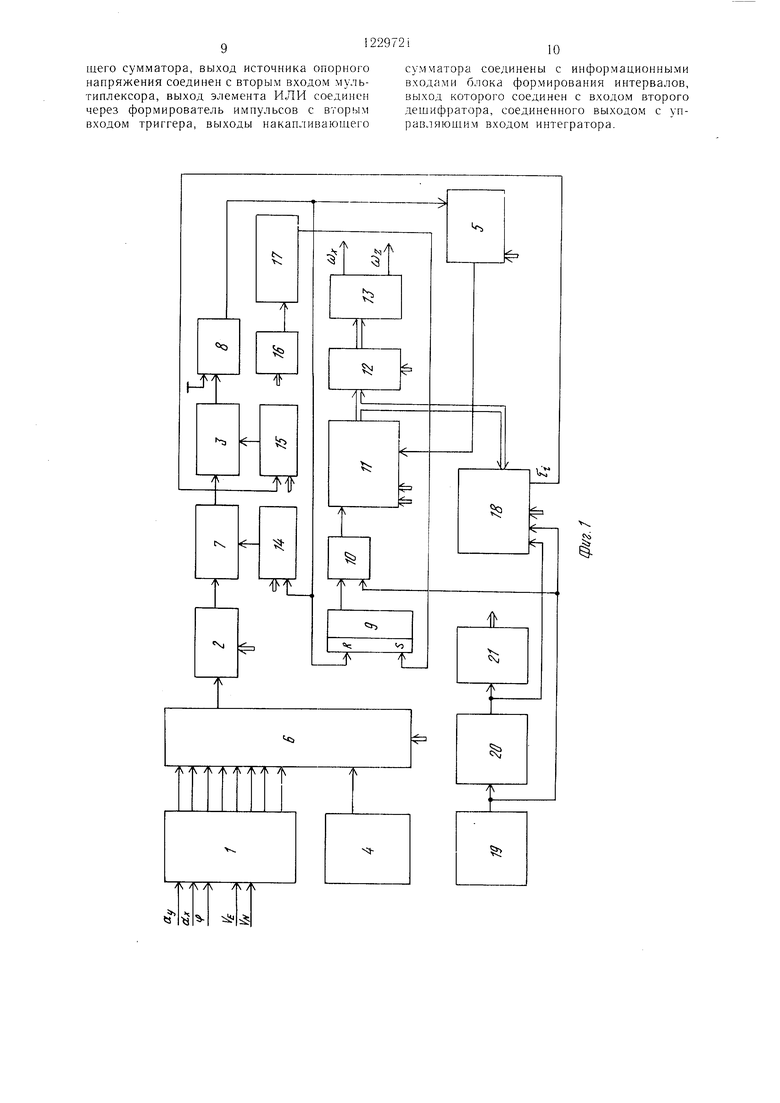

На фиг. 1 представлена блок-схема устройства управления; на фиг. 2-6 приведены примеры выполнения соответственно управляемого делителя напряжения, схемы определения знака, первого дешифратора, второго дешифратора и блока формирования интервалов.

Устройство управления содержит блок 1 формирования, управляемый делитель 2 напряжения, интегратор 3, источник 4 опорного напряжения, схему 5 определения знака, мультиплексор 6, управляемый инвертор- повторитель 7, компаратор 8, триггер 9, элемент И 10, накапливающий сумматор II, блок 12 регистров, цифроаналоговый преобразователь 13, первый и второй дешифраторы 14 и 15, элеме}1т ИЛИ 16, формирователь 17 импульсов, блок 18 формирования интервалов, генератор 19 тактовых импульсов, делитель 20 частоты и распределитель 21 импульсов.

Делитель 4 (фиг. 2) включает цепной делитель 22, схему 23 дифференцирования (например, дифференцирующий усилитель), компараторы 24 и 25, элемент ИЛИ 26, логическую схему 27, блок 28 элементов И и цифроаналоговый преобразователь 29. Делитель 4 .может быть реализован в виде масштабирующего резистивного делителя напряжения.

Схема 13 (фиг. 3) содержит элемент ИЛИ 30, D-триггеры 31 и 32, элементы 33 и 34 сложения по модулю два и мультигклек- сор 35.

Первый дешифратор 18 (фиг. 4) может быть выполнен в виде последовательно соединенных элементов ИЛИ 36 и ИЛ И-НЕ 37, мультиплексора 38 и инвертора 39. Второй дешифратор 19 (фиг. 5) включает элементы ИЛИ 40 и 41 и мультиплексор 42. Ехлок 17 содержит элемент ИЛИ 43. рс всрснвные двоичные счетчики 44 и 45. .тель 46 импульсов, линию 47 задержка i; инвертор 48. Формирователи 21 и 46 11ред:|а;-;..чы для формирования и.мпульса но нереднслг/ фронту ноте}П1иального сигнала на их вх),1,е и могут быть выполнены в виде последов 1Т лп но соединенных дифференцируюнхей цепочки и выпрямителя (диода).

Устройство управления работает следующим образом.

Входные сигналы с датчиков (например, ускорения a,v, а,,, широты ф, составляюпщх скорости VE , YV) поступают с блока 21 на входы мультиплексора 6 вместе с опорным напряжением Uon с выхода источника 4.

297212

В блоке 1 все сигналы преобразуются в постоянное напряжение и ограничиваются (нормируются) но амплитуде.

Генератор 19, делитель 20 и распредели- те.,1ь 21 тактируют работу всего устройства, - в котором математическая обработка вход- Н1)1х сигналов осуществляется интеграторо.м 3, колшаратором 8 и накапливающим сум.ма- тором 11.

Пусть, например, устройство должно 10 формировать управляющие воздействия по с, 1едуюшему алгоритму:

oj , (U sin(|.: + tg(p)sinY + I -cosY +

+ Prsin7+p,;;

15

. SUKp

tg(f))cosY + siii

-f p.cosY + fi« j

(2)

гдер, : .,:- PJdx; 3. - ф.М;

siny -(ay-S:my)di;

TI, TL), Тз - Постоянные времени;

и и R - соответственно скорость вращения и радиус Земли.

В это.м случае блок 1 вьпюлняется в виде

двух фазочувствительных выпрямителей для преобразования в постоянное (биполярное) напряжение составляющих скорости, поступающих, например, с обмоток вращающегося трансформатора, двух интегрирующих

усилителей с обратной связью, фор.мирующих сигналы PU и s mf из а и а,, соответственно, функционального преобразователя - cosy и интегратора для фор.мирования fir из р„. Широта ф с задатчика (он может находиться в составе пульта) передается

на вход блока 1 через два функциональных преобразователя, формирующих функции 51пф и со5ф . Функциональные преобразователя тригонометрических ф нкций могут быть выполнены в виде вращаюпшхся трансформаторов (для переменных напряжений) потенциометрических преобразователей или последовательно соедине1 пых АЦП, дещиф- ратора (функционального) и ЦАП. При наличии других первичных датчиков изменится и выиол 1епие блока 1. Например, все величины, поступаюнАие на первый вход мультиплексора 6 могут формироваться датчиками постоянного тока и в этом случае блок 1 будет включать . u-injb масштабирующие уси- ;1ите.;1и по числу входных сигналов.

Таким образом, задачей устройства является формирование сигналов oj,, и си (1), (2). riocKO. ibKy выражения (1) и (2) аналогичны, рассмотрим для при.мера только процесс фор.мирования сол-.

В таблице приведена программа, пояс- ,ая порядок подключения входных сигналов мультиплексором 6 на вход интегратора 3. Для простоты предположи.м, что все величины положительные, а коэффициент передачи делителя 2 равен единице.

и siny

Uon

(Jon

Cos f

Sinf

Uon

VE/R

Uon

1

г

i:

f,

ib C-,

Как следует из таблицы, весь процесс формирования w.v состоит из 21 такта, где такт - это интервал времени между выходными импульсами делителя 20 длительностью Т. В соответствии с программой на вход интегратора 3 подаются последовательно величины Usincp, LJo, Uon, созф и так далее.

€г 1/cosf

Cj - tg

V,

tg

t3

Коммутация осуществляется мультиплексором 6, в качестве которого может быть использована стандартная интегральная схема, управляемая кодом.

Интегратор 3 представляет собой последовательно соединенные ключ (управляемый дешифратором 15 и задающий время пнтегрирования и собственно аналоговый интег ратор).

В нервом такте интегратор 3 заряжается нанряжением и51Пф в течение всего такта, а во втором он разряжается опорным напряжением и,,,, до нуля или небольшого фиксированного уровня Ь „, который зад.ается уставкой, подаваемой на второй вход компаратора 8. Триггер 9 через элемент 16 и формирователь 17 устанав;1ивается в единицу в начале тех тактов, в которых необходимо занести очередное слагаемое в сумматор 11 или очередную величину в блок 18. В рассматриваемом примере это такты 2, 4, 6, 8, П, 15, 19, 21, поступающие на вход элемента 16. Uen выбирается больше максимального из входных сигналов, так что компаратор 8 во втором такте перебросит триггер 9 в ноль и прекратит заполнение сумматора 11 (последний выполняется в виде реверсивного двоичного счетчика) выходными импульсами генератора 19 через элемент 12. В результате в сумматоре окажется записанной величина Usintp {интервал разряда интегратора 3 Т| пропорционален из1пф). В третьем и четвертом такте интегратор 3 соответственно заряжается Uon и разряжается напряжением созф, а интервал времени его разряда (т2) фиксируется в блоке 18.

В пятом такте интегратор 3 заряжается напряжением 51Пф в течение времени тг, а затем в шестом такте вновь разряжается Uon, причем интервал времени разряда запоминается блоком 18. Этот интервал пропорционален произведению 51пф- -, т. е.

ccrs ф

1&ФДальнейшие преобразования осуш,ествля- ются аналогично, в соответствии с таблицей. Таким образом, все действия, все математические операции осуществляются в предложенном устройстве последовательно. Для измерения величины какого-либо сигнала интегратор 3 заряжается соответствующим напряжением и разряжается опорным. Для получения обратной величины поступают наоборот. В течение всего времени разряда число-импульсный код очередного слагаемого или сомножителя поступает соответственно В сумматор 11 или блок 18. Процесс умножения и деления описан выше.

Назначение управляемого делителя 2 - введение коэффициентов согласно алгоритму обработки информации или режиму работы устройства.

Он может быть выполнен в виде дешифратора, выдающего в определенные такты код соответствующего коэффициента на информационные входы ЦАП, на вход опорного напряжения которого подается выходной сигнал мультиплексора 6. Делитель 2 включает (фиг. 2) компараторы 24-25, осуществляющее совместно с резистивным делителем 22, формирующим уставки, и схемой 23 формирование сигнала ГА (гироазимут).

5

Компас по этому сигналу переводится из режима ГК (гирокомпас) в ГА в случае, если широта ф или ве;1ичина превысит уставку. Схема 27 осуществляет сборку по ИЛИ тактов, з которых используются одинаковые разряды коэффициентов, сборку по И тактов и сигналов ГА, ГК, если какие- либо коэффициенты, используемые в этих тактах, разнятся в зависимости от режима компаса, и инверсию полученных сигналов

0 управления, поступающих па блок 28, кото- рьлй . 1няет роль выходного дешифратора. На выходах блока 28 в соответствующих т.актах и режимах возьшкают коэффициенты, поступающие на ;п1формациоииые входы ЦАП 29.

Например, если на входы схемы 27 поступают такты 1, 3, 6, 12, 14, 16, 18 и 20, как это показано на фиг. 2, в обоих режимах (ГА и ГК) коэффицие1гг 1/R при V и н будет равен 118 (225-128-8-1), а в 20°ом

0 такте коэффициент при р„ в режиме ГК будет равен 240 (255 -15) и т. д. (свободные входы э;1ементов И блока 28 соединяются с шиной логической единицы). В третьем же такте коэффициент при U,, уменьшается до 31 (255-128-64-32) д.чя тог о, чтобы напря5 жепие созф успело разрядить интегратор 6 в четвертом такте. Однако возможен и иной путь: четвертый такт может быть выбран длиннее остальных, для чего делитель 20 частоты (в качестве которого может использоваться счетчик с выходом переполнения)

0 выполняется управляемым (например, четвертый тахт может управлять мультиплексором, установленным на выходе делителя 20 и коммутируюпшм выходы переполнения с двух его старших разрядов -- в течение четвертого такта используется самый стар5

5

шии, в течепие остальных - предыдущий).

Схема 5 (фиг. 3) управляет иаправлепие.м счета в сумматоре 11. На элемент 30 поступают (в рассматривае.мо.м примере) такты 2, 13, 17 и в начале этих тактов D-триггер 34

Q ф иксирует состояние компаратора (используются Ь-триггеры, срабатывающие но переднему фронту импульса на тактовом входе С), которое определяется знаком величин и51пф:, VN/R и р,. Таким образом, элемент 33 определяет знак произведений , , prSin, который в тактах 8, 15 и 19 через мультиплексор 35, построенный так же, как мультиплексор 6, поступает па знаковый вход сумматора 1.

Триггер 32 и элемент 34 опреде.чяют знак

Q в 11-ом такте, поскольку в 9-ом такте знак

величины

VE,

(и51Пф -f

из

старшего I перепи(знакового) разряда сумматора сывается в триггер 32.

Депшфратор 14 управлярт полярностью

5 интегрируемого сигна. 1а, чем обеспечивается

разряд интегратора 3 (в соответствующих

тактах) при любой полярности его входного

сигнала. Мультиплексор 38 передает на выход де1иифрутора 18 знаки плюс . пит . MHHVC о. т. или В1 ходной сигна/ компаратора 8 в тактах, поступающих на вход э. ю- мента 36.

Например, в IICJIBOM такте иизерторлю- вторитель 7 повторяет ьходь-ой величп- пы Us in If,, во втором - - и нвсп тирует знак компаратора 8, а в третьем все1 да передает минус. В соответстзии с таблицей знак плюс должен передаваться пз выход мультпп/1ск- сора 38 в 1,4, 5, 7, 10. 12, 14, 16, 18 и 20 тактах, .минус в 3 такте, а во 2, 6, 8, 11, 13, 15, 17, 19 и 21 тактах знак должен определяться компаратором 8. На выход мультиплексора 38 (он может быть выполнен так же, как мультиплексор 6, или в виде трех ключей, на входы которых заведены сиг. UnHT. о. т. и выход инвертора 39, выходы которых объединены, а на управляющие входы поступают соответственно сигь:аль с элемента 37, третий такт, и с выхода элемента 36) поступают таким образо.м сигналы логического нуля или логической единицы, управляющие работой (коэффипиентом передачи) инвертора повторителя 7.

Второй дешифратор 15 {фиг. 5) определяет время интегрирования. В предложепно.м устройстве это либо Т (длительность такта), либо т,- (задается блоком 18). Соответственно мультиилексор 42 .может быть выполнен описанным образо.м или в виде двух ключей.

В блоке 18 (фиг. 6) в тактах, поступающих на вход элемента 43 (в расс.матриваемом случае это 9-й такт) код с выхода сумматора 1 I записывается в счетчик 44. В тех же тактах, когда на выходе элемента 10 нояв.ля- ется число-импульспый код (нанример, 4, 6, 13 и т. д.) он также записывается в счетчик 44. В каждом такте с небольн им временным сдв11го, необходимым для завершения нере- ходных нроцессов в счетчиках 44 п 45 и состав, 1яюн1им порядка 1/2 периода t,-,, выходных импульсов генератора 19, по импульсу на выходе линии 47 задержки этот код переписывается в счетчик 45, который затем начинает вычитать из этого кода имну, 1ьсы с выхода генератора 19 до момента переполнения счетчика 45, а точнее прихода его в нулевое состояпие. Инвертор 48 блокирует счетчик 45, а вре.менной интервал т„, нропорцнональпый величине кода, записанного в счетчик 45 в начале данного такта, иоступает на дешифратор 15.

Распределитель 21 для формирования MX должен осун1еетвлять последовательное раснреде.гение выходных импульсов делителя 20 на 23 такта, т. е. на 23 своих выхода (в качестве распределителя 21 может быть испо:1ьзован также кольцевой сдвиговый регистр, в котором при включении устройства через формирователь импульсов от напряжения питания записывается единица в первый разряд и ну.1и во все остальные).

22-й такт поступает на тактовый вход блока 12 (он вьтолнен в виде двух региетров для величин ы и о),, на тактовый вход иер

вого из KOTOjJbix и постч-цает такт, а на ииф(}р.1ационн1,че пхо.;1,ы обоих регистров НОС :х паст выходно ко.ч cyNP-taT opa 11). Блок 13 содержит нифрог Налоговые преобразова- то, ;г. и си,1мте. 1И но чис. П регистров блока 12.

Разр;1дность с 1матора 11 и счетчиков 44 и 45 (выбирается достаточной для нск, 1юче- Н;я 1и}ЗА1ОЖНостн их перепо, 1пения с учетом задапно т; алгоритма выработки управ.тяю- iUJix воздействий.

образом, в нред, 1оженно.м строй- c lLic осчшествляется преобразование анало- 1-(1вой информации в дискретный вид и последующая математическая обработка, однако в нем отсутствует собственно АЦП и арифметико-логический блок, а также ПЗУ. Л1атематическая обработка в предложенном устройстве может осуществляться в зависи- iocTii от вненших условий (q;, cosK), что обеспечивает адаптивность его структуры.

5

0

5

0

5

0

5

Формула изобретения

Устройство управ,тения, содержан1ее блок фор.мироваиия, управляемый делитель напряжения и интегратор, отличающееся тем, что, с целью новьинения точности, в него введены источник опорного напряжения, схема определения знака, мультиплексор, управляемый инвертор-повторитель, последовательно соединенные компаратор, триггер, элемент И, паканливающпй сумматор, б,1ок регистров и блок цифроаналогового преобразования, а также два ден ифратора, элемент ПЛИ, формирователь имлульсов, блок формирования интервалов и последо- вате,тьно соединенные генератор тактовых и.мпу,1ьсов, делитель частоты и распределитель импульсов, при этом выходы б, юка формирования соединены с первыми входами му.1ьтиплексора, соединенного выходом с входом управляемого де.тителя напряжения, выход которого соединен с входом управ- ляе.мого инвертора-повторителя, соединенного выходом с входом интегратора, выход которого подключен к входу компаратора, выход делителя частоты соединен с первым входом блока формнрования интервалов, второй вход которого подключен к выходу генератора тактовых импульсов и второ.му входу элемента П, выход компаратора соединен с входом схемы определения знака и входом первого дешифратора, выход которого соединен с вторым входом управляемого инвертора-повторителя, причем выходы распределителя и.мпульсов соединены с соответствующими тактовыми входами управляемого делителя нанряження, первого и второго дешифраторов, блока регистров, блока фор.мирования интервалов, накап, 1ивающего сумматора, мультиплексора, элемента ПЛИ и схемы опреде,1енпя знака, выход которой соединен со знаковым входом накап,1ивающего сумматора, выход источника опорного нанряжения соединен с вторым входом мультиплексора, выход элемента ИЛИ соединен через формирователь импульсов с вторым входом триггера, выходы накапливающего

10

сумматора соединены с информационными входами блока формирования интервалов, выход которого соединен с входом второго дешифратора, соединенного выходом с управляющим входом интегратора.

tsl

/

jy

J

/V / / Л / f f J t J / A / / /

/ / /

j

.

A / / /

/ /

t«Nj

Nl

r

W

фиг.З

фиг. 5

фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик угловой скорости | 1985 |

|

SU1296949A1 |

| Регулятор | 1987 |

|

SU1462232A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Цифровой акселерометр | 1984 |

|

SU1242831A1 |

| Система управления | 1987 |

|

SU1444707A1 |

| Масштабирующий преобразователь | 1982 |

|

SU1038880A1 |

| Устройство для измерения произведения двух напряжений | 1983 |

|

SU1195265A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| ГЕНЕРАТОР СИГНАЛОВ СЛОЖНОЙ ФОРМЫ | 1991 |

|

RU2019908C1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU942095A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании систем автоматического управления и контроля. Цель изобретения - повышение точности. Для этого в систему, содержащую блок формирования, управляемый делитель напряжения и первый интегратор, введены второй интегратор, накапливающий сумматор, блок формирования интервалов и дешифратор. Это позволяет производить последовательную математическую обработку входных величин без использования собственно арифметического блока. Достоинством системы является оптимальное разделение функций между аналоговой и дискретной ее частями. 6 ил. го го со го

| Гироскопические приборы | |||

| / Под ред | |||

| Д | |||

| С | |||

| Пельпора, ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М.: Высшая школа, 1977, с | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

Авторы

Даты

1986-05-07—Публикация

1984-10-11—Подача