Изобретение относится к изображению информации и может быть использовано нри создании шкальных устройств для индикации с матричной адресацией индикаторных элементов.

Цель изобретения - новышение качества изображения за счет новьииения его контрастности.

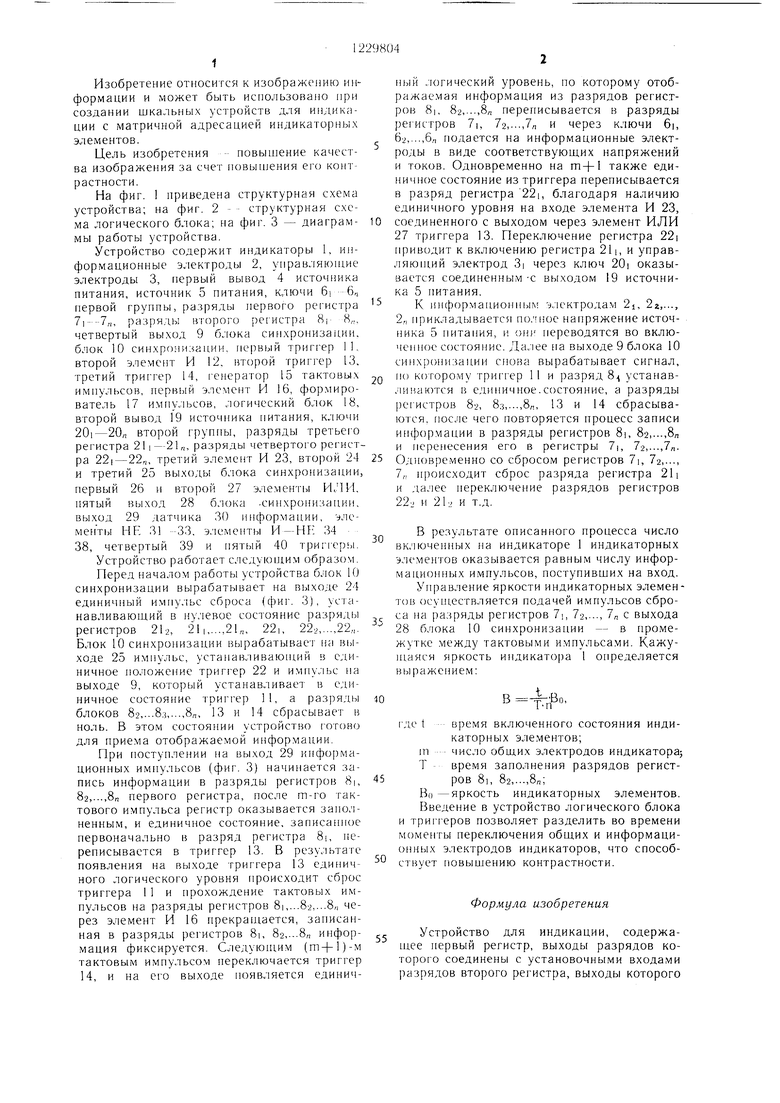

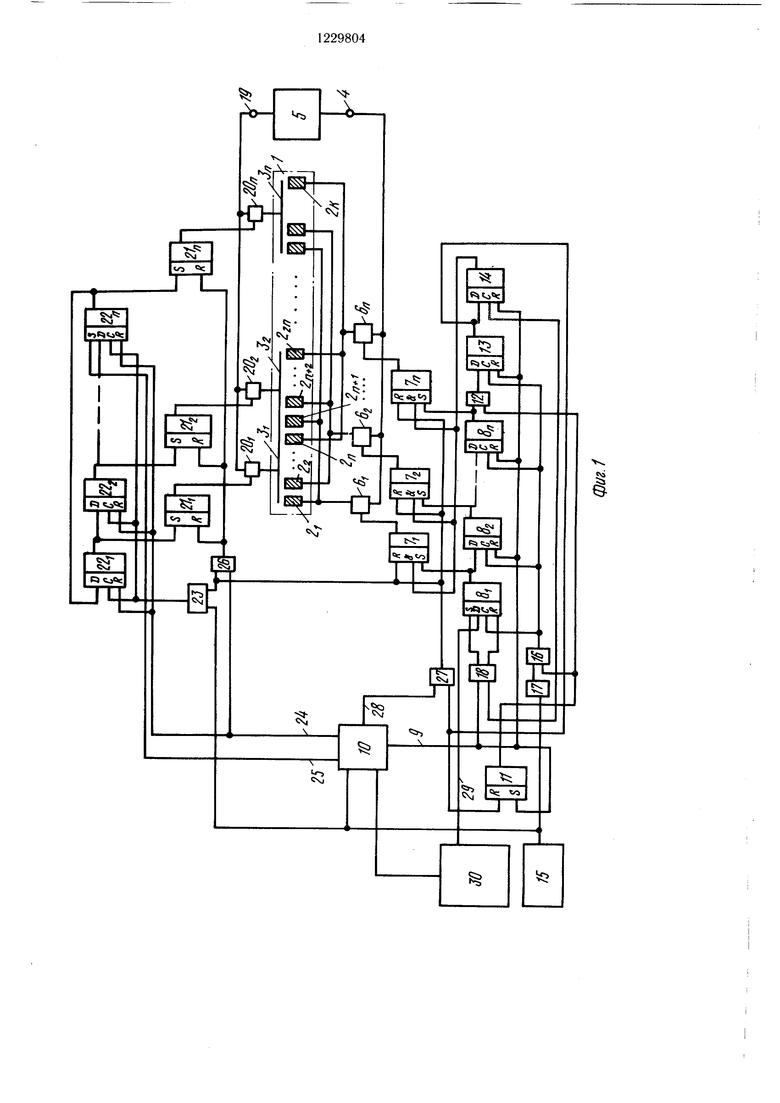

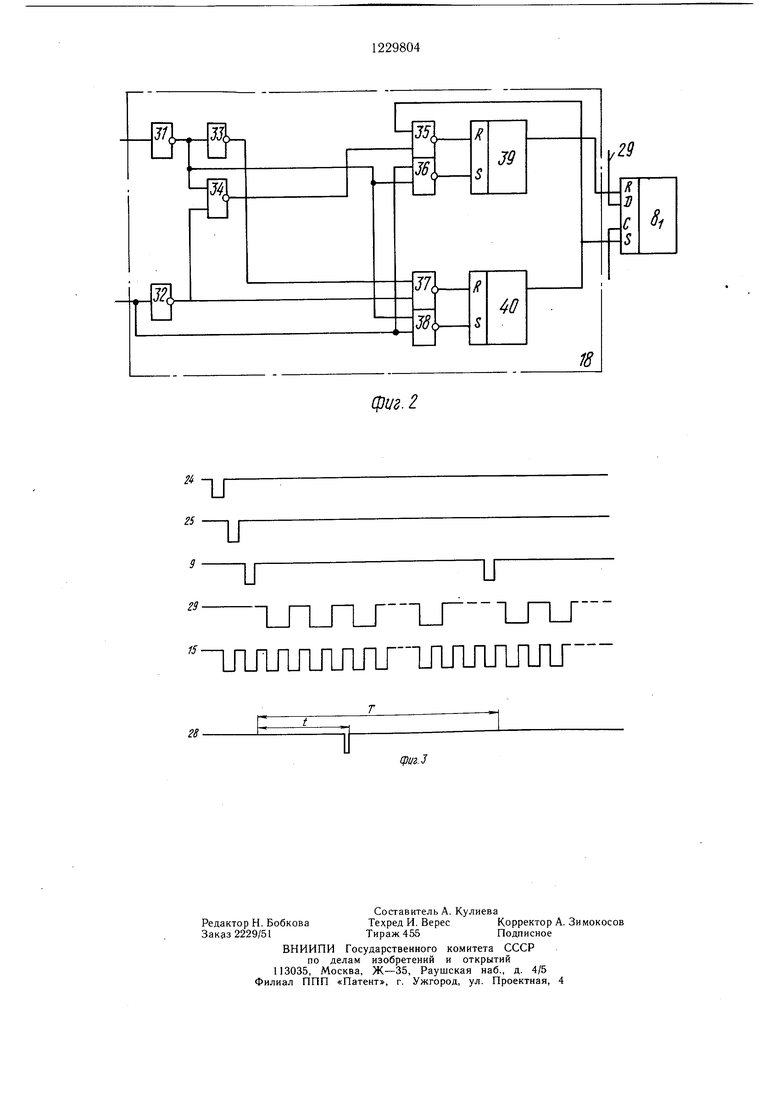

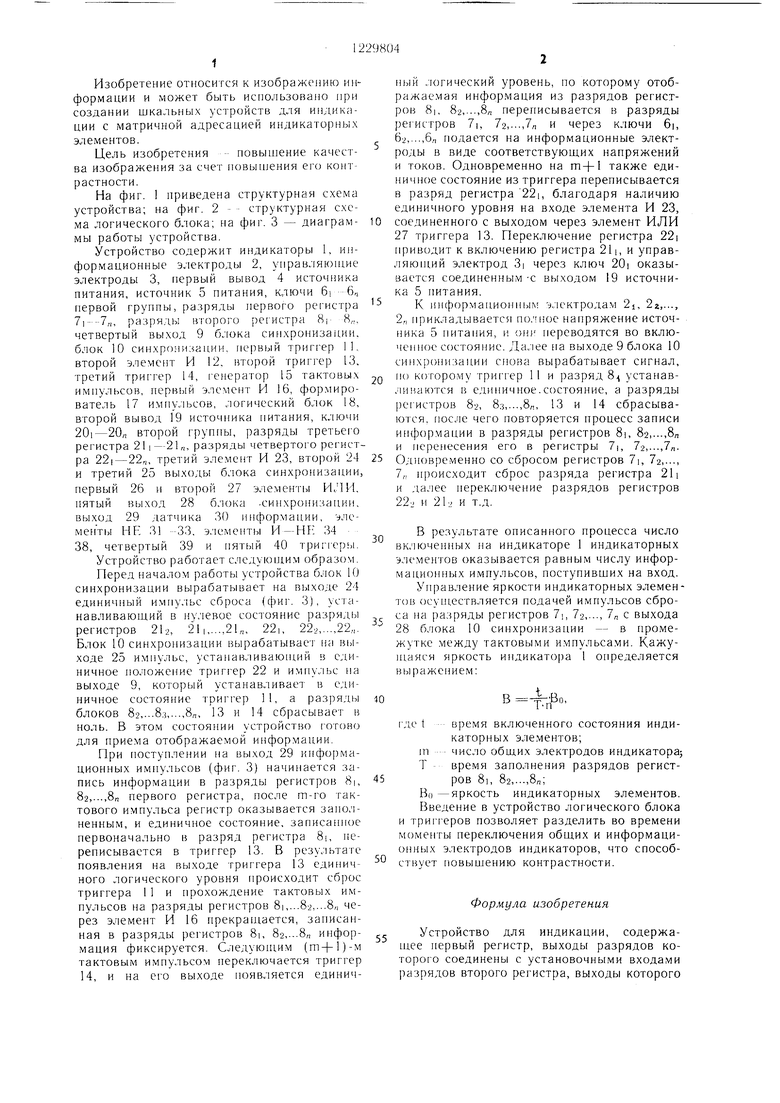

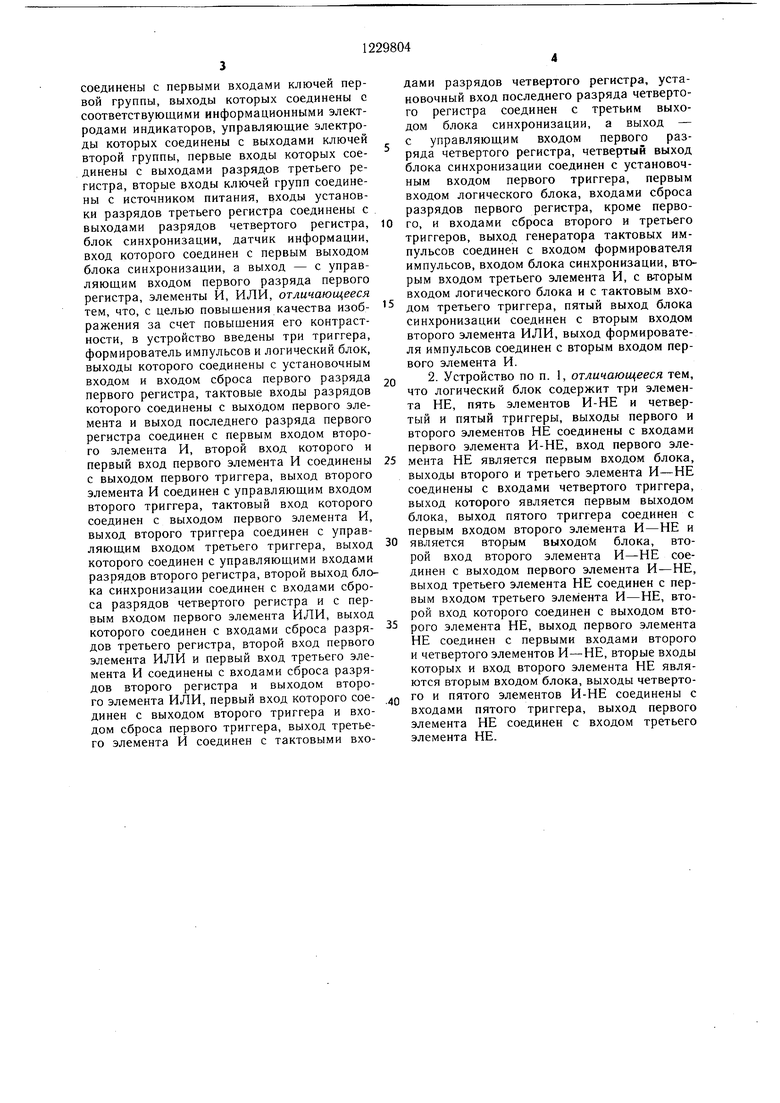

На фиг. 1 приведена структурная схема устройства; на фиг. 2 структурная схема логического блока; на фиг. 3 - диаграммы работы устройства.

Устройство содержит индикаторы 1, информационные электроды 2, угфавляк)Н1ие электроды 3, первый вывод 4 источника питания, источник 5 питания, ключи 6i 6„ первой грунпы, разряды первого ре1 истра 7|--7„, разряды второго рег истра 8i- 8,,. четвертый выход 9 блока синхронизации, блок 10 синхронизации, первый триггер II. второй элемент И 12, второй триггер 13, третий триггер 14, генератор 15 тактовых импульсов, первый элемент И 16, формирователь 17 и.мну.льсов, логический блок 18, второй вывОлЧ 19 источника питания, ключи 20i-20,1 второй группы, разряды третьего регистра 211-21„, разряды четвертого рег ист- ра 22|-22„, третий элемент И 23, второй 24 и третий 25 выходы блока синхронизации, первый 26 и второй 27 элементы ИЛИ, пятый выход 28 блока .синхронизации, выход 29 датчика 30 информации, эле- мен ты ИР 31 33, элементы И-НН 34 38, четвертый 39 и пятый 40 трип-еры.

Устройство работает следующим образом.

Перед началом работы устройства блок 10 синхронизации вырабатывает на выходе 24 единичный имг|у.-1ьс сброса (фиг. 3), устанавливающий в нулевое состояние разряды регистров 212, 2,,...,21,,, 22,, 22.,...,22,,. Блок 10 синхронизации вырабатывает на Biii- ходе 25 импульс, устанавливающий в единичное ноложепие триггер 22 и импу;1ьс па выходе 9, который устанавливает в единичное состояние триггер 11, а разряды блоков 82,...8з,...,8п, 13 и 14 сбрасывает в ноль. В этом состоянии устройство 1-отово для приема отображаемой информации.

При поступлении на выход 29 ипфо)ма- ционных импульсов (фиг. 3) начинается запись информации в разряды регистров 8|, 82,...,8„ первого регистра, после т-го гак- тового импульса регистр оказывается заполненным, и единичное состояние, записанное первоначально в разряд регистра 8i, переписывается в триггер 13. В результате появления па выходе триггера 13 единичного логического уровня происходит сброс триггера 11 и прохождение тактовых импульсов па разряды регистров 8|,...82,...8„ через элемент И 16 прекращается, заппсап- ная в разряды регистров 8i, 82,...8„ ипфор- мация фиксируется. Следующим (ш+1)-м тактовым импульсом переключается триггер 14, и на его выходе появляется единич

пый логический уровень, по которому отображаемая информация из разрядов регистров 8|, 82,...,8„ переписывается в разряды регистров 7|, 72,...,7„ и через ключи 6i, б2,...,6п подается на информационные электроды в виде соответствующих напряжений п токов. Одновременно на m+I также единичное состояние из триггера переписывается в разряд регистра 22|, благодаря наличию единичного уровня на входе элемента И 23, соединенного с выходом через элемент ИЛИ

27триггера 13. Переключение регистра 22i приводит к включению регистра 211, и управляющий электрод 3| через ключ 20| оказывается соединенным-с выходом 19 источника 5 питания.

К 1111()ормационпым электродам 2i, 2z,..., 2, прикладывается полное напряжение источ- пика 5 питания, и от- переводятся во включенное состояние. Далее на выходе 9 блока 10 сипхропизации спова вырабатывает сигнал, по которому триггер 1 1 и разряд 8 устанавливаются в единичное.состояние, а разряды регистров 82, 8.3,...,8л, 13 и 14 сбрасываются, после чего повторяется процесс записи ипформации в разряды регистров 8i, 82,...,8л п перенесения его в регистры 7|, 72,...,7„. Одновременно со сбросом регистров 7, 72,..., 7,, 11)оисходит сброс разря/аа регистра 211 и далее нереключение разрядов регистров 22. и 21. и т.д.

В результате описанного процесса число включепных на индикаторе 1 индикаторных элементов оказывается равным числу инфор- мапионщз1х импульсов, поступивщих на вход.

Управление яркости индикаторных элементов осун1ествляется подачей импульсов сброса на разряды регистров 7, 72,..., 7„ с выхода

28блока 10 синхрониза 1ии - в промежутке между тактовыми импульсами. Кажущаяся яркость индикато|)а 1 определяется выражепием:

В ,

| дс t время включенного состояния индикаторных элементов;

111 число общих электродов индикатора;

Т вре.мя заполнения разрядов регистров 8i, 82,...,8,,;

BO -яркость индикаторных элементов.

Введение в устройство логического блока и триггеров позволяет разделить во времени момепты переключения общих и информационных электродов индикаторов, что способствует гювыщению контрастности.

Формула изобретения

Устройство для индикации, содержа- пгее первый регистр, выходы разрядов которого соединены с установочными входами разрядов второго регистра, выходы которого

соединены с первыми входами ключей первой группы, выходы которых соединены с соответствующими информационными электродами индикаторов, управляющие электроды которых соединены с выходами ключей второй группы, первые входы которых соединены с выходами разрядов третьего регистра, вторые входы ключей групп соединены с источником питания, входы установки разрядов третьего регистра соединены с выходами разрядов четвертого регистра, блок синхронизации, датчик информации, вход которого соединен с первым выходом блока синхронизации, а выход - с управляющим входом первого разряда первого регистра, элементы И, ИЛИ, отличающееся тем, что, с целью повышения качества изоб- ражения за счет повыщения его контрастности, в устройство введены три триггера, формирователь импульсов и логический блок, выходы которого соединены с установочным входом и входом сброса первого разряда первого регистра, тактовые входы разрядов которого соединены с выходом первого элемента и выход последнего разряда первого регистра соединен с первым входом второго элемента И, второй вход которого и первый вход первого элемента И соединены с выходом первого триггера, выход второго элемента И соединен с управляющим входом второго триггера, тактовый вход которого соединен с выходом первого элемента И, выход второго триггера соединен с управляющим входом третьего триггера, выход которого соединен с управляющими входами разрядов второго регистра, второй выход блока синхронизации соединен с входами сброса разрядов четвертого регистра и с первым входом первого элемента ИЛИ, выход которого соединен с входами сброса разря- доз третьего регистра, второй вход первого элемента ИЛИ и первый вход третьего элемента И соединены с входами сброса разрядов второго регистра и выходом второго элемента ИЛИ, первый вход которого сое- динен с выходом второго триггера и входом сброса первого триггера, выход третьего элемента И соединен с тактовыми входами разрядов четвертого регистра, установочный вход последнего разряда четвертого регистра соединен с третьим выходом блока синхронизации, а выход - с управляющим входом первого разряда четвертого регистра, четвертый выход блока синхронизации соединен с установочным входом первого триггера, первым входом логического блока, входами сброса разрядов первого регистра, кроме первого, и входами сброса второго и третьего триггеров, выход генератора тактовых импульсов соединен с входом формирователя импульсов, входом блока синхронизации, вторым входом третьего элемента И, с вторым входом логического блока и с тактовым входом третьего триггера, пятый выход блока синхронизации соединен с вторым входом второго элемента ИЛИ, выход формирователя импульсов соединен с вторым входом первого элемента И.

2. Устройство по п. 1, отличающееся тем, что логический блок содержит три элемента НЕ, пять элементов И-НЕ и четвертый и пятый триггеры, выходы первого и второго элементов НЕ соединены с входами первого элемента И-НЕ, вход первого элемента НЕ является первым входом блока, выходы второго и третьего элемента И-НЕ соединены с входами четвертого триггера, выход которого является первым выходом блока, выход пятого триггера соединен с первым входом второго элемента И-НЕ и является вторым выходом блока, второй вход второго элемента И-НЕ соединен с выходом первого элемента И-НЕ, выход третьего элемента НЕ соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом второго элемента НЕ, выход первого элемента НЕ соединен с первыми входами второго и четвертого элементов И-НЕ, вторые входы которых и вход второго элемента НЕ являются вторым входом блока, выходы четвертого и пятого элементов И-НЕ соединены с входами пятого триггера, выход первого элемента НЕ соединен с входом третьего элемента НЕ.

24

и

25

nj

29 1 Л

15

тшш т ши1Г

фиг. 2

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения графической информации | 1989 |

|

SU1767520A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

| Устройство для индикации | 1981 |

|

SU1012328A1 |

| Устройство для индикации | 1978 |

|

SU734755A1 |

| МНОГОМОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ТЕКСТОВОЙ И ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1992 |

|

RU2037885C1 |

| Устройство для отображения информации | 1987 |

|

SU1476523A1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Устройство для контроля группы цифровых узлов | 1987 |

|

SU1534461A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Двухканальное устройство для сопряжения ЭВМ | 1989 |

|

SU1735860A1 |

Изобретение относится к отображению информации и может быть использовано при создании шкальных устройств для индикации с матричной адресацией индикаторных элементов. Целью изобретения является повышение качества изображения за счет увеличения его контрастности. Поставленная цель достигается введением в устройство логического блока, трех триггеров и формирователя импульсов. Введение указанных блоков позволяет разделить во времени моменты переключения общих и информационных электродов индикаторов, что способствует повышению контрастности. 1 з.п. ф-лы, 3 ил. ьэ 1чЭ со оо

| Устройство для индикации | 1978 |

|

SU819817A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Патент США № 4060801, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1986-05-07—Публикация

1984-08-02—Подача