Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для контроля экспоненциальных переходных процессов в различных технологических объектах, например, энергоблоках электростанций.

Известно устройство для допускового контроля параметров объектов, содержащее три преобразователя аналог-длительность импульса, блок сравнения, блок индикации, блок синхронизации, блок уставок, распределитель импульсов, сумматор, регистр сдвига, два триггера, два элемента ИЛИ, четыре элементе И и элемент НЕ,

Недостатком этого устройства является низкое быстродействие контроля установившихся значений возрастающих экспоненциальных процессов, так как контроль

осуществляется после завершения переходного процесса.

Известно также устройство для контроля экспоненциальных процессов, содержащее регистр сдвига, сумматор, блок управления, два пороговых элемента, два генератора одиночных импульсов, три триггера, три элемента И, элемент ИЛИ-НЕ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента задержки.

Недостатком этого устройства является ограничение его функциональных возможностей контролем только затухающих экспоненциальных процессов и отсутствие средств контроля возрастающих экспоненциальных процессов.

Наиболее близким техническим решением к изобретению является устройство

VI

U) hO СО CJ

для контроля экспоненциальных процессов, содержащее три пороговых элемента, преобразователь аналог-длительность импульса, три генератора одиночных импульсов, три триггера, два регистра сдвига, два сумматора-вычитателя, делитель частоты, счетчик, блок индикации, восемь элементов И, пять элементов ИЛИ, элемент задержки, три элемента индикации и блок синхронизации.

Недостатком этого устройства является относительная сложность его реализации.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что устройство для контроля экспоненциальных процессов, содержащее преобразователь аналог-длительность импульса, с первого по третий генераторы одиночных импульсов, с первого по третий триггеры, первый и вто- рой регистры сдвига, сумматор-вычитатель, делитель частоты, счетчик, блок индикации, с первого по восьмой элементы И, с первого по пятый элементы ИЛИ, с первого по третий элементы индикации, блок синхрониза- ции и с первого по третий пороговые элементы, входы опорных напряжений которых являются с первого по третий входами задания порогов устройства, информационные входы с первого по тре- тий пороговых элементов соединены с входом преобразователя аналог-длительность импульса и подключены к информационному входу устройства, выходы с первого по третий пороговых элементов соединены со- ответственно с входами запуска с первого по третий генераторов одиночного импульса, тактовые входы которых соединены с управляемым выходом синхронизации блока синхронизации, выход первого генерато- ра одиночного импульса соединен с первым входом первого элемента ИЛИ, и входом установки первого триггера, выход которого соединен с входом первого индикатора и первыми входами шестого и седьмого эле- ментов И, выход второго генератора одиночного импульса соединен с входом установки второго триггера, прямой выход которого соединен с входом второго индикатора и первым входом второго элемента И, инверсный выход второго триггера соединен с вторым входом шестого элемента И, а вход сброса - с входом сброса первого триггерам выходом третьего элемента ИЛИ, первый вход которого соединен с выходом третьего генератора одиночного импульса и входом установки третьего триггера, прямой выход которого соединен с входом третьего индикатора и первым входом восьмого элемента И, выход которого соединен

со счетным входом счетчика,-выходы которого соединены с входами блока индикации, а вход установки - с выходом сброса блока синхронизации, входом блокировки первого регистра сдвига, входом установки делителя частоты, вторым входом третьего элемента ИЛИ, первым входом четвертого элемента ИЛИ, выход которого соединен с входом сброса третьего триггера, синхров- ходы первого и второго регистров сдвига соединены с выходом синхронизации блока синхронизации, первый информационный вход первого регистра сдвига соединен с общей шиной, выход второго регистра сдвига соединен с первым суммирующим входом сумматора-вычитателя, второй суммирующий вход которого соединен с выходом второго элемента ИЛИ, а выход переноса соединен с первым входом третьего элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, второй вход восьмого элемента И соединен с выходом синхронизации частотой f/2n блок синхронизации (где п - количество разрядов первого и второго регистров сдвига) и вторым входом седьмого элемента И, выход преобразователя аналог - длительность импульса соединен с первым входом пятого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, инверсный выход синхронизации частотой f/2n соединен с вторым входом второго элемента И и третьим входом седьмого элемента И, выход которого соединен с информационным входом делителя частоты, выход пятого элемента 1ЛИ соединен с входом режима суммирования сумматора-вычитателя, второй вход третьего элемента И соединен с выходом синхронизации частотой f/n блока синхронизации, выход делителя частоты соединен со вторым входом первого элемента ИЛИ, выход которого соединен с входом запуска преобразователя аналог-длительность импульса, оно содержит элемент ИЛИ-НЕ первый, второй входы и выход которого соединен соответственно с выходом пятого элемента ИЛИ, вторым входом третьего элемента И, входом режима вычитания сумматора-вычитателя, выход которого соединен с информационным входом первого регистра сдвига, выход которого соединен с информационным входом второго регистра сдвига, первым входом четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, а второй вход - с управляющим входом блокировки второго регистра сдвига, прямым выходом третьего триггера и первым входом пятого элемента ИЛИ, второй и третий входы которого соединены с выходами соответственно второго

и первого элементов И, первый и второй входы первого элемента И соединены соответственно с выходом шестого элемента И и выходом синхронизации частотой f/2n блока синхронизации, соединенным с вторым входом пятого элемента И, третий вход которого соединен с вторым входом восьмого элемента И, третий вход второго элемента ИЛИ соединен с выходом делителя частоты.

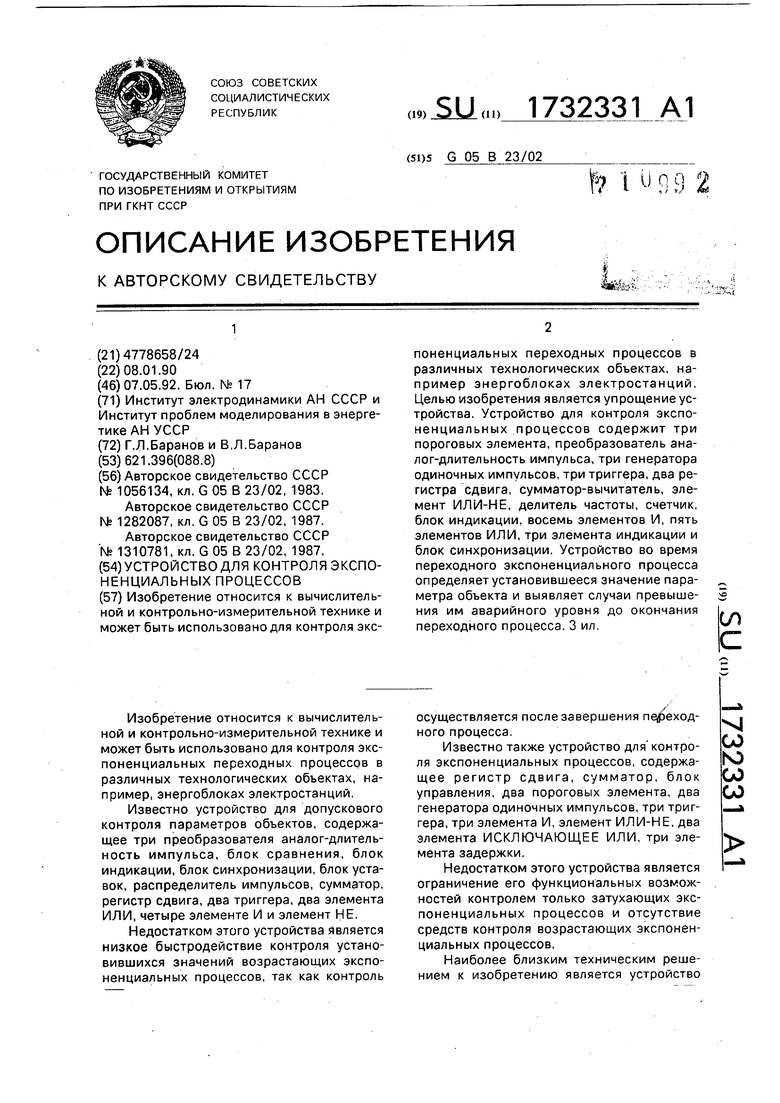

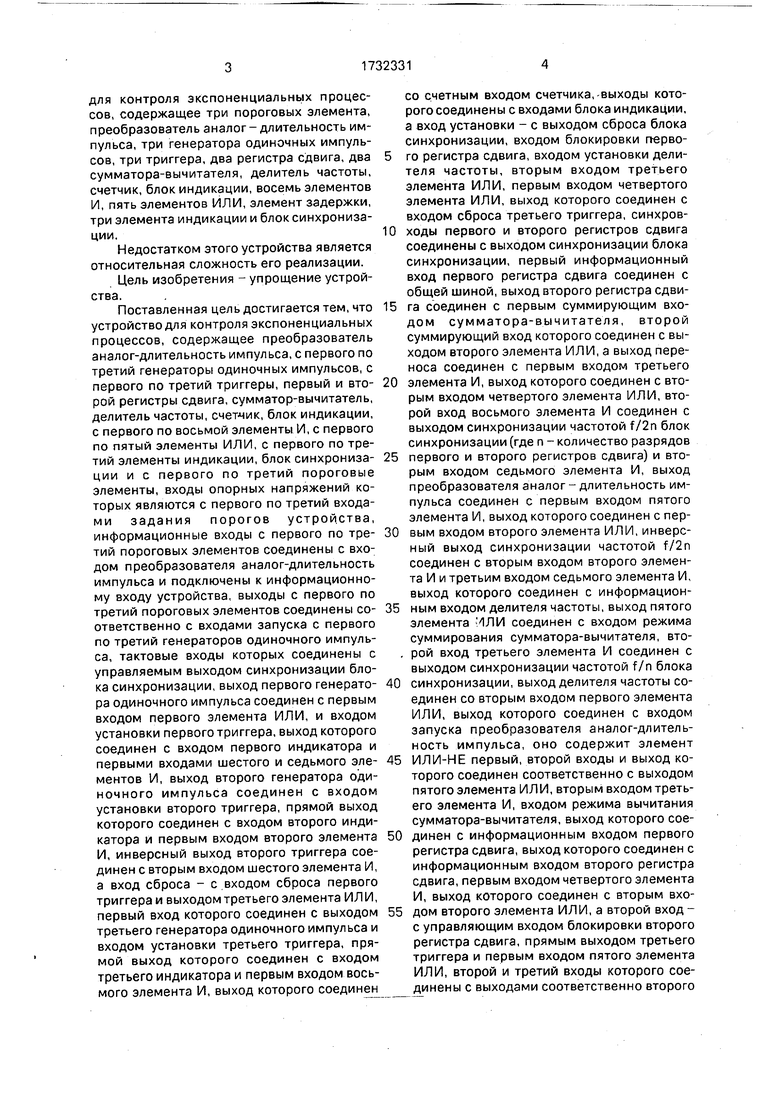

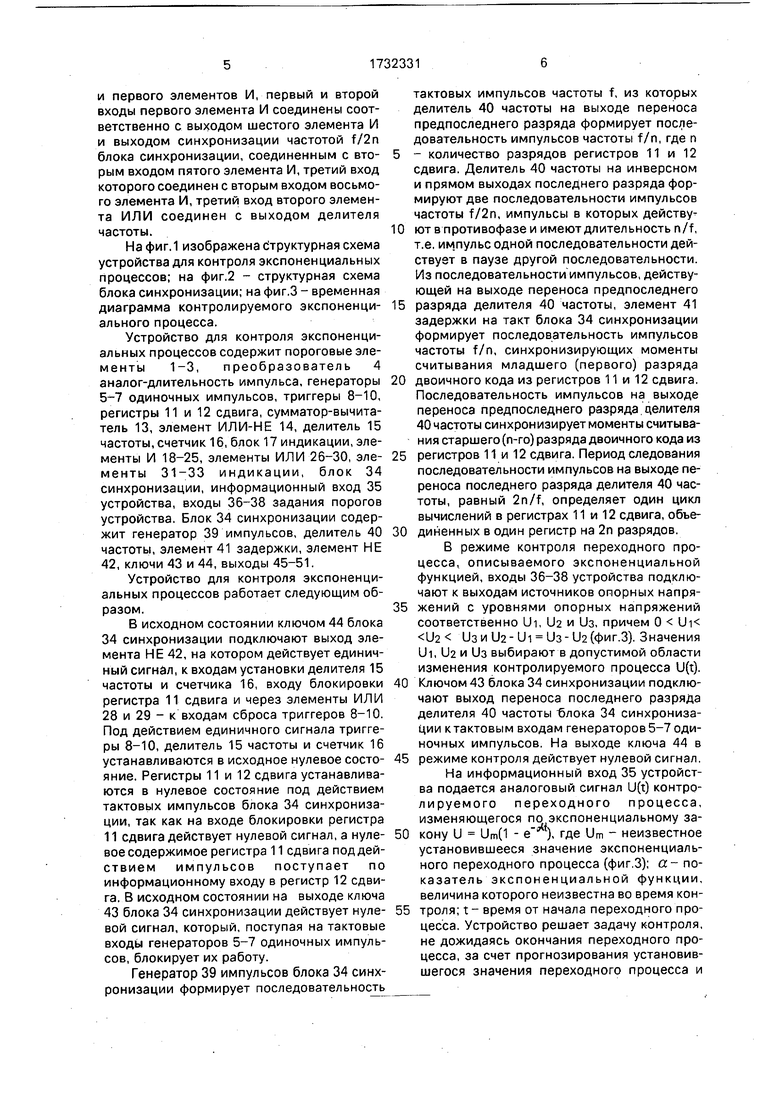

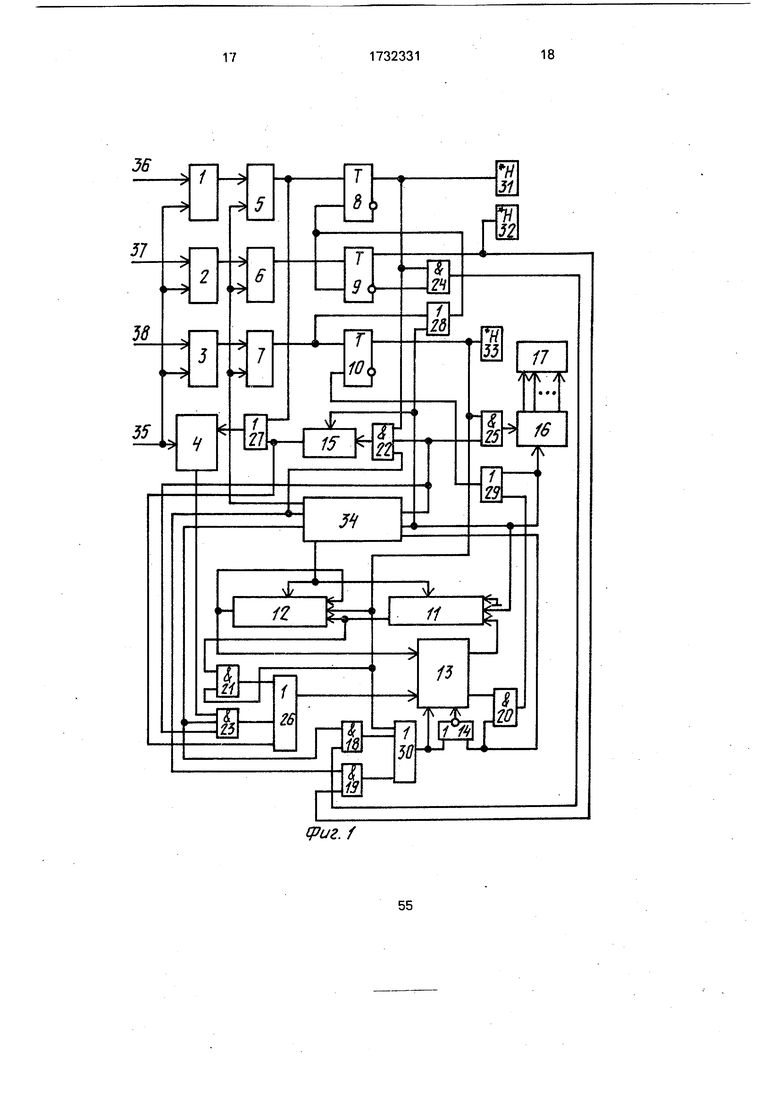

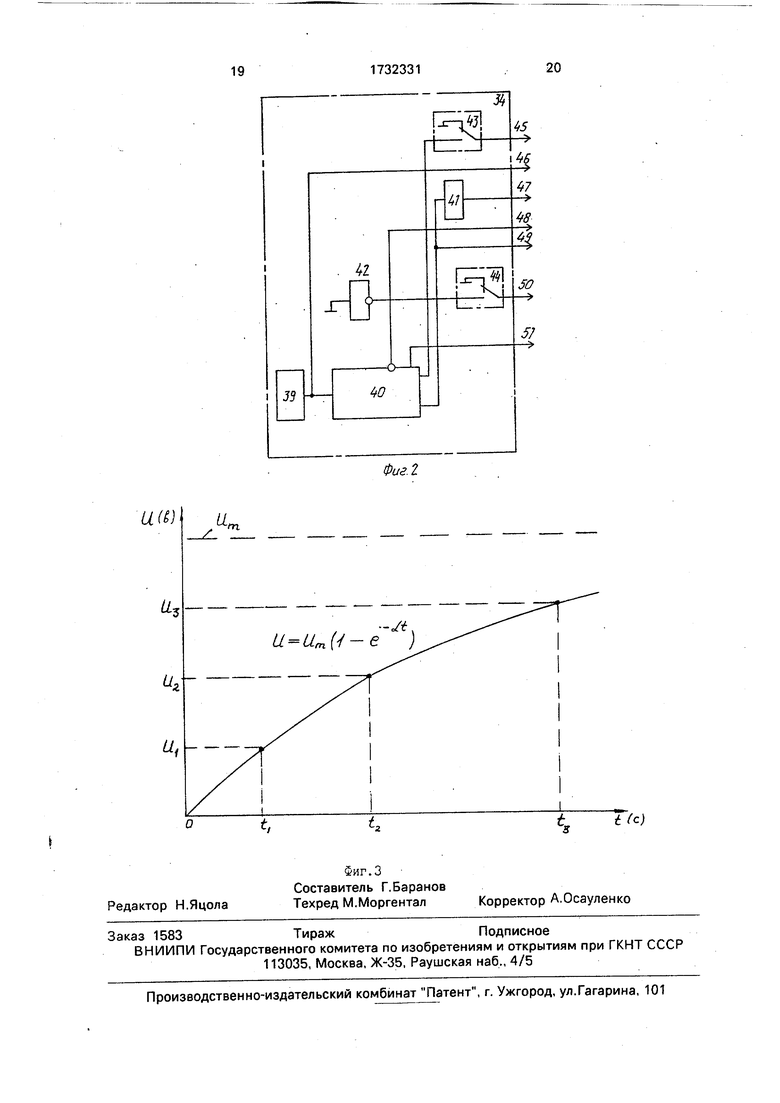

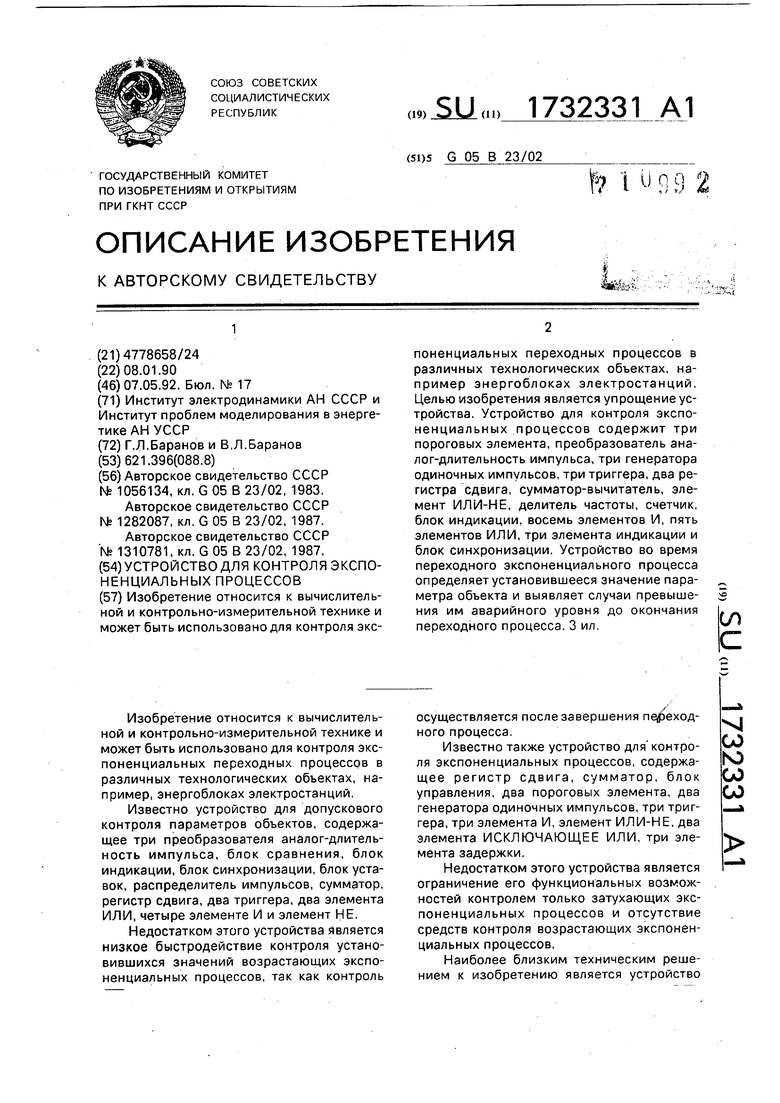

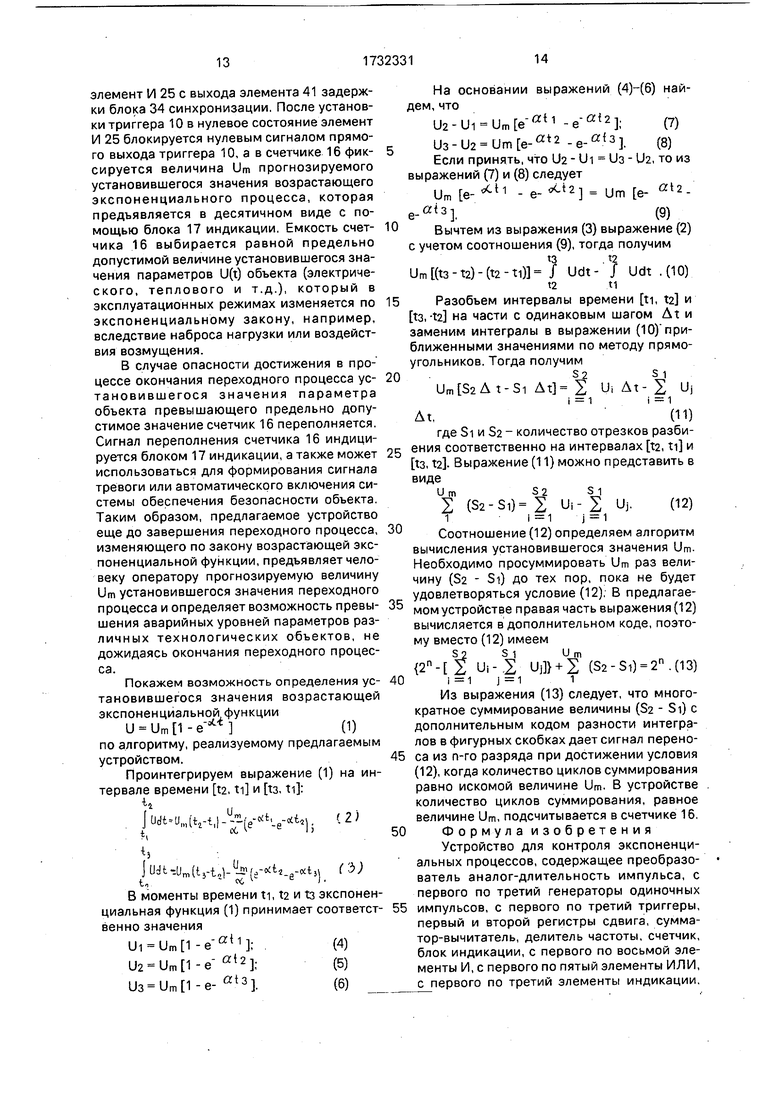

На фиг.1 изображена Структурная схема устройства для контроля экспоненциальных процессов; на фиг.2 - структурная схема блока синхронизации; на фиг.З - временная диаграмма контролируемого экспоненциального процесса.

Устройство для контроля экспоненциальных процессов содержит пороговые элементы 1-3, преобразователь 4 аналог-длительность импульса, генераторы 5-7 одиночных импульсов, триггеры 8-10, регистры 11 и 12 сдвига, сумматор-вычита- тель 13, элемент ИЛИ-НЕ 14, делитель 15 частоты, счетчик 16, блок 17 индикации, элементы И 18-25, элементы ИЛИ 26-30, элементы 31-33 индикации, блок 34 синхронизации, информационный вход 35 устройства, входы 36-38 задания порогов устройства. Блок 34 синхронизации содержит генератор 39 импульсов, делитель 40 частоты, элемент 41 задержки, элемент НЕ 42, ключи 43 и 44, выходы 45-51.

Устройство для контроля экспоненциальных процессов работает следующим образом.

В исходном состоянии ключом 44 блока 34 синхронизации подключают выход элемента НЕ 42, на котором действует единичный сигнал, к входам установки делителя 15 частоты и счетчика 16, входу блокировки регистра 11 сдвига и через элементы ИЛИ 28 и 29 - к входам сброса триггеров 8-10. Под действием единичного сигнала триггеры 8-10, делитель 15 частоты и счетчик 16 устанавливаются в исходное нулевое состояние. Регистры 11 и 12 сдвига устанавливаются в нулевое состояние под действием тактовых импульсов блока 34 синхронизации, так как на входе блокировки регистра 11 сдвига действует нулевой сигнал, а нулевое содержимое регистра 11 сдвига под действием импульсов поступает по информационному входу в регистр 12 сдвига. В исходном состоянии на выходе ключа 43 блока 34 синхронизации действует нулевой сигнал, который, поступая на тактовые входы генераторов 5-7 одиночных импульсов, блокирует их работу.

Генератор 39 импульсов блока 34 синхронизации формирует последовательность

тактовых импульсов частоты f, из которых делитель 40 частоты на выходе переноса предпоследнего разряда формирует последовательность импульсов частоты f/n, где п

- количество разрядов регистров 11 и 12 сдвига. Делитель 40 частоты на инверсном и прямом выходах последнего разряда формируют две последовательности импульсов частоты f/2n, импульсы в которых действуют в противофазе и имеют длительность n/f, т.е. им.пульс одной последовательности действует в паузе другой последовательности. Из последовательности импульсов, действующей на выходе переноса предпоследнего

разряда делителя 40 частоты, элемент 41 задержки на такт блока 34 синхронизации формирует последовательность импульсов частоты f/n, синхронизирующих моменты считывания младшего (первого) разряда

двоичного кода из регистров 11 и 12 сдвига. Последовательность импульсов на выходе переноса предпоследнего разряда целителя 40 частоты синхронизирует моменты считывания старшего (n-го) разряда двоичного кода из

регистров 11 и 12 сдвига. Период следования последовательности импульсов на выходе переноса последнего разряда делителя 40 частоты, равный 2n/f, определяет один цикл вычислений в регистрах 11 и 12 сдвига, обьединенных в один регистр на 2п разрядов.

В режиме контроля переходного процесса, описываемого экспоненциальной функцией, входы 36-38 устройства подключают к выходам источников опорных напряжений с уровнями опорных напряжений соответственно Ui, U2 и Уз, причем 0 Ui U2 U3nU2-Ui U3-U2fanr.3). Значения Ui, U2 и Уз выбирают в допустимой области изменения контролируемого процесса U(t).

Ключом 43 блока 34 синхронизации подключают выход переноса последнего разряда делителя 40 частоты блока 34 синхронизации к тактовым входам генераторов 5-7 одиночных импульсов. На выходе ключа 44 в

режиме контроля действует нулевой сигнал. На информационный вход 35 устройства подается аналоговый сигнал U(t) контро- лируемого переходного процесса, изменяющегося по экспоненциальному закону U Um(1 - е ), где Um - неизвестное установившееся значение экспоненциального переходного процесса (фиг.З); а- показатель экспоненциальной функции, величина которого неизвестна во время контроля; t - время от начала переходного процесса. Устройство решает задачу контроля, не дожидаясь окончания переходного процесса, за счет прогнозирования установившегося значения переходного процесса и

определения факта перехода установившимся значением допустимого уровня.

В исходном состоянии на выходе пороговых элементов 1-3 действуют нулевые сигналы. Как только входное напряжение, действующее на информационном входе 35 устройства, достигнет уровня опорного напряжения Ui, на выходе порогового элемента 1 формируется единичный сигнал, запускающий гепнератор 5 одиночных импульсов, который выделяет одиночный импульс из последовательности импульсов выхода переноса последнего разряда делителя 40 частоты блока 34 синхронизации. Одиночный импульс, формируемый генератором 5 одиночных импульсов, устанавливает триггер 8 в единичное состояние и через элемент ИЛИ 27 запускает преобразователь 4 аналог-длительность импульса. Единичный сигнал прямого выхода триггера 8 приводит к срабатыванию элемента 31 индикации, снимает блокировку элемента И 22 и формирует единичный сигнал на выходе элемента И 24, снимающий блокировку элемента И 18.

Условимся называть время действия импульсов на инверсном и прямом выходах последнего разряда делителя 40 частоты блока 34 синхронизации соответственно первой и второй фазой. Тогда элемент И 22 открывается во время первой фазы и пропускает на вход делителя 15 частоты последовательность импульсов, формируемую элементом 41 задержки на такт блока 34 синхронизации. Во время второй фазы открывается элемент И 23,через который последовательность импульсов выхода элемента 41 задержки блока 34 синхронизации проходит на информационный вход сумматора-вычитателя 13. После запуска преобразователь 4 аналог-длительность импульса формирует импульс, длительность которого пропорциональна аналоговому сигналу, действующему на информационном входе 35 устройства. На выходе элемента И 23, управляемого выходным сигналом преобразователя 4 аналог-длительность импульсов, формируется пачка импульсов, количество которых пропорционально входному аналоговому сигналу.

Последовательность импульсов второй фазы с прямого выхода последнего разряда делителя 40 частоты блока 34 синхронизации через элементы И 18, ИЛИ 30 поступает на вход режима суммирования сумматора- вычитателя 13. При нулевом сигнале на прямом выходе триггера 10 п-разрядные регистры 11 и 12 сдвига объединяются в 2п-разрядный регистр, в цепи циркуляции которого включен сумматор-вычитатель 13,

который во время второй фазы действует в режиме суммирования. Первый импульс пачки, действующей на информационном входе сумматора-вычитателя 13, формирует

на его выходе импульс результата, который под действием тактовых импульсов генератора 39 импульсов блока 34 синхронизации записывается в регистр 11 сдвига и спустя п тактов поступает в регистр 12 сдвига. Спу0 стя 2п тактов первый импульс пачки сдвигается под действием тактовых импульсов с выхода регистра 12 сдвига на первый информационный вход сумматора-вычитателя 13, на втором входе которого в этот момент

5 времени действует второй импульс пачки. На выходе сумматора-вычитателя 13 формируется последовательный двоичный код 00...010 результата, который, начиная с младшего разряда, записывается в регистр

0 11 сдвига и через 2п тактов сдвигается под действием тактовых импульсов с выхода регистра 12 сдвига на первый информационный вход сумматора-вычитателя 13. Если на информационный вход сумматора-вычита5 теля 13 поступила пачка из К импульсов, то спустя 2 Кп тактов в регистре 11 сдвига формируется n-разрядный двоичный код, значение которого равно К.

После окончания импульса на выходе

0 преобразователя 4 аналог-длительность импульса двоичный код, пропорциональный входному аналоговому сигналу, действовавшему на информационном входе 35 устройства, запоминается динамическим способом

5 путем циркуляции его под действием тактовых импульсов с выхода регистра 12 сдвига через сумматор-вычитатель 13 на информационный вход регистра 11 сдвига.

В дальнейшем устройство работает ана0 логично до момента появления импульса на выходе делителя 15 частоты, коэффициент деления которого выбирается так, чтобы период следования выходных импульсов делителя 15 частоты был больше длительности

5 выходного импульса преобразователя 4 аналог-длительность импульса для максимально возможного уровня напряжения на информационном входе 35 устройства. Поэтому импульс на выходе делителя 15 частоты

0 формируется после окончания действия импульса на выходе преобразователя 4 аналог- длительность импульса. Выходной импульс делителя 15 частоты вновь запускает преобразователь 4 аналог-длительность импуль5 са, который формирует импульс длительностью, пропорциональной текущему значению напряжения на информационном входе 35 устройства.

На выходе элемента И 23 формируется новая пачка импульсов, количество которых

пропорционально текущему значению входного аналогового сигнала. По каждому импульсу новой пачки сумматор-вычитатель 13 за время 2п тактов увеличивает двоичный код, хранящийся в регистрах 11 и 12 сдвига, на единицу младшего разряда. Таким образом, в регистрах 11 и 12 сдвига накапливается n-разрядный двоичный код, значение которого пропорционально интегралу от аналогового сигнала возрастающей экспоненциальной функции, действующей на информационном входе 35 устройства с момента срабатывания порогового элемента 1. Этот двоичный код формируется сум- матором-вычитателем 13 в режиме суммирования во время действия вторых фаз. Сумматор-вычитатель 13 во время действия первых фаз переключается в режим вычитателя, так как во время первых фаз элементы И 18 и 19 закрыты и на выходе элемента ИЛИ 30 действует нулевой сигнал, формирующий на выходе элемента ИЛИ-НЕ 14 единичный сигнал.

Сумматор-вычитатель 13, работающий в режиме вычитания во время первых фаз, формирует в регистрах 11 и 12 сдвига п-раз- рядный дополнительный двоичный код, значение которого пропорционально времени с момента срабатывания порогового элемента 1. Действительно, первый выходной импульс делителя 15 частоты, действующий через элемент ИЛИ 26, во время первой фазы вычитается сумматором-вычитателем 13 из начального нулевого кода регистра 12 сдвига, сдвигаемого под действием тактовых импульсов блока 34 синхронизации. На выходе сумматора-вычитателя 13 за п тактов первой фазы формируется дополнительный двоичный код 11...111 величины 2 - 1, который под действием тактовых импульсов блока 34 синхронизации записывается, начиная с младшего разряда, в регистр 11 сдвига и спустя 2п тактов вновь сдвигается с выхода регистра 12 сдвига на информационный вход сумматора-вычитателя 13.

В дальнейшем устройство работает аналогичным образом, спустя время

S -nf m , где m - коэффициент деления делителя 15 частоты, в регистрах 11 и 12 сдвига формируется n-разрядный дополнительный код 2П - S, где величина S пропорциональна времени работы устройства с момента срабатывания порогового элемента 1. Так как в 2п-разрядном регистре, образованном последовательным соединением двух n-разрядных регистров 11 и 12 сдвига, формируются два п-разрядных кода (дополнительный код времени во время первой фазы и прямой код интеграла от

аналогового сигнала во время второй фазы), то с целью независимого формирования этих кодов сигнал переноса предпоследнего разряда делителя 40 частоты блока 34

синхронизации через элемент ИЛИ-НЕ 14 формирует нулевой сигнал на входе режима вычитания сумматора-вычитателя 13, блокируя этим сигнал займа из n-го разряда дополнительного кода времени в первый

0 разряд двоичного кода интеграла от аналогового сигнала.

В дальнейшем устройство работает аналогично до тех пор, пока не сработает поро- говый элемент 2 при достижении

5 напряжения на информационном входе 35 уровня опорного напряжения U2. В этом случае на выходе порогового элемента 2 формируется единичный сигнал, запускающий генератор 6 одиночных импульсов, вы0 ходной импульс которого устанавливает триггер 9 в единичное состояние. Нулевой сигнал инверсного выхода триггера 9 блокирует элемент И 24, нулевой сигнал на выходе которого закрывает элемент И 18.

5 Единичный сигнал прямого выхода триггера 9 приводит к срабатыванию элемента 32 индикации и снимает блокировку элемента И 19, на выход которого начинает поступать последовательность импульсов первой фа0 зы, формируемая на инверсном выходе последнего разряда делителя частоты 40 блока синхронизации. Последовательность импульсов первой фазы с выхода элемента И 19 поступает через элемент ИЛИ 30 на вход

5 режима суммирования сумматора-вычитателя 13, который переходит в режим суммирования во время первой фазы и в режим вычитания - во время второй фазы. Во время второй фазы элементы И 18 и 19 закрыты

0 и на выходе элемента ИЛИ 30 действует нулевой сигнал, который формирует через элемент ИЛИ-НЕ 14 единичный сигнал на входе режима вычитания сумматора-вычитателя 13.

5 К моменту срабатывания порогового элемента 2 в регистрах 11 и 12 сдвига сформированы: дополнительный код 2n - Si, где Si - величина, пропорциональная интервалу времени ta -11 Si 2 nm/f, и двоичный

0 код, пропорциональный интегралу от входного напряжения, действующего на информационном входе 35 устройства на интервале времени t2 - ti, где ti и ta - моменты времени срабатывания соответственно

5 порогов Ui и U2.

После срабатывания порогового элемента 2 сумматор-вычитатель 13 во время первой фазы осуществляет суммирование последовательности импульсов, действующих на выходе делителя 15 частоты, с дополнительным кодом 2n - Si, сдвигаемым под действием тактовых импульсов с выхода регистра 12 сдвига. Во время второй фазы сумматор-вычитатель 13 выполняет вычитание из двоичного кода, пропорционального 5 интегралу от аналогового сигнала, поступающего под действием тактовых импульсов с выхода регистра 12 сдвига, пачки импульсов, действующей на выходе элемента И 23 и формируемой под действием выходных 10 импульсов преобразователя 4 аналог-длительность импульса. Таким образом, каждый импульс выхода делителя 15 частоты увеличивает на единицу младшего разряда дополнительный код2п-$1 во время первой 15 фазы, а во время второй фазы по каждому импульсу пачки на выходе элемента И 23 двоичный код, пропорциональный интегралу от аналогового сигнала на интервале t2 - ti, уменьшается на единицу младшего раз- 20 ряда.

В дальнейшем устройство работает аналогично до тех пор, пока уровень входного напряжения не достигнет уровня опорного напряжения из. В этом случае срабатывает 25 пороговый элемент 3, выходной сигнал которого запускает генератор 7 одиночных импульсов. Выходной импульс генератора 4 одиночных импульсов устанавливает триггер 10 в единичное состояние и через эле- 30 мент ИЛИ 28 сбрасывает триггеры 8 и 9 в нулевое состояние. К моменту ta срабатывания порогового элемента 3 в регистрах 11 и 12 сдвига во время первой фазы сформировался n-разрядный двоичный код, величина 35 которого пропорциональна разности интервалов времени (ta - ta) - (t2 - ti) (82 - Si)/ 2nm/f, где S2 величина пропорциональная интервалу времени ts -12 82 2nm/f. Этот двоичный код представляет положительную 40 величину, так как при уровнях опорных напряжений U3-U2 U2-Ui для возрастающей экспоненциальной функции всегда (т.з-12) (t2- - ti). Кроме этого двоичного кода в регистрах 11 и 12 сдвига во время второй фазы к мо- 45 менту времени ts сформировался п-разряд- ный дополнительный код разности интегралов от возрастающей экспоненциальной функции на интервалах времени ti -12 и t3 -12, так как при уровнях опорных напряже- 50 ний Уз- U2 U2 - U1 интеграл от возрастающей экспоненциальной функции на интервале ts - t2 всегда больше интеграла на интервале t2 - ti (фиг.З).

Установка триггеров 8 и 9 в нулевое 55 состояние обеспечивает блокировку элементов И 18, 19, 22 и 24. После блокировки элемента И 22 прекращается поступление импульсов на информационный вход делителя 15 частоты и прекращается формирование импульсов запуска преобразователя 4 аналог-длительность импульса, нулевой сигнал на выходе которого блокирует элемент И 23. Единичный сигнал прямого выхода триггера 10, сформированный при достижении момента времени ts, приводит к срабатыванию элемента 33 индикации, снимает блокировку элементов И 21 и 25 и через элемент ИЛИ 30 переключает сумматор-вычитатель 13 в режим суммирования. Поступление единичного сигнала прямого выхода триггера 10 на вход блокировки регистра 12 сдвига приводит к блокировке его информационного входа и к подключению выхода регистра 12 сдвига к его информационному входу. К этому моменту времени в регистре 12 сдвига содержится n-разрядный двоичный код, величина S2 - Si которого пропорциональна разности интервалов времени (ts- -12) - (t2 - ti). Двоичный код величины $2 - Si под действием тактовых импульсов, вырабатываемых генератором 39 импульсов блока 34 синхронизации, циркулирует по цепи рециркуляции с выхода регистра 12 сдвига на его информационный вход. Этим обеспечивается динамическое хранение двоичного кода величины $2 - Si, который каждые п тактов последовательно во времени поступает на первый информационный вход сум- матора-вычитателя 13, на второй информационный вход которого через элементы И 21 и ИЛИ 26 поступает п-разряд- ный дополнительный код разности интегралов от экспоненциальной функции, сдвигаемый под действием тактовых импульсов блока 34 синхронизации с выхода регистра 11 сдвига.

Каждые п тактов сумматор-вычитатель 13, работающий в режиме суммирования, к дополнительному коду, сдвигаемому с выхода регистра 11 сдвига, прибавляет двоичный код величины $2 - Si, поступающий под действием тактовых импульсов с выхода регистра 12 сдвига. Результат суммирования с выхода сумматора-вычитателя 13 записывается под действием тактовых импульсов блока 34 синхронизации в регистр 11 сдвига. Таким образом устройство работает до тех пор, пока на выходе переноса сумматора-вычитателя 13 не появится сигнал переноса из п-го разряда, который открывает элемент И 20. Импульс, действующий на выходе переноса предпоследнего разряда делителя 40 частоты блока 34 синхронизации, проходит через элементы И 20 и ИЛИ 29 и устанавливает триггер 10 в нулевое состояние. В период времени, когда триггер 10 находился в единичном состоянии, счетчик 16 осуществлял счет количества импульсов, поступающих на его счетный вход через

элемент И 25 с выхода элемента 41 задержки блока 34 синхронизации. После установки триггера 10 в нулевое состояние элемент И 25 блокируется нулевым сигналом прямого выхода триггера 10, а в счетчике 16 фиксируется величина Um прогнозируемого установившегося значения возрастающего экспоненциального процесса, которая предъявляется в десятичном виде с помощью блока 17 индикации. Емкость счетчика 16 выбирается равной предельно допустимой величине установившегося значения параметров U(t) объекта (электрического, теплового и т.д.), который в эксплуатационных режимах изменяется по экспоненциальному закону, например, вследствие наброса нагрузки или воздействия возмущения.

В случае опасности достижения в процессе окончания переходного процесса установившегося значения параметра объекта превышающего предельно допустимое значение счетчик 16 переполняется. Сигнал переполнения счетчика 16 индицируется блоком 17 индикации, а также может использоваться для формирования сигнала тревоги или автоматического включения системы обеспечения безопасности объекта. Таким образом, предлагаемое устройство еще до завершения переходного процесса, изменяющего по закону возрастающей экспоненциальной функции,предъявляет человеку оператору прогнозируемую величину Um установившегося значения переходного процесса и определяет возможность превышения аварийных уровней параметров различных технологических объектов, не дожидаясь окончания переходного процесса.

Покажем возможность определения установившегося значения возрастающей

экспоненциальной функции U Um 1 - е 8

0)

i

с.

по алгоритму, реализуемому предлагаемым устройством.

Проинтегрируем выражение (1) на интервале времени t2. ti и тз,

t4

Iwt.JVt.l-rie- -e- l- (2)

J (t}-t2l-(e- -e-«M ( Ъ)

В моменты времени ti, t2 и тз экспоненциальная функция (1) принимает соответственно значения

Ui Um 1-e at1 ;(4)

U2-Um 1-e- (5)

U3 at3.(6)

На основании дем, что

выражений (4)-(6) найU2-Ui Um e-a{1 -e at2 ;(7)

U3-U2 Um e-at2 -e-af3. (8) Если принять, что U2 - Ui Us - U2, то из выражений (7) и (8) следует

Um - Um e- at20

0

5

0

5

0

e-at3.

(9)

Вычтем из выражения (3) выражение (2) с учетом соотношения (9), тогда получим

Um (ts -12) - (t2 - ti) - / Udt - 1 Udt . (10)

t2ti

5 Разобьем интервалы времени ti, 12 и t3,-t2 на части с одинаковым шагом At и заменим интегралы в выражении (10) приближенными значениями по методу прямоугольников. Тогда получим 0S7s1

t-Si At X U, At- X Uj

At,(11)

где Si и $2 - количество отрезков разбис ения соответственно на интервалах t2, ti и

ts, te. Выражение (11) можно представить в

виде

UmS2S1

I (S2-S1) E Ui- S Uj.(12)

1i 1j 1

Соотношение (12) определяем алгоритм вычисления установившегося значения Um. Необходимо просуммировать Um раз величину ($2 - Si) до тех пор, пока не будет удовлетворяться условие (12), В предлагаемом устройстве правая часть выражения (12) вычисляется в дополнительном коде, поэтому вместо (12) имеем

S2S 1U m

Ui-2 + 2 (S2-Si) 2n.(13)

i 1 j 11

Из выражения (13) следует, что многократное суммирование величины (82 - Si) с дополнительным кодом разности интегралов в фигурных скобках дает сигнал переноса из n-го разряда при достижении условия (12), когда количество циклов суммирования равно искомой величине Um. В устройстве количество циклов суммирования, равное величине Um, подсчитывается в счетчике 16. Формула изобретения Устройство для контроля экспоненциальных процессов, содержащее преобразователь аналог-длительность импульса, с первого по третий генераторы одиночных 5 импульсов, с первого по третий триггеры, первый и второй регистры сдвига, сумма- тор-вычитатель, делитель частоты, счетчик, блок индикации, с первого по восьмой элементы И, с первого по пятый элементы ИЛИ, с первого по третий элементы индикации.

блок синхронизации и с первого по третий пороговые элементы, входы опорных напряжений которых являются с первого по третий входами задания порогов устройства, информационные входы с первого по третий пороговых элементов соединены с входом преобразователя аналог-длительность импульса и подключены к информационному входу устройства, выходы с первого по третий пороговых элементов соединены соответственно с входами запуска с первого по третий генераторов одиночного импульса, тактовые входы которых соединены с управляемым выходом синхронизации блока синхронизации, выход первого генератора одиночного импульса соединен с первым входом первого элемента ИЛИ и входом установки первого триггера, выход которого соединен с входом первого индикатора и первыми входами шестого и седьмого элементов И, выход второго генератора одиночного импульса соединен с входом установки второго триггера, прямой выход которого соединен с входом второго индикатора и первым входом второго элемента И, инверсный выход второго триггера соединен с вторым входом шестого элемента И, а вход сброса - с входом сброса первого триггера и выходом третьего элемента ИЛИ, первый вход которого соединен с выходом третьего генератора одиночного импульса и входом установки третьего триггера, прямой выход которого соединен с входом третьего индикатора и первым входом восьмого элемента И, выход которого соединен с счетным входом счетчика, выходы которого соединены с входами блока индикации, а вход установки - с выходом сброса блока синхронизации, входом блокировки первого регистра сдвига, входом установки делителя частоты, вторым входом третьего элемента ИЛИ, первым входом четвертого элемента ИЛИ, выход которого соединен с входом сброса третьего триггера, синхров- ход первого и второго регистров сдвига соединены с выходом синхронизации блока синхронизации, первый информационный вход первого регистра сдвига соединен с общей шиной, выход второго регистра сдвига соединен с первым суммирующим входом сумматора-еычитателя, второй суммирующий вход которого соединен с выходом второго элемента ИЛИ, а выход переноса соединен с первым входом третьего элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, второй вход восьмого элемента И соединен с

выходом синхронизации частотой f/2n блока синхронизации (где п - количество разрядов первого и второго регистров сдвига) и вторым входом седьмого элемента И, выход преобразователя аналог-длительность импульса соединен с первым входом пятого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, инверсный выход синхронизации частотой f/2n соединен с вторым входом второго элемента И и третьим входом седьмого элемента И, выход которого соединен с информационным входом делителя частоты, выход пятого элемента ИЛИ соединен с входом режима суммирования сумматора-вычитателя, второй вход третьего элемента И соединен с выходом синхронизации частотой f/n блока синхронизации, выход делителя частоты соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом

запуска преобразователя аналог-длительность импульса, отличающееся тем, что, с целью упрощения устройства, оно содержит элемент ИЛИ-НЕ, первый, второй входы и выход которого соединены соответственно с выходом пятого элемента ИЛИ, вторым входом третьего элемента И, входом режима вычитания сумматора-вычитателя, выход которого соединен с информационным входом первого регистра сдвига, выход

которого соединен с информационным входом второго регистра сдвига, первым входом четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, а второй вход - с управляющим

входом блокировки второго регистра сдвига, прямым выходом третьего триггера и первым входом пятого элемента ИЛИ, второй и третий входы которого соединены с выходами соответственно второго и первого элементов И, первый и второй входы первого элемента И соединены соответственно с выходом шестого элемента И и выходом синхронизации частотой f/2n блока синхронизации, соединенным с вторым входом пятого элемента И, третий вход которого соединен с вторым входом восьмого элемента И, третий вход второго элемента ИЛИ соединен с выходом делителя частоты.

tpuz.f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1984 |

|

SU1272342A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1335989A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для контроля экспоненциальных переходных процессов в различных технологических объектах, например энергоблоках электростанций. Целью изобретения является упрощение устройства. Устройство для контроля экспоненциальных процессов содержит три пороговых элемента, преобразователь аналог-длительность импульса, три генератора одиночных импульсов, три триггера, два регистра сдвига, сумматор-вычитатель, элемент ИЛИ-НЕ, делитель частоты, счетчик, блок индикации, восемь элементов И, пять элементов ИЛИ, три элемента индикации и блок синхронизации. Устройство во время переходного экспоненциального процесса определяет установившееся значение параметра объекта и выявляет случаи превышения им аварийного уровня до окончания переходного процесса. 3 ил. сл с

им

а

пг

а,

)

tи

| Устройство для допускового контроля параметров объектов | 1982 |

|

SU1056134A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-05-07—Публикация

1990-01-08—Подача