Изобретение относится к вычислительной технике и может быть использовано в автоматике и в системах числового программного управления станками.

Цель изобретения - повышение достоверности преобразования информации

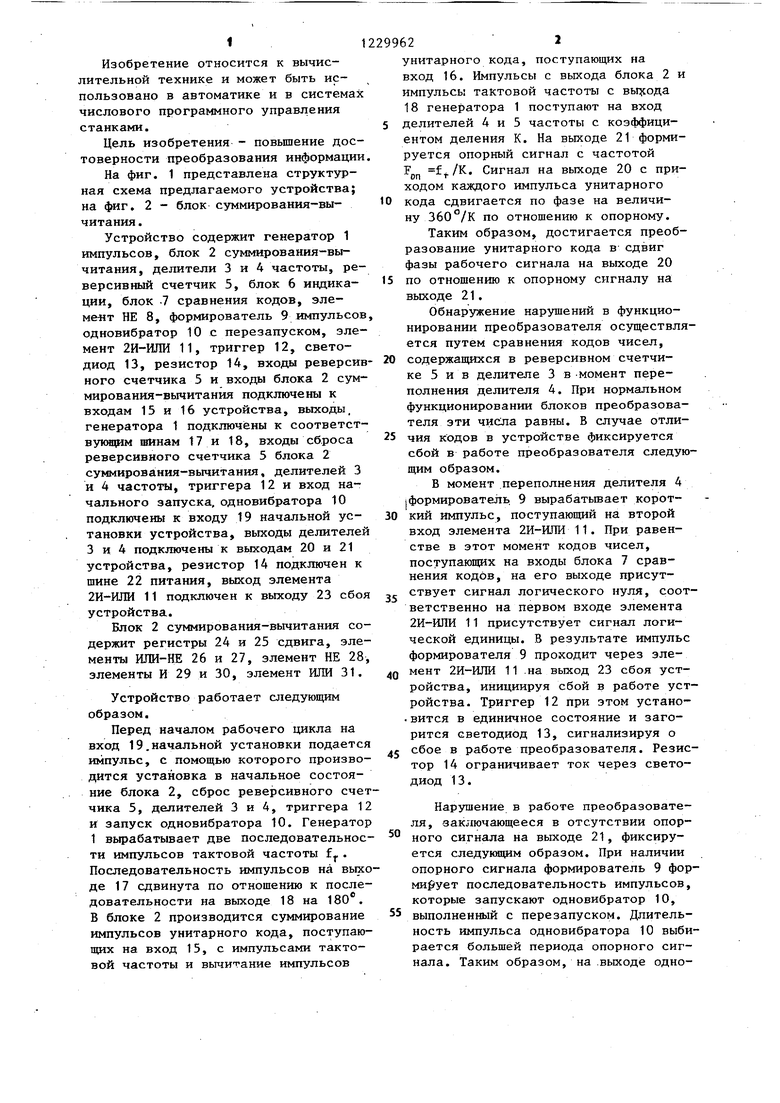

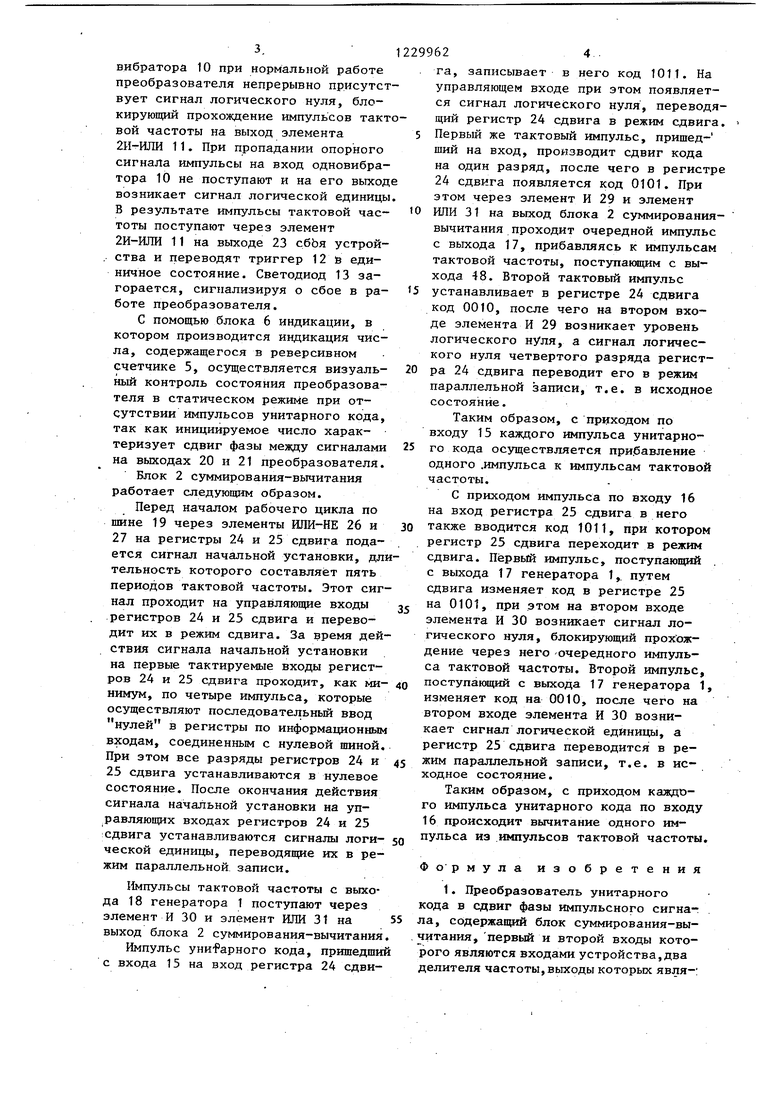

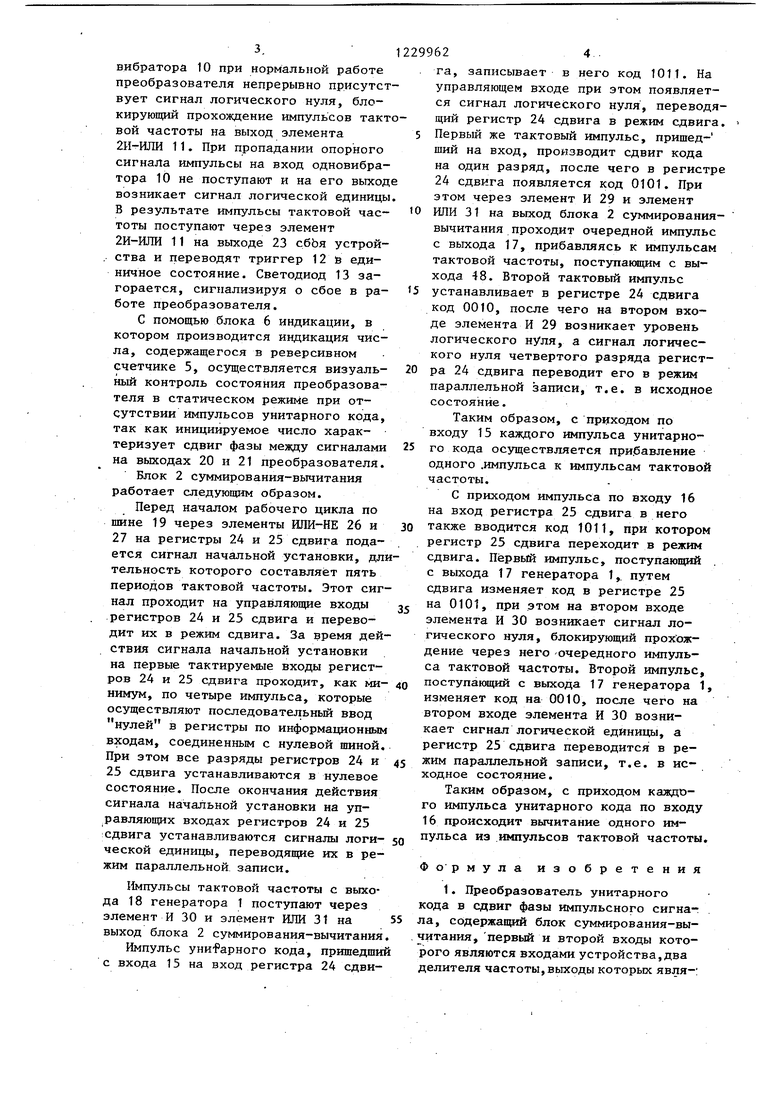

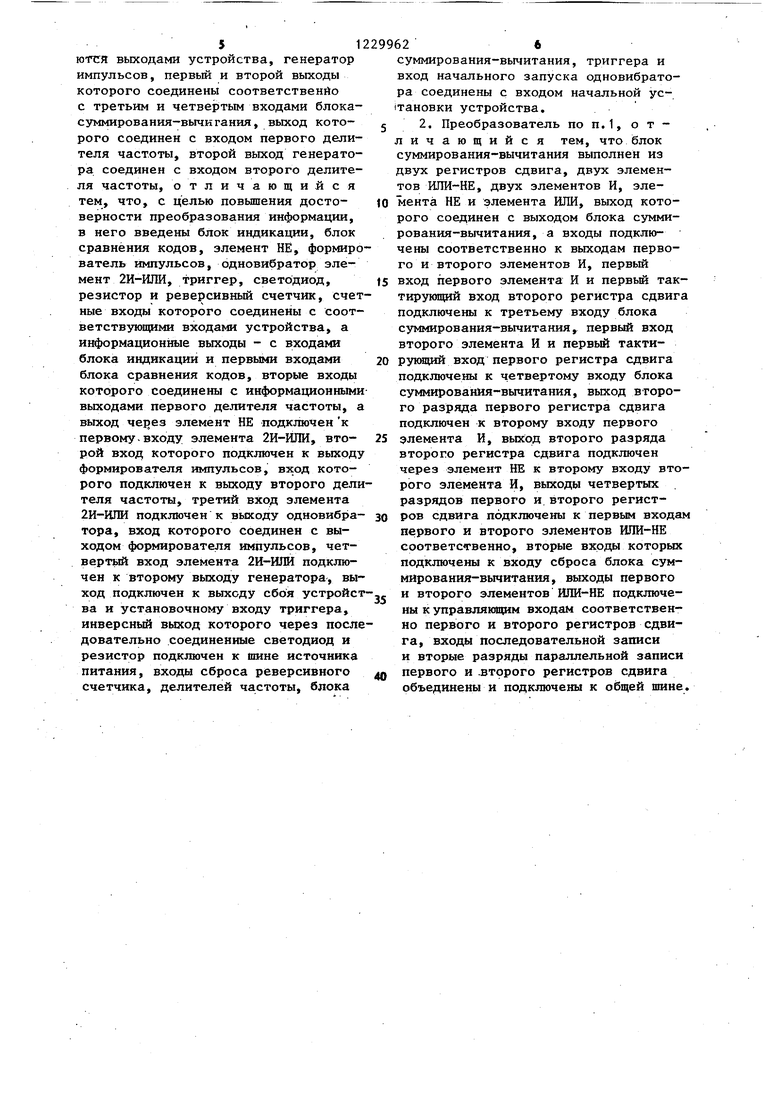

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг, 2 - блок суммирования-вычитания ,

Устройство содержит генератор 1 импульсов, блок 2 суммирования-вычитания, делители 3 и 4 частоты, реверсивный счетчик 5, блок 6 индикации, блок -7 сравнения кодов, элемент НЕ 8, формирователь 9 импульсов одновибратор 10 с перезапуском, элемент 2Й-ИЛИ 11, триггер 12, свето- диод 13, резистор 14, входы реверсивного счетчика 5 и входы блока 2 суммирования-вычитания подключены к входам 15 и 16 устройства, выходы, генератора 1 подключены к соответствующим шинам 17 и 18, входы сброса реверсивного счетчика 5 блока 2 суммирования-вычитания, делителей 3 и 4 частоты, триггера 12 и вход начального запуска, одновибратора 10 подключены к входу 19 начальной установки устройства, выходы делителей 3 и 4 подключены к выходам 20 и 21 устройства, резистор 14 подключен к шине 22 питания, выход элемента 2И-ИЛИ 11 подключен к выходу 23 сбоя устройства.

Блок 2 суммирования-вычитания содержит регистры 24 и 25 сдвига, элементы ИЛИ-НЕ 26 и 27, элемент НЕ 28, элементы И 29 и 30, элемент ИЛИ 31.

Устройство работает следующим образом.

Перед началом рабочего цикла на вход 19.начальной установки подается импульс, с помощью которого производится установка в начальное состояние блока 2, сброс реверсивного счетчика 5, делителей 3 и 4, триггера 12 и запуск одновибратора 10. Генератор 1 вырабатывает две последовательности импульсов тактовой частоты f. Последовательность импульсов на выходе 17 сдвинута по отношению к последовательности на выходе 18 на 180. В блоке 2 производится суммирование импульсов унитарного кода, поступающих на вход 15, с импульсами тактовой частоты и вычитание импульсов

to

15

20

2299622

унитарного кода, поступающих на вход 16. Импульсы с выхода блока 2 и импульсы тактовой частоты с вьцсода 18 генератора 1 поступают на вход делителей 4 и 5 частоты с коэффициентом деления К, На выходе 21 формируется опорный сигнал с частотой Fp , Сигнал на выходе 20 с приходом каждого импульса унитарного кода сдвигается по фазе на величину 360 °/К по отношению к опорному.

Таким образом, достигается преобразование унитарного кода в сдвиг фазы рабочего сигнала на выходе 20 по отношению к опорному сигналу на выходе 21.

Обнаружение нарушений в функционировании преобразователя осуществляется путем сравнения кодов чисел, содержащихся в реверсивном счетчике 5 ив делителе 3 в-момент переполнения делителя 4. При нормальном функционировании блоков преобразователя эти числа равны. В случае отличия кодов в устройстве фиксируется сбой в работе преобразователя следующим образом.

В момент .переполнения делителя 4 jформирователь, 9 вырабатьшает корот- 30 кий импульс, поступающий на второй вход элемента 2И-ИЛИ 11. При равенстве в этот момент кодов чисел, поступающих на входы блока 7 сравнения кодов, на его выходе присутствует сигнал логического нуля, соответственно на первом входе элемента 2И-ИЛИ 11 присутствует сигнсШ логической единицы. В результате импульс формирователя 9 проходит через элемент 2И-ИЛИ 11 .на выход 23 сбоя устройства, инициируя сбой в работе устройства. Триггер 12 при этом установится в единичное состояние и загорится светодиод 13, сигнализируя о сбое в работе преобразователя. Резис25

35

40

45

тор 14 ограничивает ток через светодиод 13.

Нарушение в работе преобразователя, заключающееся в отсутствии опорного сигнала на выходе 21, фиксируется следукщим образом. При наличии опорного сигнала формирователь 9 формирует последовательность импульсов, которые запускают одновибратор 10, выполненный с перезапуском. Длительность импульса одновибратора 10 выбирается большей периода опорного сигнала. Таким образом, на .выходе одновибратора 10 при нормальной работе преобразователя непрерывно присутствует сигнал логического нуля, блокирующий прохождение импульсов тактвой частоты на выход элемента 2И-ИЛИ 11. При пропадании опорного сигнала импульсы на вход одновибра- тора 10 не поступают и на его выход возникает сигнал логической единицы В результате импульсы тактовой час- тоты поступают через элемент 2И-ИЛИ 11 на выходе 23 сбЬя устройства и переводят триггер 12 fe единичное состояние. Светодиод 13 загорается, сигнализируя о сбое в ра- боте преобразователя.

С помощью блока 6 индикации, в котором производится индикация числа, содержащегося в реверсивном счетчике 5, осуществляется визуаль- ный контроль состояния преобразователя в статическом режиме при отсутствии импульсов унитарного кода, так как инициируемое число характеризует сдвиг фазы между сигналами на выходах 20 и 21 преобразователя.

Блок 2 суммирования-вычитания работает следующим образом.

Перед началом рабочего цикла по шине 19 через элементы ШТИ-НЕ 26 и 27 на регистры 24 и 25 сдвига подается сигнал начальной установки, длтельность которого составляет пять периодов тактовой частоты. Этот сигнал проходит на управляющие входы регистров 24 и 25 сдвига и переводит их в режим сдвига. За время действия сигнала начальной установки на первые тактируемые входы регистров 24 и 25 сдвига проходит, как ми- нимум, по четыре импульса, которые осуществляют последовательный ввод нулей в регистры по информационным входам, соединенным с нулевой шиной. При этом все разряды регистров 24 и 25 сдвига устанавливаются в нулевое состояние. После окончания действия сигнала начальной установки на управляющих входах регистров 24 и 25 сдвига устанавливаются сигналы логи- ческой единищ 1, переводящие их в режим параллельной записи.

Импульсы тактовор частоты с выхода 18 генератора 1 поступают через элемент И 30 и элемент ИЛИ 31 на выход блока 2 суммирования-вычитания

Импульс yHHfapHoro кода, пришедши с входа 15 на вход регистра 24 сдвига, записывает в него код 1011. На управляющем входе при этом появляется сигнал логического нуля, переводящий регистр 24 сдвига в режим сдвига Первый же тактовый импульс, пришед- ший на вход, производит сдвиг кода на один разряд, после чего в регистр 24 сдвига появляется код 0101. При этом череэ элемент И 29 и элемент ИЛИ 31 на выход блока 2 суммирования вычитания проходит очередной импульс с выхода 17, прибавляясь к импульсам тактовой частоты, поступающим с выхода 48. Второй тактовый импульс устанавливает в регистре 24 сдвига код 0010, после чего на втором входе элемента И 29 возникает уровень логического нуля, а сигнал логического нуля четвертого разряда регистра 24 сдвига переводит его в режим параллельной записи, т.е. в исходное состояние.

Таким образом, с приходом по входу 15 каждого импульса унитарного кода осуществляется прибавление одного .импульса к импульсам тактовой частоты.

С приходом импульса по входу 16 на вход регистра 25 сдвига в него также вводится код 1011, при котором регистр 25 сдвига переходит в режим сдвига. Первый импульс, поступающий с выхода 17 генератора 1, путем сдвига изменяет код в регистре 25 на 0101, при этом на втором входе элемента И 30 возникает сигнал логического нуля, блокирующий прох ож- дение через него очередного импульса тактовой частоты. Второй импульс, поступаклций с выхода 17 генератора 1, изменяет код на 0010, после чего на втором входе элемента И 30 возникает сигнал логической единицы, а регистр 25 сдвига переводится в режим параллельной записи, т.е. в исходное состояние.

Таким образом, с приходом каждого импульса унитарного кода по входу 16 происходит вычитание одного импульса из импульсов тактовой частоты.

Формула изобретения

1. Преобразователь унитарного кода в сдвиг фазы импульсного сигнала, содержащий блок суммирования-вычитания, первый и Второй входы которого являются входами устройства,два делителя частоты,выходы которьгх явля-:

ются выходами устройства, генератор импульсов, первый и второй выходы которого соединены соответственйо с третьим и четвертым входами блока- суммирования-вычигания, выход кото- рого соединен с входом первого делителя частоты, второй выход генератора соединен с входом второго делителя частоты, отличающийся тем, что, с целью повьшения досто- верности преобразования информации, в него введены блок индикации, блок сравнения кодов, элемент НЕ, формирователь импульсов, одновибратор элемент 2И-Ш1И, триггер, светодиод, резистор и реверсивный счетчик, счетные входы которого соединены с соответствующими входами устройства, а информационные выходы - с входами блока индикации и первыми входами блока сравнения кодов, вторые входы которого соединены с информационными выходами первого делителя частоты, а выход через элемент НЕ подключен к первому.входу элемента 2И-Ш1И, вто- рой вход которого подключен к выходу формирователя импульсов, вход которого подключен к выходу второго делителя частоты, третий вход элемента 2И-ШШ подключен к выходу одновибра- тора, вход которого соединен с выходом формирователя импульсов, чет- вертьй вход элемента 2И-ИЛИ подключен к второму выходу генератора, выход подключен к выходу сбоя устройст-.. и второго элементов ИЛИ-НЕ подключева и установочному входу триггера, инверсный выход которого через последовательно соединенные светодиод и резистор подключен к пшне источника питания, входы сброса реверсивного дл счетчика, делителей частоты, блока

ны к управлякшщм входам соответственно первого и второго регистров сдвига, входы последовательной записи и вторые разряды параллельной записи первого и .второго регистров сдвига объединены и подключены к общей шине.

суммирования-вычитания, триггера и вход начального запуска одновибрато- ра соединены с входом начальной ус- |тановки устройства.

2. Преобразователь по п.1, отличающийся тем, что блок суммирования-вычитания выполнен из двух регистров сдвига, двух элементов ИЛИ-НЕ, двух элементов И, элемента НЕ и элемента ИЛИ, выход которого соединен с выходом блока суммирования-вычитания, а входы подключены соответственно к выходам первого и второго элементов И, первьШ вход первого элемента И и первый тактирующий вход второго регистра сдвиг подключены к третьему входу блока суммирования-вычитания, первый вход второго элемента И и первый такти- РУКШЦ1Й вход первого регистра сдвига подключены к четвертому входу блока суммирования-вычитания, выход второго разряда первого регистра сдвига подключен к второму входу первого элемента И, выход второго разряда второго регистра сдвига подключен через элемент НЕ к второму входу второго элемента И, выходы четвертых . разрядов первого и второго регистров сдвига подключены к первым входа первого и второго элементов ИЛИ-НЕ соответственно, вторые входы которых подключены к входу сброса блока суммирования-вычитания, выходы первого

ны к управлякшщм входам соответственно первого и второго регистров сдвига, входы последовательной записи и вторые разряды параллельной записи первого и .второго регистров сдвига объединены и подключены к общей шине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Цифровой регулятор | 1983 |

|

SU1182485A1 |

| Формирователь импульсных сигналов | 1984 |

|

SU1181126A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 1991 |

|

RU2050693C1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Резервированный усилитель | 1987 |

|

SU1434568A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1989 |

|

SU1667214A1 |

| Устройство для логарифмирования двоичных чисел | 1978 |

|

SU767755A1 |

| Генератор рекуррентной последовательности с самоконтролем | 1988 |

|

SU1550502A1 |

Изобретение относится к вычислительной технике, может быть использовано в автоматике и в системах числового программного управления и позволяет повысить достоверность преобразования информации. Устройство содержит генератор импульсов, блок суммми- рования-вычитания, состоящий из двух регистров сдвига, двух элементов ИПИ-НЕ, элемента НЕ, двух элементов И и элемента ШШ, делители частоты, блок индикации, блок сравнения кодов, элемент НЕ, формирователь импульсов, одновибратор, элемент 2И-ИПИ, триггер, светодиод и резистор. 1 з.п. ф-лы, 2 ил. i |с/ д (С

. Составитель О. Неплохов Редактор А. Шандор Техред Л.Олейник .

Заказ 2460/59 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская иаб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Преобразователь унитарного кода в сдвиг фазы | 1974 |

|

SU506123A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Киселев В.М | |||

| Фазовые системы числового программного управления станками | |||

| М.: Машиностроение, 1976, с | |||

| Катодное реле | 1921 |

|

SU250A1 |

Авторы

Даты

1986-05-07—Публикация

1984-07-27—Подача