Изобретение относится к вычислительной технике и может быть использовано в устройствах, решающих задачи оценки спектра сигналов по алгоритму быстрого преобразования Фурье (БПФ).

Цель изобретения - повышение достоверности функционирования устройства путем осуществления контроля работы.

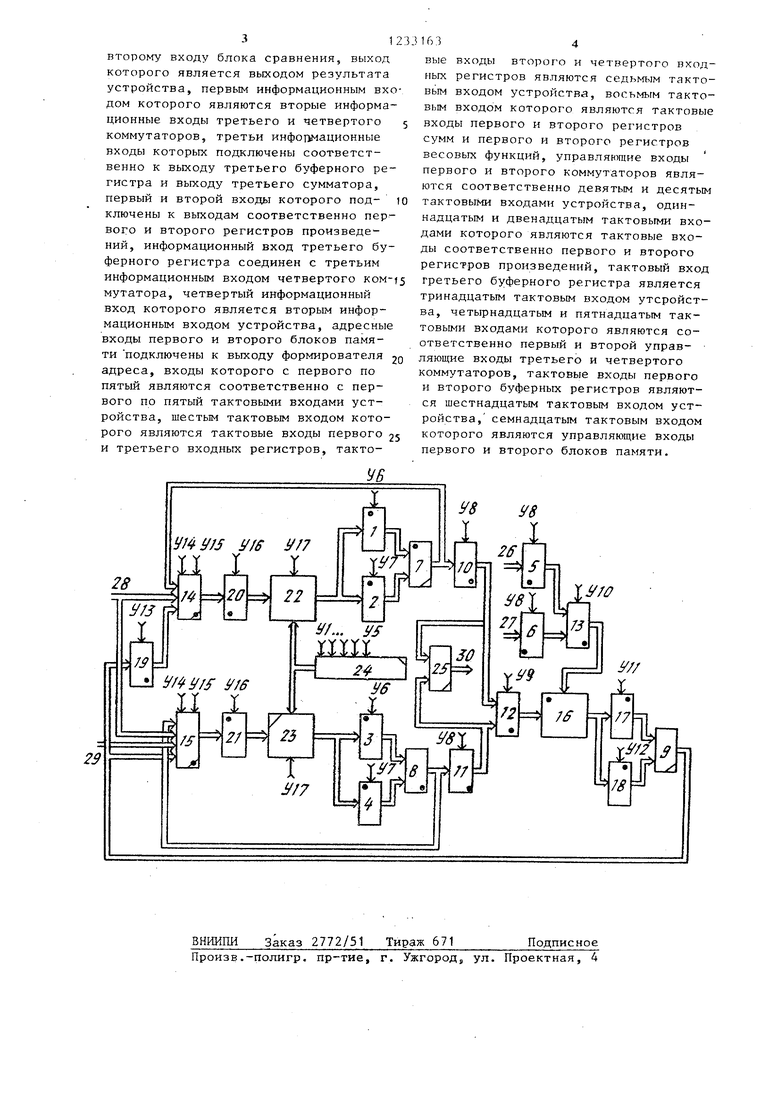

На чертеже представлена блок-схема устройства.

Устройство для реализации БПФ содержит входные регистры 1-4 входных операндов, регистры 5 и 6 весовой функции, сумматоры 1-9, регистры 10 и 11 (результатов) сумм, коммутаторы 12-15, умножитель 16, регистры 17 и 18 произведений, буферные регистры 19-21, блок и 22 и 23 памяти, формирователь 24 адреса, блок 25 сравнения. Входы 26 и-27 (комплексной) весовой функции, информационные входы 28 и 29 устройства и контрольный выход 30 устройства.

Устройство работает в двух режимах : режиме выработки коэффициентов дискретного преобразования Фурье (ДПФ и режиме контроля. В устройстве реализуется безызбыточный алгоритм БПФ с прореживанием по частоте, при котором после операции БПФ требуется разделение спектров, поэтому каждый режим имеет два подрежима. В первом подрежиме устройство реализует форму лы

ReA ReA + ReB ,

i+t I

Im A Im A + Im B; , ReB, (ReA, -ReB;) -ImCi (ImA -ImBj ), ImB,,ImC, (ReA,-ReB, )+ReC, (imA, -ImB, ) ,.

где A - первое комплексное число;

Bj - второе комплексное число;

Cj .- комплексная весовая функция Во втором подрежиме устройство реализует формулы

50

ReF.. ReA. + ReA , ,

11 1 N-l

ReF IniA + IraA , ImF, ImA - ImA; ; , ImF ReA,.- ReA ,

де F - комплексный коэффициент 1 (

ДПФ N-точечной действитель- . ной последовательности по 5 первому каналу; F. - комп.пексный коэффициент

ЛПФ N-тг,чечной действитель

0 5

0

5

0

. 5

ной Г1оследовате.пьности по второму каналу.

изобретения

Устройство для реализации быстрого преобразования Фурье, содержащее четыре входных регистра, первый сумматор, первый и второй регистры сумм, первый коммутатор, выход которого подключен к первому входу умножителя, выход которого подключен к информационным входам первого и второго регистров произведений, а первый и второй информационные входы первого коммутатора подключены к выходам соответственно первого и второго регистров весовой фу нкции, информационные входь )соторых являются входами соответственно реальной и мниной частей весовой функции устройства, второй кoм ryтaтop и три буферных регистра, отличающееся тем, что, с целью повышения достоверности функционирования, оно содержит формирователь адреса, второй и третий сумматоры, блок сравнения, третий и четвертый коммутаторы, выходы которых подключены к информацио шым входам соответственно первого и второго буферных регистров, выходы которьк под- клкпгены к информационным входам соответственно первого и второго блоков памяти,, выходы которых подключены соответственно; вькод первого блока памяти - к информационным входам первого и второго входных регистров, выход второго блока памяти - к информационным входам третьего и,четвертого входных регистров, выходы которых подключены соответственно к первому и второму входам первого сумматора, выход которого подключен к первому информационному входу четвертого коммутатора и информационному входу второго регистра суммы, выход которого подключен к первому входу блока сравнения и первому информационному входу второго кoм гyтaтopa, выход которого подключен к второму входу умножителя, вькоды первого и второго входных ре- 1 истров подключены соответственно к neipBOMy и второму входам второго сум- ма Гора, выход которого подключен к первому информационном входу третьего коммутатора и информационному входу первого регистра суммы, вькод которого подключен к второму информационному входу второго коммутатора и

3123

второму входу блока сравнения, выход которого является вьсходом результата устройства, первым информационным входом которого являются вторые информационные входы третьего и четвертого 5 коммутаторов, третьи инфог ационные входы которых подключены соответственно к выходу третьего буферного регистра и выходу третьего сумматора, первый и второй входы которого под- ю ключены к выходам соответственно первого и второго регистров произведений, информационный вход третьего буферного регистра соединен с третьим информационньм входом четвертого KOM-fj мутатора, четвертый информационный вход которого является вторым информационным входом устройства, адресные входы первого и второго блоков памяти подключены к выходу формирователя 2о адреса, входы которого с первого по пятый являются соответственно с первого по пятый тактовыми входами устройства, шестым тактовым входом которого являются тактовые входы первого 25 и третьего входных регистров, такто1634

вые входы второго и четвертого входных регистров являются седьмым такто- вь1м входом устройства, восьмым тактовым входом которого являются тактовые входы первого и второго регистров сумм и первого и второго регистров весовых функций, управляющие входы первого и второго коммутаторов являются соответственно девятым и десятым тактовыми входами устройства, одиннадцатым и двенадцатым тактовыми входами которого являются тактовые входы соответственно первого и второго регистров произведений, тактовый вход третьего буферного регистра является тринадцатым тактовым входом утсройст- ва, четьфнадцатым и пятнадцатым тактовыми входами которого являются соответственно первый и второй управляющие входы третьего и четвертого коммутаторов, тактовые входы первого и второго буферных регистров являют- ся шестнадцатым тактовым входом устройства, семнадцатым тактовым входом которого являются управляющие входы первого и второго блоков памяти.

-V 1л/71

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1327120A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1984 |

|

SU1242986A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1282156A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1982 |

|

SU1101835A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

Изобретение относится к области вычислительной техники и может быть использовано в устройствах, решающих задачи оценки спектра сигналов по алгоритьту быстрого преобразования Фурье (БПФ). Цель изобретения - повышение достоверности функционирования устройства путем осуществления контроля его работы. Цель изобретения достигается за счет введения в устройство формирователя адреса,двух сумматоров, блока сравнения и двух коммутаторов с соответствующими функциональными связями между ними и известными блоками устройства. Устройство работает в двух режимах: режиме выработки коэффициентов дискретного преобразования Фурье и режиме контроля. В устройстве реализуется безызбыточный алгоритм БПФ с прореживанием по чястотс, при котором после операции БПФ требуется разделение спектров . 1 ил. (Л tsD ОО СО О5 со

вниипи

Заказ 2772/51 Тираж 671

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Подписное

| Устройство для реализации преобразования фурье | 1977 |

|

SU687449A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для быстрого преобразования фурье | 1977 |

|

SU736113A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1983-12-05—Подача