Изобретение относится к вычислительной технике, в частности к технике запоминающих устройств, и может, . быть иснользовано в устройствах обработки информации, например, для изменения последовательности следования сигналов в алгоритмах преоб- разованит Фурье,

Цель изобретения - повышение быстродействия устройства.

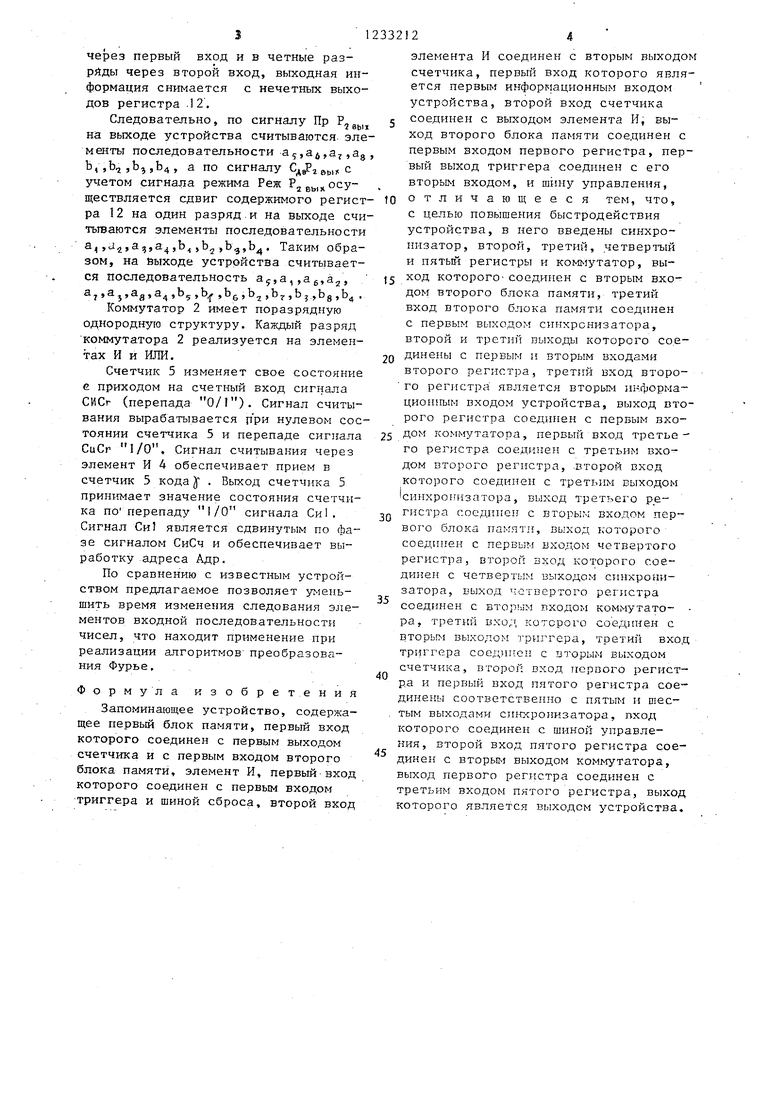

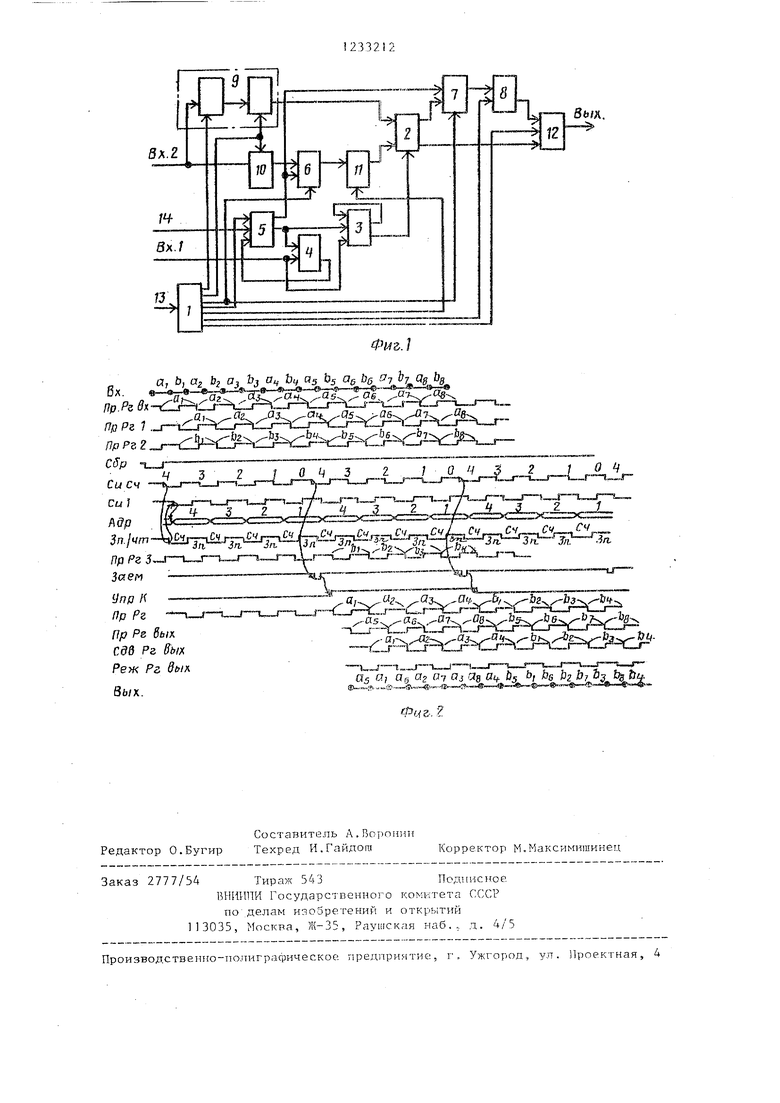

На фиг. 1 приведена функциональная схема предлагаемого устройства, на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит синхронизатор 1, коммутатор 2, триггер 3, элемент И 4, счетчик 5, блоки 6 и 7 памяти, регистры 8-12, шину 13 управления и шину 14 сброса.

Регистр 9 выполнен на двух последовательно соединенных регистрах.:

Устройство работает следующим образом.

Последовательности чисел а,,Ь,5 a2,b2,a,,,b,,,a jb., а,Ъ,а,Ъ, ag,bg поступают на информационный вход (Вх,2) устройства, начиная с некоторого числа у:, На вход (Вх.1) устройства подается код величины задержки, определяющий глубину переком поковки элементов последовательности например jj -4, На шину 14 сброса поступает сигнал, устанавливающий тригер З.и управляемой им коммутатор 2 ..в исходное состояние.. Исходное состоние коммутатора 2 заключается з подключении первого и второго входов соотвел ственно к его первому и второму выходам. Кроме Toroj через элемент И 4 сигнал сброса обеспечивает прием в счетчик 5 кода . На вход синхронизатора 1 поступает снг нал типа меандр, Сиггхронизатор I вырабатыз ает сиг налы Реж

i- -, ,..., Пр Р.

СдЛзых Р

г вы л

4т

Зп/

Пр , С,

Р,

Пр Р„3, Пр р.

2 DKJ -У -, J ч/ч-г, C,,

2-, i .H Р 5 поступающие соответственно на синхровходы регистров 8- П, входы запись/чтение блоков 6 и 7 памяти и на счетный вход счетчика 5, Эти сигналы (фиг, 2) получены из входного сигнала синхронизатора путем задержки на логических элементах (повторителях5 инверторах).

Временные диаграммы (фиг. 2)позволяют проследить работу устройства

Входная последовательность чисел поступает на информационные -входы регистров 9 и 10 и принимается в реР. 1

гистры по сигналам Пр Ру Пр соответственно. При этом на выходах регистров 9 и 0 считываются соответственно последовательности чисел

s

0

0

а .,а j,a,a.,а. ,

6

BI ,ag и b, ..b ,b.

b, jb, ,bg ,b7 ,b(,. Вторая последовательность чисел записывается в первый блок 6 памяти. Блок 6 под действием приходящих на его адресный вход сигналов Адр (с выхода счетчика 5) и на вход запись/чтение сигнала Зп/Чт (с выхода синхронизатора 1) реализует функцию задержки, обеспечивая считывание указанной последовательности через четыре такта с момента ее поступления на его вход. Считанная последовательность чисел принимается в регистр 1 1 по ср гналу Пр , К моменту L появления на выходе регистра 1 числа Ь, счетчик 5 принимает на счетный вход у 4 перепадов 0/1 сигнала СиСч (начиная с момента установки счетчика 5 сигналом Сбр) и вырабатывает сигнал 5 считывания, под действием которого триггер 3, работающий как Т--триггер, изменяет свое состояние на инверсное .

При этом сигнал Упр.К. поступающий с выхода триггера 3 на управляющий вход коммутатора 3, вызывает его 11;-:реключение, в результате которого первый и второй входы о каз ша- ются подключенными соответственгю к второму/ к перзомз его вь1ходам.

Указанное переключение коммутатора 2 обеспечивает поступление на информационный вход второго блока 7

амяти последовательности а,а,а, а л до, момента времени L и последова- тельжзсти Ь, ,Ь,, ,b,b , считанной с ыхода регистра 11 после момента L.

Бторой блок 7 памяти, работающий аналогич но первому блоку 6 памяти, задерживает поступающую на его формационный вход последовательность ка такта, которая далее принимается в регистр 8 (по сигналу ПрР) и с его выхода поступает на второй вход регистра 12,

Через второй выход ког-я- утатора 2 на первый вход регистра 12 поступают последовательность чисел а г, а,а s3g (до момента времени L) и Ь5,Ьй,Ьу,Ьд (после момента L).

Регистр 12 является сдвиговым. По сигналу Пр Р-гвых записывается информация в-нечетные разряды

3

через первый вход и в четные раз- рйды через второй вход, выходная информация снимается с нечетных выходов регистра .1 2.

Следовательно, по сигналу Пр ,, на выходе устройства считываются, элементы последовательности ау,ай,а,ад b,,b,,b, ,Ь4, а по сигналу C jewxC учетом сигнала режима Реж РгвыхО У ществляется сдвиг содержимого регистра 12 на один разряд.и на выходе счи тьгеаются элементы последовательности а,,а2,а,,а,,b,b. Таким образом, на выходе устройства считывается последовательность а5,а,,аб,а2, а,,а j,a,a ,Ь5 ,Ь ,bg,b,, ,bj,,b3 ,b8,b .

Коммутатор 2 имеет поразрядную однородг ую структуру. Каждый разряд коммутатора 2 реализуется на элементах И и ИЛИ.

Счетчик 5 изменяет свое состояние е приходом на счетный вход сигнала СИСг (перепада 0/1). Сигнал считывания вырабатывается п ри нулевом состоянии счетчика 5 и перепаде сигнала CuCr 1/0. Сигнал считывания через элемент И 4 обеспечивает прием в счетчик 5 кода . Выкод счетчика 5 принимает значение состояния счетчика по перепаду 1/0 сигнала Си1, Сигнал Си1 является сдвинутым по фазе сигналом СиСч и обеспечивает выработку .адреса Адр.

По сравнению с известным устройством предлагаемое позволяет уменьшить время изменения следования элементов входной последовательности чисел, что находит применение при реализации алгоритмов преобразования Фурье...

Формула изобретения Запоминающее устройство, содержащее первый блок памяти, первый вход которого соединен с первым выходом счетчика и с первым входом второго блока памяти, элемент И, первый вход которого соединен с первым входом триггера и шиной сброса, второй вход

332124

элемента И соединен с вторым выходом счетчика, первый вход которого является первым инфорршционным входом устр.ойства, второй вход счетчика с соединен с выходом элемента И, выход второго блока памяти соединен с первым входом первого регистра, первый выход триггера соединен с его вторым входом, и шину управления, to отличающееся тем, что, с целью повышения быстродействия устройства, в него введены синхронизатор, второй, третий, четвер1Ъ1й и пятьш регистры и коммутатор, вы- 5 ход которого соединен с вторым вхо- . дом второго блока памяти, третий вход второго блока памяти соединен с первым выходом синхронизатора, второй и третий пыхо,ць которого со.е- 2Q динены с первым и вторым входами

второго регистра, третий вход второ- го регистра является вторым информационным входом устройства, выход второго регистра соединен с первым вхо- 25 дом коммутатора, первый вход третье го ред истра соедннен с третьим входом второго регистра, .второй вход которого соединен с третьим выходом сннхроннзатора, выход третьего ,„ гистра соедипец с вторым входом первого блока памяти, вь. ход icoToporo соединен с первым входо четвертого регистра, второй вход которого соединен с четвертым выходом синхронизатора, выход четвертого регистра соединен с вторым входом коммутатора, третий вхо; котсрого соединен с вторым выходом триггера, третий вход триггера соединен с вторым выходом счетчика, второй вход первого регистра и первый вход пятого регистра соединены соответственно с пятым и шестым выходами С1П.1хронизатора, пход которого соединен с шиной управления, второй вход пятого регистра соединен с вторь&1 выходом коммутатора, выход первого регистра соединен с третьим входом пятого регистра, выход которого является выходом устройства.

35

40

45

lU-ьЛ

Вы,

t-

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с контролем информации | 1986 |

|

SU1437924A1 |

| Генератор знаков | 1981 |

|

SU963074A1 |

| Генератор случайных чисел | 1981 |

|

SU980093A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Устройство задержки | 1990 |

|

SU1750036A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для считывания графической информации | 1988 |

|

SU1536413A1 |

| Устройство синхронизации источников сейсмических сигналов | 1991 |

|

SU1787278A3 |

Изобретение относится к вычислительной технике, Б частности к технике запоминающих устройств, и может быть использовано в устройствах обработки информации для изменения последовательности следования сигналов в- алгоритмах преобразования Фурье. С целью повьшения быстродействия устройство дополнительно имеет синхронизатор и четыре регистра, которые позволяют уменьшить время изменения следования элементов входной последовательности чисел. 2 ил. ю W со ю

Фмг./

а, Ь, Ог Ьг о, bj о by bj а Ь 7 &.% &5

д д - - д-«у-я « -Г.П--rU-gii-иь,Ж-ив-и

Пр Ре 5ь/х саа Рг Вш Ре ж Ра дых.

вык.

-Ьг- Ьз- liif Т Г П.

-Jjes- b/

:5 i :f cK:fF4i

Составитель А.Воронин Редактор О.Бугир Техред И.Гайдога Корректор М.Максимишинец

Заказ 2777/54 Тираж 5АЗПодписное

ВНИИПИ Государственного комитета СССР

ПО делам изобретений и открытий 113035, Москва, Ж-ЗЗ, Рауигская наб., д. 4/5

Производственно-тюлиграс рическое предприятие, i-, Ужгород, ул. Проектная, 4

..Е

Авторы

Даты

1986-05-23—Публикация

1984-09-21—Подача