Изобретение относится к вычислительной техникЕЭ Б частности к запоминающим устройствам, и может быть использовано в устройствах обработки информации для изменения последовательности сле,1 /;)ваиия сигнало з в алгоритмах преоСразования Фурье,

Цель изобретения - лтозышенке достоверности функционирования уст-- ройства

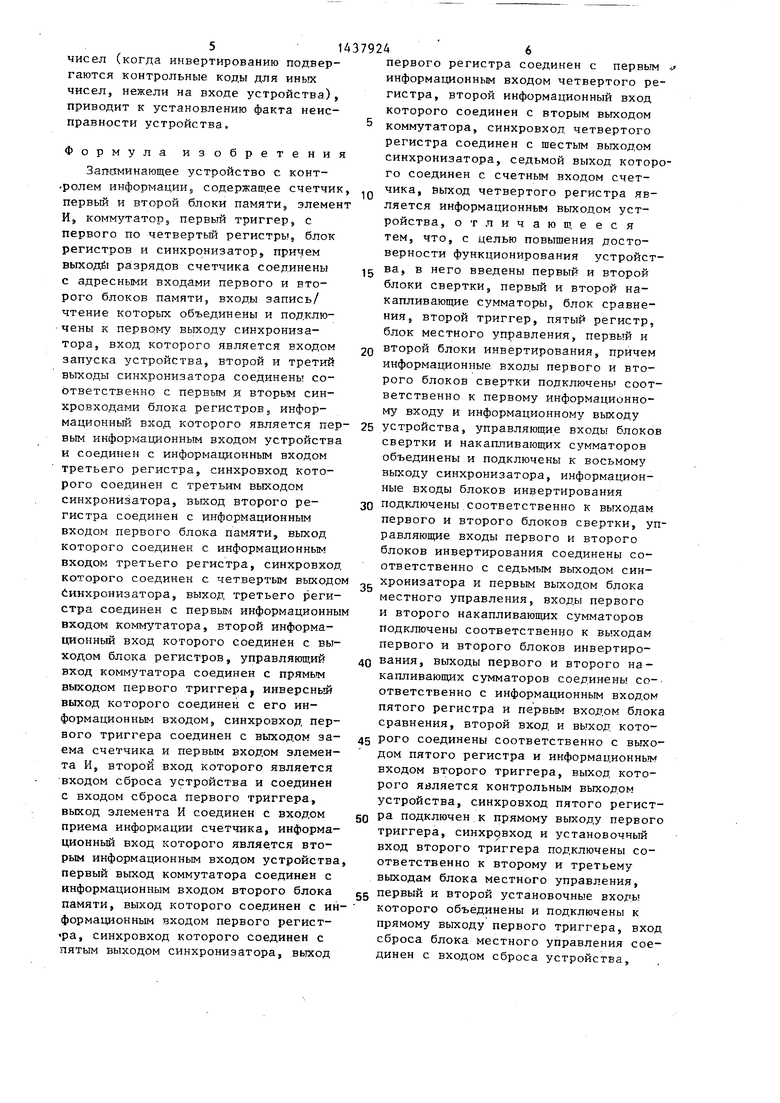

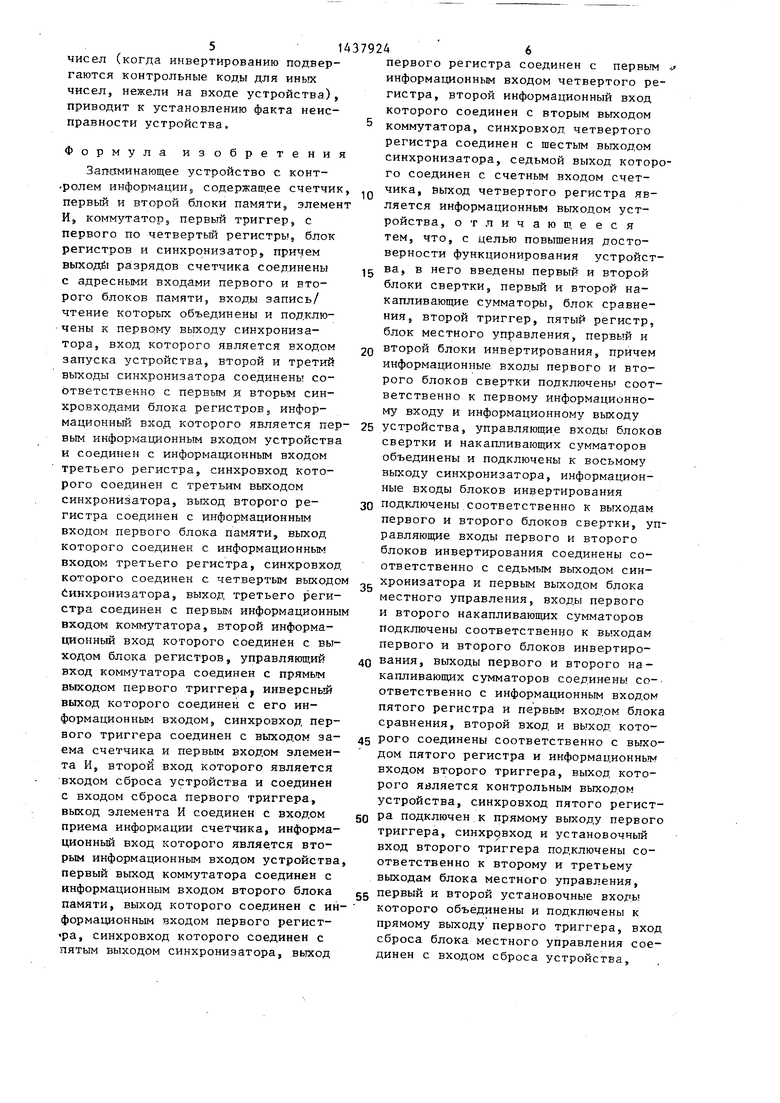

На чертеже г зображена структз/ркая схема устройства с контролем инфор-- мации,.

Устройство содерлсит сртнхрониза- тор 1, коммутатор 2,, ггерььм триггер 3,, элемент И А, счетчик 5,. первый 6 и второй 7 блоки памяти5 первый регистр 8,, блок 9 регистроэз состоящий например;, из двух последователь- Но соединенньгх регистров (не пока заны) 5 второй 10, тре гйй 11 ii четвертый 12 регистры, первьи / 13 я второй 14 блоки инвертирования;, пятый регистр 15э первьП блок 16 сверткиj ; состоящий из регистра 17 и узлэ 18 свертки по модулю три,, второй блок 19 свертки,, состояЕщта из узла 20 свертки по модулю три и регистра 2К/ блок 22 сравнения, второй триггер 7, блок 24 местного управления., состоящий из триггеров 25--27; первый накапливающий сумматор 28

Устройство имеет первьш информационный вход 29 вход, 30 запуска, второй информаьронный вход 31;, вход 32 сброса, информационный выход 335 кон трольный выход, 34,

Сумматор 28 состоит из узла 35 суммирования по модулю три с накоплением и регистра 36, Устройство также содержит второй накапливающий сумматор 37., состоящ п-г из узла 38 суммирования по модулю три с накоплением и регистра 39.

Устройство работает cлeдyкJщшv . образом

Последовательности -{исел а. Ь,, ,,

J 5 b2 5 а J J D ;, J а ,; 6 3,--j 5

ад S bg поступают на вход

29 устройствао На вход 31 устройства подается код, величины задержки , , определяющий глубину перекомпоновки элементов последовательности, например У 4, На вход, 32 поступает сигнал, устанавливающий триггер 3 и управляемый им ко Ф1утатор 2 в исходное состояние. Исходное состояние коммутатора 2 заключается в подключении первого и второго входов соответственно к его первому и второму выходам. Кроме того, через злемент И 4 сигнал сброса обеспечивает прием в счетчик 5 кода ,у . На вход. 30 устройства поступает сигнал типа Ме- сНДР. Синхронизатор 1 вырабатывает

сигналы, поступающие на управляющий вход регистра 12 на синхровходы блока 9 и регистра 10, на входы Запись - чтение блоков 6 и 7 памяти, на синхровходы регистров 11 и 8,

на счетный вход счетчика 5, на син- хрозходы регистров 17, 21, 36 и 39. Эти сигналы получены из входного сиг-нала синхронизатора 1 путем задержки на логических элементах.

Входная доследовательность чисел поступает на информационные входы регистров 9 и 10. При этом на выходах регистров 9 и 10 считываются соответственно последовательности

2 5

Ь, bjj Ьл,, b

Эб -г bg , b , b.

чисел a,.

Яд И b,, s Ujj U, , Ug , u , u.g

Втор;ая последовательность чисел записывается в первый блок 6 памяти. Блок 6 под действием приходящих

на его адресный вход сигналов с выхода счетчика 5 и на вход Запись - чтение сигнала с выхода синхронизатора 1 реализует функцию задержки, обеспечивая считывание указанной пос,педовательности через четыре такта с момента ее поступления на его вход. Считывание пос,педовательности чисел принимается в регистр 11, к моменту L появления на выходе

регистра 11 числя Ь, счетчик 5 принимает на счетный вход у перепадов 0/1 и вьфабатывает сигнал считывания, под действием которого триггер 3, работающий как Т-триггер,

изменяет свое состояние на инверсное ,- При этом сигнал, поступающий с выхода триггера 3 на управляющий вход коммутатора 3, вызывает его переключение, в результате которого первый

и второй входы оказываются подклю- ,ченными соответственно к второму и первому его выходам.

Указанное переключение коммутатора 2 обеспечивает поступление на информационньй вход второго блока 7 паг-шти последовательности а,, , а.

а до момента времени L и последозательности Ь, , Ъ

Ь, J, Ъ ,

считайной с выхода регистра 11 после этого момента. Второй блок 7 памяти, работающий аналогично первому блоку 6 памяти, задерживает поступающую на его информапионный вход последовательность на i 4 такта, которая далее принимается в регистр 8 и с его выхода поступает на вход, регистра 12. Через второй выход коммутатора 2 на вход регистра 12 поступают последовательности чисел а, Pg, а, а (до момента времени L) и bj, b , b , bg (после момента L),,

Регистр 12 является сдвиговым. В него записывается информация в нечетные разряды через первый вход и в четные разряды через второй вход, выходная информация снимается с нечетных выходов регистра 12.

На выходе 31 устройства считываются элементы последовательности а., ag , а,, а, Ь , bj, Ь,, Ь,, осуществляется сдвиг содержимого регистра 12 на один разряд, и на выходе считываются элементы последовательности а , а , а S а, Ь,, Ь,, , Ь. Таким образом, на выходе 31 устройства считывается последовательность

N

6

4L

Ч

а.з

bg, b,, b, , b, , bo , b

6

7 3 8 4

изменяет свое

b,,

Счетчик 5 изменяет свое состояние с приходом на его счетный вход сигнала (перепада 0/1). Сигнал считывания вырабатывается при нулевом состоянии счетчика 5 и перепада сигнала 1/0. Сигнал считывания через элемент И 4 обеспечивает прием в счетчик 5 кода у . Выход счетчика 5 принимает значение состояния счетчика по перепаду 0/1.

Входная последовательность чисел поступает через вход 29 устройства также на вход узла. 18, который определяет для чисел последовательное- ти их контрольные коды са; и сЬ; (i I,D) по модулю три (остатки от деления чисел на три). По синхросигналам, поступающим с восьмого выхода-синхронизатора 1, полученные контрольные коды принимаются регистром 17, ас его выхода подаются на информационный вход блока 13, На управляющий вход блока 13 поступает сигнал с седьмого выхода синхронизатора 1. Под действием этого сигнала инвертируется каждд 1й второй конт- .рольный код последовательности, пос- тупающей на вход блока 13. С выхода

.

437924

блока 13 полученная контрольная по- сл&довнтельность контролькьт кодор сЪ,, са,, сЬ, ,, сЪ, ,

сЬ, са , сЬ, са, сЪ са„ , сЬ., поступает на

С,,

сЬ, cji.

Я 4

5- -6 б -°7

.. , ug поступает на вход узла 35, которы : вместе с регистром 36 образует накапливающий сумматор 28, обеспечивающий вычисление суммы по

10 модулю три K,g кодов контрольной последовательности .

Полученная сумма по сигналу, поступающемз с выхода триггера 3, принимается в регистр 15.

15 Выходная последовательность чисел с выход а регистра 12 поступает также на вход, блока 20 свертки, который определяет для чисел этой последовательности контрольные коды по модулю три:

20 са; и сЬ;. Полученные контрольные ко- ,цы принимаются в регистр 21, ас его выхода поступают на информационный вход блока 14. На управляющий вход, блока 14 поступает сигнал с инверс25 кого выхода триггера .25, под действием которого контрольные коды сЬ; (i 1,8) инвертируют свои значения. Полученная контрольная последователь0

5

ность са,

в

сЬ, , сЬо

са,,, ,

са, , cag, са, са, са,.

сЬ,., сЬ , сЬ,

сЬ

5-

, Cbg. , V-L..J , Jf ,

, --ug , -поступает на вход сумматора 37, обеспечивающего вычисление суммы по модулю три кодов указанной контрольной последовательности.

Код H,g с выхода регистра 15 и код с выхода регистра 39 поступают на входы блока 22 сравнения. Результат сравнения кодов запомина

ется триггером 23 по заднему фронту сигнала, поступающего с выхода триггера 27.

Результат сравнения кодов с выхода триггера 23 поступает в качестве сиг- нала контроля на контрольный выход. 34 устройства.

Поскольку коды H|g и K,g являются суммами по модулю три одних и тех же контрольных кодов, характеризующих соответственно входную и выходную последовательность чисел, то при правильной работе устройства коды Н, и Kf равны друг другу, а сигнал контроля указывает на отсутствие ошибок на-выходе 33 устройства.

Несовпадение кодов Н и , вызванное искажением отдельных чисел в выходной последовательности или нарущением порядка следования

чисел (когда инвертированию подвергаются контрольные коды для иных чисел, нежели на входе устройства), приводит к установлению факта неисправности устройства.

Формула изобретения

Запоминающее устройство с конт- .ролей информации5 содержащее счетчик первый и второй блоки памяти, элемен И, коммутатор, первый триггер, с первого по четвертый регистрЫе блок регистров и синхронизатор, причем ВЫХОДЕ разрядов счетчика соединены с адресными входами первого и второго блоков памяти, входы запись/ чтение которых объединены и под.клю- - чены к первому выходу синхронизатора, вход которого является входом запуска устройства, второй и третий выходы синхронизатора соединены соответственно с первым и вторьм син- хровходами блока регистров, информационный вход которого является первым информационным входом устройства и соединен с информационным входом третьего регистра, синхровход которого соединен с третьим выходом синхронизатора, выход второго регистра соединен с информационным входом первого блока памяти, выход которого соединен с информационным входом третьего регистра, синхровход которого соединен с четвертым выходо Синхронизатора, выход третьего регистра соединен с первьм информационны входом коммутатора, второй информационный вход которого соединен с выходом блока регистров, управляющий вход коммутатора соединен с прямьм выходом первого триггера, инверсный выход которого соединен с его информационным входом, синхровход. первого триггера соединен с выходом за- ема счетчика и первым входом элемента И, второй вход которого является входом сброса устройства и соединен с входом сброса первого триггера, выход элемента И соединен с входом приема информации счетчика, информационный вход которого является вторым информационным входом устройства первый выход коммутатора соединен с информационным входом второго блока памяти, выход которого соединен с иформационным входом первого регист- «ра, синхровход которого соединен с пятым выходом синхронизатора, выход

5

первого регистра соединен с первьп информационным входом четвертого регистра, второй информационный вход которого соединен с вторым выходом коммутатора, синхровход четвертого регистра соединен с шестым выходом синхронизатора, седьмой выход которого соединен с счетным входом счетчика, йыход четвертого регистра является информационным выходом устройства, отличающе вся тем, что, с целью повышения достоверности функционирования устройства, в него введены первый и второй блоки свертки, первый и второй накапливающие сумматоры, блок сравнения, второй триггер, пятый регистр, блок местного управления, первый и

Q второй блоки инвертирования, причем информационные входы первого и второго блоков свертки подключены соответственно к первому информационному входу и информационному выходу

5 устройства, управляющие входы блоков свертки и накапливающих сумматоров объединены и подключены к восьмому выходу синхронизатора, информационные входы блоков инвертирования подключены.соответственно к выходам первого и второго блоков свертки, управляющие входы первого и второго блоков инвертирования соединены соответственно с седьмым выходом синхронизатора и первым выходом блока местного управления, входы первого и второго накапливающих сумматоров подключены соответственно к выходам первого и второго блоков инвертиро0 вания, выходы первого и второго накапливающих сумматоров соединены со-- ответственно с информационным входом пятого регистра и первым входом блока сравнения, второй вход и выход кото5 рого соединены соответственно с выходом пятого регистра и информационнь м входом второго триггера, выход которого является контрольным выходом устройства, синхровход пятого регист0 ра подключен к прямому выходу первого триггера, синхровход и установочньш вход второго триггера подключены соответственно к второму и третьему выходам блока местного управления,

g первый и второй установочные входы которого объединены и подключены к прямому выходу первого триггера, вход сброса блока местного управления соединен с входом сброса устройства.

0

5

71437924

первый и второй синхровходы блока ответственно к четвертому и шестому местного управления подключены со- выходам синхронизатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для задержки цифровой информации | 1986 |

|

SU1383325A1 |

| Запоминающее устройство | 1984 |

|

SU1233212A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ РАСПРЕДЕЛЕНИЯ РАВНОМЕРНО ЦЕЛОЧИСЛЕННЫХ ПСЕВДОСЛУЧАЙНЫХ ВЕЛИЧИН | 1990 |

|

RU2042187C1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство цифрового интегрирования | 1986 |

|

SU1345192A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1619326A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| Устройство для сдвига информации | 1983 |

|

SU1109807A1 |

Изобретение относится к вычис- лительнок технике, в частности к запоминающим устройствам, и может быть использовано в устройствах обработки информации для изменения последовательности следования сигналов в алгоритмах преобразования Фурье. Цель изобретения - повьшение достоверности функционирования устройства. Устройство содержит синхронизатор 1, триггеры 3 и 23, счетчик 5, блоки 6 и 7 памяти, регистры 8, 10-12, 15, блок 9 регистров, блоки 13 и 14 инвертирования, блоки 16 и 19 свертки по модулю три, блок 22 сравнений, накапливающие сумматоры 28 и 37 по модулю три, блок 24 местного управления, состоящий из триггеров 25-27. ил. i (Л

| Электроника | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Запоминающее устройство | 1984 |

|

SU1233212A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-11-15—Публикация

1986-10-13—Подача