блока 11. На второй вход этого блока поступает напряжение обратной связи с вторичной обмотки 4 трансформатора 5 через выпрямитель 10. В блоке управления формируют сигнал рассогласования с помощью элементов цифровой логики. Этот сигнал через соответствующий элемент И поступает на соотИзобретение относится к электротехнике, в частности к источникам вторичного электропитания, предусматривающим стабилизацию и преобразова-. ние постоянного напряжения в постоян- ное с Iальванической изоляцией входных и выходных цепей, и может найти применение для питания аппара:туры широкого назначения.

Цель изобретения - расширение диапазона изменения входного напряжения при одновременном уменьшении маесы и объема.

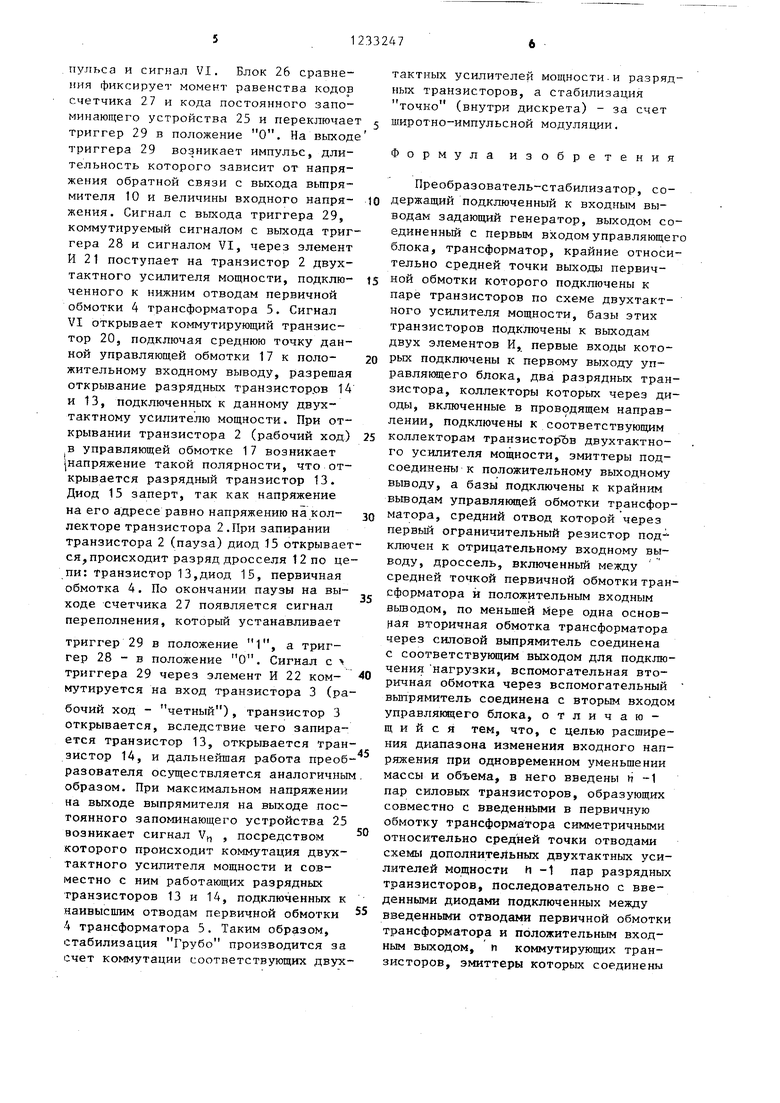

На чертеже представлена функциональная схема преобразователя-стаби- лизатора.

Устройство -содержит подключенный к выходным выводам задающий генератор 1, 2 Л транзисторов 2 и 3 усилителей (МОЩНОСТИ, эмиттеры которых подключе- ны к отрицательному входному выводу, а коллекторы - к соответствующим симметричным выводам первичной обмотки 4 трансформатора 5. По меньшей мере одна основная вторичная обмотка 6, -6„ трансформатора через силовой выпрямитель 7 соединена с соответствующим выходом для подключения нагрузки 8. Вспомогательная обмотка 9 трансформатора через вспомогательный выпрями- тель 10 соединена с вторым входом уп- равляющего блока 11. Преобразователь снабжен дросселем 12, включенным между средним выводом первичной обмотки 4 трансформатора 5 и положительным входным выводом 2 п разрядных транзисторов 13 и 14, эмиттерами подключенных к положительному входному выводу, коллекторами через диоды 15 и 16 соединенных с соответствуклцими

симметричными выводами первичной обветствукяций транзистор двухтактного усилителя мощности, подключенного к отводам первичной обмотки 4 трансформатора 5. Таким образом про- исходит стабилизация Грубо. Стабилизация Точно (внутри дискрета) производится за счет широтно-им- пульсной модуляции. 1 ил.

мотки 4 трансформатора 5. Базы разрядных: транзисторов подключены к крайним выводам соответствующих управля- .ющих обмоток 17, Развязывающие диоды 18 включены в прямом направлении между коллекторами транзисторов 2 и 3 и отводами первичной обмотки 4 трансформатора. Средние выводы обмоток 17 через резисторы 19 подключены к отрицательному входному выводу, а через соответствующий коммутационный транзистор 20 - к положительному входному выводу. Элементы И 21 и 22 первыми входами соединены с первым выходом управляющего блока 11, попарно соединенные вторые входы элементов И 21 и 22 соединены с одним из группы вькодов-управляющего блока 11, третьи входы элементов И 21 соединены с вторым выходом управляющего блока 11, третий выход которого соединен с третьими входами элементов И 22.

Управляющий блок 11 содержит последовательно соединенные преобразователь 23 постоянного напряжения в код, регистр 24 и постоянный запоминающий блок (накопитель) 25, группа п выходов которого является выходами блока 11, другая группа его выходов соединена с входом блока 26 сравнения. Другие входы блока сравнения соединены с выходом счетчика 27. Выход переполнения счетчика 27 соединен со счетным входом триггера 28 и с 5 входом триггера 29, R - вход которого соединен с выходом схемы 26 сравнения. Выход триггера 29 является первым выходом блока, прямой и инверсный выходы триггера 28 являются вторым и третьим выходами блока.

прямой выход триггера 28 соединен с установочными входами регистра 24. Счетный вход счетчика 27 является первым входом блока, а вход преобразователя 23 напряжения в код - вто- |рым входом блока.«

Входы преобразователя 30 напряжения- в код являются третьим и четвертым входами управляющего блока, соединенными соответственно с входными клеммами преобразователя. Выходы преобразователя 30 напряжения в код соединены с информационными входами регистра 31, выход которого соединен с второй группой адресных входов Б псстоянного запоминающего устройства 25, а установочный вход подсоединен к прямому выходу триггера 28. Первая группа адресных входов А постоянного запоминающего блока 25 соединена с выходом регистра 24.Таким образом, адрес, по которому происходит обращение к постоянному запоминающему устройству 25, формируется из кодов АЖБ, формируемых на выходе регистров 24 и 31, где символ означает склеивание кодов. Б ячейки постоянного запоминающего блока 25 по соответствующим адресам производят предварительную запись кодов длительностей импульсов.

Управляющий блок 11 представляет собой цифровой широтно-импульсный модулятор с переключением каналов преобразования (пвухтактных усилите- 35 лей мощности и разрядных транзисторов) .

Частота генератора 1 и разрядность счетчика 27 выбираются исходя из тре- O бований к частоте щиротно-модулиро- ванных импульсов на выходе информационного триггера 29. Триггер 28 цикла сигналом с прямого выхода разрешает работу транзистора 2 (нечетный цикл),5 а сигналом с инверсного выхода - работу транзисторов 3. Длительность импульса на выходе информационного триггера 29 формируется сигналом с выхода блока 26 сравнения, обнуляющим 50 триггер 29. Момент формирования сиг- нала на выходе схемы 26 сравнения определяется кодом на выходе постоянного запоминающего блока 25. Постоянный запоминающий блок 25 предназна- чен для хранения микрокоманд VI+ V,, , выбирающих канал преобразования и набор длительностей импульсов, код

j

Q - о 5

которых записывается по определергным адресам совместно с микрокомандами VI- Vj, . Причем набор длительностей импульсов, содержащийся в постоянном запоминающем устройстве 25, может изменяться в зависимости от величины и типа нагрузки. Преобразователь 23 напряжения в код совместно с регистром 24 формирует адрес А, а преобразователь 30 напряжения в код совместно с регистром 31 п адрес Б. При этом полный адрес обращения к постоянному накопителю равен А Б. Код Б указы- ,вает зону постоянного накопителя 25. |В соответствии с данным кодом в зоне {постоянного накопителя 25 записьгеает- ся соответствующая микрокоманда Yf, . Код длительности импульса определяет код адреса-А обращения к постоянному накопителю 25 один раз за два цикла. При этом адрес обращения к постоянному накопителю 25 изменяется в зависимости от напряжения обратной связи с вьшрямителя 10, а код адреса Б - в зависимости от величины входного ряжения.

Преобразователь работает следующим образом.

Задающий генератор 1 формирует прямоугольные импульсы, которые поступают на первый вход управляющего блока 11, на второй вход которого поступает напряжение обратной связи с вторичной обмотки 9 трансформатора 5 через выпрямитель 10. Пропорционально напряжению обратной связи на выходе блока 23 возникает код, который фиксируется на выходе регистра 24 в момент переключения триггера 28 сигналом с его прямого выхода. При этом в регистре 31 фиксируется код преобразователя 30 напряжения в код, пропорциональный входному напряжению. Переключение триггера 28 происходит при переполнении счетчика 27. Кроме того, сигнал переполнения счетчика 27 переключает триггер 29 в положение 1. Сигнал с выхода регистров 24 и 31 поступает на адресный вход постоянного накопителя 25, в который заранее заносится информация о длительностях импульсов в двоичном коде и номере коммутируемого канала (VI+ +Vj,). Например, при минимальном выходном напряжении на выходе выпрямителя 10 на выходе постоянного запоминающего блока 25 возникают максимальный код длительности выходного импульса и сигнал VI. Блок 26 сравнения фиксирует момент равенства кодов счетчика 27 и кода постоянного запоминающего устройства 25 и переключает триггер 29 в положение О. На выходе триггера 29 возникает импульс, длительность которого зависит от напряжения обратной связи с выхода выпрямителя 10 и величины входного напря- жения. Сигнал с выхода триггера 29, коммутируемый сигналом с выхода триггера 28 и сигналом VI, через элемент И 21 поступает на транзистор 2 двухтактного усилителя мощности, подклю- ченного к нижним отводам первичной обмотки 4 трансформатора 5. Сигнал VI открывает коммутирующий транзистор 20, подключая среднюю точку данной управляющей обмотки 17 к поло- жительному входному выводу, разрешая открывание разрядных транзисторрв 14 и 13, подключенных к данному ц,вук- тактному усилителю мощности. При открывании транзистора 2 (рабочий ход) в управляющей обмотке 17 возникает |напряжение такой полярности, что открывается разрядный транзистор 13. Диод 15 заперт, так как напряжение на его адресе равно напряжению на кол- лекторе транзистора 2,При запирании транзистора 2 (пауза) диод 15 открывается, происходит разряд дросселя 1 2 по цепи: транзистор 13, диод 15, первичная обмотка 4. По окончании паузы на выходе счетчика 27 появляется сигнал переполнения, который устанавливает

триггер 29 в положение 1, а триггер 28 - в положение О. Сигнал с триггера 29 через элемент И 22 ком- мутируется на вход транзистора 3 (рабочий ход - четный), транзистор 3 открывается, вследствие чего запирается транзистор 13, открывается транзистор 14, и дальнейшая работа преобразователя осуществляется аналогичным образом. При максимальном напряжении на выходе выпрямителя на выходе постоянного запоминающего устройства 25 аозннкает сигнал V, , посредством которого происходит коммутация двухтактного усилителя мощности и совместно с ним работающих разрядных транзисторов 13 и 14, подключенных к наивысшим отводам первичной обмотки 4 трансформатора 5. Таким образом, стабилизация Грубо производится за счет коммутации соответствующих двух

j 0 5 0 5 о

0 .

5

5

0

тактных усилителей мощности.и разрядных транзисторов, а стабилизация точно (внутри дискрета) - за счет жиротно-импульсной модуляции,

Формула изобретения

Преобразователь-стабилизатор, содержащий подключенный к входным выводам задающий генератор, выходом соединенный с первым входом управляющего блока, трансформатор, крайние относительно средней точки выходы первичной обмотки которого подключены к паре транзисторов по схеме двухтактного усилителя мощности, базы этих транзисторов подключены к выходам двух элементов И, первые входы которых подключены к первому выходу управляющего блока, два разрядных транзистора, коллекторы которых через диоды, включенные в проводящем направлении, подключены к соответствующим коллекторам транзистор бв двухтактного ус:ипителя мощности, эмиттеры подсоединены к положительному выходному выводу, а базы подключены к крайним выводам управляющей обмотки трансформатора, средний отвод которой через первьш ограничительный резистор под- - ключен к отрицательному входному выводу, дроссель, включенный между средней точкой первичной обмотки трансформатора и положительным входным вьшодом, по меньшей riepe одна основ- 1ая вторичная обмотка трансформатора через силовой выпрямитель соединена с соответствующим выходом для подключения нагрузки, вспомогательная вторичная обмотка через вспомогательный выпрямитель соединена с вторым входом управляющего блока, отличающийся тем, что, с целью расширения диапазона изменения входного напряжения при одновременном уменьшении массы и объема, в него введены fi -1 пар силовых транзисторов, образующих совместно с введенными в первичную обмотку трансформатора симметричными относительно средней точки отводами схемы дополните.йьных двухтактных усилителей мощности h -1 пар разрядных транзисторов, последовательно с введенными диодами подключенных между введенными отводами первичной обмотки трансформатора и положительным входным выходом, п коммутирующих транзисторов, эмиттеры которых соединены

с положительным входным вьшодом, базы, подключенные к соответствующему из группы ц ВЫХОДА управляющего блока, а коллекторы подсоединены к соответ- ствующему среднему отводу И управляющих обмоток трансформатора, 2 и -2 элементов И, выходы которых соединены с соответствующими управляющими вьшо- дами II -1 пар транзисторов двухтакт- ных усилителей мощности, первые входы соединены с первым выходом управляющего блока, вторые входы первой группы из h элементов И соединены с вторым выходом управлякицего блока,. вторые входы второй группы элементов И соединены с третьим выходом управляющего блока, третьи выходы ZH элементов И соединены попарно с соответ-- ствующим из групйь п выходом уп- равляющего блока, положительные и отрицательные входные выводы подключены соответственно к третьим и четвертым входам управляющего блока, причем управляющий блок включает в себя две цепи из последовательно соединенных преобразователя постоянного тока в код и регистра, постоянный запоминающий узел, ц выходных выводов коРедактор О. Бугир

еоставитель Ю. Опадчий

Техред М.Ходанич . Корректор Л. Патай

Заказ 2779/55Тираж 631Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

торого подключены к группе из 4. выходов управлякнцего блока, другая группа выходов постоянного запомина- кнцего узла соединена с входом узла сравнения, другие входы которых сое- динены с выходом счетчика, выход переполнения которого соединен с счетным входом триггера цикла и с 5 -входо информационного.триггера, R -вход которого соединен с выходом узла сравнения, выход информационного триггера подключен к первому выходу управляющего блока, прямой и инверсный выходы триггера цикла соединены с вторым и третьим выходами управляющего блока, прямой выход триггера цикла соединен с установочными входами регистров, счетный вход счетчика соединен с первым входом управля- ющемого блока,вход первого преобразователя напряжения в код соединен с вторым входом управляющего блока,входы второго преобразователя напряжения в код соединены с третьим и четвертым входами управляющего блока, а выходы регистров соединены с адресными входами постоянного запоминающего узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для сопряжения цифровой и аналоговой вычислительных машин | 1983 |

|

SU1128273A1 |

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1436111A1 |

| Стабилизатор-регулятор переменного напряжения | 1987 |

|

SU1501009A1 |

| Стабилизированный преобразователь постоянного напряжения в постоянное | 1976 |

|

SU752661A1 |

| ГЕНЕРАТОР ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМПУЛЬСОВ | 2022 |

|

RU2784622C1 |

| Измеритель сопротивлений резисторов | 1985 |

|

SU1357866A1 |

| СТАБИЛИЗИРОВАННЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ С ЦИФРОВЫМИ МИКРОСХЕМАМИ | 1991 |

|

RU2014713C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Двухтактный преобразователь | 1989 |

|

SU1676042A1 |

Изобретение относится к области стабилизированных источников питания. Целью изобретения является расширение диапазона изменения входного напряжения при одновременном уменьшении массы и объема преобразователя-стабилизатора. Цель достигается тем, что стабилизация выходного напряжения преобразователя происходит следующим образом. Задающий генератор 1 формирует прямоугольные импульсы, которые поступают на первый вход упр;авляющего

| Преобразователь-стабилизатор | 1972 |

|

SU490109A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Стабилизированный преобразователь постоянного напряжения в постоянное | 1976 |

|

SU752661A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| | gl | |||

Авторы

Даты

1986-05-23—Публикация

1984-11-01—Подача